Beruflich Dokumente

Kultur Dokumente

9a04605 Vlsi Design

Hochgeladen von

sivabharathamurthyCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

9a04605 Vlsi Design

Hochgeladen von

sivabharathamurthyCopyright:

Verfügbare Formate

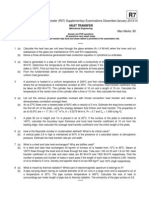

Code: 9A04605

B. Tech III Year II Semester (R09) Regular & Supplementary Examinations, April/May 2013 VLSI DESIGN (Common to ECE, EIE & E.Con.E) Time: 3 hours Max. Marks: 70 Answer any FIVE questions All questions carry equal marks ***** 1 (a) (b) (c) 2 (a) (b) 3 4 What are the types of major processes used in IC fabrication? Mention any four advantages of VLSI. Mention the design flow in VLSI process. Explain clearly about the latch up effects in p well structure with the help of a neat circuit diagrams. Mention remedies for this effect. Explain lambda based design rules. Derive an equation for the propagation delay from input to output of the pass transistor chain shown in figure. Design logic for an ALU that can perform both logical and arithmetic operations. Enumerate all the 16 possible functions of a two input ALU. What are the various design options used to implement the CMOS system design explain each in detail? Write a program in VHDL for an 8:1 multiplexer in behavioral and structural style and compare them. Through comparison explain the manufacturing tests and functionality tests. Mention how many test vectors are required to exhaustively test a combinational circuit with n-inputs and a sequential circuit with n-inputs and m-storage devices respectively. *****

5 (a) (b) 6

8 (a) (b)

Code: 9A04605

B. Tech III Year II Semester (R09) Regular & Supplementary Examinations, April/May 2013 VLSI DESIGN (Common to ECE, EIE & E.Con.E) Time: 3 hours Max. Marks: 70 Answer any FIVE questions All questions carry equal marks ***** 1 2 3 4 With neat sketches explain electron lithography process. Explain clearly about different operating regions in nmos transistor with neat diagrams. Draw the CMOS 2 input NAND gate, its physical lay out with its stick diagram. Estimate the total delay when a larger load capacitance is driven by a large inverter gate N which is driven by a small gate N-1 and so on. Provide the design of an 8 8 array multiplier. Explain the working principle of booth multiplier. Write about standard cell based design. Implement an optimized 3X8 binary decoder using PLA. What are the various styles of writing a program in VHDL? Explain. Write a program using VHDL in structural style to implement a 3 8 binary decoder. What is a fault model? Explain in detail about stuck at fault model. Explain the terms fault simulation, fault coverage and fault collapsing. *****

5 (a) (b) 6 (a) (b) 7 (a) (b) 8 (a) (b)

Code: 9A04605

B. Tech III Year II Semester (R09) Regular & Supplementary Examinations, April/May 2013 VLSI DESIGN (Common to ECE, EIE & E.Con.E) Time: 3 hours Max. Marks: 70 Answer any FIVE questions All questions carry equal marks ***** 1 (a) (b) (c) 2 3 (a) (b) 4 5 Write important characteristics of CMOS. Why CMOS is preferred over bipolar technology? Short notes on advanced CMOS fabrication technologies. Mention different non ideal I-V effects and clearly explain about them. What are the effects of scaling on Vt? Discuss the limits due to sub threshold currents. What is the problem of driving large capacitance load? Explain a method to drive such load. Implement a 4-bit ALU using adder as basic primitive block and explain how the arithmetic and logical operations are performed using adder element. Differentiate between chips with programmable logic structure and chips with programmable interconnect. Give an example for each. Give a brief description of various methods of programming the programmable array logic (PALs) in CMOS. What is register transfer level (RTL) synthesis? Explain with an example how RTL descriptions in VHDL capture the attributes of a design. Write about different fault models. List out all the possible struck at faults for three input NAND gate and thus generate the minimum test vectors that detect all the faults. *****

6 (a) (b)

7 (a) (b) 8 (a) (b)

Code: 9A04605

B. Tech III Year II Semester (R09) Regular & Supplementary Examinations, April/May 2013 VLSI DESIGN (Common to ECE, EIE & E.Con.E) Time: 3 hours Max. Marks: 70 Answer any FIVE questions All questions carry equal marks ***** 1 (a) (b) 2 (a) (b) Explain the evaluation of a VLSI design technology. Explain clearly about Moores law. Draw the circuit of nMOS inverter and explain its operation. Draw and explain its transfer characteristics. Determine the pull-up and pull-down ratio for an nMOS inverter driven by another nMOS inverter. Design a stick diagram for NMOS EX-OR gate. Calculate gate capacitance value of 2 m technology minimum sized transistor with gate to channel capacitance value of 8 X 104 pF/ohm m2. Explain the principle of working of a 4-bit carry-look ahead adder and hence draw the logical schematic used to obtain the generate and propagate signals. With the help of the logical schematic explain the working of a parity generator. Summarize the difference between reprogrammable gate array designing and programmable interconnect designing. Give a brief description about full custom design. Justify where full custom design is preferred to semicustom design. Compare the simulation process at various levels of design of chips with respect to complexity of computation, speed and accuracy. With the help of schematic diagram using logical blocks explain the working of BILBO as a test pattern generator. Discuss about various approaches of design for testability. *****

3 4

5 (a) (b) 6 (a) (b)

8 (a) (b)

Das könnte Ihnen auch gefallen

- Control Systems (CS) Notes As Per JntuaDokument203 SeitenControl Systems (CS) Notes As Per Jntuasivabharathamurthy100% (3)

- SSC Telugu (FL) (AP)Dokument232 SeitenSSC Telugu (FL) (AP)sivabharathamurthyNoch keine Bewertungen

- 07A4EC01 Environmental StudiesDokument1 Seite07A4EC01 Environmental StudiessivabharathamurthyNoch keine Bewertungen

- R7410407 Operating SystemsDokument1 SeiteR7410407 Operating SystemssivabharathamurthyNoch keine Bewertungen

- R7311006 Process Control InstrumentationDokument1 SeiteR7311006 Process Control InstrumentationsivabharathamurthyNoch keine Bewertungen

- 9A05707 Software Project ManagementDokument4 Seiten9A05707 Software Project ManagementsivabharathamurthyNoch keine Bewertungen

- R7311506 Operating SystemsDokument1 SeiteR7311506 Operating SystemssivabharathamurthyNoch keine Bewertungen

- SSC Social Textbook (AP)Dokument100 SeitenSSC Social Textbook (AP)sivabharathamurthyNoch keine Bewertungen

- R7410506 Mobile ComputingDokument1 SeiteR7410506 Mobile ComputingsivabharathamurthyNoch keine Bewertungen

- R5410201 Neural Networks & Fuzzy LogicDokument1 SeiteR5410201 Neural Networks & Fuzzy LogicsivabharathamurthyNoch keine Bewertungen

- R7311205 Distributed DatabasesDokument1 SeiteR7311205 Distributed DatabasessivabharathamurthyNoch keine Bewertungen

- R7310506 Design & Analysis of AlgorithmsDokument1 SeiteR7310506 Design & Analysis of AlgorithmssivabharathamurthyNoch keine Bewertungen

- 9A13701 Robotics and AutomationDokument4 Seiten9A13701 Robotics and AutomationsivabharathamurthyNoch keine Bewertungen

- Code: R7311306: (Electronics & Control Engineering)Dokument1 SeiteCode: R7311306: (Electronics & Control Engineering)sivabharathamurthyNoch keine Bewertungen

- R7312301 Transport Phenomena in BioprocessesDokument1 SeiteR7312301 Transport Phenomena in BioprocessessivabharathamurthyNoch keine Bewertungen

- R7310306 Heat TransferDokument1 SeiteR7310306 Heat Transfersivabharathamurthy100% (1)

- R7310106 Engineering GeologyDokument1 SeiteR7310106 Engineering GeologysivabharathamurthyNoch keine Bewertungen

- R7310406 Digital CommunicationsDokument1 SeiteR7310406 Digital CommunicationssivabharathamurthyNoch keine Bewertungen

- R7310206 Linear Systems AnalysisDokument1 SeiteR7310206 Linear Systems AnalysissivabharathamurthyNoch keine Bewertungen

- 9A21506 Mechanisms & Mechanical DesignDokument8 Seiten9A21506 Mechanisms & Mechanical DesignsivabharathamurthyNoch keine Bewertungen

- 9A23501 Heat Transfer in BioprocessesDokument4 Seiten9A23501 Heat Transfer in BioprocessessivabharathamurthyNoch keine Bewertungen

- R5310406 Digital CommunicationsDokument1 SeiteR5310406 Digital CommunicationssivabharathamurthyNoch keine Bewertungen

- 9A15502 Digital System DesignDokument4 Seiten9A15502 Digital System Designsivabharathamurthy100% (1)

- R5310204 Power ElectronicsDokument1 SeiteR5310204 Power ElectronicssivabharathamurthyNoch keine Bewertungen

- 9A04504 Digital IC ApplicationsDokument4 Seiten9A04504 Digital IC ApplicationssivabharathamurthyNoch keine Bewertungen

- 9A05505 Operating SystemsDokument4 Seiten9A05505 Operating SystemssivabharathamurthyNoch keine Bewertungen

- 9A14503 Principles of Machine DesignDokument8 Seiten9A14503 Principles of Machine DesignsivabharathamurthyNoch keine Bewertungen

- 9A10505 Principles of CommunicationsDokument4 Seiten9A10505 Principles of CommunicationssivabharathamurthyNoch keine Bewertungen

- 9A02505 Electrical Machines-IIIDokument4 Seiten9A02505 Electrical Machines-IIIsivabharathamurthyNoch keine Bewertungen

- 9A03505 Heat TransferDokument4 Seiten9A03505 Heat TransfersivabharathamurthyNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5782)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Nowy Przewód Dvop1960 3m Mini Din 8-Pin Sub-D 9-Pin Panasonic DatasheetDokument3 SeitenNowy Przewód Dvop1960 3m Mini Din 8-Pin Sub-D 9-Pin Panasonic DatasheetShekhar SrivassNoch keine Bewertungen

- Lib Burst GeneratedDokument2 SeitenLib Burst GeneratedAbyssNoch keine Bewertungen

- Datasheet - CoronaShield SC - 217.01 - EN - GL - 2012Dokument3 SeitenDatasheet - CoronaShield SC - 217.01 - EN - GL - 2012LECTORNoch keine Bewertungen

- Strategies for Implementing Web 3.0 Tools in EducationDokument8 SeitenStrategies for Implementing Web 3.0 Tools in EducationJefri HussinNoch keine Bewertungen

- Expression Language in UI Personalization - EM WP PDFDokument11 SeitenExpression Language in UI Personalization - EM WP PDFJihad Darwish100% (1)

- Mini Cooper S: User GuideDokument24 SeitenMini Cooper S: User GuideGazza TNoch keine Bewertungen

- HexadecimalDokument3 SeitenHexadecimalAngel LawsonNoch keine Bewertungen

- Rotary Heat Recovery Unit for Commercial BuildingsDokument2 SeitenRotary Heat Recovery Unit for Commercial BuildingsDamian OvidiuNoch keine Bewertungen

- Adobe Experience Manager Architect: Adobe Certified Expert Exam GuideDokument8 SeitenAdobe Experience Manager Architect: Adobe Certified Expert Exam GuideZjadacz AntymateriiNoch keine Bewertungen

- Indra Sakti CVDokument3 SeitenIndra Sakti CVHendri Agus Setiawan BintangNoch keine Bewertungen

- Dse4420 Installation InstDokument2 SeitenDse4420 Installation InstMuhammad Denny67% (3)

- CiscoDokument122 SeitenCiscoManoel ValladãoNoch keine Bewertungen

- Lecture 1-3 Introduction To Verilog HDLDokument50 SeitenLecture 1-3 Introduction To Verilog HDLjjeongdongieeNoch keine Bewertungen

- Basic FeaturesDokument19 SeitenBasic FeaturesumangNoch keine Bewertungen

- Thesis Theme 2.0Dokument8 SeitenThesis Theme 2.0PaperWritingWebsitePalmBay100% (2)

- ELECTRONICS TRICKS and TIPS - DT 830D Digital Multimeter Fault Finding PCB ComponentDokument6 SeitenELECTRONICS TRICKS and TIPS - DT 830D Digital Multimeter Fault Finding PCB Componentmuntashir mamunNoch keine Bewertungen

- Liquid-filled distribution transformers up to 24 kVDokument1 SeiteLiquid-filled distribution transformers up to 24 kVRAULNoch keine Bewertungen

- BCA-404: Data Mining and Data Ware HousingDokument19 SeitenBCA-404: Data Mining and Data Ware HousingefwewefNoch keine Bewertungen

- TL-PA2010 (EU) V1 DatesheetDokument2 SeitenTL-PA2010 (EU) V1 DatesheetSuganya LokeshNoch keine Bewertungen

- 5G Air Interface by MPIRICAL PDFDokument210 Seiten5G Air Interface by MPIRICAL PDFvicky_211287Noch keine Bewertungen

- Wireless Compilation 19122014wir CompDokument21 SeitenWireless Compilation 19122014wir CompPankaj Singh RawatNoch keine Bewertungen

- b66042 - Programmer's GuideDokument362 Seitenb66042 - Programmer's GuideMiroserh100% (1)

- Example 2.2: 2.3 C-V CharacteristicsDokument1 SeiteExample 2.2: 2.3 C-V CharacteristicsCarlos SaavedraNoch keine Bewertungen

- Ami WimaxDokument29 SeitenAmi WimaxSingh KamaldeepNoch keine Bewertungen

- Infinity Serviss: Batch Coding MachinesDokument2 SeitenInfinity Serviss: Batch Coding MachinesSatyaki SNoch keine Bewertungen

- GBA's Guide to Selecting Flare Tip MaterialsDokument2 SeitenGBA's Guide to Selecting Flare Tip MaterialsDpto SSO SimbioNoch keine Bewertungen

- Input and Output DevicesDokument22 SeitenInput and Output Devicesanuragmishra1205Noch keine Bewertungen

- OES 2 enDokument34 SeitenOES 2 en111Noch keine Bewertungen

- Chapter 10: Performance Measurement, Monitoring, and Program EvaluationDokument20 SeitenChapter 10: Performance Measurement, Monitoring, and Program EvaluationShauntina SorrellsNoch keine Bewertungen

- TS-4000 Service Manual Rev. 1.0Dokument24 SeitenTS-4000 Service Manual Rev. 1.0Ринат Жахин100% (1)