Beruflich Dokumente

Kultur Dokumente

Webench Design 1504242 1 2

Hochgeladen von

Yogeswaran SundarrajOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Webench Design 1504242 1 2

Hochgeladen von

Yogeswaran SundarrajCopyright:

Verfügbare Formate

VinMin = 14.

0V

VinMax = 60.0V

Vout = 12.0V

Iout = 5.0A

WEBENCH

Device = LM5117PMH/NOPB

Topology = Buck

Created = 2/26/13 6:02:53 PM

BOM Cost = $6.72

Total Pd = 3.3W

Footprint = 1,940.0mm2

BOM Count = 26

Design Report

Design : 1504242/1 LM5117PMH/NOPB

LM5117PMH/NOPB 14.0V-60.0V to 12.0V @ 5.0A

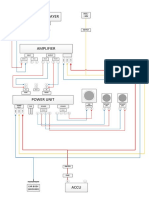

Dvcc

D1

Ruv2

Cvcc

M1

Cboot

DEMB

VCC

VIN

Cin

Cinx

UVLO

L1

HB

LM5 1 1 7

HO

U1

RT

SW

RES

Rram p

M2

LO

CS

SS

VCCDIS

Cout

CSG

CM

AGND

PGAND COMP

Rsense

RAMP

FB

Rfb2

Ccom p2

Ruv1

Rt

Cres

Css

Ccom p1 Rcom p

Cram p

Rfb1

Electrical BOM

# Name

Manufacturer

Part Number

Properties

Qty

Price

1. Cboot

AVX

08053C104KAT2A

Series= X7R

Cap= 100.0 nF

ESR= 280.0 mOhm

VDC= 25.0 V

IRMS= 0.0 A

$0.01

CC0805KRX7R9BB272

Series= X7R

Cap= 2.7 nF

VDC= 50.0 V

IRMS= 0.0 A

CC0805JRNP09BN101

Series= C0G/NP0

Cap= 100.0 pF

VDC= 50.0 V

IRMS= 0.0 A

EEUED2E470

Series= 286

Cap= 47.0 F

ESR= 380.955 mOhm

VDC= 250.0 V

IRMS= 920.0 mA

2. Ccomp1

3. Ccomp2

4. Cin

Yageo America

Yageo America

Panasonic

Footprint

0805 13mm2

$0.01

0805 13mm2

$0.01

0805 13mm2

$0.37

CAPPR5-12.5X25 210mm2

5. Cinx

TDK

6. Cout

Nippon Chemi-Con

7. Cramp

Yageo America

8. Cres

MuRata

C2012X7R2A104K

Series= X7R

Cap= 100.0 nF

ESR= 15.8 mOhm

VDC= 100.0 V

IRMS= 0.0 A

APXE160ARA101MF80G

Series= PXE

Cap= 100.0 F

ESR= 24.0 mOhm

VDC= 16.0 V

IRMS= 2.7 A

CC0805KRX7R9BB821

Series= X7R

Cap= 820.0 pF

VDC= 50.0 V

IRMS= 0.0 A

GRM155R60J474KE19D

Series= X5R

Cap= 470.0 nF

VDC= 6.3 V

IRMS= 0.0 A

Copyright 2013, Texas Instruments Incorporated

WEBENCH

Design Report

$0.03

0805 13mm2

$0.75

CAPSMT_62_F80 74mm2

$0.01

0805 13mm2

LM5117PMH/NOPB : LM5117PMH/NOPB 14.0V-60.0V to 12.0V @ 5.0A

$0.01

0402 8mm2

ti.com/webench

February 26, 2013 21:57:31 GMT-8

WEBENCH

# Name

Manufacturer

Part Number

Properties

Qty

Price

9. Css

Yageo America

CC0805KRX7R9BB153

Series= X7R

Cap= 15.0 nF

VDC= 50.0 V

IRMS= 0.0 A

$0.01

EMK212B7474KD-T

Series= X7R

Cap= 470.0 nF

VDC= 16.0 V

IRMS= 0.0 A

BAT54-7-F

VF@Io= 650.0 mV

VRRM= 30.0 V

VF@Io= 650.0 mV

VRRM= 30.0 V

L= 22.0 H

DCR= 10.0 mOhm

10. Cvcc

Taiyo Yuden

11. D1

Diodes Inc.

12. Dvcc

Diodes Inc.

13. L1

BAT54-7-F

Bourns

PM2110-220K-RC

Design

Footprint

0805 13mm2

$0.02

0805 13mm2

$0.03

SOT-23 22mm2

$0.03

SOT-23 22mm2

$1.21

PM2110 890mm2

14. M1

Infineon Technologies

BSZ160N10NS3 G

VdsMax= 100.0 V

IdsMax= 28.0 Amps

$0.63

15. M2

Infineon Technologies

BSZ160N10NS3 G

VdsMax= 100.0 V

IdsMax= 28.0 Amps

$0.63

PG-TSDSON-8 29mm2

PG-TSDSON-8 29mm2

16. Rcomp

Vishay-Dale

17. Rfb1

Vishay-Dale

18. Rfb2

Vishay-Dale

19. Rramp

Vishay-Dale

20. Rsense

Stackpole Electronics Inc

21. Rt

Vishay-Dale

22. Ruv1

Vishay-Dale

23. Ruv2

Vishay-Dale

24. U1

Texas Instruments

CRCW040226K1FKED

Series= CRCW..e3

Res= 26.1 kOhm

Power= 63.0 mW

Tolerance= 1.0%

CRCW04021K00FKED

Series= CRCW..e3

Res= 1,000 Ohm

Power= 63.0 mW

Tolerance= 1.0%

CRCW040214K0FKED

Series= CRCW..e3

Res= 14.0 kOhm

Power= 63.0 mW

Tolerance= 1.0%

CRCW0402221KFKED

Series= CRCW..e3

Res= 221.0 kOhm

Power= 63.0 mW

Tolerance= 1.0%

CSR1206FK12L0

Series= ?

Res= 12.0 mOhm

Power= 500.0 mW

Tolerance= 1.0%

CRCW040220K0FKED

Series= CRCW..e3

Res= 20.0 kOhm

Power= 63.0 mW

Tolerance= 1.0%

CRCW04025K49FKED

Series= CRCW..e3

Res= 5.49 kOhm

Power= 63.0 mW

Tolerance= 1.0%

CRCW040254K9FKED

Series= CRCW..e3

Res= 54.9 kOhm

Power= 63.0 mW

Tolerance= 1.0%

LM5117PMH/NOPB

Switcher

$0.01

0402 8mm2

$0.01

0402 8mm2

$0.01

0402 8mm2

$0.01

0402 8mm2

$0.11

1206 19mm2

$0.01

0402 8mm2

$0.01

0402 8mm2

$0.01

0402 8mm2

$2.04

MXA20A 71mm2

Copyright 2013, Texas Instruments Incorporated

WEBENCH

Design Report

LM5117PMH/NOPB : LM5117PMH/NOPB 14.0V-60.0V to 12.0V @ 5.0A

ti.com/webench

February 26, 2013 21:57:31 GMT-8

WEBENCH

IC Tj

Design

Duty Cycle

52

85

51

80

50

75

49

70

Duty Cycle(%)

IC Tj(degC)

90

48

47

46

45

44

43

65

60

55

50

45

40

42

35

41

30

25

40

20

39

15

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

3 .0

3 .5

4 .0

4 .5

5 .0

4 .0

4 .5

5 .0

4 .0

4 .5

5 .0

Iout(A)

Vin= 6 0 .0 V

Vin= 1 4 .0 V

Cin IRMS

Vin= 3 7 .0 V

Vin= 6 0 .0 V

M2 PdSw

2 .2 5

2 .0 0

M2 PdSw(W)

1 .7 5

Cin IRMS(A)

2 .5

1 .5 0

1 .2 5

1 .0 0

0 .7 5

0 .5 0

0 .2 5

0 .1 8

0 .1 7

0 .1 6

0 .1 5

0 .1 4

0 .1 3

0 .1 2

0 .1 1

0 .1 0

0 .0 9

0 .0 8

0 .0 7

0 .0 6

0 .0 5

0 .0 4

0 .0 3

0 .0 2

0 .0 1

0 .0 0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

2 .5

3 .0

3 .5

Iout(A)

Vin= 6 0 .0 V

Vin= 1 4 .0 V

L Pd

Vin= 3 7 .0 V

Vin= 6 0 .0 V

Efficiency

98

0 .3 2 5

97

0 .3 0 0

96

0 .2 7 5

Efficiency(%)

0 .2 5 0

L Pd(W)

0 .2 2 5

0 .2 0 0

0 .1 7 5

0 .1 5 0

0 .1 2 5

95

94

93

92

0 .1 0 0

91

0 .0 7 5

90

0 .0 5 0

89

0 .0 2 5

88

0 .0 0 0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

WEBENCH

Design Report

3 .0

3 .5

Iout(A)

Vin= 6 0 .0 V

Copyright 2013, Texas Instruments Incorporated

2 .5

Vin= 1 4 .0 V

LM5117PMH/NOPB : LM5117PMH/NOPB 14.0V-60.0V to 12.0V @ 5.0A

Vin= 3 7 .0 V

Vin= 6 0 .0 V

ti.com/webench

February 26, 2013 21:57:31 GMT-8

WEBENCH

M1 PdCond

0 .0 4 5 0

0 .4 0 0

0 .0 4 2 5

0 .3 7 5

0 .0 4 0 0

0 .3 5 0

0 .0 3 7 5

0 .3 2 5

0 .0 3 5 0

0 .3 0 0

M1 PdCond(W)

Vout p- p(V)

Vout p- p

0 .0 3 2 5

0 .0 3 0 0

0 .0 2 7 5

0 .0 2 5 0

0 .0 2 2 5

0 .0 2 0 0

0 .0 1 7 5

0 .2 7 5

0 .2 5 0

0 .2 2 5

0 .2 0 0

0 .1 7 5

0 .1 5 0

0 .1 2 5

0 .0 1 5 0

0 .1 0 0

0 .0 1 2 5

0 .0 7 5

0 .0 1 0 0

0 .0 5 0

0 .0 0 7 5

0 .0 2 5

0 .0 0 5 0

0 .0 0 0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

2 .5

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

3 .0

3 .5

4 .0

4 .5

5 .0

4 .0

4 .5

5 .0

4 .5

5 .0

Iout(A)

Vin= 6 0 .0 V

Vin= 1 4 .0 V

Vin= 3 7 .0 V

Cin Pd

Vin= 6 0 .0 V

Cout Pd

0 .0 0 6 5

0 .7 0

0 .6 5

0 .0 0 6 0

0 .6 0

0 .0 0 5 5

0 .5 5

0 .0 0 5 0

0 .5 0

0 .0 0 4 5

Cout Pd(W)

Cin Pd(W)

Design

0 .4 5

0 .4 0

0 .3 5

0 .3 0

0 .2 5

0 .0 0 4 0

0 .0 0 3 5

0 .0 0 3 0

0 .0 0 2 5

0 .0 0 2 0

0 .2 0

0 .0 0 1 5

0 .1 5

0 .1 0

0 .0 0 1 0

0 .0 5

0 .0 0 0 5

0 .0 0

0 .0 0 0 0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

2 .5

3 .0

3 .5

Iout(A)

Vin= 6 0 .0 V

Vin= 1 4 .0 V

M1 Irms

Vin= 3 7 .0 V

Vin= 6 0 .0 V

M1 Pd

1 .1

4 .5

1 .0

4 .0

0 .9

0 .8

M1 Pd(W)

M1 Irms(A)

3 .5

3 .0

2 .5

2 .0

0 .7

0 .6

0 .5

0 .4

1 .5

0 .3

1 .0

0 .2

0 .5

0 .1

0 .0

0 .0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

Design Report

3 .0

3 .5

4 .0

Iout(A)

Vin= 6 0 .0 V

Copyright 2013, Texas Instruments Incorporated

WEBENCH

2 .5

Vin= 1 4 .0 V

LM5117PMH/NOPB : LM5117PMH/NOPB 14.0V-60.0V to 12.0V @ 5.0A

Vin= 3 7 .0 V

Vin= 6 0 .0 V

ti.com/webench

February 26, 2013 21:57:31 GMT-8

WEBENCH

Rsns Pd

Design

L1 Irms

0 .2 5 0

5 .0

0 .2 2 5

4 .5

0 .2 0 0

4 .0

L1 Irms(A)

Rsns Pd(W)

0 .1 7 5

0 .1 5 0

0 .1 2 5

0 .1 0 0

0 .0 7 5

3 .5

3 .0

2 .5

2 .0

1 .5

0 .0 5 0

1 .0

0 .0 2 5

0 .5

0 .0 0 0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

Vin= 6 0 .0 V

Vin= 1 4 .0 V

Vin= 3 7 .0 V

55

5 .5

50

5 .0

45

4 .5

40

4 .0

35

30

25

1 .5

10

1 .0

0 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

Vin= 6 0 .0 V

Vin= 1 4 .0 V

1 .5

2 .0

2 .5

Vin= 3 7 .0 V

3 .0

3 .5

Design Report

3 .5

4 .5

5 .0

4 .0

4 .5

5 .0

Vin= 6 0 .0 V

4 .0

4 .5

5 .0

4 .5 0

4 .2 5

4 .0 0

3 .7 5

3 .5 0

3 .2 5

3 .0 0

2 .7 5

2 .5 0

2 .2 5

2 .0 0

1 .7 5

1 .5 0

1 .2 5

1 .0 0

0 .7 5

0 .5 0

0 .2 5

0 .0 0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

Iout(A)

Vin= 6 0 .0 V

Copyright 2013, Texas Instruments Incorporated

WEBENCH

3 .0

Vin= 3 7 .0 V

Iout(A)

Vin= 1 4 .0 V

2 .5

M2 Irms

M2 Irms(A)

Iin Avg(A)

Iin Avg

1 .0

4 .0

Vin= 6 0 .0 V

Iout(A)

4 .5 0

4 .2 5

4 .0 0

3 .7 5

3 .5 0

3 .2 5

3 .0 0

2 .7 5

2 .5 0

2 .2 5

2 .0 0

1 .7 5

1 .5 0

1 .2 5

1 .0 0

0 .7 5

0 .5 0

0 .2 5

0 .0 0

0 .5

5 .0

2 .5

2 .0

2 .5

4 .5

3 .0

15

2 .0

4 .0

3 .5

20

1 .5

3 .5

SW Ipk

6 .0

SW Ipk(A)

Pout(W)

Pout

1 .0

3 .0

Iout(A)

60

0 .5

2 .5

Vin= 1 4 .0 V

LM5117PMH/NOPB : LM5117PMH/NOPB 14.0V-60.0V to 12.0V @ 5.0A

Vin= 3 7 .0 V

Vin= 6 0 .0 V

ti.com/webench

February 26, 2013 21:57:31 GMT-8

WEBENCH

Cross Freq Ch1

Design

M2 Pd

2 3 ,6 1 0

0 .5 0

0 .4 5

2 3 ,6 0 0

0 .4 0

2 3 ,5 9 5

2 3 ,5 9 0

M2 Pd(W)

Cross Freq Ch1 (Hz)

2 3 ,6 0 5

2 3 ,5 8 5

2 3 ,5 8 0

2 3 ,5 7 5

2 3 ,5 7 0

0 .3 5

0 .3 0

0 .2 5

0 .2 0

0 .1 5

2 3 ,5 6 5

0 .1 0

2 3 ,5 6 0

0 .0 5

2 3 ,5 5 5

0 .0 0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

4 .0

4 .5

5 .0

4 .0

4 .5

5 .0

Iout(A)

Vin= 6 0 .0 V

Vin= 1 4 .0 V

Total Pd

Vin= 3 7 .0 V

Vin= 6 0 .0 V

Cout IRMS

3 .2 5

0 .5 0

3 .0 0

0 .4 5

2 .7 5

0 .4 0

Cout IRMS(A)

Total Pd(W)

2 .5 0

2 .2 5

2 .0 0

1 .7 5

1 .5 0

1 .2 5

1 .0 0

0 .7 5

0 .3 5

0 .3 0

0 .2 5

0 .2 0

0 .1 5

0 .5 0

0 .1 0

0 .2 5

0 .0 5

0 .0 0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

3 .0

3 .5

Iout(A)

Vin= 6 0 .0 V

Vin= 1 4 .0 V

L Ipp

Vin= 3 7 .0 V

Vin= 6 0 .0 V

IC Pd

1 .8

0 .5 5 0

1 .7

0 .5 2 5

1 .6

1 .5

0 .5 0 0

1 .4

0 .4 7 5

1 .3

0 .4 5 0

1 .2

IC Pd(W)

L Ipp(A)

2 .5

1 .1

1 .0

0 .9

0 .8

0 .4 2 5

0 .4 0 0

0 .3 7 5

0 .3 5 0

0 .7

0 .3 2 5

0 .6

0 .3 0 0

0 .5

0 .2 7 5

0 .4

0 .2 5 0

0 .3

0 .2 2 5

0 .2

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

Design Report

3 .0

3 .5

Iout(A)

Vin= 6 0 .0 V

Copyright 2013, Texas Instruments Incorporated

WEBENCH

2 .5

Vin= 1 4 .0 V

LM5117PMH/NOPB : LM5117PMH/NOPB 14.0V-60.0V to 12.0V @ 5.0A

Vin= 3 7 .0 V

Vin= 6 0 .0 V

ti.com/webench

February 26, 2013 21:57:31 GMT-8

WEBENCH

M1 Tj

Design

M1 PdSw

100

1 .0

90

0 .9

85

0 .8

80

M1 PdSw(W)

M1 Tj(degC)

95

75

70

65

60

55

50

0 .7

0 .6

0 .5

0 .4

0 .3

45

40

0 .2

35

0 .1

30

0 .0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

4 .0

4 .5

5 .0

Iout(A)

Vin= 6 0 .0 V

Vin= 1 4 .0 V

Phase Marg Ch1

Vin= 3 7 .0 V

Vin= 6 0 .0 V

M2 Tj

6 2 .5

6 9 .0 0

5 7 .5

5 5 .0

6 8 .5 0

M2 Tj(degC)

Phase Marg Ch1 (deg)

6 0 .0

6 8 .7 5

6 8 .2 5

6 8 .0 0

6 7 .7 5

5 2 .5

5 0 .0

4 7 .5

4 5 .0

4 2 .5

4 0 .0

3 7 .5

6 7 .5 0

3 5 .0

3 2 .5

6 7 .2 5

3 0 .0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

0 .5

1 .0

1 .5

2 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

2 .5

3 .0

3 .5

Iout(A)

Vin= 6 0 .0 V

Vin= 1 4 .0 V

Vin= 3 7 .0 V

Vin= 6 0 .0 V

M2 PdCond

0 .3 5 0

0 .3 2 5

0 .3 0 0

M2 PdCond(W)

0 .2 7 5

0 .2 5 0

0 .2 2 5

0 .2 0 0

0 .1 7 5

0 .1 5 0

0 .1 2 5

0 .1 0 0

0 .0 7 5

0 .0 5 0

0 .0 2 5

0 .0 0 0

0 .5

1 .0

1 .5

2 .0

2 .5

3 .0

3 .5

4 .0

4 .5

5 .0

Iout(A)

Vin= 1 4 .0 V

Vin= 3 7 .0 V

Vin= 6 0 .0 V

Operating Values

#

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

Name

Cin IRMS

Cout IRMS

Iin Avg

L Ipp

L1 Irms

M1 Irms

M2 Irms

SW Ipk

BOM Count

FootPrint

Frequency

Value

2.011 A

514.713 mA

1.055 A

1.783 A

5.026 A

2.252 A

4.464 A

5.892 A

26

1.94 kmm2

248.234 kHz

Copyright 2013, Texas Instruments Incorporated

WEBENCH

Design Report

Category

Current

Current

Current

Current

Current

Current

Current

Current

General

General

General

Description

Input capacitor RMS ripple current

Output capacitor RMS ripple current

Average input current

Peak-to-peak inductor ripple current

Inductor ripple current

MOSFET RMS ripple current

MOSFET RMS ripple current

Peak switch current

Total Design BOM count

Total Foot Print Area of BOM components

Switching frequency

7

LM5117PMH/NOPB : LM5117PMH/NOPB 14.0V-60.0V to 12.0V @ 5.0A

ti.com/webench

February 26, 2013 21:57:31 GMT-8

WEBENCH

#

12.

13.

14.

15.

16.

17.

18.

19.

20.

21.

22.

23.

24.

25.

26.

27.

28.

29.

30.

31.

32.

33.

34.

35.

36.

37.

38.

Name

IC Tolerance

Mode

Pout

Total BOM

Vout OP

Duty Cycle

Efficiency

IC Tj

IOUT_OP

M1 Tj

M2 Tj

VIN_OP

Vout p-p

Cin Pd

Cout Pd

IC Pd

L Pd

M1 Pd

M1 PdCond

M1 PdSw

M2 Pd

M2 PdCond

M2 PdSw

Rsns Pd

Total Pd

Cross Freq Ch1

Phase Marg Ch1

Value

12.0 mV

CCM

60.0 W

$6.72

12.0 V

20.286 %

94.79 %

52.383 degC

5.0 A

100.268 degC

62.535 degC

60.0 V

43.724 mV

513.363 mW

6.358 mW

559.583 mW

333.186 mW

1.131 W

105.925 mW

1.025 W

515.0 mW

342.54 mW

172.46 mW

239.142 mW

3.298 W

23.581 kHz

68.542 deg

Category

General

General

General

General

Op_Point

Op_point

Op_point

Op_point

Op_point

Op_point

Op_point

Op_point

Op_point

Power

Power

Power

Power

Power

Power

Power

Power

Power

Power

Power

Power

Unknown

Unknown

Design

Description

IC Feedback Tolerance

Conduction Mode

Total output power

Total BOM Cost

Operational Output Voltage

Duty cycle

Steady state efficiency

IC junction temperature

Iout operating point

M1 MOSFET junction temperature

M2 MOSFET junction temperature

Vin operating point

Peak-to-peak output ripple voltage

Input capacitor power dissipation

Output capacitor power dissipation

IC power dissipation

Inductor power dissipation

M1 MOSFET total power dissipation

M1 MOSFET conduction losses

M1 MOSFET switching losses

M2 MOSFET total power dissipation

M2 MOSFET conduction losses

M2 MOSFET switching losses

Current Limit Sense Resistor Power Dissipation

Total Power Dissipation

Bode plot crossover frequency

Bode Plot Phase Margin

Design Inputs

#

1.

2.

3.

4.

5.

6.

7.

8.

9.

Name

Iout

Iout1

VinMax

VinMin

Vout

Vout1

base_pn

source

Ta

Value

5.0 A

5.0 Amps

60.0 V

14.0 V

12.0 V

12.0 Volt

LM5117

DC

30.0 degC

Description

Maximum Output Current

Output Current #1

Maximum input voltage

Minimum input voltage

Output Voltage

Output Voltage #1

National Based Product Number

Input Source Type

Ambient temperature

Design Assistance

1. Outline The LM5117 is a synchronous buck controller intended for step-down regulator applications from a high voltage or widely varying

input supply. The control method is based upon current mode control utilizing an emulated current ramp. Current mode control provides inherent

line feed-forward, cycle-by-cycle current limiting and ease of loop compensation. The use of an emulated control ramp reduces noise sensitivity

of the pulse-width modulation circuit, allowing reliable control of very small duty cycles necessary in high input voltage applications. External

Vcc An output voltage derived bias supply can be applied to the VCC pin to reduce the controller power dissipation at higher input voltage. This

can also relax constraints on the driver supply current if your external source can supply more than the LM(2)5117 internal regulator. Please

see Datasheet for more information. Diode Emulation A fully synchronous buck regulator implemented with a freewheel MOSFET rather than a

diode has the capability to sink current from the output in certain conditions such as light load, over-voltage or pre-bias startup. The LM(2)5117

provides a diode emulation feature that can be enabled to prevent reverse (drain to source) current flow in the low side free-wheel MOSFET.

2. LM5117 Product Folder : http://www.ti.com/product/lm5117 : contains the data sheet and other resources.

Texas Instruments' WEBENCH simulation tools attempt to recreate the performance of a substantially equivalent physical implementation

of the design. Simulations are created using Texas Instruments' published specifications as well as the published specifications of other

device manufacturers. While Texas Instruments does update this information periodically, this information may not be current at the time the

simulation is built. Texas Instruments does not warrant the accuracy or completeness of the specifications or any information contained therein.

Texas Instruments does not warrant that any designs or recommended parts will meet the specifications you entered, will be suitable for your

application or fit for any particular purpose, or will operate as shown in the simulation in a physical implementation. Texas Instruments does not

warrant that the designs are production worthy.

You should completely validate and test your design implementation to confirm the system functionality for your application prior to

production.

Use of Texas Instruments' WEBENCH simulation tools is subject to Texas Instruments' Site Terms and Conditions of Use. Prototype boards

based on WEBENCH created designs are provided AS IS without warranty of any kind for evaluation and testing purposes and are subject to

the terms of the Evaluation License Agreement.

Copyright 2013, Texas Instruments Incorporated

WEBENCH

Design Report

LM5117PMH/NOPB : LM5117PMH/NOPB 14.0V-60.0V to 12.0V @ 5.0A

ti.com/webench

February 26, 2013 21:57:31 GMT-8

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Distribution Standard: Reference REV Title: Distribution Standard Date: OF Revision DateDokument56 SeitenDistribution Standard: Reference REV Title: Distribution Standard Date: OF Revision DateWarren MorseNoch keine Bewertungen

- Tamil Computer Book - LinuxDokument68 SeitenTamil Computer Book - LinuxSakthivel100% (11)

- JD56AULVer103TianMaModule en 15422879070Dokument13 SeitenJD56AULVer103TianMaModule en 15422879070Yogeswaran SundarrajNoch keine Bewertungen

- cc3200 Datasheet PDFDokument522 Seitencc3200 Datasheet PDFYogeswaran SundarrajNoch keine Bewertungen

- 111 PDFDokument9 Seiten111 PDFPrakhar JainNoch keine Bewertungen

- Hoja Caracteristicas 7404 PDFDokument5 SeitenHoja Caracteristicas 7404 PDFEdgarNoch keine Bewertungen

- User Manual: Printing and Binding By: S.Yogeswaran E-Mail: Web: Http://yogece - inDokument2 SeitenUser Manual: Printing and Binding By: S.Yogeswaran E-Mail: Web: Http://yogece - inYogeswaran SundarrajNoch keine Bewertungen

- Regulation - 2009: Affiliated Institutions Anna University, ChennaiDokument27 SeitenRegulation - 2009: Affiliated Institutions Anna University, ChennaiYogeswaran SundarrajNoch keine Bewertungen

- Regulation - 2009: Affiliated Institutions Anna University, ChennaiDokument27 SeitenRegulation - 2009: Affiliated Institutions Anna University, ChennaiYogeswaran SundarrajNoch keine Bewertungen

- Guide To Buildauto Robots Auto RobotsDokument28 SeitenGuide To Buildauto Robots Auto RobotsSharan RajendiranNoch keine Bewertungen

- Bluetooth UART Module 1545 RobokitsDokument23 SeitenBluetooth UART Module 1545 Robokitsf4a2dl5939Noch keine Bewertungen

- Programming Atmega Using Boot LoaderDokument4 SeitenProgramming Atmega Using Boot LoaderrnepologyNoch keine Bewertungen

- Experiment 3Dokument10 SeitenExperiment 3Yogeswaran SundarrajNoch keine Bewertungen

- 20121229.beginners Guide To Android Reverse EngineeringDokument18 Seiten20121229.beginners Guide To Android Reverse EngineeringYogeswaran SundarrajNoch keine Bewertungen

- CS1306 LMDokument104 SeitenCS1306 LMYogeswaran SundarrajNoch keine Bewertungen

- Welcome To Pinoybix!: Engineering MathematicsDokument4 SeitenWelcome To Pinoybix!: Engineering MathematicsMa. Corazon DumalaogNoch keine Bewertungen

- TCAD Lecture3Dokument16 SeitenTCAD Lecture3Thi NguyenNoch keine Bewertungen

- сервис мануал LG 43UJ634V шасси UD74P PDFDokument101 Seitenсервис мануал LG 43UJ634V шасси UD74P PDFsebas ruiz100% (1)

- A Study of Power System Security and Contingency AnalysisDokument4 SeitenA Study of Power System Security and Contingency AnalysisPurnima BiruaNoch keine Bewertungen

- 1GT105DC PDFDokument4 Seiten1GT105DC PDFIsos CellNoch keine Bewertungen

- Datasheet (TDA4863AJ) )Dokument20 SeitenDatasheet (TDA4863AJ) )Antony GarciaNoch keine Bewertungen

- Real Time In-Situ Measurements of Diffraction and Ferroelectric PolarizationDokument1 SeiteReal Time In-Situ Measurements of Diffraction and Ferroelectric PolarizationNational Physical LaboratoryNoch keine Bewertungen

- IHM Con Doble Display: Motors and DrivesDokument2 SeitenIHM Con Doble Display: Motors and DrivesJuan Carlos Palomares BeltranNoch keine Bewertungen

- Solving the Fresnel Equations with COMSOLDokument18 SeitenSolving the Fresnel Equations with COMSOLLogan BleysNoch keine Bewertungen

- Circuit Elements and ParametersDokument30 SeitenCircuit Elements and ParametersCarl PNoch keine Bewertungen

- Manual Temporizador TH3M PDFDokument10 SeitenManual Temporizador TH3M PDFMauricio Barraza FigueroaNoch keine Bewertungen

- EHV Catalogue PDFDokument29 SeitenEHV Catalogue PDFvineets058Noch keine Bewertungen

- Current Clamp Adaptor For Multimeters: by John ClarkeDokument7 SeitenCurrent Clamp Adaptor For Multimeters: by John Clarkemor3danNoch keine Bewertungen

- Analog communication: Balanced modulator using diodesDokument5 SeitenAnalog communication: Balanced modulator using diodesJasdeep SinghNoch keine Bewertungen

- Cat 3520 Ignition TransformerDokument9 SeitenCat 3520 Ignition TransformerRashid Mahmood Jaat0% (1)

- Eim 2nd Grading TopicDokument21 SeitenEim 2nd Grading Topickevin john quilino100% (1)

- Basic Principles of QCLs PDFDokument44 SeitenBasic Principles of QCLs PDFNikita SinghNoch keine Bewertungen

- MOS Investigate AVR & CBF RelayDokument25 SeitenMOS Investigate AVR & CBF Relaybuayasa22Noch keine Bewertungen

- SMAW 9 HTask 1Dokument5 SeitenSMAW 9 HTask 1Michael John SegarinoNoch keine Bewertungen

- Dyna-102 New PDFDokument4 SeitenDyna-102 New PDFZar MtzNoch keine Bewertungen

- NCP1251 DatasheetDokument24 SeitenNCP1251 DatasheetJose BenavidesNoch keine Bewertungen

- Skema Audio CarDokument1 SeiteSkema Audio CarValentVeeNoch keine Bewertungen

- Switching Operators Manual DistributionDokument338 SeitenSwitching Operators Manual DistributionJames GeorgeNoch keine Bewertungen

- UC5895Dokument8 SeitenUC5895aniNoch keine Bewertungen

- RF Systems Both PartsDokument124 SeitenRF Systems Both PartsJonathan CuroleNoch keine Bewertungen

- Abhi Baby Cry DetectorDokument22 SeitenAbhi Baby Cry DetectorÃbhilâśh RêddÿNoch keine Bewertungen

- FEKO Software For Automotive 2016Dokument2 SeitenFEKO Software For Automotive 2016UdhamNoch keine Bewertungen

- Eacon Inv Ec500Dokument74 SeitenEacon Inv Ec500michalis zisisNoch keine Bewertungen

- PHYSICS (Code No. 042) : Besides, The Syllabus Also Attempts ToDokument11 SeitenPHYSICS (Code No. 042) : Besides, The Syllabus Also Attempts ToRanit MukherjeeNoch keine Bewertungen