Beruflich Dokumente

Kultur Dokumente

Ultra Low Power Low Dropout Voltage Regulator

Hochgeladen von

mikeshinoda2011Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ultra Low Power Low Dropout Voltage Regulator

Hochgeladen von

mikeshinoda2011Copyright:

Verfügbare Formate

1072

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMSI: REGULAR PAPERS, VOL. 60, NO. 4, APRIL 2013

A 0.9- A Quiescent Current Output-Capacitorless LDO Regulator With Adaptive Power Transistors in 65-nm CMOS

Sau Siong Chong, Student Member, IEEE, and Pak Kwong Chan, Senior Member, IEEE

AbstractAn ultra-low quiescent current output-capacitorless low-dropout (OCL-LDO) regulator with adaptive power transistors technique is presented in this paper. The proposed technique permits the regulator to transform itself between 2-stage and 3-stage cascaded topologies with respective power transistor, depending on the load current condition. As such, it enables the OCL-LDO regulator to achieve ultra-low power consumption, high stability and good transient response without the need of off-chip capacitor at the output. The proposed LDO regulator has been implemented and fabricated in a UMC 65-nm CMOS process. It occupies an active area of 0.017 mm . The measured results have shown that the proposed circuit consumes a quiescent current of 0.9 A at no load, regulating the output at 1 V from a voltage supply of 1.2 V. It achieves full range stability from 0 to 100 mA load current at a maximum 100 pF parasitic capacitance load. The measured transient output voltage is 68.8 mV when load pF. current is stepped from 0 to 100 mA in 300 ns with The recovery time is about 6 s. Compared to previously reported counterparts, the proposed OCL-LDO regulator shows a signicant improvement in term of OCL-LDO transient gure-of-merit (FOM) as well as balanced performance parameters in terms of PSR, line regulation and load regulation. Index TermsLDO regulator, output-capacitorless LDO regulator, OCL-LDO regulator, ultra-low quiescent LDO, multi gain stage LDO.

I. INTRODUCTION ODERN development of power management unit for on-chip applications requires many voltage regulators to power-up each component and functional block [1]. A low-dropout (LDO) regulator is an ideal choice, especially for high performance and sensitive analog/mixed-signal blocks. Normally, the conventional LDO regulator relies on a bulky off-chip capacitor in the range of F to maintain a stable operation [2][6]. However, the large off-chip capacitor may not be favorable for on-chip applications that embed many voltage regulators. This motivates the use of embedded output-capacitorless LDO (OCL-LDO) regulators in the on-chip applications. With OCL-LDO regulators, the resistive and inductive parasitic

Manuscript received April 24, 2012; revised June 28, 2012; accepted July 27, 2012. Date of publication September 07, 2012; date of current version March 23, 2013. This paper was recommended by Associate Editor M. Ortmanns. The authors are with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798 (e-mail: chon0157@e. ntu.edu.sg; epkchan@ntu.edu.sg). Color versions of one or more of the gures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identier 10.1109/TCSI.2012.2215392

effects due to the external connection and the huge number of I/O pads on the chip can be eliminated. Furthermore, the printed-circuit-board layout area can be minimized [7]. This raises the interest in developing the OCL-LDO regulators. For portable electronic devices such as mobile phones and PDAs, low power consumption is a very critical requirement to extend the battery life. Thus, low voltage and low quiescent current are the most desirable parameters to achieve high battery efciency for power saving purpose. However, the OCL-LDO regulators suffer from the exiting tradeoff problem between power consumption against other important design parameters such as loop stability and transient response performance metrics. OCL-LDO regulators have been recently reported in [7][17]. In [8], an ultra-fast-transient regulator implemented in 90 nm CMOS with an on-chip capacitor of 0.6 nF consumes signicant high quiescent current of 6 mA, which is not suitable for low power design. Although the LDO regulator [9] implemented in a 2-stage structure is ease in frequency compensation, it comes at the price of not having high loop gain. In [10], an efcient multistage LDO regulator using an active-feedback frequency compensation approach is proposed. Its operating supply voltage needs to be increased to cater for the cascode structure in the slew rate enhancement circuit. Further architecture is the use of ipped-voltage-follower (FVF) based designs [7], [11], [12]. Due to the simple folded structure, the LDO regulators in [11] and [12] can be made stable easily in exchange of low loop gain. As a result, the load regulation is affected. When extended to the gain-enhanced structure [7] for load regulation improvement, it demands a minimum load current of 3 mA to maintain stability despite it consumes a quiescent current of 8 A. The minimum load current operation limits the exibility for applications that require light load currents. Furthermore, the value of minimum load current depends on the size of output load capacitor. A higher minimum load current is often needed when the OCL-LDO regulator drives a capacitive load larger than 50 pF. Similarly, the proposed designs in [13] and [14] demanding a minimum load current which makes it unattractive in the light load case. This is mainly because when load current is low, the non-dominant complex poles, having a large Q factor, cause a magnitude peaking near the unity gain frequency in a multistage structure. Ultra low quiescent current design techniques are proposed in [15] and [16]. Although LDO regulator in [15] consumes only 103 nA (the biasing current for the power transistor is not included), it has been reported to have a settling time of 400 s.

1549-8328/$31.00 2012 IEEE

CHONG AND CHAN: QUIESCENT CURRENT OUTPUT-CAPACITORLESS LDO REGULATOR

1073

Fig. 1. Structure of the proposed LDO regulator.

In [16], the design displays a faster settling time but it suffers from the larger undershoot and overshoot which may not meet the specic demand in some applications. Therefore, it is very challenging to design an ultra-low quiescent current and fast transient response OCL-LDO regulator without requiring the minimum load current due to additional gain stage(s) in a multistage circuit topology. This paper presents an ultra-low quiescent current OCL-LDO regulator using an adaptive power transistors technique in 65-nm CMOS process. The proposed technique allows the regulator to transform itself from a 2-stage structure to a 3-stage structure OCL-LDO regulator when a larger load current is drawn. In addition, it offers an ultra-low quiescent current solution for OCL-LDO regulator at no load whilst achieving stability across the whole load current range. Section II discusses the structure as well as the stability analysis of the proposed OCL-LDO regulator. Section III describes the details of the circuit implementation of the proposed structure. The experimental results, discussions and performance comparison are given in Section IV. Finally, the conclusion is drawn in Section V. II. PROPOSED ARCHITECTURE A. Topology Fig. 1 shows the proposed regulator architecture. It comprises a dynamic-biased error amplier as 1st gain stage, a non-inverting amplier as 2nd gain stage, a main power transistor , a sub-power transistor , an overshoot reduction circuitry, a frequency compensation network and a feedback network. In the proposed structure, the main power transistor is adaptively turned on or off, depending on the loading current condition. At light load condition, the 2nd gain stage is working in triode region and the main power transistor is turned off. The proposed regulator can be viewed as a 2-stage structure when the load . Besides, current is less than the dened threshold current in order to achieve ultra-low quiescent current and improve the current efciency at light loads, the dynamic biasing technique [4] is added to the 1st gain stage. The dynamic biasing technique proportional is achieved by making the biasing current . It should be noted to the current in sub-power transistor

that the biasing current stop increasing after the main power is activated. transistor , the proposed When the load current increases above regulator transforms itself into a 3-stage structure. Due to the higher transconductance and reduced effective output resistance arising from the load current, the pole at the output of regulator is shifted to high frequency. The proposed regulator remains stable with the structural transformation. Furthermore, it eliminates the minimum loading current and stability problems in a multistage structure. Therefore, it has the feature of ultra-low quiescent current at no load current condition. B. Stability Analysis The stability of the whole system is achieved by cascode compensation technique. Cascode compensation is adopted in this design because it offers higher current-bandwidth efciency when compared to the Miller compensation technique [18]. Not only does it improve stability by removing the right-hand-plane zero, it enhances power-supply rejection (PSR) [18][20]. To analyze the stability of the proposed OCL-LDO regulator, the small-signal transfer function is investigated. Due to the structural transformation, the stability of the proposed OCL-LDO regulator will be discussed on the basis of 2-stage and 3-stage is dened as the structure as shown in Fig. 2. It is noted that and transconductance of the respective device whereas denote the respective lumped output parasitic capacitance and output resistance of each node. The feedback factor, , is 1/2 in this design. The transfer function is derived using the following assumptions: (i) the input resistance of the feedback transcon, is equal to the reciprocal of its transconductance stage, ductance, (ii) the gain of 1st stage and 2nd stage are much larger and are much than 1 and (iii) the capacitances . smaller than -Stage Structure): When Case I ( , the 2nd gain stage is operating in triode region and the main power transistor is deactivated. Hence, they can be ignored in the analysis. Fig. 2(a) shows the simplied small-signal model of the proposed OCL-LDO regulator in a 2-stage conguration. The effective output resistance for 2-stage structure is dened by , where and is output resistance of sub-power transistor, feedback

1074

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMSI: REGULAR PAPERS, VOL. 60, NO. 4, APRIL 2013

Fig. 2. Small-signal modeling. (a) 2-stage and (b) 3-stage conguration.

network resistance and load resistance, respectively. In genis large, when the load current is small. The eral, derived transfer function is shown as follows:

(1) is the low frequency gain and where pole. They are given as is dominant (2) (3) Hence, the GBW can be obtained as (4) As shown in (1), the non-dominant poles and zero can be expressed by (5) (6) (7) Fig. 3 shows the relative position of poles and zero. It can be and cancel each other. The dominant pole observed that at the output of error amplier is the only pole locates within the unity-gain bandwidth. Hence, the loop stability solely depends on the location of . Due to cascode compensation, is pushed to higher frequencies by a cascode factor of .

Fig. 3. Loop gain (magnitude plot not in scale) of the proposed LDO regulator.

Furthermore, is proportional to , which is proportional to square-root of the load current. Therefore, the worst case stability happens at no load condition. As the load current inmoves to higher frequencies. As a result, the phase creases, margin is enhanced. -Stage Structure): The simpliCase II ( ed small-signal model of the proposed OCL-LDO regulator in the transformed 3-stage structure is depicted in Fig. 2(b). Since the 2nd gain stage and main power transistor are activated, they are included in the stability analysis. The overall structure can be viewed as a 3-stage amplier. The effective output resistance for 3-stage structure is dened by , where and is the output resistance of sub-power transistor, main power transistor, feedback network resistance and load resisis small because it is greatly tance, respectively. and dominated by the affected by load current . The simplied transfer function of the load resistance, transformed structure is shown in (8) at the bottom of the page.

(8)

CHONG AND CHAN: QUIESCENT CURRENT OUTPUT-CAPACITORLESS LDO REGULATOR

1075

The low frequency gain spectively given by

and dominant pole

are re-

TABLE I POLES AND ZEROS LOCATION WITH

PF

(9) (10) The expression of the GBW remains the same. However, the GBW is extended when compared to light load condition. It is is enhanced due to the dynamic biasing scheme. because From the transfer function (8), the non-dominant complex poles and the corresponding Q factor can then be determined as phase margin of 80 when load current is larger than 1 mA due to dynamically increase in the bias currents. Fig. 5 shows the simulated phase margin as a function of load current. Similar to previous works [7], [9], the worst case stability happens when is at its minimum and is at its maximum. Therefore, it can conclude that the stability of the regulator over the full is less than 100 pF. range is ensured as long as III. CIRCUIT IMPLEMENTATION OF PROPOSED LDO REGULATOR A. Schematic Fig. 6 depicts the simplied schematic of the proposed regulator. The error amplier is realized by a single folded-cascode stage with transistor - . The dynamic biasing network which is formed by transistors is added to improve the bandwidth of the ODC-LDO regulator under moderate load conditions. The non-inverting 2nd gain stage is realized by transistors . Transistors and are sub-power and main power transistor, respectively. The transistor size of and is 120 m/60 nm and 1800 m/60 nm, respectively. The feedback network is realized by a string of diode-connected PMOS transistors biased in the subthreshold region to minimize quiescent current as well as the silicon area [21]. In ultra-low power design, the silicon area will be much larger if the feedback network is realized by conventional approach using passive resistors. Finally, the load current is modeled as a resistor in parallel with a parasitic capacitor . The quiescent current distribution when is indicated in Fig. 6. The dynamic current sources can be ignored as they are very small when compared to the static current source at no load condition. The targeted quiescent current is about 0.5 A for the core circuit. Start-up circuit and bias current generator for the proposed design are shown in Fig. 7. Transistors and resistor form a supply-independent current generator to provide a constant biasing to the proposed circuit. A capacitive-coupled start-up circuit [22] is adopted because it consumes no static power. The tradeoff of this scheme is that the start-up capacitors occupy extra silicon area. The bias current generator consumes 0.3 A. Since all the load current is supplied by sub-power transistor when the system operates in 2-stage mode, the transistor in the dynamic biasing network is used to copy the current from [4]. A gate voltage that varies according to the load current is obtained. As a result, the biasing current of the 1st

(11) (12) From (11) and (12), both and Q factor depend on the paand that control the stability of rameters are parasitic related the regulator. It can be observed that poles which can be located at high frequencies easily. From (12), it suggests that the Q factor is inversely proportional to . The largest Q factor happens at full load current is the minimum. To avoid peaking effect where the and or a smaller arising from high Q factor, a larger can be used. In general, it is preferred to choose a larger because it pushes the to a higher frequencies as well. The location of fourth pole is obtained as (13) As indicated in (13), the pole depends on the output capacitance and output resistance. The effective output resistance is inversely proportional to the output load current which will push to higher frequencies as the load current increases. the pole On the other hand, there are also two zeros in the system. They can be derived as follows: (14) (15) The relative poles and zeros position when is illustrated in Fig. 3. The zero is placed slightly beyond the GBW to enhance the phase margin when transconductance is designed to be slightly larger than transconductance . The zero occurs at very high frequency which is even much higher than that of the fourth pole. As such, its effects can be neglected. Table I summaries the poles and zeros locations with pF in 2-stage and 3-stage conguration. Fig. 4 shows the simulated loop gain response of the proposed regulator at different load current conditions. At no load current, the regulator achieves a minimum phase margin of 53 with a low frequency loop gain of 40 dB. When load current raises, the loop gain increases to around 100 dB. The regulator achieves a gain bandwidth product GBW of about 9 MHz with a

1076

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMSI: REGULAR PAPERS, VOL. 60, NO. 4, APRIL 2013

Fig. 4. Simulated open-loop gain at different load currents with

pF.

Fig. 5. Phase margin as a function of load currents.

gain stage can be increased accordingly. The dynamic biasing network stops increasing the biasing current of 1st gain stage when the system transforms into 3-stage mode. It is because the excess current is now supplied by main power transistor . Therefore, the amount of current owing through is more or less xed. Both the sub-power transistor and 2nd gain stage transistor are driven by the output voltage of the dynamic-biased 1st gain stage at node . They can be viewed as a pair of current mirror having a current ratio of 1: M. When the load current is low, the current /M. The transistor is biased

. When , the transistor to source a current of is forced to operate in the triode region. As such, the node potential at is pulled up close to potential that turns the main power transistor off. The pole at node is thus located at high frequency despite of the parasitic capacitances arising from the gate of . Hence, stable operation is guaranteed. When the load current increases gradually at the transition bias point where , the transistor moves out of triode region and starts operating in saturation region. At this juncture, the proposed regulator transforms itself into the 3-stage structure. The 2nd gain stage is activated and the main power transistor starts conducting and supplying the extra required load. The available amount of loop gain increases substantially due to extra gain stage. The threshold current is dened by M, N and . The value of , M and N is 100 nA, 67 and 125, respectively. The calculated is about 837.5 A. However, the simulated is around 200 A. The difference is due to the combined effect of reverse short-channel effect (RSCE) [23], [24] and channel length modulation. In this design, the channel length of the transistor and is 60 nm (60 nm is allowed by the foundry and stated in the design rule) and 500 nm respectively. The extracted threshold voltage of sub-power transistor is 78 mV larger than transistor . Therefore, for a given , the normalized current driving capability of transistor is larger than that of sub-power transistor . Temperature and corner simulations have been conducted to conrm the stability of the proposed LDO regulator. Despite of that, the early activation of main power transistor would not affect the operation and performance of the proposed scheme.

CHONG AND CHAN: QUIESCENT CURRENT OUTPUT-CAPACITORLESS LDO REGULATOR

1077

Fig. 6. Schematic of the proposed LDO regulator.

Fig. 7. Schematic of bias generator and start-up circuit.

Fig. 9. Layout and chip micrograph.

Fig. 8. Simulated load transient response.

B. Overshoot and Undershoot Reduction In general, undershoot and overshoot of the OCL-LDO regulators is larger when compared to the conventional LDO regula-

tors with a large output capacitor. In this design, the undershoot is reduced by employing the dynamic biasing technique introduced in [25]. It has been demonstrated in [25] that dynamic biasing technique yields a smaller undershoot when compared to the xed biasing counterpart. It is because the amount of current that can be used to discharge the parasitic capacitance at the gate of both power transistors is larger. In fact, the dynamic biasing technique helps to reduce the overshoot too. However, the diode-connected feedback network PMOS, which is biased in the subthreshold region, is the only path to discharge the extra current when is switched from full load to no load. The overshoot appears at the output takes a longer time to discharge and recover in transient condition. To suppress the overshoot, a resistor , a capacitor and a transistor form an overshoot reduction network. is a pseudo-resistor realized by a

1078

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMSI: REGULAR PAPERS, VOL. 60, NO. 4, APRIL 2013

Fig. 10. Measured load transient response with mA (d) (c)

V and pF,

V (a) mA.

mA (b)

pF,

mA,

PMOS transistor biased in the cut-off region whereas is a 3 pF MOS capacitor which is realized by a high-voltage native device to save silicon area and prevent the leakage current. This proposed overshoot reduction network is similar to the RC circuits proposed in [5]. However, the overshoot reduction network in our design is directly applied at the output of the LDO regulator which is similar to the amplier design in [26]. In steady state, the current is around 100 nA. When the output load current is switched from heavy to light load, couples the effect to the gate of and it momentarily increases the discharging current from to ground. As a result, the overshoot is suppressed and the transient response is improved. Fig. 8 shows the simulated results of the proposed LDO regulator with and without overshoot reduction. It can be seen that the overshoot is reduced greatly from 93 mV to almost no overshoot. It is worth noting that the small-signal frequency response will not be affected by the proposed overshoot reduction circuitry as is much smaller than . IV. EXPERIMENTAL RESULTS AND DISCUSSIONS The proposed OCL-LDO regulator was designed and fabricated in a UMC 65-nm low-leakage CMOS technology. The layout and microphotograph of the proposed OCL-LDO regulator is shown in Fig. 9. The active area for the proposed design is about 0.017 mm (90 m 190 m). It is able to supply a load current from 0 to 100 mA with an output voltage of 1 V for a supply of 1.2 V. The dropout voltage is less than 200 mV at maximum load current. At no load, the measured quiescent current for the proposed OCL-LDO regulator including the biasing circuit is 0.9 A which is slightly higher than the targeted value of 0.8 A. It is stabilized by a MOS compensation capacitor of 1.5 pF throughout the whole load current range. An external voltage reference of 0.5 V is used and an off-chip capacitor of 100 pF is added at the output to model the for measurement purpose. It should be noted that the system maintains stable as long as the is less than 100 pF. It is because both (5) and

(13) suggest that the non-dominant pole is shifted to higher freis smaller. quencies when The measured load transient responses under different loading conditions are shown in Fig. 10(a)(d) to conrm the stability of the proposed LDO regulator for different testing conditions. The and are set to 1.2 V and 1 V, respectively when doing the load transient measurement. As shown in Fig. 10(a) and (b), the load current is switched between 0 and 100 mA with a rise and fall time of 300 ns. Due to the high GBW contributed by the dynamic biasing scheme and the employment of overshoot reduction circuitry, there is no obvious overshoot when load current is switched from 100 mA to 0. On the other hand, the maximum undershoot for and 100 pF is 65.1 mV and 68.8 mV, respectively. This is due to the low quiescent current of 0.9 A at no load current condition. The maximum output voltage variation is less than 7% (68.8 mV/1 V) and is able to settle to its nal value in 6 s. Fig. 10(c) and (d) depict the measured load transient responses when the load current is switched from 1 mA and 10 mA to 100 mA, respectively, with an edge time of 300 ns as well. It is shown that the measured undershoot is reduced to 36.9 mV and 24.4 mV, respectively. The improvement is due to the fact that the 1st gain stage has larger biasing current and the main power transistor has been activated. The measured load transient response conrms that the proposed OCL-LDO regulator is stable for whole range of load current. Fig. 11 shows the measured and estimated load regulation of the proposed work. The voltage drops at high load condition is due to the parasitic resistance of the bonding wire which is around 250 m in our packaging. The voltage drops across the bonding wire can be as large as 25 mV when mA. In order to estimate the actual load regulation, the IR drop due to the bonding resistance is excluded and plotted in Fig. 11 for comparison. The line transient response is shown in Fig. 12. The supply voltage changes between 1 V and 1.2 V in 10 s with an output

CHONG AND CHAN: QUIESCENT CURRENT OUTPUT-CAPACITORLESS LDO REGULATOR

1079

Fig. 11. Measured and estimated load regulation with

pF. Fig. 13. Dropout voltage as a function of load currents.

Fig. 12. Measured line transient response at

and

V.

voltage of 0.8 V and . The result shows that the maximum voltage spike is only 10.63 mV. It is interesting to observe an overshoot at when is switched from 1.2 V to 1 V. The overshoot is caused by the residue charges at the gate of when is switched from 1 V to 1.2 V. Fig. 13 shows the measured dropout voltage across the load current. The measured result shows that the dropout voltage is less than 200 mV when mA. Finally, the measured PSR at load current of 100 mA, V, V and pF is shown in Fig. 14. The PSR is measured by using a network analyzer (HP 4395A) and a high impedance active probe (HP 41800A). The proposed OCL-LDO regulator has achieved a PSR of dB at 10 kHz. Furthermore, a 50 kHz sinusoidal waveform is applied to the input of the LDO regulator. The measured result is depicted in Fig. 15. Fig. 16 shows the measured versus . As can be observed, keeps increasing until is about 200 A where the 2nd stage start working in saturation and the main power transistor start to conduct. It can be observed that, due to channel length modulation effect, increases slightly after A. At full load condition, the proposed regulator draws a maximum current of 82.4 A and achieves a current efciency of larger than 99.9%. The measured performance of the proposed regulator is compared to the state-of-the-art works in Table II. The transient gure-of-merit (FOM) for OCL-LDO regulator in [7] is adopted for comparison. It is given by (16)

Fig. 14. Measured PSR at

V,

V and

mA.

Fig. 15. Measured ripple-response at mA.

V,

V and

where the symbols have their usual meanings. K is the edge time ratio and dened by

(17) The smaller FOM value, the better is the transient performance metric. The proposed design achieves the smallest OCL-LDO FOM value among the recently reported works. With the adaptive gain circuit architecture, dynamic biasing

1080

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMSI: REGULAR PAPERS, VOL. 60, NO. 4, APRIL 2013

TABLE II PERFORMANCE COMPARISON WITH REPORTED PRIOR-ART OCL-LDO REGULATORS

only 0.9 A at no load condition and enhances the current efciency at light load. At moderate and heavy loading condition, the performance is enhanced by additional gain stage. The proposed OCL-LDO regulator has been implemented and veried experimentally. Compared to the prior-art works, the proposed LDO regulator achieves a better quiescent current, transient performance metrics. It also offers good performance parameters in terms of PSR, line regulation and load regulation. Finally, it also achieves the smallest transient FOM value dedicated for OCL-LDO regulator, suggesting the effectiveness of the proposed scheme. The proposed work will be useful in on-chip applications using nanometer CMOS technologies. ACKNOWLEDGMENT The authors would like to thank MediaTek, Singapore for the sponsorship of the chip fabrication. REFERENCES

[1] D. D. Buss, Technology in the internet age, in Proc. ISSCC Dig. Tech. Papers, Feb. 2002, pp. 1821. [2] G. A. Rincon-Mora and P. E. Allen, A low-voltage, low-quiescent current, low drop-out regulator, IEEE J. Solid-State Circuits, vol. 33, no. 1, pp. 3644, Jan. 1998. [3] M. Al-Shyoukh, H. Lee, and R. Perez, A transient-enhanced low-quiescent current low-dropout regulator with buffer impedance attenuation, IEEE J. Solid-State Circuits, vol. 42, no. 8, pp. 17321742, Aug. 2007. [4] Y. H. Lam and W. H. Ki, A 0.9 V 0.35 m adaptively biased CMOS LDO regulator with fast transient response, in Proc. ISSCC Dig. Tech. Papers, Feb. 2008, pp. 442443. [5] K. N. Leung and Y. S. Ng, A CMOS low-dropout regulator with a momentarily current-boosting voltage buffer, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 9, pp. 23122319, Sep. 2010. [6] M. Ho, K. N. Leung, and K. L. Mak, A low-power fast-transient 90-nm low-dropout regulator with multiple small-gain stages, IEEE J. Solid-State Circuits, vol. 45, pp. 24662476, Nov. 2010. [7] J. Guo and K. N. Leung, A 6- W chip-area-efcient output-capacitorless LDO in 90-nm CMOS technology, IEEE J. Solid-State Circuits, vol. 45, no. 9, pp. 18961905, Sep. 2010. [8] P. Hazucha et al., Area-efcient linear regulator with ultra-fast load regulation, IEEE J. Solid-State Circuits, vol. 40, no. 4, pp. 933940, Apr. 2005.

Fig. 16. Measured quiescent current as a function of load currents.

scheme and overshoot reduction circuitry, the transient performance at ultra-low quiescent current is comparable to the counterparts biased at much higher quiescent values. Finally, other performance parameters such as PSR, line regulation and load regulation have achieved reasonable good values. V. CONCLUSION An ultra-low quiescent current OCL-LDO regulator with adaptive power transistors technique in 65-nm low-leakage CMOS process has been presented. With the proposed technique and circuit architecture, the OCL-LDO regulator achieves full range stability from 0 to 100 mA without the need of minimum loading current requirement. In addition, it consumes

CHONG AND CHAN: QUIESCENT CURRENT OUTPUT-CAPACITORLESS LDO REGULATOR

1081

[9] R. J. Milliken, J. Silva-Martinez, and E. Snchez-Sinencio, Full-onchip CMOS low-dropout voltage regulator, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 54, no. 9, pp. 18791890, Sep. 2007. [10] E. N. Y. Ho and P. K. T. Mok, A capacitor-less CMOS active feedback low-dropout regulator with slew-rate enhancement for portable on-chip application, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 57, no. 2, pp. 8084, Feb. 2010. [11] T. Y. Man, K. N. Leung, C. Y. Leung, P. K. T. Mok, and M. Chan, Development of single-transistor-control LDO based on ipped voltage follower for SoC, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 5, pp. 13921401, Jun. 2008. [12] P. Y. Or and K. N. Leung, An output-capacitorless low-dropout regulator with direct voltage-spike detection, IEEE J. Solid-State Circuits, vol. 45, no. 2, pp. 458466, Feb. 2010. [13] K. N. Leung and P. K. T. Mok, A capacitor-free CMOS low dropout regulator with damping-factor-control frequency compensation, IEEE J. Solid-State Circuits, vol. 38, no. 10, pp. 16911702, Oct. 2003. [14] S. K. Lau, P. K. T. Mok, and K. N. Leung, A low-dropout regulator for SoC with Q-reduction, IEEE J. Solid-State Circuits, vol. 2, no. 3, pp. 658664, Mar. 2007. [15] Y. S. Hwang, M. S. Lin, B. H. Hwang, and J. J. Chen, A 0.35 m CMOS sub-1 V low-quiescent-current low-dropout regulator, in Proc. Asian Solid-State Circuits Conf. (A-SSCC), Nov. 35, 2008, pp. 153156. [16] M. Ho and K. N. Leung, Dynamic bias-current boosting technique for ultralow-power low-dropout regulator in biomedical applications, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 58, no. 3, pp. 174178, Mar. 2011. [17] C. M. Chen and C. C. Hung, A fast self-reacting capacitor-less lowdropout regulator, in Proc. Eur. Solid-State Circuits Conf. (ESSCIRC), Sep. 1216, 2011, pp. 375378. [18] B. Ahuja, An improved frequency compensation technique for CMOS operational ampliers, IEEE J. Solid-State Circuits, vol. SC-18, pp. 629633, Dec. 1983. [19] R. Reay and G. Kovacs, An unconditionally stable two-stage CMOS amplier, IEEE J. Solid-State Circuits, vol. 30, no. 5, pp. 591594, May 1995. [20] D. B. Ribner and M. A. Copeland, Design techniques for cascaded CMOS op amps with improved PSRR and common-mode input range, IEEE J. Solid-State Circuits, vol. SC-19, no. 12, pp. 919925, Dec. 1984. [21] C. J. Cheng, C. J. Wu, and S. Y. Lee, A programmable pacing channel with a fully on-chip regulator for cardiac pacemaker, in Proc. Asian Solid-State Circuits Conf. (A-SSCC), Nov. 35, 2008, pp. 285288. [22] S. Mandal, S. Arn, and R. Sarpeshkar, Fast startup CMOS current references, in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2006, pp. 28442848. [23] C. Y. Lu and J. M. Sung, Reverse short-channel effects on threshold voltage in submicrometer salicide devices, IEEE Electron Device Lett., vol. 10, no. 10, pp. 446448, Oct. 1989. [24] C. Subramanian, Reverse short channel effect and channel length dependence of boron penetration in PMOSFETs, in Proc. Int. Electron Device Meeting, Dec. 1995, pp. 423426.

[25] C. Zhang and W. H. Ki, Output-capacitor-free adaptively biased lowdropout regulator for system-on-chips, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 5, pp. 10171028, May 2010. [26] J. Ramirez-Augulo, R. G. Carvajal, J. A. Galan, and A. Lopez-Martin, A free but efcient low-voltage class-AB two-stage operational amplier, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 7, pp. 568571, Jul. 2006.

Sau Siong Chong was born in Malaysia. He received the B.Eng. (hons.) degree from Nanyang Technological University (NTU), Singapore, in 2009, where he is currently working towards the Ph.D. degree in School of Electrical and Electronic Engineering. His research interests include design of analog integrated circuits and frequency compensation techniques for low-voltage low-power multistage ampliers and low-dropout regulators.

Pak Kwong Chan was born in Hong Kong. He received the B.Sc. (hons.) degree from the University of Essex, Colchester, U.K., in 1987, the M.Sc. degree from the University of Manchester, Institute of Science and Technology (U.M.I.S.T.), Manchester, U.K., in 1988, and the Ph.D. degree from the University of Plymouth, U.K. in 1992. From 1989 to 1992, he was a Research Assistant with the University of Plymouth, working in the area of MOS continuous-time lters. In 1993, he joined the Institute of Microelectronics (IME), Singapore as a Member Technical Staff, where he designed high-performance analog/mixedsignal circuits for integrated systems and CMOS sensor interfaces for industrial applications. In 1996, He was a Staff Engineer with Motorola, Singapore where he developed the magnetic write channel for Motorola 1st generation hard-disk preamplier. He joined Nanyang Technological University (NTU), Singapore in 1997, where he is an Associate Professor in the School of Electrical and Electronic Engineering. He served the Program Director (analog/mixed-signal IC and applications) for the Center for Integrated Circuits and Systems (CICS) from 2003 to 2010. He has also conducted numerous IC design short courses to the IC companies and design centers. He is the Program Manager for Advanced Technology IC Shuttle Program between NTU and MediaTek, Singapore. He serves as a Guest Editor for several Special Issues on recent research topics. His research interests include sensor circuits and systems, mixed-mode circuits and systems, precision analog circuits, ultra low-voltage low-power analog circuits as well as power management IC for integrated sensors and system-on-chip.

Das könnte Ihnen auch gefallen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Experiments in Principles of Electronic Devices and Circuits (PDFDrive)Dokument321 SeitenExperiments in Principles of Electronic Devices and Circuits (PDFDrive)Ralph Jason Alvarez100% (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- Design of Analog CMOS Integrated Circuits (Behzad Razavi) MarcadoDokument706 SeitenDesign of Analog CMOS Integrated Circuits (Behzad Razavi) MarcadoAminAbed100% (4)

- UAE University Electric Circuits Chapter SummaryDokument362 SeitenUAE University Electric Circuits Chapter SummaryPattem KedarnathNoch keine Bewertungen

- Switched Mode Power SupplyDokument153 SeitenSwitched Mode Power SupplyIvan222244Noch keine Bewertungen

- 1000w Inverter PURE SINE WAVE Schematic DiagramDokument153 Seiten1000w Inverter PURE SINE WAVE Schematic Diagramjeevapillay100% (4)

- Analog IC Design With Low-Dropout RegulatorsDokument374 SeitenAnalog IC Design With Low-Dropout Regulatorsberbou100% (2)

- Semiconductor Manufacturing AustriamicrosystemsDokument47 SeitenSemiconductor Manufacturing Austriamicrosystemsmikeshinoda20110% (1)

- High-Efficiency Hybrid Resonant Converter for Wide PV Input RegulationDokument76 SeitenHigh-Efficiency Hybrid Resonant Converter for Wide PV Input RegulationVINAYNoch keine Bewertungen

- Analog Circuit Design Volume Three: Design Note CollectionVon EverandAnalog Circuit Design Volume Three: Design Note CollectionBewertung: 3 von 5 Sternen3/5 (2)

- Two-Stage Micro-Grid Inverter With High PDFDokument10 SeitenTwo-Stage Micro-Grid Inverter With High PDFacostaricciNoch keine Bewertungen

- Ee - Module 3 - April 2012Dokument3 SeitenEe - Module 3 - April 2012Znevba Quintano100% (2)

- Compact Models For Future Generation CMOSDokument170 SeitenCompact Models For Future Generation CMOSmikeshinoda2011Noch keine Bewertungen

- BuckConverter Design Jpe10Dokument13 SeitenBuckConverter Design Jpe10joviflocasNoch keine Bewertungen

- Power Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesVon EverandPower Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesNoch keine Bewertungen

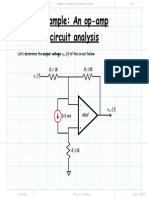

- Example An Op Amp Circuit Analysis LectureDokument23 SeitenExample An Op Amp Circuit Analysis LectureAthiyo MartinNoch keine Bewertungen

- Design and Analysis of Low Voltage Low Dropout RegulatorDokument4 SeitenDesign and Analysis of Low Voltage Low Dropout RegulatorIJSTENoch keine Bewertungen

- ThesisDokument75 SeitenThesishodeegits9526Noch keine Bewertungen

- Capacitor Less LdoDokument11 SeitenCapacitor Less LdoantharmukiNoch keine Bewertungen

- Current Source InverterDokument16 SeitenCurrent Source Inverterjp-sharma100% (1)

- Design of Cmos Low Drop-Out Regulators: A Comparative Study: Ashvani Kumar Mishra, Rishikesh PandeyDokument7 SeitenDesign of Cmos Low Drop-Out Regulators: A Comparative Study: Ashvani Kumar Mishra, Rishikesh PandeyrahmanakberNoch keine Bewertungen

- Full On-Chip CMOS Low-Dropout Voltage RegulatorDokument12 SeitenFull On-Chip CMOS Low-Dropout Voltage RegulatorashishmanyanNoch keine Bewertungen

- IET Power Electronics Volume 4 Issue 9 2011 [Doi 10.1049_iet-Pel.2010.0363] Jung, J.-h.; Ahmed, S. -- Flyback Converter With Novel Active Clamp Control and Secondary Side Post Regulator for Low Standby Power Consumption Under HighDokument10 SeitenIET Power Electronics Volume 4 Issue 9 2011 [Doi 10.1049_iet-Pel.2010.0363] Jung, J.-h.; Ahmed, S. -- Flyback Converter With Novel Active Clamp Control and Secondary Side Post Regulator for Low Standby Power Consumption Under HighTuấn Anh PhạmNoch keine Bewertungen

- Capless LDO DESIGNDokument6 SeitenCapless LDO DESIGNbhasin_hemantNoch keine Bewertungen

- A 6-UW Chip-Area-Efficient Output-Capacitorless LDO in 90-Nm CMOS TechnologyDokument10 SeitenA 6-UW Chip-Area-Efficient Output-Capacitorless LDO in 90-Nm CMOS Technology孙士祯Noch keine Bewertungen

- Capacitor Less Ldo ThesisDokument4 SeitenCapacitor Less Ldo Thesisevelyndonaldsonbridgeport100% (2)

- Self-calibrating output-capacitor-free LDO with wide range and fast responseDokument12 SeitenSelf-calibrating output-capacitor-free LDO with wide range and fast responseVani YamaniNoch keine Bewertungen

- Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial ApplicationsDokument14 SeitenWide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applicationsstrngr06Noch keine Bewertungen

- A Capacitor-Free CMOS Low-Dropout Regulator With Damping-Factor-Control Frequency CompensationDokument12 SeitenA Capacitor-Free CMOS Low-Dropout Regulator With Damping-Factor-Control Frequency Compensationtotoya38Noch keine Bewertungen

- Capacitorless LDO Voltage RegulatorsDokument14 SeitenCapacitorless LDO Voltage Regulatorsd_nikuNoch keine Bewertungen

- LDO Voltage Regulator by Sanjay Singh NIT KKRDokument9 SeitenLDO Voltage Regulator by Sanjay Singh NIT KKRSanjay SinghNoch keine Bewertungen

- Project ReportDokument37 SeitenProject ReportAmit SinghNoch keine Bewertungen

- Investigating Buck Converter With Hybrid LDO Mode For Improved Low-Load OperationDokument4 SeitenInvestigating Buck Converter With Hybrid LDO Mode For Improved Low-Load OperationInternational Journal of Innovative Science and Research TechnologyNoch keine Bewertungen

- A Low-Power and High-Speed Voltage Level Shifter Based On A Regulated Cross-Coupled Pull-Up NetworkDokument5 SeitenA Low-Power and High-Speed Voltage Level Shifter Based On A Regulated Cross-Coupled Pull-Up Network15022000rskushalNoch keine Bewertungen

- ARCP Converter Enables Soft Switching Without Increased Device RatingsDokument8 SeitenARCP Converter Enables Soft Switching Without Increased Device RatingsAjit JainNoch keine Bewertungen

- Modified SEPIC Converter Literature ReviewDokument55 SeitenModified SEPIC Converter Literature ReviewHEERAVATHINoch keine Bewertungen

- Cascade Controller For DCDC Buck ConvertorDokument6 SeitenCascade Controller For DCDC Buck ConvertorCristóbal Eduardo Carreño MosqueiraNoch keine Bewertungen

- IEEE POWER ELECTRONICS 2015 Matlab Projectlist Mtech BeDokument4 SeitenIEEE POWER ELECTRONICS 2015 Matlab Projectlist Mtech BeKumar RajNoch keine Bewertungen

- (Doi 10.1109/TPEL.2014.2310731) J. Galvez M. Ordonez - Swinging Bus Operation of Inverters For Fuel Cell Applications With Small DC-Link CapacitanceDokument12 Seiten(Doi 10.1109/TPEL.2014.2310731) J. Galvez M. Ordonez - Swinging Bus Operation of Inverters For Fuel Cell Applications With Small DC-Link Capacitancesk.karimeeeNoch keine Bewertungen

- High-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniqueDokument9 SeitenHigh-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniquekerblaNoch keine Bewertungen

- Heavy Load Light Load Conversion ReportDokument41 SeitenHeavy Load Light Load Conversion ReportSanjivee SachinNoch keine Bewertungen

- Solid State Tap Changer PresentationDokument17 SeitenSolid State Tap Changer PresentationSujit GangurdeNoch keine Bewertungen

- Ultra-Low Quiescent Current CMOS LDO with Small Output VariationsDokument6 SeitenUltra-Low Quiescent Current CMOS LDO with Small Output VariationsMehanathan Maggie MikeyNoch keine Bewertungen

- Topic Assignment14Dokument6 SeitenTopic Assignment14cuongakamarineNoch keine Bewertungen

- Design and Optimization of On-Chip Voltage Regulators For High Performance ApplicationsDokument4 SeitenDesign and Optimization of On-Chip Voltage Regulators For High Performance ApplicationsBaluvu JagadishNoch keine Bewertungen

- IpcDokument4 SeitenIpcdbircs.wwwNoch keine Bewertungen

- A High Slew-Rate Push-Pull Output Amplifier For Low-Quiescent Current Low-Dropout Regulators With Transient-Response ImprovementDokument5 SeitenA High Slew-Rate Push-Pull Output Amplifier For Low-Quiescent Current Low-Dropout Regulators With Transient-Response ImprovementsonofalexanderNoch keine Bewertungen

- Integrated Current Balancing Transformer Based Input-Parallel Output-Parallel LLC Resonant Converter ModulesDokument8 SeitenIntegrated Current Balancing Transformer Based Input-Parallel Output-Parallel LLC Resonant Converter ModulesSh M AaqibNoch keine Bewertungen

- Single-Ended High-Efficiency Step-Up Converter Using The Isolated Switched-Capacitor CellDokument13 SeitenSingle-Ended High-Efficiency Step-Up Converter Using The Isolated Switched-Capacitor CellHarjinder SinghNoch keine Bewertungen

- SHORT CIRCUIT CURRENT LIMITATION TECHNIQUESDokument13 SeitenSHORT CIRCUIT CURRENT LIMITATION TECHNIQUESariefNoch keine Bewertungen

- A Low-Voltage, Low Quiescent Current, Low Drop-Out RegulatorDokument9 SeitenA Low-Voltage, Low Quiescent Current, Low Drop-Out RegulatorVinayNoch keine Bewertungen

- Designing PFC and PSFB Stages for EV Battery ChargersDokument5 SeitenDesigning PFC and PSFB Stages for EV Battery ChargersThien DinhNoch keine Bewertungen

- Sursa 200W, 470kHzDokument67 SeitenSursa 200W, 470kHzv_costelNoch keine Bewertungen

- High-speed voltage follower designDokument2 SeitenHigh-speed voltage follower designfatyfroisNoch keine Bewertungen

- New resonant DC link converter concept for static power conversionDokument9 SeitenNew resonant DC link converter concept for static power conversionSenthil KumarNoch keine Bewertungen

- Series Reactors in CLP NetworkDokument5 SeitenSeries Reactors in CLP NetworkAmberMeerabNoch keine Bewertungen

- An Out-Put Cap Free Adaptively Biased LDO PDFDokument13 SeitenAn Out-Put Cap Free Adaptively Biased LDO PDF孙士祯Noch keine Bewertungen

- Design Analysis of Low Drop-Out Voltage Regulator With Current Buffer CompensationDokument5 SeitenDesign Analysis of Low Drop-Out Voltage Regulator With Current Buffer Compensationkhang npNoch keine Bewertungen

- 9.eee Ijeee Two Phase Interleaved DC SumalathaDokument16 Seiten9.eee Ijeee Two Phase Interleaved DC Sumalathaiaset123Noch keine Bewertungen

- Fix3 33333333Dokument4 SeitenFix3 33333333doanminhtien030903Noch keine Bewertungen

- 2008 Yin Man Development of Single-Transistor-Control LDO PDFDokument10 Seiten2008 Yin Man Development of Single-Transistor-Control LDO PDFrahmanakberNoch keine Bewertungen

- A Fold-Back Current Limit Circuit With Load-Insensitive Quiescent Current For CMOS Low Dropout RegulatorDokument4 SeitenA Fold-Back Current Limit Circuit With Load-Insensitive Quiescent Current For CMOS Low Dropout Regulatorhjtseng1974Noch keine Bewertungen

- Analysis, Design, and Implementation of A High-Efficiency Full-Wave Rectifier in Standard CMOS TechnologyDokument11 SeitenAnalysis, Design, and Implementation of A High-Efficiency Full-Wave Rectifier in Standard CMOS TechnologymohsinmanzoorNoch keine Bewertungen

- 5 - 2015 ITRS 2.0 - More MooreDokument21 Seiten5 - 2015 ITRS 2.0 - More Mooremikeshinoda2011Noch keine Bewertungen

- 5 - 2015 ITRS 2.0 - More MooreDokument52 Seiten5 - 2015 ITRS 2.0 - More Mooremikeshinoda2011Noch keine Bewertungen

- 5 - 2015 ITRS 2.0 - More MooreDokument52 Seiten5 - 2015 ITRS 2.0 - More Mooremikeshinoda2011Noch keine Bewertungen

- MbanDokument74 SeitenMbanmikeshinoda2011Noch keine Bewertungen

- 7 - 2015 ITRS 2.0 Factory Integration PDFDokument80 Seiten7 - 2015 ITRS 2.0 Factory Integration PDFmikeshinoda2011Noch keine Bewertungen

- All-In-One Energy Harvesting and Storage DevicesDokument19 SeitenAll-In-One Energy Harvesting and Storage Devicesmikeshinoda2011Noch keine Bewertungen

- AtcpanDokument18 SeitenAtcpanmikeshinoda2011Noch keine Bewertungen

- 607 Lect 12 LDODokument58 Seiten607 Lect 12 LDOmikeshinoda2011Noch keine Bewertungen

- DvugDokument158 SeitenDvugmikeshinoda2011Noch keine Bewertungen

- ME1000 RF Circuit Design Lab 4 Filter Characterization Using Vector Network AnalyzerDokument6 SeitenME1000 RF Circuit Design Lab 4 Filter Characterization Using Vector Network Analyzermikeshinoda2011Noch keine Bewertungen

- ADC Performance Survey 1997-2015 Trends and LimitsDokument72 SeitenADC Performance Survey 1997-2015 Trends and Limitsmikeshinoda2011Noch keine Bewertungen

- High-Speed Digital Test & Measurement: Chris Allen (Callen@eecs - Ku.edu)Dokument21 SeitenHigh-Speed Digital Test & Measurement: Chris Allen (Callen@eecs - Ku.edu)mikeshinoda2011Noch keine Bewertungen

- 3D Low Frequency Wakeup Receiver: General DescriptionDokument49 Seiten3D Low Frequency Wakeup Receiver: General Descriptionmikeshinoda2011Noch keine Bewertungen

- Thesis Younis SOE PDFDokument123 SeitenThesis Younis SOE PDFmikeshinoda2011Noch keine Bewertungen

- ASEE - Thermoelectric Paper - FinalDokument12 SeitenASEE - Thermoelectric Paper - FinalmasakpNoch keine Bewertungen

- BSIM470 Manual PDFDokument184 SeitenBSIM470 Manual PDFmikeshinoda2011Noch keine Bewertungen

- Fourier 94Dokument9 SeitenFourier 94mikeshinoda2011Noch keine Bewertungen

- Ch6 7 ProblemsDokument82 SeitenCh6 7 Problemsmikeshinoda2011Noch keine Bewertungen

- AmsdmvDokument176 SeitenAmsdmvmikeshinoda2011Noch keine Bewertungen

- 1 and 2 Printings: MOS Transistor, 3d EditionDokument2 Seiten1 and 2 Printings: MOS Transistor, 3d Editionmikeshinoda2011Noch keine Bewertungen

- Voltage Regulator PDFDokument6 SeitenVoltage Regulator PDFSai KrishnaNoch keine Bewertungen

- Patent LeungDokument11 SeitenPatent Leungmikeshinoda2011Noch keine Bewertungen

- 93XX Series RTC Battery PDFDokument17 Seiten93XX Series RTC Battery PDFmikeshinoda2011Noch keine Bewertungen

- b16396 8Dokument32 Seitenb16396 8mikeshinoda2011Noch keine Bewertungen

- 120-08 Telemetry (TM) Radio Frequency (RF) HandbookDokument133 Seiten120-08 Telemetry (TM) Radio Frequency (RF) Handbookviveknarula295382Noch keine Bewertungen

- Modeling RF SystemsDokument41 SeitenModeling RF Systemsmikeshinoda2011Noch keine Bewertungen

- The Experimental Researches of Michael FaradayDokument368 SeitenThe Experimental Researches of Michael Faradaygazorninplotz100% (1)

- Sverker 760Dokument6 SeitenSverker 760Junior Ramirez ReyesNoch keine Bewertungen

- ProtectionDokument53 SeitenProtectionsantoshkumar100% (1)

- EE809: Analog Integrated Circuit Design: Week-4 4 - 8 Oct 2021Dokument24 SeitenEE809: Analog Integrated Circuit Design: Week-4 4 - 8 Oct 2021Muhammad FaizanNoch keine Bewertungen

- Back-to-Back Accelerometer CalibrationDokument3 SeitenBack-to-Back Accelerometer CalibrationAekDzLaiNoch keine Bewertungen

- Description Features: Ait Semiconductor IncDokument10 SeitenDescription Features: Ait Semiconductor IncMaktum KamatNoch keine Bewertungen

- AN10009 Differential Terminations Rev1.2Dokument18 SeitenAN10009 Differential Terminations Rev1.2eppramod3271Noch keine Bewertungen

- Electrical CircuitsDokument89 SeitenElectrical CircuitsManyam KummariNoch keine Bewertungen

- Network Theorems: Publishing As Pearson (Imprint) BoylestadDokument117 SeitenNetwork Theorems: Publishing As Pearson (Imprint) BoylestadMarion John OngNoch keine Bewertungen

- 博士班資格考 電子學題庫Dokument15 Seiten博士班資格考 電子學題庫Adil KhanNoch keine Bewertungen

- MOSFET Biasing TechniquesDokument33 SeitenMOSFET Biasing TechniquesKesani Venkat Narsimha ReddyNoch keine Bewertungen

- Pulse Oximeter DesignDokument31 SeitenPulse Oximeter DesignPraba KaranNoch keine Bewertungen

- Understanding Current Control Snva555Dokument30 SeitenUnderstanding Current Control Snva555boteem20070% (1)

- Erno Borbely Fet Articel 2Dokument5 SeitenErno Borbely Fet Articel 2Srdjan ProkicNoch keine Bewertungen

- Norton's Theorem ExplainedDokument19 SeitenNorton's Theorem ExplainedVedashree ShetyeNoch keine Bewertungen

- Network Filters Transmission LinesDokument11 SeitenNetwork Filters Transmission Linesmaacpie8353Noch keine Bewertungen

- CSI and VSI (ch-1) DifferenceDokument9 SeitenCSI and VSI (ch-1) DifferenceGoud SannyNoch keine Bewertungen

- TB62747AFG ToshibaDokument20 SeitenTB62747AFG ToshibavinNoch keine Bewertungen

- Norton's Theorem: Experiment No.7Dokument5 SeitenNorton's Theorem: Experiment No.7Abera DeressaNoch keine Bewertungen

- Slides - 17 - CH 18 - Network Theorems (Ac) - Updated - 2Dokument59 SeitenSlides - 17 - CH 18 - Network Theorems (Ac) - Updated - 2Tamim ANoch keine Bewertungen

- Electrical ElectronicsDokument92 SeitenElectrical ElectronicstechNoch keine Bewertungen

- Phase-Controlled Converter: ObjectivesDokument8 SeitenPhase-Controlled Converter: Objectiveskafle_yrsNoch keine Bewertungen

- Input-controlled Buck Converter Modeling for Photovoltaic ApplicationsDokument5 SeitenInput-controlled Buck Converter Modeling for Photovoltaic ApplicationsIlva Leandro ElenaNoch keine Bewertungen

- Power Electronics For RenewablesDokument22 SeitenPower Electronics For RenewablesShiv Prakash M.Tech., Electrical Engineering, IIT(BHU)Noch keine Bewertungen

- IEEE Journal Article Summary: A 10-b, 500-MSample/s CMOS DACDokument11 SeitenIEEE Journal Article Summary: A 10-b, 500-MSample/s CMOS DACBhavin DesaiNoch keine Bewertungen

![IET Power Electronics Volume 4 Issue 9 2011 [Doi 10.1049_iet-Pel.2010.0363] Jung, J.-h.; Ahmed, S. -- Flyback Converter With Novel Active Clamp Control and Secondary Side Post Regulator for Low Standby Power Consumption Under High](https://imgv2-2-f.scribdassets.com/img/document/220209509/149x198/8baf096670/1429428106?v=1)