Beruflich Dokumente

Kultur Dokumente

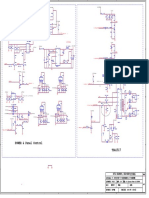

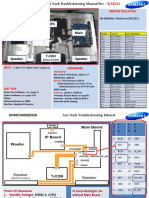

Schematic Diagram Overview

Hochgeladen von

alfredo_izquierdo_12Originalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Schematic Diagram Overview

Hochgeladen von

alfredo_izquierdo_12Copyright:

Verfügbare Formate

Schematic Diagram

7. Schematic Diagram

7-1 Circuit Description

Logic Board Y Main Board X Main Board PDP Panel

42 - 1024x768 Pixels 1024x768x3 Cells (R,G,B) 50 - 1365x768 Pixels 1365x768x3 Cells (R,G,B)

DRAM Input Data Processor Data Controller Driver Timing Controller

Display Data Display Timing Scan Timing

Row Driver

Y-Pulse Generator

X-Pulse Generator

Address Buffer

SMPS Board

LVDS

Main SMPS

Main Board

LVDS Trans Image Scaler TMDS Recever

Image Enhancer CPU Decoder A/D Converter

Deinterlacer Video Decoder Video S/W

Audio Processor Speaker Out Micom

Tuner

AC Power Source

SMPS Board The SMPS used for the PDP has been designed to be efficient, compact and lightweight. For VS and VA outputs, a LLC converter has been used. For the other outputs, a Flyback converter has been used. LOGIC Board The logic circuit consists of a Logic Main Board and an Address Buffer Board. The Logic Main Board decodes the video signal encoded by the Video Board, outputs the ADDRESS data signal for each pattern and generates X and Y drive signals. The Address Buffer Board buffers and transfers the ADDRESS data output signal using TCP IC. - LVDS with built-in video signal processing (W/L, error diffusion, APC, FCR, etc.) applied and 1 ASIC chip. - Outputs the address Drive IC control and data signals to the Buffer Board. - Outputs the control signal for the X and Y Drive Boards. - Monitors major drive voltages (Micom Circuit Block); detects if a surge voltage has been applied and protects the Drive Circuit. - Temperature Adaptive Operating Mode (Low Temperature/Room Temperature/High Temperature); Discharge optimization for each temperature level. X-MAIN Board Connects to the X terminal block, 1) provides maintaining voltage waveform (including ERC), and 2) maintains the Ve bias in the Scan section. Y-MAIN Board Connects to the Y terminal block, 1) provides maintaining voltage waveform (including ERC), 2) provides Y Rising, Falling Ramp waveforms, and 3) maintains the Vscan bias. Address Buffer Board It delivers the data signal and control signal to the TCP. Samsung Electronics 7-1

MEMO

7-2

Samsung Electronics

Schematic Diagram

7-2 Schematic Diagram

7-2-1 Power

This Document can not be used without Samsungs authorization.

Power

Samsung Electronics

7-3

Schematic Diagram

7-2-2 Sound Processing

This Document can not be used without Samsungs authorization.

Power

Samsung Electronics

7-4

Schematic Diagram

7-2-3 Input & Output Jack I

This Document can not be used without Samsungs authorization.

Power

7-5

Samsung Electronics

Schematic Diagram

7-2-4 Input & Output Jack II

This Document can not be used without Samsungs authorization.

Power

Samsung Electronics

7-6

Schematic Diagram

7-2-5 MICOM

This Document can not be used without Samsungs authorization.

Power

7-7

Samsung Electronics

Schematic Diagram

7-2-6 SVP-UX (Scaler)

This Document can not be used without Samsungs authorization.

Power

Samsung Electronics

7-8

Schematic Diagram

7-2-7 DDR & Tuner

This Document can not be used without Samsungs authorization.

Power

7-9

Samsung Electronics

Schematic Diagram

7-2-8 DTV Reset & AV out

This Document can not be used without Samsungs authorization.

Power

Samsung Electronics

7-10

Schematic Diagram

7-2-9 DTV Memory & STi5105

This Document can not be used without Samsungs authorization.

Power

7-11

Samsung Electronics

Schematic Diagram

7-2-10 PCMCIA & STi5105

This Document can not be used without Samsungs authorization.

Power

Samsung Electronics

7-12

Das könnte Ihnen auch gefallen

- Pdf 文件使用 "Pdffactory Pro" 试用版本创建 Ÿÿ: Tsumv26KuDokument1 SeitePdf 文件使用 "Pdffactory Pro" 试用版本创建 Ÿÿ: Tsumv26KuVladimir SazanovecNoch keine Bewertungen

- 14mt2ad2da V2.0.0Dokument1 Seite14mt2ad2da V2.0.0Bryan Felton100% (1)

- Sanyo DCG-105 Sistema Audio CD-MP3 Manual SimpleDokument11 SeitenSanyo DCG-105 Sistema Audio CD-MP3 Manual Simplecharly36Noch keine Bewertungen

- Schematic Ktc-Cbu 24 VCMDokument4 SeitenSchematic Ktc-Cbu 24 VCMMarco Kersul100% (1)

- Linear Integrated Circuits Course Outline PDFDokument49 SeitenLinear Integrated Circuits Course Outline PDFSarvjeet Singh SohalNoch keine Bewertungen

- ElectronicsDokument29 SeitenElectronicsfineautumnNoch keine Bewertungen

- Philips 40pfl3505df7 Chassis Pl10 5Dokument87 SeitenPhilips 40pfl3505df7 Chassis Pl10 5latino52Noch keine Bewertungen

- An Overview of Switched-Mode Power Supplies: Integrated CircuitsDokument6 SeitenAn Overview of Switched-Mode Power Supplies: Integrated CircuitsJohn Wanyoike MakauNoch keine Bewertungen

- 5635.under The Hood of Flyback SMPS DesignsDokument41 Seiten5635.under The Hood of Flyback SMPS DesignsAntochi CiprianNoch keine Bewertungen

- 5 Current Mode Control ModelingDokument12 Seiten5 Current Mode Control ModelingzmrbillNoch keine Bewertungen

- Daewood Hc6120uDokument40 SeitenDaewood Hc6120uAna Six100% (1)

- Switching Power Supply CalculationsDokument4 SeitenSwitching Power Supply CalculationsEdilson TavaresNoch keine Bewertungen

- 32 MicroprocessorsDokument3 Seiten32 MicroprocessorsTilak Raj100% (1)

- EE2207 Lab ManualDokument72 SeitenEE2207 Lab ManualgowthamveluNoch keine Bewertungen

- Semiconductor Device and Physics ApplicationDokument336 SeitenSemiconductor Device and Physics ApplicationNguyenPhucTruong100% (1)

- Smart Ups Su1000 1400 Chassis 733Dokument5 SeitenSmart Ups Su1000 1400 Chassis 733miklexNoch keine Bewertungen

- GLM240128Dokument35 SeitenGLM240128api-3700809Noch keine Bewertungen

- Power Supply Unit DesignDokument37 SeitenPower Supply Unit DesignfamtaluNoch keine Bewertungen

- Schematic LCR MeterDokument1 SeiteSchematic LCR MeterTrường Phúc Lưu100% (1)

- Electrical Networks and RESONANCE SQA.Dokument124 SeitenElectrical Networks and RESONANCE SQA.Ibrahim KhleifatNoch keine Bewertungen

- ESR Tester 096kDokument41 SeitenESR Tester 096kFabrício AngieneNoch keine Bewertungen

- MonkeyBoard DAB DAB FM Digital Radio Development Board Pro Mit SlideShowDokument3 SeitenMonkeyBoard DAB DAB FM Digital Radio Development Board Pro Mit SlideShowDawid MleczkoNoch keine Bewertungen

- Power Electronics Devices LectureDokument78 SeitenPower Electronics Devices LectureM Waqar ZahidNoch keine Bewertungen

- Aiwa TV C2121 PDFDokument43 SeitenAiwa TV C2121 PDFAsallimitNoch keine Bewertungen

- Drake PartlistDokument50 SeitenDrake PartlistAnonymous hPUlIF6Noch keine Bewertungen

- AQ3485Y ManualDokument15 SeitenAQ3485Y ManualVu SonNoch keine Bewertungen

- Sony Chassis Ba-4 (C-TV KV-13M40 - 50 - 51, KV-14MB40, KV-20M40, KV-20S40 - 41, KV-20V80, Kv-21se80, Kv-21se40, Kv-21me40... Service Manual)Dokument94 SeitenSony Chassis Ba-4 (C-TV KV-13M40 - 50 - 51, KV-14MB40, KV-20M40, KV-20S40 - 41, KV-20V80, Kv-21se80, Kv-21se40, Kv-21me40... Service Manual)Mauro Mendez100% (1)

- An32f PDFDokument12 SeitenAn32f PDFPaulo MonteiroNoch keine Bewertungen

- Articolo SWR EngDokument4 SeitenArticolo SWR EngLuis Enrique Castillejo GonzalesNoch keine Bewertungen

- PIFA Planar Inverted F AntennaDokument4 SeitenPIFA Planar Inverted F AntennaAhsan AltafNoch keine Bewertungen

- 1 3 8 TI Digital Logic FamiliesDokument4 Seiten1 3 8 TI Digital Logic FamiliesJose Luis Castro AguilarNoch keine Bewertungen

- Semicounductors & Pn-Junction (Complete)Dokument47 SeitenSemicounductors & Pn-Junction (Complete)Khalid AliNoch keine Bewertungen

- Confidential Manual for Rainbow 150 Welder RepairDokument54 SeitenConfidential Manual for Rainbow 150 Welder RepairJaroslaw Brzozowski100% (2)

- Manual Axpert KING PYLONDokument59 SeitenManual Axpert KING PYLONEllis BergmanNoch keine Bewertungen

- Switch Mode Power Supply Topologies Compared - Wurth Electronics MidcomDokument4 SeitenSwitch Mode Power Supply Topologies Compared - Wurth Electronics Midcommayank shuklaNoch keine Bewertungen

- LC22-24LE250 - 17MB95S SM - June2013 PDFDokument106 SeitenLC22-24LE250 - 17MB95S SM - June2013 PDFAnonymous h80fVWNoch keine Bewertungen

- IC Logic Families and CharacteristicsDokument10 SeitenIC Logic Families and CharacteristicsAnonymous eWMnRr70qNoch keine Bewertungen

- Circuits I Have KnownDokument189 SeitenCircuits I Have Knownjack266Noch keine Bewertungen

- Practical Mosfet Testing For Audio: by Nelson Pass, (C) 2003 Pass LaboratoriesDokument11 SeitenPractical Mosfet Testing For Audio: by Nelson Pass, (C) 2003 Pass Laboratoriesanon-306355100% (1)

- Slua 125Dokument10 SeitenSlua 125Anonymous RloUXGnmSWNoch keine Bewertungen

- AVR Lecture 2Dokument72 SeitenAVR Lecture 2Mahrukh Baloch100% (2)

- Colour Television NTSC Carnt Wireless World 1961Dokument518 SeitenColour Television NTSC Carnt Wireless World 1961Fredji82Noch keine Bewertungen

- Lecture Notes For Analog ElectronicsDokument54 SeitenLecture Notes For Analog Electronicsmom028Noch keine Bewertungen

- Toshiba 24AF46 TVDokument44 SeitenToshiba 24AF46 TVWilfredo ManzanoNoch keine Bewertungen

- Dumont 79-02A - Dual Trace (Vertical Plugin) Instruction Manual With Maintenance Part - 6704 55l2Dokument113 SeitenDumont 79-02A - Dual Trace (Vertical Plugin) Instruction Manual With Maintenance Part - 6704 55l2jabo499534Noch keine Bewertungen

- FFUS2613LS4 Frigidaire Refrigerator Wiring 240389639Dokument2 SeitenFFUS2613LS4 Frigidaire Refrigerator Wiring 240389639aderloch100% (1)

- 1989 Analog Devices DSP Products DatabookDokument437 Seiten1989 Analog Devices DSP Products DatabookkgrhoadsNoch keine Bewertungen

- Ee - 105 - ADSP-2100 Family C Programming Examples Guide (En)Dokument61 SeitenEe - 105 - ADSP-2100 Family C Programming Examples Guide (En)tiretrakNoch keine Bewertungen

- Electromagnetic Foundations of Electrical EngineeringVon EverandElectromagnetic Foundations of Electrical EngineeringNoch keine Bewertungen

- British Special Quality Valves and Electron Tube Devices Data Annual 1964–65Von EverandBritish Special Quality Valves and Electron Tube Devices Data Annual 1964–65Noch keine Bewertungen

- Real-Time Simulation Technology for Modern Power ElectronicsVon EverandReal-Time Simulation Technology for Modern Power ElectronicsNoch keine Bewertungen

- Fundamentals of Electronics 2: Continuous-time Signals and SystemsVon EverandFundamentals of Electronics 2: Continuous-time Signals and SystemsNoch keine Bewertungen

- Electrical Overstress (EOS): Devices, Circuits and SystemsVon EverandElectrical Overstress (EOS): Devices, Circuits and SystemsNoch keine Bewertungen

- MIPI LVDS ICN6202 Specification V08Dokument22 SeitenMIPI LVDS ICN6202 Specification V08周勇Noch keine Bewertungen

- Tps18.1e La 312278520753 190126Dokument54 SeitenTps18.1e La 312278520753 190126ALAIN GOUDEAUNoch keine Bewertungen

- LCD Cable PinoutsDokument3 SeitenLCD Cable PinoutsMilan HouskaNoch keine Bewertungen

- Samsung UN40C5000QFXZA Fast TrackDokument4 SeitenSamsung UN40C5000QFXZA Fast TrackJustin NgNoch keine Bewertungen

- IS200e SMDokument92 SeitenIS200e SMsaa984Noch keine Bewertungen

- LG Lc320dun-Sfr1Dokument37 SeitenLG Lc320dun-Sfr1kalanghoNoch keine Bewertungen

- 5820 Edition 2Dokument114 Seiten5820 Edition 2Erasmo FrancoNoch keine Bewertungen

- B154ew01 V4 AuoDokument37 SeitenB154ew01 V4 AuoFranklin JimenezNoch keine Bewertungen

- Flyer EZ-ROJ-2Dokument2 SeitenFlyer EZ-ROJ-2Fabricio VigolloNoch keine Bewertungen

- Electronicdesign 10390 Jesd204bsimplifiedDokument5 SeitenElectronicdesign 10390 Jesd204bsimplifiedSB GAYENNoch keine Bewertungen

- Driving LVPECL, LVDS, CML and SSTL Logic With IDT's "Universal" Low-Power HCSL OutDokument14 SeitenDriving LVPECL, LVDS, CML and SSTL Logic With IDT's "Universal" Low-Power HCSL Outtian yuNoch keine Bewertungen

- 1 Sharp LCDTVDokument62 Seiten1 Sharp LCDTVChris JenkinsNoch keine Bewertungen

- Lp141wx3 Tln1 LGDokument31 SeitenLp141wx3 Tln1 LGYusuf AbdullahNoch keine Bewertungen

- 02 EtherCAT Introduction 1609Dokument111 Seiten02 EtherCAT Introduction 1609Khaled OuniNoch keine Bewertungen

- Lenovo D1960WDokument51 SeitenLenovo D1960WSalatiel FirminoNoch keine Bewertungen

- Stratix5 HandbookDokument527 SeitenStratix5 HandbookSathesh KumarNoch keine Bewertungen

- Istilah Dalam Skema Diagram Laptop-NotebookDokument6 SeitenIstilah Dalam Skema Diagram Laptop-NotebookTrifa ElectronikaNoch keine Bewertungen

- ServiceDokument69 SeitenServiceVimalGopiNarayananNoch keine Bewertungen

- LP154W01 TLD2Dokument27 SeitenLP154W01 TLD2Bianca BuenoNoch keine Bewertungen

- Presentation On: Presented byDokument28 SeitenPresentation On: Presented bysyedaNoch keine Bewertungen

- Service Manual: PDP TelevisionDokument53 SeitenService Manual: PDP TelevisionSimon MariñoNoch keine Bewertungen

- LTM220M2 L01Dokument35 SeitenLTM220M2 L01Manuel Lorenzo100% (1)

- Матрица LP154WX5-TLA1Dokument31 SeitenМатрица LP154WX5-TLA1Voznesensk CdutNoch keine Bewertungen

- Panasonic Th-42pz700u Th-50pz700u Th-58pz700u Th-50pz750u Th-58pz750u 10th Generation HD Plasma TrainingDokument116 SeitenPanasonic Th-42pz700u Th-50pz700u Th-58pz700u Th-50pz750u Th-58pz750u 10th Generation HD Plasma TrainingNsb El-kathiriNoch keine Bewertungen

- Dell Latitude E5530 Owner's ManualDokument71 SeitenDell Latitude E5530 Owner's ManualesatpehlivanNoch keine Bewertungen

- Specification FOR Approval: TitleDokument31 SeitenSpecification FOR Approval: TitleMauricio Gálvez MarínNoch keine Bewertungen

- Operating Instructions SubracksDokument21 SeitenOperating Instructions SubracksOma Ouali50% (2)

- Tpm20.7e LaDokument109 SeitenTpm20.7e LaTavi Dumitrescu100% (1)

- V315B5L01Dokument29 SeitenV315B5L01canal.alternativo.videosNoch keine Bewertungen

- TFT-Display Datenblatt: Modell LM230WF1-TLA3Dokument32 SeitenTFT-Display Datenblatt: Modell LM230WF1-TLA3Angel Lazarte DueñasNoch keine Bewertungen