Beruflich Dokumente

Kultur Dokumente

Ap92s12 Advanced Digital System Design

Hochgeladen von

sridhar_omalurCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ap92s12 Advanced Digital System Design

Hochgeladen von

sridhar_omalurCopyright:

Verfügbare Formate

AP9212 ADVANCED DIGITAL SYSTEM DESIGN SYLLABUS | ANNA UNIVERSITY ME APPLIED ELECTRONICS 1ST SEM SYLLABUS REGULATION 2009

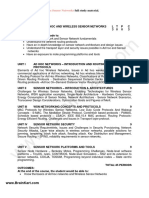

2011 20122013 BELOW IS THE ANNA UNIVERSITY FIRST SEMESTER M.E APPLIED ELECTRONICS DEPARTMENT SYLLABUS, TEXTBOOKS, REFERENCE BOOKS,EXAM PORTIONS,QUESTION BANK,PREVIOUS YEAR QUESTION PAPERS,MODEL QUESTION PAPERS, CLASS NOTES, IMPORTANT 2 MARKS, 8 MARKS, 16 MARKS TOPICS. IT IS APPLICABLE FOR ALL STUDENTS ADMITTED IN THE YEAR 2011 2012-2013 (ANNA UNIVERSITY CHENNAI,TRICHY,MADURAI, TIRUNELVELI,COIMBATORE), 2009 REGULATION OF ANNA UNIVERSITY CHENNAI AND STUDENTS ADMITTED IN ANNA UNIVERSITY CHENNAI DURING 2009 AP9212 ADVANCED DIGITAL SYSTEM DESIGN L T P C3 0 0 3 UNIT I SEQUENTIAL CIRCUIT DESIGN 9 Analysis of clocked synchronous sequential circuits and modeling- State diagram, state table, state table assignment and reduction-Design of synchronous sequential circuitsdesign of iterative circuits-ASM chart and realization using ASM

UNIT II ASYNCHRONOUS SEQUENTIAL CIRCUIT DESIGN 9 Analysis of asynchronous sequential circuit flow table reduction-races-state assignment-transition table and problems in transition table- design of asynchronous sequential circuit-Static, dynamic and essential hazards data synchronizers mixed operating mode asynchronous circuits designing vending machine controller 4

UNIT III FAULT DIAGNOSIS AND TESTABILITY ALGORITHMS 9 Fault table method-path sensitization method Boolean difference method-D algorithm -Tolerance techniques The compact algorithm Fault in PLA Test generation-DFT schemes Built in self test

UNIT IV SYNCHRONOUS DESIGN USING PROGRAMMABLE DEVICES 9 Programming logic device families Designing a synchronous sequential circuit using PLA/PAL Realization of finite state machine using PLD FPGA Xilinx FPGA-Xilinx 4000

UNIT V SYSTEM DESIGN USING VHDL 9 VHDL operators Arrays concurrent and sequential statements packages- Data flow Behavioral structural modeling compilation and simulation of VHDL code Test bench - Realization of combinational and sequential circuits using HDL Registers counters sequential machine serial adder Multiplier- Divider Design of simple micropr ocessor

TOTAL : 45 PERIODS REFERENCES: 1. Charles H.Roth Jr Fundamentals of Logic Design Thomson Learning 2004 2. Nripendra N Biswas Logic Design Theory Prentice Hall of India,2001 3. Parag K.Lala Fault Tolerant and Fault Testable Hardware Design B S Publications,2002 4. Parag K.Lala Digital system Design using PLD B S Publications,2003 5. Charles H Roth Jr.Digital System Design using VHDL Thomson learning, 2004 6. Douglas L.Perry VHDL programming by Example Tata McGraw.Hill - 2006 click here to read more: http://www.annaunivedu.in/2012/10/ap9212-advanced-digitalsystem-design.html#ixzz2VEjifbix more question bank and prevoius year question paper

Das könnte Ihnen auch gefallen

- Water FountainDokument13 SeitenWater Fountaingarych72Noch keine Bewertungen

- AR Porta CabinDokument2 SeitenAR Porta CabinVp SreejithNoch keine Bewertungen

- AP7101-Advanced Digital Signal Processing Question BankDokument8 SeitenAP7101-Advanced Digital Signal Processing Question BanksharmikbkNoch keine Bewertungen

- (EngineeringEBookspdf) Failure Investigation of Bolier PDFDokument448 Seiten(EngineeringEBookspdf) Failure Investigation of Bolier PDFcarlos83% (6)

- Verilog Lab ManualDokument72 SeitenVerilog Lab ManualAditya NarayanNoch keine Bewertungen

- Digital System Design Lab Manual - KMSDokument94 SeitenDigital System Design Lab Manual - KMSSiva Kumar100% (3)

- Free Convection (Formulae & Problems)Dokument15 SeitenFree Convection (Formulae & Problems)ananth2012Noch keine Bewertungen

- Return Material Authorization: 1/2 RMA Number Customer No. Purchase Order No. Sales Order DateDokument2 SeitenReturn Material Authorization: 1/2 RMA Number Customer No. Purchase Order No. Sales Order DateMichelle PadillaNoch keine Bewertungen

- DSP Lab Manual EC8562 (R 2017)Dokument82 SeitenDSP Lab Manual EC8562 (R 2017)SETNHILNoch keine Bewertungen

- 3D - Quick Start - OptitexHelpEnDokument26 Seiten3D - Quick Start - OptitexHelpEnpanzon_villaNoch keine Bewertungen

- Sem 638 Manual de MantenimientoDokument12 SeitenSem 638 Manual de MantenimientoJhon Simanca100% (1)

- Scooptram ST14 Battery: Fully Battery Electric Loader With 14-Tonne CapacityDokument8 SeitenScooptram ST14 Battery: Fully Battery Electric Loader With 14-Tonne CapacityAnonymous Mdw6y7Q1Noch keine Bewertungen

- Question Bank-1913104-Design of Embedded SystemsDokument12 SeitenQuestion Bank-1913104-Design of Embedded SystemsHasib Al-ariki100% (1)

- HDL Lab Manual For VTUDokument93 SeitenHDL Lab Manual For VTULavanya Vaishnavi D.A.Noch keine Bewertungen

- Advanced Digital System DesignDokument1 SeiteAdvanced Digital System Designarunecetheboss0% (3)

- Pest Analysis of Telecom IndustryDokument6 SeitenPest Analysis of Telecom IndustryAymanCheema70% (10)

- M.E Advanced-Digital-System-DesignDokument2 SeitenM.E Advanced-Digital-System-DesignvanithapremkumarNoch keine Bewertungen

- Ap9212 AdsdDokument12 SeitenAp9212 AdsdKartheeswaran Arumugam33% (3)

- EC8661 VLSI Design LaboratoryDokument53 SeitenEC8661 VLSI Design LaboratorySriram100% (4)

- Verilog Lab ManualDokument27 SeitenVerilog Lab Manualjainatush912100% (1)

- Low-Power Digital VLSI DesignDokument530 SeitenLow-Power Digital VLSI DesignAllanki Sanyasi Rao50% (2)

- Ec8562 Digital Signal Processing LabDokument73 SeitenEc8562 Digital Signal Processing LabRaghul M100% (3)

- EC8702 Adhoc Syllabus PDFDokument3 SeitenEC8702 Adhoc Syllabus PDFThahsin Thahir100% (1)

- AP5004-High Performance Networks - SyllabusDokument1 SeiteAP5004-High Performance Networks - Syllabusjames RNoch keine Bewertungen

- Multiplier in Vlsi PDFDokument23 SeitenMultiplier in Vlsi PDFvmspraneeth100% (1)

- Anallysis and Design of Analog Integrated Circuits QuestionsDokument5 SeitenAnallysis and Design of Analog Integrated Circuits QuestionsshankarNoch keine Bewertungen

- VLSI Unit-IVDokument87 SeitenVLSI Unit-IVUma Maheswari100% (2)

- EC8661 VLSI Design Lab ManualDokument76 SeitenEC8661 VLSI Design Lab ManualN.S.Priyanga 33100% (3)

- VL5101 Periodical 1Dokument4 SeitenVL5101 Periodical 1DarwinNoch keine Bewertungen

- 15ecl48-VTU-raghudathesh-BJT MIXER PDFDokument2 Seiten15ecl48-VTU-raghudathesh-BJT MIXER PDFraghudatheshgp100% (1)

- Low Power Vlsi Question PaperDokument2 SeitenLow Power Vlsi Question Paperustadkrishna100% (3)

- Digital Design Lab Manual: Introduction To VerilogDokument48 SeitenDigital Design Lab Manual: Introduction To VerilogKeith FernandesNoch keine Bewertungen

- Dr. N.G.P. Institute of Technology - Coimbatore-48: Analog and Digital Integrated CircuitsDokument48 SeitenDr. N.G.P. Institute of Technology - Coimbatore-48: Analog and Digital Integrated CircuitsMrs.S.Divya BMENoch keine Bewertungen

- EC 8453 LINEAR INTEGRATED CIRCUITS Unit 1Dokument16 SeitenEC 8453 LINEAR INTEGRATED CIRCUITS Unit 1Madhavan Sam0% (1)

- VLSI CAD QuestionDokument2 SeitenVLSI CAD QuestionMCV101Noch keine Bewertungen

- EC6612 VLSI DESIGN Laboratory Question SetDokument6 SeitenEC6612 VLSI DESIGN Laboratory Question Setanand_duraiswamyNoch keine Bewertungen

- EC8392-DE Question Bank With Answers 1Dokument44 SeitenEC8392-DE Question Bank With Answers 1shanthiantony100% (1)

- DS4152 Statistical Signal ProcessingDokument2 SeitenDS4152 Statistical Signal Processingiiecea 2122Noch keine Bewertungen

- EC8251-Circuit Analysis PDFDokument30 SeitenEC8251-Circuit Analysis PDFPalanikumar Pitchaikani0% (1)

- DSD Lab ManualDokument64 SeitenDSD Lab ManualAkkonduru KumarNoch keine Bewertungen

- Circuit Theory Two MarksDokument26 SeitenCircuit Theory Two Markshakkem bNoch keine Bewertungen

- Manufacturing Test Principles: (Vlsi Unit-5)Dokument53 SeitenManufacturing Test Principles: (Vlsi Unit-5)Tamil ArasuNoch keine Bewertungen

- Digital System Design Using VerilogDokument55 SeitenDigital System Design Using VerilogAditya PatilNoch keine Bewertungen

- Jain College of Engineering, Belagavi: Signals & Systems (18ec45) Question Bank For Cie - IiiDokument3 SeitenJain College of Engineering, Belagavi: Signals & Systems (18ec45) Question Bank For Cie - Iiisystech techniques50% (2)

- EC8791 Important QuestionsDokument27 SeitenEC8791 Important QuestionsSurendar PNoch keine Bewertungen

- EC8651 TLW R2017 2 MarksDokument11 SeitenEC8651 TLW R2017 2 Marksdhanaraj100% (2)

- 16EC454 ASIC Design SyllabusDokument2 Seiten16EC454 ASIC Design SyllabusGautami SumanNoch keine Bewertungen

- Ec8461 Cd&si LabDokument86 SeitenEc8461 Cd&si LabReena RajNoch keine Bewertungen

- Cad For Vlsi Circuits 2 PDFDokument2 SeitenCad For Vlsi Circuits 2 PDFrajasekarkpr100% (1)

- Jntu (NR) M.tech 2-Semester Design of Fault Tolerant Systems July - Aug-2006 Exam Question Paper - Indian ShoutDokument3 SeitenJntu (NR) M.tech 2-Semester Design of Fault Tolerant Systems July - Aug-2006 Exam Question Paper - Indian Shoutramanaidu1Noch keine Bewertungen

- eInfoChips Interview QuestionsDokument2 SeiteneInfoChips Interview Questionsshafi hasmaniNoch keine Bewertungen

- Ec8562 - DSP Lab QuestionDokument1 SeiteEc8562 - DSP Lab QuestionTAMILSELVAN R100% (2)

- AP7101-Advanced Digital Signal ProcessingDokument8 SeitenAP7101-Advanced Digital Signal ProcessingDhamodharan Srinivasan50% (2)

- IT6502-Digital Signal Processing, UNIT IDokument98 SeitenIT6502-Digital Signal Processing, UNIT Isyed1188100% (1)

- Ec8691 MPMC 2mark UnivDokument20 SeitenEc8691 MPMC 2mark Univspgmaniarunagiri50% (2)

- University Question Bank - EdcDokument16 SeitenUniversity Question Bank - EdcSenthil IlangovanNoch keine Bewertungen

- Digital System Design Question PaperDokument1 SeiteDigital System Design Question Papermujju433100% (1)

- CS8382 DS Lab Manual Cse PDFDokument65 SeitenCS8382 DS Lab Manual Cse PDFvlsiprabhu0% (1)

- Assignment 1 DSDDokument2 SeitenAssignment 1 DSDsarala tNoch keine Bewertungen

- Ap5191 Embedded System DesignDokument3 SeitenAp5191 Embedded System DesignHasib Al-ariki100% (1)

- Comm Networks LabDokument74 SeitenComm Networks Labjaba123jaba100% (1)

- VLSIDokument22 SeitenVLSIMoulana YasinNoch keine Bewertungen

- Regulation - 2009: Affiliated Institutions Anna University, ChennaiDokument27 SeitenRegulation - 2009: Affiliated Institutions Anna University, ChennaiYogeswaran SundarrajNoch keine Bewertungen

- Ap9212 Advanced Digital System Design L T P c3 0 0 3Dokument1 SeiteAp9212 Advanced Digital System Design L T P c3 0 0 3Adam Wells100% (1)

- Applied Mathematics For Electronics EngineersDokument35 SeitenApplied Mathematics For Electronics EngineersRamJiDRNoch keine Bewertungen

- ME VLSI SyllabusDokument33 SeitenME VLSI Syllabusps0208Noch keine Bewertungen

- Syllabus For Applied ElectronicsDokument28 SeitenSyllabus For Applied ElectronicsvinayakbondNoch keine Bewertungen

- Vlsi Mtech Jntu Kakinada SyllabusDokument11 SeitenVlsi Mtech Jntu Kakinada Syllabusaditya414Noch keine Bewertungen

- A Robust DWT-Based Blind Data Hiding Algorithm: Liu ShiDokument4 SeitenA Robust DWT-Based Blind Data Hiding Algorithm: Liu Shisridhar_omalurNoch keine Bewertungen

- Lecture 1: Introduction To Microprocessors and MicrocomputersDokument24 SeitenLecture 1: Introduction To Microprocessors and Microcomputerssridhar_omalurNoch keine Bewertungen

- KprTeaching Staff Application FormDokument78 SeitenKprTeaching Staff Application Formsridhar_omalurNoch keine Bewertungen

- Part - A (Answer All The Questions)Dokument1 SeitePart - A (Answer All The Questions)sridhar_omalurNoch keine Bewertungen

- Dhanpal ResumeDokument3 SeitenDhanpal Resumesridhar_omalurNoch keine Bewertungen

- Boomer M-Series Technical Specification tcm835-1533266 PDFDokument8 SeitenBoomer M-Series Technical Specification tcm835-1533266 PDFseferinoNoch keine Bewertungen

- Broch 6700 New 1Dokument2 SeitenBroch 6700 New 1rumboherbalNoch keine Bewertungen

- Assessment of Reinforcement CorrosionDokument5 SeitenAssessment of Reinforcement CorrosionClethHirenNoch keine Bewertungen

- DH Xvr4b16Dokument3 SeitenDH Xvr4b16Jumar JumadiaoNoch keine Bewertungen

- MP Interconnection StandardsDokument54 SeitenMP Interconnection StandardsAnonymous utxGVB5VyNoch keine Bewertungen

- Fit-Up Piping B192-5-S2Dokument22 SeitenFit-Up Piping B192-5-S2Prathamesh OmtechNoch keine Bewertungen

- Mmro C 053 MD 0357 Interior PL DrawingsDokument82 SeitenMmro C 053 MD 0357 Interior PL DrawingsAnonymous 4Ts8UBFwzNoch keine Bewertungen

- Guidelines For Performance Task - LIVING MUSEUM PDFDokument2 SeitenGuidelines For Performance Task - LIVING MUSEUM PDFJoserie Barioga HernaneNoch keine Bewertungen

- Durability of Culvert PipeDokument21 SeitenDurability of Culvert PipeIftiNoch keine Bewertungen

- Telenor Organization Structure and CultureDokument29 SeitenTelenor Organization Structure and CultureAli Farooqui85% (20)

- Surge Arresters PP 7Dokument9 SeitenSurge Arresters PP 7gabriela69sNoch keine Bewertungen

- 300Mbps/150Mbps Wireless LAN Broadband Router: Quick Installation GuideDokument2 Seiten300Mbps/150Mbps Wireless LAN Broadband Router: Quick Installation GuideLuis AngelNoch keine Bewertungen

- BOB SO Information HandoutDokument5 SeitenBOB SO Information HandoutKabya SrivastavaNoch keine Bewertungen

- ERJ 145 InfoDokument11 SeitenERJ 145 InfoMarcus100% (1)

- Myanmar Power SystemDokument4 SeitenMyanmar Power Systemkayden.keitonNoch keine Bewertungen

- Masterprotect 190: A Two Component Solvent Free High Build Flexible Epoxy Polyurethane Resin Coating SystemDokument3 SeitenMasterprotect 190: A Two Component Solvent Free High Build Flexible Epoxy Polyurethane Resin Coating SystemEngTamer100% (1)

- CS 201 1 PDFDokument7 SeitenCS 201 1 PDFMd AtharNoch keine Bewertungen

- 晴天木塑目录册Dokument18 Seiten晴天木塑目录册contaeduNoch keine Bewertungen

- Is 803Dokument98 SeitenIs 803Gaurav BedseNoch keine Bewertungen

- Dyatlov Interview 1995 enDokument6 SeitenDyatlov Interview 1995 enmhulot100% (1)

- Relationship Between Organisations and Information SystemsDokument16 SeitenRelationship Between Organisations and Information SystemsJoan KuriaNoch keine Bewertungen