Beruflich Dokumente

Kultur Dokumente

EE 421-Digital System Design-Dr. Shahid Masud-Updated PDF

Hochgeladen von

Ubaid UmarOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

EE 421-Digital System Design-Dr. Shahid Masud-Updated PDF

Hochgeladen von

Ubaid UmarCopyright:

Verfügbare Formate

Lahore University of Management Sciences

EE 421 Digital System Design Fall 2012 - 13

Instructor Room No. Office Hours Email Telephone Secretary/TA TA Office Hours Course URL (if any) Course Basics Credit Hours Lecture(s) Lab (per week) Tutorial (per week)

Dr. Shahid Masud 9-323A Friday 0930 to 1030 smasud 8199 8355 LMS page

4 Nbr of Lec(s) Per Week Nbr of Lab(s) Per Week Nbr of Lec(s) Per Week

2 1

Duration 75 mins Duration 3 hours Duration

Course Distribution Core Elective Open for Student Category Close for Student Category COURSE DESCRIPTION

EE Junior / Senior / MS Freshman / Sophomore

This course explains how to go about designing complex, high-speed digital circuits and systems. The use of modern EDA tools in the design, simulation, synthesis and implementation is explored. Application of a hardware description language such as Verilog or VHDL to model digital systems at Behavior and RTL level is studied. Field programmable gate arrays (FPGA) are used in the laboratory exercises as a vehicle to understand complete design-flow of an integrated circuit. Advanced methods of logic minimization and state-machine design are discussed. Design and implementation of digital system building blocks such as arithmetic circuits, datapaths, microprocessors, I/O modules, UARTs, frequency generators, memories etc. is included. BIST and Scan techniques for testing of digital systems are also covered. Laboratories and projects are an integral part of this course that culminates in a comprehensive design exercise.

COURSE PREREQUISITE(S) Microprocessors and Interfacing OR Computer Organization and Assembly Language

1|P age

Lahore University of Management Sciences

COURSE OBJECTIVES To teach modern techniques of complex hardware design using hardware description language and field programmable gate array devices.

Learning Outcomes Upon completion of the course, students should be able to: i. Understand issues in designing high-speed complex digital systems ii. Understand hardware architectures of basic building blocks of digital systems iii. Undertake design and optimization complex combinational and sequential logic iv. Describe a complex digital system using VHDL v. Simulate and Debug digital systems using EDA tools vi. Implement digital systems on FPGA platforms vii. Analyze and specify timing in high-speed design

Grading Breakup and Policy Lab Exercises(s): 15% (Attendance during lab=4%, Completion of lab tasks=6%, Lab Midterm=5%) Project: 15% (Specifications=2%, Coding and Simulation=5%, FPGA Implementation=4%, Report=4%) Quiz(s): 15% (Around 6) Midterm Examination: 25% Final Examination:30%

Examination Detail Yes/No: Yes Combine Separate: Combine Duration: 75 minutes Preferred Date: Exam Specifications: Calculators allowed Yes/No: Yes Combine Separate: Combine Duration: 120 mins Exam Specifications: Calculators allowed

Midterm Exam

Final Exam

2|P age

Lahore University of Management Sciences

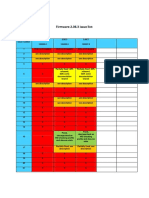

Lecture / Week 1 / Wk 1 2 / Wk 1 Lab 1 3 / Wk 2 4 / Wk 2 Lab 2 5 / Wk 3 6 / Wk 3 Lab 3 7 / Wk 4 8 / Wk 4 Lab 4 9 / Wk 5 10 / Wk 5 Lab 5 11 / Wk 6 12 / Wk 6 13 / Wk 7 Wk 7 14 / Wk 7 14 / Wk 7 15 / Wk 8 16 / Wk 8 Lab 7 17 / Wk 9 18 / Wk 9 Lab 8 19 / Wk 10 20 / Wk 10 Lab 9 21 / Wk 11 22 / Wk 11 Lab 10 22 / Wk 11 23 / Wk 12 Lab 11 24 / Wk 13 25 / Wk 13 Labs 12 to 14 26 / Wk 14 Course Topics Introduction to digital systems and their design flow Review of combinational logic, logic minimization Introductory VHDL 1 Timing in Combinational Circuits, Hazards and Glitches, Review of sequential logic Lecture - Introductory VHDL - 2 VHDL Coding and Simulation on Modelsim Design using flip-flop and latches, State machines State reduction, timing issues VHDL Behavioural Coding and Simulation Design of Adders and Subtractors, Carry Lookahead Adders Serial Adders, Array Multipliers, Critical Paths VHDL Sequential Coding and Simulation Booth and Radix-4 Encoded Signed Multipliers Further VHDL modeling, parameterization VHDL Design of State Machines Design of dividers and other arithmetic circuits Circuits for Floating Point Implementation Serial Multipliers, Keyboard Scanner, Signed Multiplication of Fractions Due Specifications (up to 2 pages) of Design Exercise Midterm Exam Midterm Exam Programmable logic, PAL, PLA, CPLD Construction and operation of FPGA Midterm Lab Exam Controller design using ASM charts Controller Design for Sequential Multipliers and Dividers FPGA Implementation 1 LFSR, BRM, Function Generators, Design Examples Faults and Testability BIST and SCAN techniques FPGA Implementation 2 Design for test JTAG Advanced VHDL Memories and Register Files Design Example 1 VHDL Synthesis Issues Advanced VHDL / Examples of Digital Systems Design Example 2 Asynchronous Sequential Design Processor Design 1 Design Exercise (Simulation, FPGA Implementation, Demonstration) Processor Design - 2 Readings Roth Roth Lab 1 Roth Lab / Quiz

Lab 2 Roth Roth Lab 3 Roth Roth Lab 4 Notes Lab 6 Roth Roth Roth

Roth Roth Lab Exam Roth Roth Lab 8 Notes Roth Lab 9 Roth Lab 10 Zwolinski Notes Lab 11 Zwolinski Roth Design Exercise Roth

3|P age

Lahore University of Management Sciences

27 / Wk 14 Digital Design Case Study Due Final Report and Submission of Design Exercise Final Exam Week 15 Notes

Lab Exercises: Lab / Week 1. / Wk 1 2. / Wk 2 3. / Wk 3 4. / Wk 4 5. / Wk 5 6. / Wk 6 Wk 7 7. / Wk 8 8. / Wk 9 9. / Wk 10 10. / Wk 11 11. / Wk 12 Wk 13 - 14

Lab Topics Structural and Modular VHDL coding Simulation and testing of VHDL code Behavior Design Examples, coding and simulation RTL Design, coding and simulation FSM in VHDL, coding and simulation VHDL Design Examples Lab Exam VHDL Simulation Xilinx Synthesis - FPGA implementation of design 1 Xilinx Synthesis - FPGA implementation of design 2 Optimize logic design (speed, area), placement and routing Design Exercise and further FPGA experiments Advanced VHDL Concepts, simulation and synthesis Design Exercise including FPGA Implementation

Readings

Textbook(s)/Supplementary Readings Text book: 1. Principles of Digital Systems Design using VHDL, Charles H. Roth, Lizy K. John, CEngage Learning, 1998, Indian Reprint 2008 Supplementary Reading: 1. Digital Electronics and Design with VHDL, Volnei A. Pedroni, Elsevier Publishers, 2008 2. Digital System Design with VHDL, Second edition, Mark Zwolinski, Pearson Education, 2004

4|P age

Das könnte Ihnen auch gefallen

- EE 421-Digital System Design-Dr. Shahid MasoodDokument4 SeitenEE 421-Digital System Design-Dr. Shahid MasoodSher Hassan RazaNoch keine Bewertungen

- Course Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentDokument6 SeitenCourse Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentAbdullah SohailNoch keine Bewertungen

- FALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LDokument3 SeitenFALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LUrjoshi AichNoch keine Bewertungen

- Course DescriptionDokument8 SeitenCourse DescriptionKiranKumarNoch keine Bewertungen

- VLSIDesigncourse TempleteDokument6 SeitenVLSIDesigncourse Templeteganga_chNoch keine Bewertungen

- Final M.tech. Credit Syllabus - ElectronicsDokument58 SeitenFinal M.tech. Credit Syllabus - Electronicskseries12Noch keine Bewertungen

- Industrial Training Vls I DesignDokument5 SeitenIndustrial Training Vls I DesignGaurav SainiNoch keine Bewertungen

- Computer Engineering Sem-1Dokument8 SeitenComputer Engineering Sem-1waniasimNoch keine Bewertungen

- ELEC 4200 Digital System DesignDokument2 SeitenELEC 4200 Digital System DesignAlan BensonNoch keine Bewertungen

- A204SE T212 StudyGuide - FinalDokument9 SeitenA204SE T212 StudyGuide - FinalLe Nguyen Tran QuangNoch keine Bewertungen

- Synthesis, Prentice Hall, 2001Dokument4 SeitenSynthesis, Prentice Hall, 2001Ralph Daniel BagaoisanNoch keine Bewertungen

- B.tech (IT)Dokument57 SeitenB.tech (IT)coolvar90Noch keine Bewertungen

- ECEN 5863 Programmable Logic Embedded System DesignDokument3 SeitenECEN 5863 Programmable Logic Embedded System DesignMehul PatelNoch keine Bewertungen

- EC6612-VLSI Lab - Lesson PlanDokument6 SeitenEC6612-VLSI Lab - Lesson PlanDsce CoimbatoreNoch keine Bewertungen

- DSD Using VerilogDokument1 SeiteDSD Using VerilogMansi JhambNoch keine Bewertungen

- Mtech Electronics Syllabus VTUDokument48 SeitenMtech Electronics Syllabus VTUmuqeetmmaNoch keine Bewertungen

- ECE419 Digital Vlsi Design 16937::tapsi Singh 3.0 1.0 0.0 4.0 Courses With Numerical and Conceptual FocusDokument8 SeitenECE419 Digital Vlsi Design 16937::tapsi Singh 3.0 1.0 0.0 4.0 Courses With Numerical and Conceptual FocusanakshaNoch keine Bewertungen

- EE 241 Digital Logic Design - Course OutlineDokument4 SeitenEE 241 Digital Logic Design - Course OutlineNasir Ud Din GoharNoch keine Bewertungen

- Teaching VLSI Design To Today's Students: Session 2532Dokument11 SeitenTeaching VLSI Design To Today's Students: Session 2532aswinjohnNoch keine Bewertungen

- Study Plan EE-221 Digital Logic DesignDokument5 SeitenStudy Plan EE-221 Digital Logic Designnauman yasinNoch keine Bewertungen

- ADSD SyllabusDokument2 SeitenADSD SyllabuswroxtarNoch keine Bewertungen

- Digital Design of Signal Processing Systems: A Practical ApproachVon EverandDigital Design of Signal Processing Systems: A Practical ApproachBewertung: 5 von 5 Sternen5/5 (1)

- Institute of Aeronautical Engineering: Mid Semester TestDokument8 SeitenInstitute of Aeronautical Engineering: Mid Semester TestNaresh BopparathiNoch keine Bewertungen

- 3rd, 5th, 7th Course OutlineDokument55 Seiten3rd, 5th, 7th Course OutlineSamiullah IlyasNoch keine Bewertungen

- DLD31Dokument36 SeitenDLD31rajNoch keine Bewertungen

- Course Specification: Se425 Distributed Control SystemDokument10 SeitenCourse Specification: Se425 Distributed Control SystemAmmar AlkindyNoch keine Bewertungen

- ME VLSI & EmdDokument58 SeitenME VLSI & EmdAnil V. WalkeNoch keine Bewertungen

- Advanced Digital System Design With FpgasDokument2 SeitenAdvanced Digital System Design With FpgasSayeed AnwarNoch keine Bewertungen

- VLSI Lab ManualDokument117 SeitenVLSI Lab ManualSusmitha BollimunthaNoch keine Bewertungen

- Cmpe223 Sylabi AbetDokument3 SeitenCmpe223 Sylabi AbetStrt SandyNoch keine Bewertungen

- First Course in VHDL Modeling and Fpga Synthesis of Digital SystemsDokument30 SeitenFirst Course in VHDL Modeling and Fpga Synthesis of Digital Systemshuy2910 dangdangNoch keine Bewertungen

- Digital Design Through Verilog HDL Course Outcomes For LabDokument1 SeiteDigital Design Through Verilog HDL Course Outcomes For LabSyed AshmadNoch keine Bewertungen

- Digital Design With HDL: With Effect From The Academic Year 2005 - 2006Dokument1 SeiteDigital Design With HDL: With Effect From The Academic Year 2005 - 2006attarbabaNoch keine Bewertungen

- ECE3362 Syllabus Fall 2014Dokument3 SeitenECE3362 Syllabus Fall 2014Gershom BenjaminNoch keine Bewertungen

- Ece103 Digital-logic-Design Eth 1.10 Ac29Dokument2 SeitenEce103 Digital-logic-Design Eth 1.10 Ac29netgalaxy2010Noch keine Bewertungen

- COMSATS Institute of Information Technology Abbottabad: GoalsDokument2 SeitenCOMSATS Institute of Information Technology Abbottabad: GoalsSohail MashwaniNoch keine Bewertungen

- Designing With VerilogDokument2 SeitenDesigning With VerilogManikandan PalaniNoch keine Bewertungen

- Ece 2003Dokument3 SeitenEce 2003gokulNoch keine Bewertungen

- EEE 270 - Advanced Topics in Logic Design Course Syllabus, Fall 2017Dokument4 SeitenEEE 270 - Advanced Topics in Logic Design Course Syllabus, Fall 2017Praveen MeduriNoch keine Bewertungen

- My First Course in Embedded SystemsDokument5 SeitenMy First Course in Embedded SystemsArpitha JainNoch keine Bewertungen

- Verilog-HDL: "Our Actions Inspires To "Dokument3 SeitenVerilog-HDL: "Our Actions Inspires To "Karthik VkNoch keine Bewertungen

- Digital Circuits CS437 - August 27 2008Dokument7 SeitenDigital Circuits CS437 - August 27 2008shivanand_shettennavNoch keine Bewertungen

- MEDokument37 SeitenMEMrunal UpasaniNoch keine Bewertungen

- EEE20001 Unit Outline Semester 2 2023Dokument12 SeitenEEE20001 Unit Outline Semester 2 2023MKNoch keine Bewertungen

- Top-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsVon EverandTop-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsNoch keine Bewertungen

- EE309 Microprocessors and Embedded Systems-ModifiedDokument2 SeitenEE309 Microprocessors and Embedded Systems-Modifiedanto5751Noch keine Bewertungen

- P G Certificate VLSI Design & Verification: (Live Project)Dokument11 SeitenP G Certificate VLSI Design & Verification: (Live Project)Devender KhariNoch keine Bewertungen

- Fall 2023 ELEC 205 (01) Syllabus 08 09 2023Dokument3 SeitenFall 2023 ELEC 205 (01) Syllabus 08 09 2023caggllayan47Noch keine Bewertungen

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Dokument2 SeitenPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirNoch keine Bewertungen

- Air University Fall 2005 Faculty of Engineering Department of Electronics Engineering Course InformationDokument2 SeitenAir University Fall 2005 Faculty of Engineering Department of Electronics Engineering Course InformationAli AhmadNoch keine Bewertungen

- System Verilog For VHDL UsersDokument4 SeitenSystem Verilog For VHDL UsersZakzouk ZakzoukNoch keine Bewertungen

- EE3003 - E S & Ic D: Mbedded Ystems EsignDokument4 SeitenEE3003 - E S & Ic D: Mbedded Ystems EsignCharles BradleyNoch keine Bewertungen

- Teaching FPGA-based Systems and Their Influence On MechatronicsDokument8 SeitenTeaching FPGA-based Systems and Their Influence On MechatronicseuardopNoch keine Bewertungen

- Digital Design With An Introduction To The Verilog HDL VHDL and Systemverilog 6 E Sixth Edition Global Edition Ciletti Full ChapterDokument52 SeitenDigital Design With An Introduction To The Verilog HDL VHDL and Systemverilog 6 E Sixth Edition Global Edition Ciletti Full Chapterflorence.hernandez892100% (3)

- Iszc462 - Networkprogramming - Question PaperDokument3 SeitenIszc462 - Networkprogramming - Question PaperShivam ShuklaNoch keine Bewertungen

- EE 423 Embedded System Design Awais KambohDokument5 SeitenEE 423 Embedded System Design Awais KambohMuhammad GulNoch keine Bewertungen

- Ece5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Dokument3 SeitenEce5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Daniel MNoch keine Bewertungen

- Software Engineering for Embedded Systems: Methods, Practical Techniques, and ApplicationsVon EverandSoftware Engineering for Embedded Systems: Methods, Practical Techniques, and ApplicationsBewertung: 2.5 von 5 Sternen2.5/5 (2)

- Frequency Assignment To Cellular Mobile Operators in PakistanDokument1 SeiteFrequency Assignment To Cellular Mobile Operators in PakistanUbaid UmarNoch keine Bewertungen

- Fiber Fundamentals (MM vs. SM)Dokument2 SeitenFiber Fundamentals (MM vs. SM)cartarNoch keine Bewertungen

- Employment Application Form Pakistan Atomic Energy CommissionDokument1 SeiteEmployment Application Form Pakistan Atomic Energy CommissionUbaid UmarNoch keine Bewertungen

- Lesson 3.1Dokument4 SeitenLesson 3.1Ubaid UmarNoch keine Bewertungen

- 1 Basics DSP AV IntroDokument36 Seiten1 Basics DSP AV IntroUbaid UmarNoch keine Bewertungen

- Limitations of BernoulliDokument1 SeiteLimitations of BernoulliUbaid UmarNoch keine Bewertungen

- 2541 Chemicalenginneering-2008Dokument80 Seiten2541 Chemicalenginneering-2008Azmatullah Khan SheraniNoch keine Bewertungen

- Theory and Design of CNC SystemsDokument129 SeitenTheory and Design of CNC SystemsValencia Luis ErnestoNoch keine Bewertungen

- Introduction To VLSI DesignDokument19 SeitenIntroduction To VLSI DesignFariyad AnsariNoch keine Bewertungen

- Datasheet Spartan 6Dokument22 SeitenDatasheet Spartan 6Luis Pabon100% (1)

- Fpga De0-Nano User Manual PDFDokument155 SeitenFpga De0-Nano User Manual PDFCesarNoch keine Bewertungen

- CPU Design HOWTO PDFDokument21 SeitenCPU Design HOWTO PDFSelvaraj VillyNoch keine Bewertungen

- FPGA Implementation of A Trained Neural Network: Seema Singh, Shreyashree Sanjeevi, Suma V, Akhil TalashiDokument10 SeitenFPGA Implementation of A Trained Neural Network: Seema Singh, Shreyashree Sanjeevi, Suma V, Akhil TalashiHaiNguyenNoch keine Bewertungen

- Industrial Training in VLSI Design - 2011Dokument10 SeitenIndustrial Training in VLSI Design - 2011Devender KhariNoch keine Bewertungen

- Diagnostic Clock BSC Flexi NokiaDokument4 SeitenDiagnostic Clock BSC Flexi NokiaMuhammad AyatullahNoch keine Bewertungen

- Firmware IssuesDokument15 SeitenFirmware IssuesGuilherme NevesNoch keine Bewertungen

- FSK Demodulator and FPGA Based BER Measurement System For Low IF ReceiversDokument2 SeitenFSK Demodulator and FPGA Based BER Measurement System For Low IF ReceiversAbhishek SrivastavaNoch keine Bewertungen

- DR Nasser Halasa CV - UkDokument8 SeitenDR Nasser Halasa CV - Uknasser halasaNoch keine Bewertungen

- Chapter 1Dokument80 SeitenChapter 1Praveena NeppalliNoch keine Bewertungen

- TeraFire PB Book For Altera PDFDokument32 SeitenTeraFire PB Book For Altera PDFakmicrodesignsNoch keine Bewertungen

- Xilinx Answer 73361 PCIe Link Training Debug Guide For US and US PlusDokument54 SeitenXilinx Answer 73361 PCIe Link Training Debug Guide For US and US PlusEvamGilotraNoch keine Bewertungen

- SwatiDokument5 SeitenSwatinabuNoch keine Bewertungen

- Arria V Avalon-St Interface For Pcie Solutions: User GuideDokument248 SeitenArria V Avalon-St Interface For Pcie Solutions: User Guideqw rwNoch keine Bewertungen

- DSP Selection Guide1Dokument38 SeitenDSP Selection Guide1J Inmanuel ZeNoch keine Bewertungen

- Asic Vs FpgaDokument34 SeitenAsic Vs FpgaPradeep ReddyNoch keine Bewertungen

- Timing Closure Exploration Tools With Smartxplorer and Planahead ToolsDokument7 SeitenTiming Closure Exploration Tools With Smartxplorer and Planahead ToolsSovi SoviNoch keine Bewertungen

- Hints For The Practical Final ExamDokument2 SeitenHints For The Practical Final ExamBrow AlaniNoch keine Bewertungen

- Cordic SVD HWDokument6 SeitenCordic SVD HWasdf2828Noch keine Bewertungen

- Master SetDokument624 SeitenMaster SetEr Lokesh MahorNoch keine Bewertungen

- Design and Implementation of Traffic Lights Controller Using FpgaDokument27 SeitenDesign and Implementation of Traffic Lights Controller Using Fpgavasu mitraNoch keine Bewertungen

- Low Constraint Length and High Performance Viterbi Decoder Using VHDLDokument7 SeitenLow Constraint Length and High Performance Viterbi Decoder Using VHDLInternational Journal of Application or Innovation in Engineering & ManagementNoch keine Bewertungen

- ResumeDokument3 SeitenResumeMuhamad HafisNoch keine Bewertungen

- Design and Implementation A Different Architectures of Mixcolumn in FPGADokument12 SeitenDesign and Implementation A Different Architectures of Mixcolumn in FPGAAnand Parakkat ParambilNoch keine Bewertungen

- Blackbook Sample For Engineering ProjectsDokument26 SeitenBlackbook Sample For Engineering ProjectsVikas Beri100% (3)

- VlsipythonDokument4 SeitenVlsipythonsiri.pogulaNoch keine Bewertungen

- Quartus - Install 683472 812587Dokument103 SeitenQuartus - Install 683472 812587hyper7697Noch keine Bewertungen

- Proposal 1Dokument8 SeitenProposal 1Muhammad Tausique100% (1)