Beruflich Dokumente

Kultur Dokumente

JK Flip Flop

Hochgeladen von

Mohammad AbdulMajidCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

JK Flip Flop

Hochgeladen von

Mohammad AbdulMajidCopyright:

Verfügbare Formate

1

ECE 433: JK Flip-Flop Design

AbstractThis report describes the process, from start to finish, of building a JK flip-flop. It includes the digital logic associated with the flip flop and the physical implementation as well. Also included are some simulation results of the design itself including rise and fall times varying with load capacitances.

Below is the logic for the flip flop. Note that for this truth table, E = 1, S = 0, and R = 0. J K Q Qnext 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 0 1 1 1 0

I. INTRODUCTION

he JK flip flop is an essential building block of digital logic. It is a device that can store a single piece of information known as a bit. The JK flip flop was chosen for this project because it is a more versatile flip flop when compared to the D- and T-types. Both the D- and T-type flip flops can be simulated by the JK flip flop by simple manipulation of the inputs J and K. For example, if one ties together the J and K inputs, a T flip flop will result. The flip flop in this design has several inputs: J, K, Set (S), Reset (R), Enable (E), and a Clock (CLK). The J and K inputs are used to manipulate the outputs Q and ~Q. The Set and Reset inputs are used to declare a particular output of set or reset regardless of the states of J and K. The Enable input is used to make the flip flop respond to its inputs. When Enable is logic 1, the flip flop behaves normally to its inputs, when it is logic 0, it will not respond. Logic 1 represents VDD = 5 V while logic 0 represents 0 V. The flip flop used in this design is a master-slave configuration. Each flip flop has complementary clock signals making one active while the other is not. The state of the flip flop, Q, is updated on the falling edge of the clock signal. The basic components that comprise this flip flop are inverters, nand gates, and nor gates. The design of this flip flop uses a process of 0.3 m. The length for all transistors in this design was 0.6 m. The width for all transistors, for simplicity, was to 3.0 m. II. LOGIC The flip flops logic table was manipulated to include a set, reset, and enable option. Karnaugh maps were used to minimize the number of gates to include these options. The set and reset inputs basically override the J and K inputs. The enable input basically enabled the clock signal to pass through to the flip flop for it to operate correctly, hence enable.

When E = 0, the flip flop is no longer active, so that truth table is omitted. If S = 1, Qnext = 1 or if R = 1, Qnext = 1 regardless of the other inputs so those truth tables were omitted as well. The Set and Reset inputs cannot both be logic 1 simultaneously. If Set and Reset both equal logic 1, then output states are undetermined. The truth tables for the individual components of the flip flop are below. Inverter gate: IN 0 1 OUT 1 0 Three-Input NAND gate: A 0 0 0 0 1 1 1 1 Two-Input NAND gate: A 0 0 1 1 B 0 1 0 1 OUT 1 1 1 0 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 OUT 1 1 1 1 1 1 1 0

Two-Input NOR gate: A 0 0 1 1 B 0 1 0 1 OUT 1 0 0 0

2 III. SCHEMATICS & LAYOUT Twenty-one gates, in total, were used in this design of a JK flip flop. There were 8 inverters, 2 nor gates, 9 two-input nand gates, and 2 three-input nand gates. Since there are several schematics associated with the components and the flip flop itself, they have been appended to the end of this report. See Appendix A for the screen captures of the schematics used for the JK flip flop and of each of the components. The layouts for the individual components have been omitted from this report. For a screenshot of the layout for the entire flip flop, see Appendix B. The padframe including the pin names can also be found in Appendix B.

IV. SIMULATION The output waveforms along with the test schematic for the flip flop can be found in Appendix C. The waveform matches the expected truth table for a general JK flip flop. The flip flop was simulated with the software used to create it. Three different graphs were generated with the results. Rise time, fall time, and total delay were plotted against a load capacitance from 1 pF to 5 pF. The results seem reasonable considering the times increased as load capacitance increased. The waveforms illustrating the rise and fall times can be found in Appendix D. Below are the graphs showing the collected data.

V. CONCLUSION After many hours of design and troubleshooting, the JK flip flop worked correctly. It was interesting to experience the basic process of building a microchip from beginning to end (with the exception of the fabrication).

VI. APPENDICES (A D)

Appendix A:

JK Flip Flop Schematic:

Inverter Gate Schematic:

Three-input NAND Gate Schematic:

Two-input NOR Gate Schematic:

Two-input NAND Gate Schematic:

Appendix B:

JK Flip Flop Layout:

Padframe with Pin Labels (top side is this design):

Appendix C:

Test Schematic for JK Flip Flop:

Waveform of Output of JK Flip Flop:

Appendix D:

Rise Time Waveform (increasing load capacitance):

Fall Time Waveform (increasing load capacitance):

Das könnte Ihnen auch gefallen

- 2Dokument8 Seiten2Eduardo Antonio Comaru Gouveia75% (4)

- D Flipflop T Flipflop by VerilogDokument4 SeitenD Flipflop T Flipflop by Verilogtungbk12375% (4)

- Activity 3.1.1 Sequential Logic - D Flip-Flops and JK Flip-Flops PDFDokument5 SeitenActivity 3.1.1 Sequential Logic - D Flip-Flops and JK Flip-Flops PDFChris Ronald CherestalNoch keine Bewertungen

- Csir Life Sciences Fresh Instant NotesDokument4 SeitenCsir Life Sciences Fresh Instant NotesAlps Ana33% (3)

- Colfax MR Series CompresorDokument2 SeitenColfax MR Series CompresorinvidiuoNoch keine Bewertungen

- ET398 LAB 6 "Flip-Flops in VHDL" (PDFDrive)Dokument19 SeitenET398 LAB 6 "Flip-Flops in VHDL" (PDFDrive)kaesarsabahNoch keine Bewertungen

- Digital LabDokument51 SeitenDigital LabBala SubramanianNoch keine Bewertungen

- Digital Design On Digital Works.Dokument25 SeitenDigital Design On Digital Works.nileshchaurasiaNoch keine Bewertungen

- Experiment 9 (Flip Flops)Dokument7 SeitenExperiment 9 (Flip Flops)groupidb3100% (3)

- A3 1 1IntroductionFlipFlopsDokument5 SeitenA3 1 1IntroductionFlipFlopsGoran MateiaseviciNoch keine Bewertungen

- Search For DocumentsDokument9 SeitenSearch For DocumentsdineshvhavalNoch keine Bewertungen

- Lab 1 PDFDokument20 SeitenLab 1 PDFNur HidayahNoch keine Bewertungen

- D and JK FFDokument22 SeitenD and JK FFRawan AyyoubNoch keine Bewertungen

- DLD Exp 8 Student ManualDokument8 SeitenDLD Exp 8 Student ManualS M AkashNoch keine Bewertungen

- T Flip FlopDokument2 SeitenT Flip FlopArka KhatuaNoch keine Bewertungen

- Unit 3Dokument24 SeitenUnit 3Raja BenitaNoch keine Bewertungen

- Lab 5 - FlipflopDokument34 SeitenLab 5 - Flipflopgokul sNoch keine Bewertungen

- American International University-Bangladesh: Title: Study of Different Flip-FlopsDokument7 SeitenAmerican International University-Bangladesh: Title: Study of Different Flip-FlopsAbid ChowdhuryNoch keine Bewertungen

- The J-K Flip Flop: ObjectivesDokument2 SeitenThe J-K Flip Flop: ObjectivesALviNoch keine Bewertungen

- DS - Expt 10Dokument6 SeitenDS - Expt 10Aditya SalunkheNoch keine Bewertungen

- COA Chap 123Dokument46 SeitenCOA Chap 123desNoch keine Bewertungen

- Lab Manual 8085 MicroprocessorDokument43 SeitenLab Manual 8085 MicroprocessorManvendra Singh0% (1)

- ECET 105 Week 7 Lab Project Detailed DirectionsDokument14 SeitenECET 105 Week 7 Lab Project Detailed DirectionsMicro EmissionNoch keine Bewertungen

- Arithmetic and Logic (Cont) : 2.3 Build Sequential Logic CircuitDokument22 SeitenArithmetic and Logic (Cont) : 2.3 Build Sequential Logic CircuitBadrul Afif ImranNoch keine Bewertungen

- Laboratory Manual Course Code:Ece 201Dokument41 SeitenLaboratory Manual Course Code:Ece 201Er Sacchu SrivastavaNoch keine Bewertungen

- Lab 1 ReportDokument12 SeitenLab 1 ReportHarining TyasNoch keine Bewertungen

- Lab 8 - LatchesDokument5 SeitenLab 8 - LatchesSiegrique Ceasar A. JalwinNoch keine Bewertungen

- Study of Flip Flops Using ICsDokument5 SeitenStudy of Flip Flops Using ICssaravanan_12aNoch keine Bewertungen

- SC1005 Tutorial 8Dokument1 SeiteSC1005 Tutorial 802chng.jiadeNoch keine Bewertungen

- Lab05 Flip FlopsDokument8 SeitenLab05 Flip Flopskhanjamil12Noch keine Bewertungen

- Latches and Flip-Flops: Experiment E10Dokument9 SeitenLatches and Flip-Flops: Experiment E10Resy ApolinarioNoch keine Bewertungen

- Flip FlopsDokument60 SeitenFlip FlopsA10-14Rajat KumarNoch keine Bewertungen

- ECE 301 - Digital Electronics: Flip-Flops and RegistersDokument36 SeitenECE 301 - Digital Electronics: Flip-Flops and RegistersDivya SoundarajanNoch keine Bewertungen

- VCLASS-2 M5 Perc Sintetik-28102020Dokument10 SeitenVCLASS-2 M5 Perc Sintetik-28102020Fatah Nur HidayatNoch keine Bewertungen

- Computer Organization: Semester 3Dokument25 SeitenComputer Organization: Semester 3lalit sainiNoch keine Bewertungen

- Flip Flop PracticalDokument9 SeitenFlip Flop PracticalhimanshuNoch keine Bewertungen

- Ofc Lab Manual 2Dokument21 SeitenOfc Lab Manual 2Shobhit JainNoch keine Bewertungen

- Report 1 (D2, Digital)Dokument10 SeitenReport 1 (D2, Digital)Kian YingNoch keine Bewertungen

- DLC LAB - 06 - Student - ManualDokument8 SeitenDLC LAB - 06 - Student - Manualrk refatNoch keine Bewertungen

- JK Flip Flop Experiment 9Dokument5 SeitenJK Flip Flop Experiment 9Nev Callejo50% (2)

- Name of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabDokument7 SeitenName of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabAurongo NasirNoch keine Bewertungen

- Demp Lab ManualDokument50 SeitenDemp Lab ManualNishant AcharyaNoch keine Bewertungen

- Lab Manual FOR Computer Organization LabDokument13 SeitenLab Manual FOR Computer Organization Labhifzan786Noch keine Bewertungen

- 1.1.6.a Componentidentification DigitalDokument7 Seiten1.1.6.a Componentidentification DigitalomNoch keine Bewertungen

- Lab 11 Digital JK FlipflopDokument5 SeitenLab 11 Digital JK Flipflopzk7766100% (1)

- BBDokument2 SeitenBBsuraj tarapureNoch keine Bewertungen

- UntitledDokument8 SeitenUntitledlalita chauhanNoch keine Bewertungen

- D Flip-FlopDokument35 SeitenD Flip-FlopSwati Kasht100% (1)

- DCS-2 Practical File Part-1Dokument26 SeitenDCS-2 Practical File Part-1ykr007Noch keine Bewertungen

- 4 Bit Counter Design - Spring 2004Dokument15 Seiten4 Bit Counter Design - Spring 2004sandyk_24Noch keine Bewertungen

- Group 8 Adc Experiment 5-1Dokument17 SeitenGroup 8 Adc Experiment 5-1ROHAN NAGRUTNoch keine Bewertungen

- SN1-2223-Lab3 1-2 EngDokument4 SeitenSN1-2223-Lab3 1-2 EngBoualem MestafaNoch keine Bewertungen

- MOSIS Counter Report Spring 2008Dokument60 SeitenMOSIS Counter Report Spring 2008atom_2334Noch keine Bewertungen

- PLDTUTORDokument13 SeitenPLDTUTORAjay Nath S ANoch keine Bewertungen

- Project ReportDokument11 SeitenProject Reportamiethurgat100% (2)

- CounterDokument22 SeitenCounterMahesh MahiNoch keine Bewertungen

- Exp 4Dokument14 SeitenExp 4Cherry Charan TejNoch keine Bewertungen

- Exper6 - 2012 D-Type JK-type Flip-FlopsDokument4 SeitenExper6 - 2012 D-Type JK-type Flip-FlopsMELANIE LLONANoch keine Bewertungen

- Chp1 - Latches and Flip-FlopsDokument44 SeitenChp1 - Latches and Flip-FlopsAbnen OngNoch keine Bewertungen

- Java NotesDokument37 SeitenJava NotesSandeep Kumar mehtaNoch keine Bewertungen

- Co Lab ManualDokument22 SeitenCo Lab ManualSachin Saxena100% (2)

- MSDFFDokument20 SeitenMSDFFShweta KumariNoch keine Bewertungen

- Anais Do Workshop De Micro-ondasVon EverandAnais Do Workshop De Micro-ondasNoch keine Bewertungen

- Session 1Dokument18 SeitenSession 1Akash GuptaNoch keine Bewertungen

- Hanwha Q Cells Data Sheet Qpeak L-g4.2 360-370 2017-10 Rev02 NaDokument2 SeitenHanwha Q Cells Data Sheet Qpeak L-g4.2 360-370 2017-10 Rev02 NazulfikarNoch keine Bewertungen

- 19 Dark PPT TemplateDokument15 Seiten19 Dark PPT TemplateKurt W. DelleraNoch keine Bewertungen

- Dialectical Relationship Between Translation Theory and PracticeDokument5 SeitenDialectical Relationship Between Translation Theory and PracticeEverything Under the sunNoch keine Bewertungen

- Dry Compressing Vacuum PumpsDokument62 SeitenDry Compressing Vacuum PumpsAnonymous zwSP5gvNoch keine Bewertungen

- Lacey Robertson Resume 3-6-20Dokument1 SeiteLacey Robertson Resume 3-6-20api-410771996Noch keine Bewertungen

- Pioneer 1019ah-K Repair ManualDokument162 SeitenPioneer 1019ah-K Repair ManualjekNoch keine Bewertungen

- OT Initial Assessment (OTIA) 2022-11-15Dokument2 SeitenOT Initial Assessment (OTIA) 2022-11-15funtikarNoch keine Bewertungen

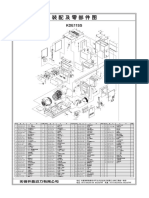

- KDE11SSDokument2 SeitenKDE11SSluisgomezpasion1Noch keine Bewertungen

- 8 A - 1615864446 - 1605148379 - 1579835163 - Topic - 8.A.EffectiveSchoolsDokument9 Seiten8 A - 1615864446 - 1605148379 - 1579835163 - Topic - 8.A.EffectiveSchoolsYasodhara ArawwawelaNoch keine Bewertungen

- Geotechnical PaperDokument16 SeitenGeotechnical PaperTxavo HesiarenNoch keine Bewertungen

- 4.2.4.5 Packet Tracer - Connecting A Wired and Wireless LAN InstructionsDokument5 Seiten4.2.4.5 Packet Tracer - Connecting A Wired and Wireless LAN InstructionsAhmadHijaziNoch keine Bewertungen

- Practice Problems - Electrochemical CellDokument5 SeitenPractice Problems - Electrochemical CellYehia IbrahimNoch keine Bewertungen

- Mushroom Project - Part 1Dokument53 SeitenMushroom Project - Part 1Seshadev PandaNoch keine Bewertungen

- Culture 2007 2013 Projects Overview 2018-03-18Dokument133 SeitenCulture 2007 2013 Projects Overview 2018-03-18PontesDeboraNoch keine Bewertungen

- SG110CX: Multi-MPPT String Inverter For SystemDokument2 SeitenSG110CX: Multi-MPPT String Inverter For SystemKatherine SmithNoch keine Bewertungen

- SEILDokument4 SeitenSEILGopal RamalingamNoch keine Bewertungen

- 18-MCE-49 Lab Session 01Dokument5 Seiten18-MCE-49 Lab Session 01Waqar IbrahimNoch keine Bewertungen

- ..Product CatalogueDokument56 Seiten..Product Catalogue950 911Noch keine Bewertungen

- Central University of Karnataka: Entrance Examinations Results 2016Dokument4 SeitenCentral University of Karnataka: Entrance Examinations Results 2016Saurabh ShubhamNoch keine Bewertungen

- Vitamins - CyanocobalaminDokument12 SeitenVitamins - CyanocobalaminK PrashasthaNoch keine Bewertungen

- Plastic Properties HandbookDokument15 SeitenPlastic Properties HandbookguilloteARGNoch keine Bewertungen

- Imabalacat DocuDokument114 SeitenImabalacat DocuJänrëýMåmårìlSälängsàngNoch keine Bewertungen

- Theorising Mobility Justice-Mimi ShellerDokument18 SeitenTheorising Mobility Justice-Mimi Shellerjllorca1288Noch keine Bewertungen

- Smartfind E5 g5 User ManualDokument49 SeitenSmartfind E5 g5 User ManualdrewlioNoch keine Bewertungen

- Noise and DB Calculations: Smart EDGE ECE Review SpecialistDokument2 SeitenNoise and DB Calculations: Smart EDGE ECE Review SpecialistLM BecinaNoch keine Bewertungen

- 2nd Term Project 4º Eso Beauty Canons 2015-16 DefinitivoDokument2 Seiten2nd Term Project 4º Eso Beauty Canons 2015-16 DefinitivopasferacosNoch keine Bewertungen