Beruflich Dokumente

Kultur Dokumente

International Journal of Computational Engineering Research (IJCER)

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

International Journal of Computational Engineering Research (IJCER)

Copyright:

Verfügbare Formate

International Journal of Computational Engineering Research||Vol, 03||Issue, 6||

THD Minimization of a Cascaded Nine Level Inverter Using Sinusoidal PWM and Space Vector Modulation

G.Lavanya1, N.Muruganandham2

1

Assistant Professor-EEE, IFET College of Engineering, Villupuram, Tamilnadu, Email: 2 Project Engineer, Aeon Automation Solutions, Chidambaram, Tamilnadu, India.

ABSTRACT:

Multi-level inverters offer several advantages such as a better output voltage with reduced total harmonic distortion (THD), reduction of voltage ratings of the power semiconductor switching devices and also the reduced electro-magnetic interference problems etc. Multilevel inverters synthesis the AC output voltages from various DC voltages. Space Vector Modulation (SVM) is one of the most popular PWM techniques used in multilevel inverters. SVM provides a best space vector performance, sequences of different space vectors suitable for voltage source inverter is identified. In this paper a 9 level cascaded H-bridge inverter model for space vector PWM is established and simulated using MATLAB/SIMULINK software and its performance is compared with sinusoidal PWM. The simulation study reveals that space vector PWM utilizes dc bus voltage more effectively and generates less THD when compared with sine PWM.

KEYWORDS: Multilevel Inverters, THD, Sinusoidal Pulse Width Modulation (SPWM), Space Vector

PWM.

I.

INTRODUCTION

The multilevel inverters have drawn tremendous interest in the power industry that is well suited for use in reactive power compensation. The increasing number of energy sources and controlled AC drives requires new strategies for the operation and management of the electricity grid in order to maintain or even to improve the power supply reliability and quality [1]. Controlled AC drives in the megawatt range are usually connected to the medium-voltage network. For these reasons, a new family of multilevel inverters has emerged as the solution for working with higher voltage levels [2]. These inverters are suitable in high-voltage and highpower applications due to their ability to synthesize waveforms with better harmonic spectrum and attain higher voltages with a limited maximum device rating [3], the increased power ratings and reduced electromagnetic interference (EMI) emission that can be achieved with the multiple DC levels that are available for synthesis of the output voltage waveforms [4].Pulse-width modulation (PWM) techniques are gaining importance to control the multilevel inverters for multi megawatt industrial applications, recently. The output voltage waveforms of the multilevel inverters can be generated at low switching frequencies with high efficiency, low distortion and also harmonics are shifted towards higher frequency bands. Many of the PWM techniques have been developed to achieve the following advantages [6]: wide linear modulation range, less switching losses, less total harmonic distortion (THD) in the spectrum of switching waveform, Easy implementation and less computation time. One of the most popular PWM techniques in the multilevel inverters is Space Vector Pulse Width Modulation (SVPWM). It was originally developed as a vector approach to PWM for three-phase inverters. Typical claims made for SVPWM include the following [7]: It achieves the wide linear modulation range associated with PWM third-harmonic injection automatically, without the need for distorted modulation. It has lower baseband harmonics than regular PWM or other sine based modulation methods optimizes harmonics. Only one switch changes state at a time. It is fast and convenient to compute.

www.ijceronline.com ||June||2013|| Page 34

Thd Minimization Of A Cascaded Nine Level Inverter II. MULTILEVEL INVERTER

Multilevel inverters easily produce high-power, high voltage output with the multilevel structure because of the way in which device voltage stresses are controlled in the structure. Increasing the number of voltage levels in the inverter, without requiring higher ratings on individual devices, can increase the power rating. The unique structure of multilevel voltage source inverters allows them to reach high voltages with low harmonics without the use of transformers or series-connected synchronized switching devices. As the number of voltage levels increases, the harmonic content of the output voltage decreases significantly [6],[10],[11]. The multilevel inverters synthesize a near sinusoidal voltage from several levels of DC voltages. As the number of levels increases, the output has more steps, resembling a staircase wave that approaches a desired waveform. The harmonic content of the output decreases as the number of levels increases [6], [12]. As the number of levels increases, the output voltage that can be spanned by summing multiple voltage levels also increases [12], [7], [8]. The multilevel inverter can be classified into three types: i) diode clamped multilevel inverter ii) flying capacitors multilevel inverters and iii) cascaded multilevel inverter.

Fig. 1 configuration of cascaded m level inverter Fig. 1 shows the configuration of cascaded multilevel inverter, the full bridge configuration with a separate DC source, which may be batteries, fuel cells or solar cells and are connected in series [5],[9]. Each full bridge inverter (FBI) unit can generate a three level output: +Vdc, 0 or Vdc by connecting the DC source to the AC load side by different combinations of the four switches S1, S2, S3 and S4.Using the top level as the example, turning on S1 and S4 yields +Vdc output. Turning on S2 and S3 yields -Vdc output. Turning off all switches yields 0 volts output. The AC output voltage at other levels can be obtained in the same manner. The number of voltage levels at the load generally defines the number of FBIs in cascade. If N is the number of DC sources, the number of output voltage levels is m=2N+1. The number of FBI units N is (m-1)/2 where m is the sum of the number of positive, negative and zero levels in multilevel inverter output. The number of converters N also depends on: 1) the injected voltage and current harmonic distortion requirements 2) the magnitude of the injected voltage required and 3) the available power switch voltage ratings [8]. The chosen inverter structure is simple since no real power needs to be supplied other than the losses. The DC sources are floating and no transformer is required for coupling to the transmission system. For each FBI unit, the current rating is the nominal current of the transmission system. The AC load rating and therefore the DC source rating depend upon the total compensation voltage required, the number of converters and the sharing of the load voltage among individual units. The main features of cascaded multilevel inverters are: For real power conversions from DC to AC, the cascaded inverters need separate DC sources. The structure of separate DC sources is well suited for various renewable energy sources such as fuel cell, photovoltaic and biomass. Least number of components is required to achieve the same number of voltage levels. Optimized circuit layout and packaging are possible Soft-switching techniques can be used to reduce switching losses and device stresses. The modular structure of the inverter leads to advantages in terms of manufacturing and flexibility of application.

www.ijceronline.com

||June||2013||

Page 35

Thd Minimization Of A Cascaded Nine Level Inverter III. SPACE VECTOR MODULATION

Space Vector Modulation (SVM) is quite different from PWM methods. It is a more sophisticated technique for generating sine wave that provides a higher voltage to the motor with lower total harmonic distortion. Space Vector PWM (SVPWM) method is an advanced; computation intensive PWM method and possibly the best techniques for variable frequency drive application. The circuit model of a typical three-phase inverter is shown in Fig. 2. S1 to S6 are the six power switches that shape the output, which are controlled by the switching variables a, a, b, b, c and c. When an upper switch is switched on, i.e., when a, b or c is 1, the corresponding lower tran sistor is switched off, i.e., the corresponding a, b or c is 0. Therefore, the on and off states of the upper switch S1, S3 and S5 can be used to determine the output voltage. SVPWM is a different approach from PWM modulation.

S1 S3 S5

S4

S6

S2

Fig. 2 Typical Three-Phase Inverter In this modulation technique the three phase quantities can be transformed to their equivalent two-phase quantity either in synchronously rotating frame (or) stationary frame. From these two-phase components, the reference vector magnitude can be found and used for modulating the inverter output. The process of obtaining the rotating space vector is explained in the following section, considering the stationary reference frame. 3.1 Switching states of space vector modulation

Fig. 3 Relationship of abc and dq reference frame Considering the stationary reference frame let the three-phase sinusoidal voltage component be, Va = Vm sint (1) Vb = Vm sin (t-2/3) (2) Vc = Vm sin (t+2/3) (3) The - components are found by Clarks transformation. Space Vector Modulation refers to a special switching sequence of the upper three power transistors of a three-phase power inverter. The stationary dq reference frame that consists of the horizontal (d) and vertical (q) axes as depicted in Fig.3. From Fig. 3, the relation between these two reference frames is below Vdq0 = Ks Vabc (4)

(5)

Vdqo = [VdVqVo]T & Vabc = [VaVbVc]T

(6)

In fig.3 this transformation is equivalent to orthogonal projection [a b c] T onto the two dimensional vector perpendicular to the vector [1 1 1]T in a three dimensional system. Six non-zero vectors and two zero vectors are depicted. Six non-zero vectors (V1-V6) shape the axes of a hexagonal as in Fig.4, and supplies power to the load. The angle between any adjacent two non-zero vectors is 60 degrees.

www.ijceronline.com ||June||2013|| Page 36

Thd Minimization Of A Cascaded Nine Level Inverter

Meanwhile, two zero vectors (V0 and V7) and are at the origin and apply zero voltage to the load. The eight vectors are called the basic space vectors and are denoted by (V0,V1,V2,V3,V4,V5,V6,V7). The same transformation can be applied to the desired output voltage to get the desired reference voltage vector, Vref in the d-q plane. The objective of SVM technique is to approximate the reference voltage vector V ref using the eight switching patterns. One simple method of approximation is to generate the average output of the inverter in a small period T to be the same as that of Vref in the same period. 6 active vectors are (V1,V2,V3,V4,V5,V6). DC link voltage is supplied to the load. Each sector (1 to 6): 60 degrees. Two zero vectors are (V0 and V7). They are located at origin. No voltage is supplied to the load.

Fig .4 basic switching vectors and sectors

For 180 mode of operation, there exist six switching states and additionally two more states, which make all three switches of either upper arms or lower arms ON. To code these eight states in binary (one-zero representation), it is required to have three bits (2 3 = 8). And also, as always upper and lower switches are commutated in complementary fashion, it is enough to represent the status of either upper or lower arm switches. Table-1 Switch states for three phase inverter Voltage Vectors Vo V1 V2 V3 V4 V5 V6 V7 Switching Vectors a 0 1 1 0 0 0 1 1 b 0 0 1 1 1 0 0 1 c 0 0 0 0 1 1 1 1 Line to neutral voltage Van 0 2/3 1/3 -1/3 -2/3 -1/3 1/3 0 Vbn 0 -1/3 1/3 2/3 1/3 -1/3 -2/3 0 Vcn 0 -1/3 -2/3 -1/3 1/3 2/3 1/3 0 Line to line voltage Vab 0 1 0 -1 -1 0 1 0 Vbc 0 0 1 1 0 -1 -1 0 Vca 0 -1 -1 0 1 1 0 0

S1 through S6 are the six power transistors that shape the output voltage. When an upper switch is turned on (i.e., a, b or c is 1), the corresponding lower switch is turned off (i.e., a', b' or c' is 0).Eight possible combinations of on and off patterns for the three upper transistors (S1, S3, S5) are possible.

IV.

SIMULATION RESULTS

The main aim of any modulation technique is to obtain variable output having maximum fundamental component with minimum harmonics. The objective of Pulse Width Modulation techniques is enhancement of fundamental output voltage and reduction of harmonic content in Three Phase Voltage Source Inverters. In this paper different PWM techniques are compared in terms of Total Harmonic Distortion (THD). Simulink Models has been developed for SPWM, SVPWM, and the Simulation work is carried in MATLAB /Simulink.

www.ijceronline.com ||June||2013|| Page 37

Thd Minimization Of A Cascaded Nine Level Inverter

4.1 Simulation Sinusoidal PWM In Sinusoidal PWM three phase reference modulating signals are compared against a common triangular carrier to generate the PWM signals for the three phases. Fig.5 shows the Simulink of cascaded nine level inverter with sinusoidal pulse width modulation scheme. Simulation has been carried out by varying the modulation index between 0 and 1.

Fig.5 Simulink of cascaded nine level inverter with SPWM 4.2 Simulation Space vector modulation Space vector PWM is an advanced technique used for variable frequency drive applications. It utilizes dc bus voltage more effectively and generates less THD in the Cascaded H Bridge Inverter. SVPWM utilize a chaotic changing switching frequency to spread the harmonics continuously to a wide band area so that the peak harmonics can be reduced greatly. Figs.6 and 7 shows the Simulink of cascaded nine level inverter with space vector pulse width modulation scheme and switching strategy of SVPWM. Simulation has been carried out by varying the modulation index between 0 and 1.

Fig.6 Simulink of cascaded nine level inverter with SVPWM

.4 m pi/2 delta

Scope4

f(u) Va_ref f(u) Vb_ref f(u) Vc_ref

a b c sector mag theta1 mag Vq0 theta1 Vq0

sector

a phase

gating signals

1

s/w state selector Vd0 Vd0 s/w state selector

abc -> mag + local theta1

<= 1e-005

S/H pulse

2 Constant

b phase

Out1

local vector gen.

Ts-pulse

gating signal generator

-C-Cc phase

state selector

Scope6

0 [1x4]

Fig.7 Simulink of cascaded nine level inverter with SVPWM switching strategy

www.ijceronline.com ||June||2013||

Page 38

Thd Minimization Of A Cascaded Nine Level Inverter

Fig.8. FFT and THD analysis of cascaded nine level inverter using SPWM with m a=0.8

Fig.9. FFT and THD analysis of cascaded nine level inverter using SVPWM with m a=0.8 Table-2 Comparisons between SPWM and SVPWM by varying modulation index (For 9 level cascaded H- bridge inverter) Technique Sinusoidal PWM THD (%) 148.57 121.60 69.01 61.56 Space Vector PWM Output line voltage (volts) 61.45 83.74 100.40 123.00 THD (%) 1.57 1.25 1.07 0.92 Modulation Index (M) Output line voltage (volts) 0.4 57.60 0.6 0.8 1.0 65.70 90.27 117.80

www.ijceronline.com

||June||2013||

Page 39

Thd Minimization Of A Cascaded Nine Level Inverter V. CONCLUSION

Space vector Modulation Technique has become the most popular and important PWM technique for Three Phase Voltage Source Inverters. In this paper first comparative analysis of Space Vector PWM with conventional SPWM for a 9 level Inverter is carried out. The Simulation study reveals that SVPWM gives 0.92% enhanced fundamental output with better quality i.e. lesser THD compared to SPWM. Space vector Modulation Technique has become the most popular and important PWM technique for Three Phase Inverters. In this paper first comparative analysis of Space Vector PWM with conventional SPWM for a 9 level Inverter is carried out. The Simulation study reveals that SVPWM gives 0.92% enhanced fundamental output with better quality i.e. lesser THD compared to SPWM. PWM strategies viz. SPWM and SVPWM are implemented in MATLAB/SIMULINK software and its performance is compared with conventional PWM techniques.

REFERENCES

[1] J.M. Carrasco, L.G. Franquelo, J.T. Bialasiewicz, E. Galvan, R.C.P. Guisado, M.A.M.Prats, J.I. Leon, N. Moreno-Alfonso, Power-electronic systems for the grid integration of renewable energy sources: a survey, IEEE Transactions on Industrial Electronics (2006) 1002 1016. J. Rodriguez, J.S. Lai, F.Z. Peng, Multilevel inverters: a survey of topologies, controls and applications, IEEE Transactions on Industrial Electronics 49 (2002) 724738. M.D. Manjrekar, P.K. Steimer, T.A. Lipo, Hybrid multilevel power conversion system: a competitive solution for high-power applications, Industry Applications Conference 3 (1999) 15201527. L.P. Chiang, D.G. Holmes, T.A. Lipo, Implementation and control of distributed PWM cascaded multilevel inverters with minimal harmonic distortion and common-mode voltage, IEEE Transactions on Power Electronics 20 (2005) 9099. G.C.Cho, N.S. Choi, C.T.Rim and G.H.Cho, Modelling and control of a static VAR compensator using an inverter topology, IEEE Trans. Power Electonics, vol. 10, no.1, Jan. 1995. P.Moore and P.Ashmole, Flexible AC transmission systems - part 4: advanced FACTS controllers, IEE Power Eng., pp 95-100, Apr.1998. S.Mori, K.Matsuno, M.Takeda and M.Seto Development of a large static VAR generation using self-commuted inverters for improving power system stability, IEEE Trans. Power system, vol. 8, pp 371- 377, Feb 1993. A.Nabae, I.Takahashi and H.Akagi, A new neutral point clamped PWM inverter, IEEE. Transaction on Industry Applications, vol .17, no. 5, pp 518-523, Sep/Oct 1981. F.Z.Peng and J.S.Lai, Dynamic performance and control of a staticVAR generator using cascade multilevel inverter , IEEE Trans Ind. Applications, vol 33, pp 748-755, May/June 1997. F.Z.Peng, J.S.Lai, J.W.Mckeever and J.Vancovering, A multilevel voltage source inverter with separate DC sources for static VAR generation, IEEE Trans. Ind. Applications,vol. 32, pp 1130-1148, Sep/Oct 1996. N.G.Hingorani and L.Gyugyi, Understanding FACTS, Piscataway NJ, IEEE Press, 2000. M.H.Rashid, Power Electronics: circuits, devices and applications, Prentice-Hall, USA, Second edition, 1993. delivery,vol. 8, no. 3, July 1993 and design. New York: John Wiley & Sons Inc.; 1995.

[2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12]

www.ijceronline.com

||June||2013||

Page 40

Das könnte Ihnen auch gefallen

- Multicarrier - Based PWM Control Strategies For Five - Level CMLIDokument7 SeitenMulticarrier - Based PWM Control Strategies For Five - Level CMLIDharani DeviNoch keine Bewertungen

- Unipolar and Bipolar SPWM Voltage Modulation Type Inverter For Improved SwitchingDokument5 SeitenUnipolar and Bipolar SPWM Voltage Modulation Type Inverter For Improved SwitchingOdnamra AlvarezNoch keine Bewertungen

- Improving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshDokument5 SeitenImproving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshsarathNoch keine Bewertungen

- New Multilevel Inverter Topology With Reduced Number of SwitchesDokument6 SeitenNew Multilevel Inverter Topology With Reduced Number of SwitchesVikram PrasadNoch keine Bewertungen

- Modulation Techniques For Matrix ConvertersDokument7 SeitenModulation Techniques For Matrix Convertersdheerajkumar02527289Noch keine Bewertungen

- Simulation & Implementation of Three Phase Induction Motor On Single Phase by Using PWM TechniquesDokument12 SeitenSimulation & Implementation of Three Phase Induction Motor On Single Phase by Using PWM TechniquesMallikarjunBhiradeNoch keine Bewertungen

- An Analysis and Survey of Multilevel Inverters Topologies, Controls, and ApplicationsDokument10 SeitenAn Analysis and Survey of Multilevel Inverters Topologies, Controls, and ApplicationsDr-Ismayil CNoch keine Bewertungen

- Discontinuous PWM Techniques For Open-End Winding Induction Motor Drive For Zero Sequence Voltage EliminationDokument13 SeitenDiscontinuous PWM Techniques For Open-End Winding Induction Motor Drive For Zero Sequence Voltage EliminationarunkmepesNoch keine Bewertungen

- Low Cost Digital Signal Generation For Driving Space Vector PWM InverterDokument12 SeitenLow Cost Digital Signal Generation For Driving Space Vector PWM InverterJunaid AhmadNoch keine Bewertungen

- International Journal of Engineering Research and DevelopmentDokument7 SeitenInternational Journal of Engineering Research and DevelopmentIJERDNoch keine Bewertungen

- Iceict2015i020315001 PDFDokument6 SeitenIceict2015i020315001 PDFmadihaNoch keine Bewertungen

- Switching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor DriveDokument6 SeitenSwitching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor Drivevinay kumarNoch keine Bewertungen

- Multi-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LDokument6 SeitenMulti-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LveguruprasadNoch keine Bewertungen

- Multistring Five-Level Inverter With Novel PWMDokument13 SeitenMultistring Five-Level Inverter With Novel PWMsandeepbabu28Noch keine Bewertungen

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerDokument12 SeitenDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaNoch keine Bewertungen

- Seven Level Inverter With Nearest Level ControlDokument7 SeitenSeven Level Inverter With Nearest Level Controlsanjay sNoch keine Bewertungen

- Implementation of 11 Level Cascaded Multilevel Inverter Using Level Shifting Pulse Width Modulation Technique With Different LoadsDokument12 SeitenImplementation of 11 Level Cascaded Multilevel Inverter Using Level Shifting Pulse Width Modulation Technique With Different LoadsInternational Journal of Application or Innovation in Engineering & ManagementNoch keine Bewertungen

- Cascaded 5-Level Inverter Type Dstatcom For Power Quality ImprovementDokument5 SeitenCascaded 5-Level Inverter Type Dstatcom For Power Quality ImprovementSiri SarojaNoch keine Bewertungen

- Simulation of Cascaded H-Bridge Multilevel Inverter Using OHSW PWM For The Elimination of HarmonicsDokument14 SeitenSimulation of Cascaded H-Bridge Multilevel Inverter Using OHSW PWM For The Elimination of HarmonicsBib SaNoch keine Bewertungen

- Performance Analysis of Multi-Level Inverter For Dynamic Voltage RestorerDokument6 SeitenPerformance Analysis of Multi-Level Inverter For Dynamic Voltage Restorersup9Noch keine Bewertungen

- Electrical - Ijeeer - 16 - Cell Back-To-back - NaveenaDokument12 SeitenElectrical - Ijeeer - 16 - Cell Back-To-back - NaveenaTJPRC PublicationsNoch keine Bewertungen

- Mali 2019Dokument7 SeitenMali 2019aymenNoch keine Bewertungen

- Three Phase Current Source Inverter Using Space Vector PWM For Grid Connected ApplicationsDokument4 SeitenThree Phase Current Source Inverter Using Space Vector PWM For Grid Connected ApplicationstheijesNoch keine Bewertungen

- Total Harmonics Distortion Investigation in Multilevel InvertersDokument8 SeitenTotal Harmonics Distortion Investigation in Multilevel InvertersAJER JOURNALNoch keine Bewertungen

- A Survey On Neutral Point Clamped Multi Level InverterDokument12 SeitenA Survey On Neutral Point Clamped Multi Level InverterrupaNoch keine Bewertungen

- Design of Multi-Level Inverter and Its Application As Statcom To Compensate Voltage Sags Due To FaultsDokument6 SeitenDesign of Multi-Level Inverter and Its Application As Statcom To Compensate Voltage Sags Due To FaultsManpreet SinghNoch keine Bewertungen

- Comparative Study of MLI and Dual Inverter Using Space Vector Modulation TechniquesDokument8 SeitenComparative Study of MLI and Dual Inverter Using Space Vector Modulation Techniquesshiva256Noch keine Bewertungen

- Design of Microcontroller Based Multilevel InverterDokument4 SeitenDesign of Microcontroller Based Multilevel InverterInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- A Is (Facts) (SVG) ,: AbstractDokument9 SeitenA Is (Facts) (SVG) ,: AbstractSherif M. DabourNoch keine Bewertungen

- Ijeet: International Journal of Electrical Engineering & Technology (Ijeet)Dokument15 SeitenIjeet: International Journal of Electrical Engineering & Technology (Ijeet)Koukou AmkoukouNoch keine Bewertungen

- Unipolar and Bipolar SPWM Voltage Modula PDFDokument5 SeitenUnipolar and Bipolar SPWM Voltage Modula PDFĐorđe ĐurđićNoch keine Bewertungen

- A Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsDokument9 SeitenA Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsInternational Journal of Engineering Inventions (IJEI)Noch keine Bewertungen

- Research Paper A Novel Method For Near State Pulse Width Modulation (NSPWM) Based Chopper DrivesDokument4 SeitenResearch Paper A Novel Method For Near State Pulse Width Modulation (NSPWM) Based Chopper Drivesdivyamanikandan007Noch keine Bewertungen

- Space Vector Pulse Width ModulationDokument25 SeitenSpace Vector Pulse Width Modulationswathi_grenNoch keine Bewertungen

- Simulation and Comparison of SPWM and SVPWM Control For Two Level InverterDokument6 SeitenSimulation and Comparison of SPWM and SVPWM Control For Two Level InverterIkram RidhoNoch keine Bewertungen

- MultilevelDokument15 SeitenMultilevelsyfullahnelNoch keine Bewertungen

- Base Paper 7Dokument13 SeitenBase Paper 7Prince RohithNoch keine Bewertungen

- 2 Ijeeerfeb20182Dokument10 Seiten2 Ijeeerfeb20182TJPRC PublicationsNoch keine Bewertungen

- An Optimized Control Method Based On Dual Three-Level Inverters For Open-End Winding Induction Motor DrivesDokument9 SeitenAn Optimized Control Method Based On Dual Three-Level Inverters For Open-End Winding Induction Motor DrivesCharles KellyNoch keine Bewertungen

- Survey of CascadeDokument10 SeitenSurvey of Cascadesumiths32Noch keine Bewertungen

- 25 - Sinusoidal Pulse Width Modulation (SPWM) With Variable Carrier PDFDokument6 Seiten25 - Sinusoidal Pulse Width Modulation (SPWM) With Variable Carrier PDFDevendra HoleyNoch keine Bewertungen

- Simulation of Single Phase Multilevel Inverters With Simple Control Strategy Using MATLABDokument9 SeitenSimulation of Single Phase Multilevel Inverters With Simple Control Strategy Using MATLABFarman UllahNoch keine Bewertungen

- Design of Single Phase H-Bridge Multilevel Inverter Using Microcontroller Atmel 89c51Dokument52 SeitenDesign of Single Phase H-Bridge Multilevel Inverter Using Microcontroller Atmel 89c51Sabir VeNoch keine Bewertungen

- Matrix Converter For Two-Phase Induction Motor Application:Analysis, Modeling and SimulationDokument5 SeitenMatrix Converter For Two-Phase Induction Motor Application:Analysis, Modeling and SimulationbudNoch keine Bewertungen

- International Journal of Engineering Research and DevelopmentDokument7 SeitenInternational Journal of Engineering Research and DevelopmentIJERDNoch keine Bewertungen

- Single Phase H Bridge Multilevel InverterDokument52 SeitenSingle Phase H Bridge Multilevel Inverterskrtamil0% (1)

- Cascaded H Bridge Multilevel Inverter Modelling and SimulationDokument34 SeitenCascaded H Bridge Multilevel Inverter Modelling and SimulationPriyanka GuptaNoch keine Bewertungen

- Minimization of Total Harmonic Distortion Using Pulse Width TechniqueDokument12 SeitenMinimization of Total Harmonic Distortion Using Pulse Width TechniqueIOSRjournalNoch keine Bewertungen

- InvertersDokument8 SeitenInvertersJeffrey A PobladorNoch keine Bewertungen

- Optimum Space Vector PWM Algorithm For Three-Level Inverter: B. Urmila and D. Subba RayuduDokument13 SeitenOptimum Space Vector PWM Algorithm For Three-Level Inverter: B. Urmila and D. Subba RayudusureshonuNoch keine Bewertungen

- Introducing The Low Switching Frequency Space Vector Modulated Multi-Modular Three-Level Converters For High Power Applications Switching StrategiesDokument6 SeitenIntroducing The Low Switching Frequency Space Vector Modulated Multi-Modular Three-Level Converters For High Power Applications Switching StrategiesmaheshwareshwarNoch keine Bewertungen

- IJETR031989Dokument5 SeitenIJETR031989erpublicationNoch keine Bewertungen

- Identification of Optimal SVPWM Technique For MLI Fed Induction Motor DriveDokument6 SeitenIdentification of Optimal SVPWM Technique For MLI Fed Induction Motor DriveManu ThomasNoch keine Bewertungen

- 94 Jicr April 2023Dokument7 Seiten94 Jicr April 2023Phani RamNoch keine Bewertungen

- Single-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDokument9 SeitenSingle-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDeepak Kumar NayakNoch keine Bewertungen

- Implementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationDokument6 SeitenImplementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationseventhsensegroupNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- Power Systems-On-Chip: Practical Aspects of DesignVon EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Analysis of Metamaterial Based Microstrip Array AntennaDokument2 SeitenAnalysis of Metamaterial Based Microstrip Array AntennaInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- An Analysis of The Noise Level at The Residential Area As The Impact of Flight Operations at The International Airport of Sultan Hasanuddin Maros in South Sulawesi ProvinceDokument4 SeitenAn Analysis of The Noise Level at The Residential Area As The Impact of Flight Operations at The International Airport of Sultan Hasanuddin Maros in South Sulawesi ProvinceInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- The Effect of Bottom Sediment Transport On Wave Set-UpDokument10 SeitenThe Effect of Bottom Sediment Transport On Wave Set-UpInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Wave-Current Interaction Model On An Exponential ProfileDokument10 SeitenWave-Current Interaction Model On An Exponential ProfileInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Stiffness Analysis of Two Wheeler Tyre Using Air, Nitrogen and Argon As Inflating FluidsDokument8 SeitenStiffness Analysis of Two Wheeler Tyre Using Air, Nitrogen and Argon As Inflating FluidsInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Parametric Study On Analysis and Design of Permanently Anchored Secant Pile Wall For Earthquake LoadingDokument16 SeitenParametric Study On Analysis and Design of Permanently Anchored Secant Pile Wall For Earthquake LoadingInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Analysis of The Pedestrian System in Jayapura City (A Case Study of Pedestrian Line On Percetakan StreetDokument9 SeitenAnalysis of The Pedestrian System in Jayapura City (A Case Study of Pedestrian Line On Percetakan StreetInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- An Analysis of The Implementation of Work Safety System in Underpass Development Projects of The Intersection of Mandai Makassar-IndonesiaDokument5 SeitenAn Analysis of The Implementation of Work Safety System in Underpass Development Projects of The Intersection of Mandai Makassar-IndonesiaInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- A Real Time Abandoned Object Detection and Addressing Using IoTDokument5 SeitenA Real Time Abandoned Object Detection and Addressing Using IoTInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Parametric Study On Analysis and Design of Permanently Anchored Secant Pile Wall For Earthquake LoadingDokument16 SeitenParametric Study On Analysis and Design of Permanently Anchored Secant Pile Wall For Earthquake LoadingInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- The Influence of Price Offers For Procurement of Goods and Services On The Quality of Road ConstructionsDokument7 SeitenThe Influence of Price Offers For Procurement of Goods and Services On The Quality of Road ConstructionsInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- A Real Time Abandoned Object Detection and Addressing Using IoTDokument5 SeitenA Real Time Abandoned Object Detection and Addressing Using IoTInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Drag Optimization of Bluff Bodies Using CFD For Aerodynamic ApplicationsDokument8 SeitenDrag Optimization of Bluff Bodies Using CFD For Aerodynamic ApplicationsInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- The Influence of Price Offers For Procurement of Goods and Services On The Quality of Road ConstructionsDokument7 SeitenThe Influence of Price Offers For Procurement of Goods and Services On The Quality of Road ConstructionsInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Investigation of Vibration On Suspension Systems at Different Load and Operating ConditionsDokument5 SeitenInvestigation of Vibration On Suspension Systems at Different Load and Operating ConditionsInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Anatomy of The Traffic Accidents On The RoadDokument6 SeitenAnatomy of The Traffic Accidents On The RoadInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Effect of The Nipah Mall Development On The Performance Roads of Urip Sumohardjo in Makassar CityDokument5 SeitenEffect of The Nipah Mall Development On The Performance Roads of Urip Sumohardjo in Makassar CityInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Comparison of Different Evapotranspiration Estimation Techniques For Mohanpur, Nadia District, West BengalDokument7 SeitenComparison of Different Evapotranspiration Estimation Techniques For Mohanpur, Nadia District, West BengalInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Modeling The Frictional Effect On The Rip Current On A Linear Depth ProfileDokument6 SeitenModeling The Frictional Effect On The Rip Current On A Linear Depth ProfileInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Multi-Response Optimization of WEDM Process Parameters of Monel 400 Using Integrated RSM and GADokument8 SeitenMulti-Response Optimization of WEDM Process Parameters of Monel 400 Using Integrated RSM and GAInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Location of Zeros of PolynomialsDokument7 SeitenLocation of Zeros of PolynomialsInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- A Holistic Approach For Determining The Characteristic Flow On Kangsabati CatchmentDokument8 SeitenA Holistic Approach For Determining The Characteristic Flow On Kangsabati CatchmentInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Time-History Analysis On Seismic Stability of Nuclear Island Bedrock With Weak InterlayerDokument9 SeitenTime-History Analysis On Seismic Stability of Nuclear Island Bedrock With Weak InterlayerInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Urban Town PlanningDokument4 SeitenUrban Town PlanningInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Wi MAX Deinter Leaver's Address Generation Unit Through FPGA ImplementationDokument3 SeitenWi MAX Deinter Leaver's Address Generation Unit Through FPGA ImplementationInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Effect of Turbulence Model in Numerical Simulation of Single Round Jet at Low Reynolds NumberDokument16 SeitenEffect of Turbulence Model in Numerical Simulation of Single Round Jet at Low Reynolds NumberInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- PCB Faults Detection Using Image ProcessingDokument5 SeitenPCB Faults Detection Using Image ProcessingInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- An Evaluation of The Taxi Supply Management at The International Airport of Sultan Hasanuddin in Makassar - IndonesiaDokument4 SeitenAn Evaluation of The Taxi Supply Management at The International Airport of Sultan Hasanuddin in Makassar - IndonesiaInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Study of The Class and Structural Changes Caused by Incorporating The Target Class Guided Feature Subsetting in High Dimensional DataDokument13 SeitenStudy of The Class and Structural Changes Caused by Incorporating The Target Class Guided Feature Subsetting in High Dimensional DataInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Modelling, Fabrication & Analysis of Pelton Turbine For Different Head and MaterialsDokument17 SeitenModelling, Fabrication & Analysis of Pelton Turbine For Different Head and MaterialsInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- A New Fatigue Damage Accumulation Rating Life Model of Ball Bearings Under Vibration LoadDokument11 SeitenA New Fatigue Damage Accumulation Rating Life Model of Ball Bearings Under Vibration LoadAlbertoNoch keine Bewertungen

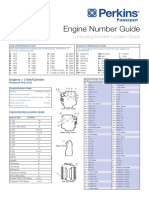

- Engine Number Guide (2-Page)Dokument2 SeitenEngine Number Guide (2-Page)Abdul KhaliqNoch keine Bewertungen

- Materiales CompuestosDokument167 SeitenMateriales CompuestosTatiana MerchanNoch keine Bewertungen

- 1962 Fallout Shelter DesignDokument218 Seiten1962 Fallout Shelter DesignLouie_popwhatski100% (1)

- Module22 - Consequence Analysis - Effect ModelDokument52 SeitenModule22 - Consequence Analysis - Effect ModelMinh ThưNoch keine Bewertungen

- MonorailDokument13 SeitenMonorailJay PadamaNoch keine Bewertungen

- 31 M.E Ed R2010Dokument61 Seiten31 M.E Ed R2010Jason JohnsonNoch keine Bewertungen

- Thermo Scientific Belt Conveyor Scale HandbookDokument20 SeitenThermo Scientific Belt Conveyor Scale HandbookEJECUTIVO_1Noch keine Bewertungen

- ECE 6123 Advanced Signal Processing: 1 FiltersDokument9 SeitenECE 6123 Advanced Signal Processing: 1 FiltersJanaki KNoch keine Bewertungen

- Civil Engineering MaterialsDokument1 SeiteCivil Engineering MaterialssushilNoch keine Bewertungen

- ALLMENDINGER (1999) Introduction To Structural GeologyDokument290 SeitenALLMENDINGER (1999) Introduction To Structural GeologyeliasNoch keine Bewertungen

- Bp8-Tension: User Defined Applied Forces at Interface Basic DimensionsDokument4 SeitenBp8-Tension: User Defined Applied Forces at Interface Basic DimensionsMallesh NenkatNoch keine Bewertungen

- LM4040 Precision Micropower Shunt Voltage Reference: 1 Features 3 DescriptionDokument60 SeitenLM4040 Precision Micropower Shunt Voltage Reference: 1 Features 3 Descriptionmuhamad faizal yaakubNoch keine Bewertungen

- Sensor Presión Keller Pa26y - 3852Dokument2 SeitenSensor Presión Keller Pa26y - 3852benditasea3352Noch keine Bewertungen

- GMAT QUANT TOPIC 3 (Inequalities + Absolute Value) SolutionsDokument46 SeitenGMAT QUANT TOPIC 3 (Inequalities + Absolute Value) SolutionsBhagath GottipatiNoch keine Bewertungen

- Comparative Study of Performance of CDS, CdSeDokument7 SeitenComparative Study of Performance of CDS, CdSeAli AhmedNoch keine Bewertungen

- Leaded Receptacle Switch BrochureDokument18 SeitenLeaded Receptacle Switch BrochureArturo De Asis SplushNoch keine Bewertungen

- WDM2 LOCO REPORT - Manoj Kr. KataraDokument23 SeitenWDM2 LOCO REPORT - Manoj Kr. KataraAbhinav AgarwalNoch keine Bewertungen

- WHCP BasicsDokument21 SeitenWHCP BasicsbalajiNoch keine Bewertungen

- Surveying With Construction Applications 8th Edition Kavanagh Solutions ManualDokument20 SeitenSurveying With Construction Applications 8th Edition Kavanagh Solutions Manualdeannarogersjfqznksiyc100% (14)

- ANSA v17.0.0 Release NotesDokument63 SeitenANSA v17.0.0 Release NotesVishnu RaghavanNoch keine Bewertungen

- L 19 - Mse628a - 30 10 19Dokument25 SeitenL 19 - Mse628a - 30 10 19Dhanishtha SinghNoch keine Bewertungen

- 2008 PJC CH H2 P3 PrelimDokument12 Seiten2008 PJC CH H2 P3 PrelimdeadbeanNoch keine Bewertungen

- Development Length of Reinforcing Bars - Need To Revise Indian Code ProvisionsDokument8 SeitenDevelopment Length of Reinforcing Bars - Need To Revise Indian Code ProvisionsAvijitNoch keine Bewertungen

- Lincolnweld 888 & LA-85Dokument2 SeitenLincolnweld 888 & LA-85Pablo PazNoch keine Bewertungen

- Usepa - 3051 ADokument30 SeitenUsepa - 3051 Awrangel_2Noch keine Bewertungen

- Syllabus - Vishwakarma Institute of TechnologyDokument211 SeitenSyllabus - Vishwakarma Institute of TechnologyAditya PophaleNoch keine Bewertungen

- Control and Interfacing of BLDC Motor With Labview Using MyrioDokument5 SeitenControl and Interfacing of BLDC Motor With Labview Using Myriovasu_koneti5124Noch keine Bewertungen

- Theory AssignmentDokument12 SeitenTheory Assignmentfahadfadi48Noch keine Bewertungen

- AEE CivilDokument16 SeitenAEE CivilPhoenix Cruise100% (1)