Beruflich Dokumente

Kultur Dokumente

New Microprocessor 1-Rec

Hochgeladen von

Agnus S Swarna LakshmiCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

New Microprocessor 1-Rec

Hochgeladen von

Agnus S Swarna LakshmiCopyright:

Verfügbare Formate

EX.

NO: DATE: IMPLEMENTATION OF MICROPROCESSOR

AIM: To implement Microprocessor using SPARTAN 3E kit.

TOOLS REQUIRED: (i) SOFTWARE REQUIRED: XILINX 13.1 version (ii) HARDWARE REQUIRED: SPARTAN 3500 kit

THEORY: A microprocessor incorporates the functions of a computers central processing unit (CPU) on a single integrated circuit, (IC) or at most a few integrated circuits. It is a multipurpose, programmable device that accepts digital data as input, processes it according to instructions stored in its memory, and provides results as output. it consist of ALU,registers,decoders,control unit.This logic can be designed in verilog/VHDL using XILINX.After simulation it is implemented in SPARTAN 3E kit.

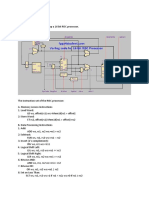

BLOCK DIAGRAM: MICROPROCESSOR MAIN MODULE

MEMORY

ADDER SUBTRACTER

ADDER SUBTRACTER:

ALGORITHM: STEP 1: Write a Verilog/VHDL code for a simple microprocessor. Each module is defined separately and their codes are written separately. STEP 2:Write a verilog coding for read and memory options ,addition, subtraction,multiplication,shift operations and memory operations. STEP 3:Then coding for adder subtracter is written. STEP 4:Similarly in Microprocessor VHDL code is written. STEP 5:These operations can be simulated and implemented in SPARTAN 3E kit. CODE FOR SIMPLE MICROPROCESSOR: module simpleprocess(cntrl,clk,en,m,w_nr,rst,data_in1,data_in2,addr_out1,addr_out2,q1,q2,out,co,out2, n_out); input [ 3:0] cntrl; input clk; input [7:0] data_in1,data_in2,addr_out1, addr_out2; output reg en,w_nr,m,rst; output [7:0] q1,q2; output [7:0] out; output reg [7:0] out2,n_out; output co; reg[7:0] ram_mem [15:0]; reg[7:0]data_reg; reg [3:0] a,b,m1,m2,m3,m4; reg [7:0] w,x,y,z;

ram_mem mm(data_in1,data_in2,rst, clk,w_nr,addr_out1, addr_out2,q1,q2); adder_sub as(q1,q2,m,out,co);

always @ (posedge clk) begin case (cntrl) 4'b0000:rst=1'b0; 4'b0001:w_nr = 1'b1;// memory write 4'b0010: w_nr = 1'b0; //memory read 4'b0011: m =1'b0; // addition 4'b0100: m = 1'b1; // subtraction

4'b0101: begin en=1'b1; // multiplacation if(en==1'b1) begin a= q1[3:0]; b=q2[3:0]; end m1 = {a[3]&b[0],a[2]&b[0],a[1]&b[0],a[0]&b[0]}; m2 = {a[3]&b[1],a[2]&b[1],a[1]&b[1],a[0]&b[1]}; m3 = {a[3]&b[2],a[2]&b[2],a[1]&b[2],a[0]&b[2]}; m4 = {a[3]&b[3],a[2]&b[3],a[1]&b[3],a[0]&b[3]}; w = m1; x = m2<<1; y = m3<<2; z = m4<<3; out2= w+x+y+z; end 4'b0110:// right shift begin data_reg=q1; data_reg= {1'b0, data_reg[7:1]}; assign out2=data_reg; end 4'b0111: // left shift begin data_reg=q2; data_reg= {data_reg [6:0],1'b0}; assign out2=data_reg; end 4'b1000 :out2= q1 & q2; 4'b1010: n_out= ~out2; 4'b1011:out2= q1|q2; 4'b1111: begin w_nr=1'b0; if (w_nr==1'b0) begin ram_mem[addr_out1]=out; ram_mem[addr_out2]=out2; end end 4'b1110: begin w_nr=1'b0; if (w_nr==1'b0)

ram_mem[addr_out1]=n_out; end endcase if ( cntrl==000) rst =1'b0; else rst=1'b1; end endmodule

module adder_sub(a,b,m,out,co); input [7:0] a,b; input m; output [7:0] out; output co; wire [7:0] cout; wire [7:0] d,s; assign d [0]= b[0]^ m; assign d [1]= b[1]^ m; assign d [2]= b[2]^ m; assign d [3]= b[3]^ m; assign d [4]=b[4]^ m; assign d [5]= b[5]^ m; assign d [6]= b[6]^ m; assign d [7]= b[7]^ m;

fa fa1 (s[0],cout[0],a[0],d[0],m); fa fa2 (s[1],cout[1],a[1],d[1] ,cout[0]); fa fa3 (s[2],cout[2],a[2],d[2],cout[1]); fa fa4 (s[3],cout[3],a[3], d[3],cout[2]); fa fa5 (s[4],cout[4],a[4], d[4],cout[3]); fa fa6 (s[5],cout[5],a[5], d[5],cout[4]); fa fa7 (s[6],cout[6],a[6], d[6],cout[5]); fa fa8 (s[7],cout[7],a[7], d[7],cout[6]); assign out = m?((b>a)? ((~s)+1'b1):s) :(s); assign co= cout[7];

endmodule

module ram_mem(data_in1,data_in2,rst, clk,w_nr,addr_out1, addr_out2,q1,q2); input [7:0] data_in1,data_in2; input clk, w_nr,rst; input [7:0] addr_out1,addr_out2; reg [7:0] ram_mem [15:0]; output reg[7:0] q1,q2; always @( posedge clk ) begin if(rst==1'b0) begin q1=8'b0; q2=8'b0; end else begin if( w_nr ==1'b0) begin q1= ram_mem[addr_out1]; q2= ram_mem[addr_out2]; end else begin ram_mem[addr_out1]=data_in1; ram_mem[addr_out2]=data_in2; end end end endmodule module fa(sout,cout,a,b,cin); output sout,cout; input a,b,cin; assign sout=(a^b^cin); assign cout=((a&b)|(a&cin)|(b&cin)); endmodule

CODE FOR MICROPROCESSOR VHDL:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values use IEEE.NUMERIC_STD.ALL; use IEEE.STD_LOGIC_SIGNED.ALL;

-- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity simpl is port ( cntrl : in std_logic_vector(3 downto 0); clk: in std_logic; data_in1,data_in2,addr1, addr2:in std_logic_vector(7 downto 0); en,w_nr,m,rst: buffer std_logic ; data_reg: buffer std_logic_vector(7 downto 0); co:out std_logic; q1,q2, out1,out2,n_out:inout std_logic_vector(7 downto 0) ); end simpl; architecture Behavioral of simpl is type ram_type is array (0 to (addr1'length)-1) of std_logic_vector(data_in1'range); signal ram : ram_type; signal w,x,y,z: std_logic_vector(7 downto 0); signal m1,m2,m3,m4:std_logic_vector(3 downto 0); signal a,b : std_logic_vector(3 downto 0); component sync_ram port ( clock : in std_logic; w_nr ,rst : in std_logic; addr1,addr2 : in std_logic_vector (7 downto 0); data_in1,data_in2 : in std_logic_vector (7 downto 0); q1,q2 : out std_logic_vector (7 downto 0) ); end component sync_ram; component add_subb port ( a,b: in std_logic_vector (7 downto 0); out1: out std_logic_vector (7 downto 0);

m: in std_logic; co:out std_logic); end component add_subb; begin mm : sync_ram port map( clk, w_nr,rst,addr1,addr2,data_in1,data_in2,q1,q2); a1 : add_subb port map(q1,q2,out1,m,co); p2:process(clk,cntrl) is begin case (cntrl) is when "0000"=> rst<='0'; when "0001"=> w_nr <='1';-- memory write when "0010"=> w_nr <= '0'; --memory read when "0011"=> m <='0'; -- addition when "0100"=> m <='1'; --subtraction when "0101"=> en<='1'; -- multiplacation if(en='1') then a <=q1(3 downto 0); b <= q2(3 downto 0); end if; m1<=(a(3)and b(0)) & (a(2)and b(0)) & (a(1)and b(0)) & (a(0)and b(0)); m2<=(a(3)and b(1)) & (a(2)and b(1)) & (a(1)and b(1)) & (a(0)and b(1)); m3<=(a(3)and b(2)) & (a(2)and b(2)) & (a(1)and b(2)) & (a(0)and b(2)); m4<=(a(3)and b(3)) & (a(2)and b(3)) & (a(1)and b(3)) & (a(0)and b(3)); w<='0'& '0' & '0' & '0' & m1; x<='0'& '0' & '0'& m2 & '0'; y<='0'& '0' & m3 & '0' &'0'; z<='0'& m4 & '0' &'0'& '0'; out2<=W + X + Y + Z; when "0110"=> -- right shift

data_reg<=q1; data_reg<='0' & data_reg(7 downto 1); out2<=data_reg; when"0111"=> -- left shift

data_reg<=q2; data_reg<=data_reg(6 downto 0)& '0'; out2<=data_reg;

when"1000"=> out2<= q1 and q2; when "1010"=> out2<= not out2; when "1011"=> out2<=q1 or q2; when "1111"=> w_nr<='0'; if (w_nr='0') then ram(to_integer(unsigned(addr1))) <= out1; ram(to_integer(unsigned(addr2))) <= out2; end if; when "1110"=> w_nr<='0'; if (w_nr='0') then ram(to_integer(unsigned(addr2))) <= n_out; end if; when others => out1<="ZZZZZZZZ"; out2<="ZZZZZZZZ"; n_out<="ZZZZZZZZ"; end case;

if ( cntrl="0000") then rst<='0'; else rst<='1'; end if;

end process p2; end Behavioral; library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.Numeric_Std.all;

entity sync_ram is

port ( clock : in std_logic; w_nr ,rst : in std_logic; addr1,addr2 : in std_logic_vector (7 downto 0); data_in1,data_in2 : in std_logic_vector (7 downto 0); q1,q2 : out std_logic_vector (7 downto 0) ); end entity sync_ram; architecture RTL of sync_ram is

type ram_type is array (0 to (addr1'length)-1) of std_logic_vector(data_in1'range); signal ram : ram_type; begin RamProc: process(clock) is begin if (rst= '0') then q1<="00000000"; q2<="00000000"; elsif rising_edge(clock) then if (w_nr = '0') then q1<= ram(to_integer(unsigned(addr1))); q2<= ram(to_integer(unsigned(addr2))); else ram(to_integer(unsigned(addr1))) <= data_in1; ram(to_integer(unsigned(addr2))) <= data_in2; end if; end if; end process RamProc;

end architecture RTL;

library IEEE; use IEEE.STD_LOGIC_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_BIT.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity add_subb is port ( a,b: in std_logic_vector (7 downto 0); out1: out std_logic_vector (7 downto 0); m: in std_logic; co:out std_logic); end add_subb; architecture Behavioral of add_subb is signal cout, d,s,g:std_logic_vector (7 downto 0); component fa port ( sum : out STD_LOGIC; co : out STD_LOGIC; a : in STD_LOGIC; b : in STD_LOGIC; cin : in STD_LOGIC); end component; begin d (0)<= b(0)xor m; d (1)<= b(1)xor m; d(2)<= b(2) xor m; d (3)<= b(3) xor m; d (4)<=b(4) xor m; d (5)<= b(5) xor m; d (6)<= b(6) xor m; d (7)<= b(7) xor m; fa1: fa port map (s(0),cout(0),a(0),d(0),m); fa2: fa port map (s(1),cout(1),a(1),d(1) ,cout(0)); fa3: fa port map (s(2),cout(2),a(2),d(2),cout(1)); fa4: fa port map (s(3),cout(3),a(3), d(3),cout(2)); fa5: fa port map (s(4),cout(4),a(4), d(4),cout(3)); fa6: fa port map (s(5),cout(5),a(5), d(5),cout(4)); fa7: fa port map (s(6),cout(6),a(6), d(6),cout(5)); fa8: fa port map (s(7),cout(7),a(7), d(7),cout(6)); g<=("00000001") or ( not s); out1 <= g when cout(7)='0' and m='1' else s when cout(7)='1' and m='1' else

s when m='0'; co<= cout(7); end Behavioral;

library IEEE; use IEEE.STD_LOGIC_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity fa is Port ( sum : out STD_LOGIC; co : out STD_LOGIC; a : in STD_LOGIC; b : in STD_LOGIC; cin : in STD_LOGIC); end fa; architecture Behavioral of fa is begin sum <=(a xor b xor cin); co <=((a and b) or (a and cin) or (b and cin)); end Behavioral;

SIMULATION OUTPUT (verilog):

SIMULATION OUTPUT(VHDL):

RESULT: Thus the microprocessor was simulated in VHDL using Xilinx and implemented using FPGA trainer kit.

Das könnte Ihnen auch gefallen

- Verilog Modules For Common Digital FunctionsDokument30 SeitenVerilog Modules For Common Digital Functionselle868Noch keine Bewertungen

- Projects With Microcontrollers And PICCVon EverandProjects With Microcontrollers And PICCBewertung: 5 von 5 Sternen5/5 (1)

- Verilog Modules For Common Digital FunctionsDokument30 SeitenVerilog Modules For Common Digital Functionssudarshan poojaryNoch keine Bewertungen

- Lab 5 DR Muslim (Latest)Dokument15 SeitenLab 5 DR Muslim (Latest)a ThanhNoch keine Bewertungen

- Code TempDokument11 SeitenCode TempHoàng Long Nguyễn BùiNoch keine Bewertungen

- V HDL SampleDokument5 SeitenV HDL Sampleppat2006Noch keine Bewertungen

- INFORME PRACTICA No 2Dokument30 SeitenINFORME PRACTICA No 2MAURICIO REYES ROSERONoch keine Bewertungen

- Mipsx 21Dokument16 SeitenMipsx 21hayoula3Noch keine Bewertungen

- My First Program On D Flip FlopDokument39 SeitenMy First Program On D Flip FlopAswinCvrnNoch keine Bewertungen

- Chip 2Dokument8 SeitenChip 2trungdthe172400Noch keine Bewertungen

- Nhom CT3 1 TuanNamHieuDuyDokument15 SeitenNhom CT3 1 TuanNamHieuDuyPhan Duy LuanNoch keine Bewertungen

- Ver I Log ExamplesDokument22 SeitenVer I Log ExamplesDayanand Gowda KrNoch keine Bewertungen

- Cad of Electronics LabDokument4 SeitenCad of Electronics LabVaibhav PandeyNoch keine Bewertungen

- Shadab - DS Lab FileDokument17 SeitenShadab - DS Lab FileEdu On PointsNoch keine Bewertungen

- Interfacing A LCD Display With 8051Dokument7 SeitenInterfacing A LCD Display With 8051bhaswati100% (1)

- 21BCT0093 VL2022230504083 Ast08Dokument15 Seiten21BCT0093 VL2022230504083 Ast08Srinivasan UmaNoch keine Bewertungen

- Void SetupDokument29 SeitenVoid SetupAlejandro RojasNoch keine Bewertungen

- VHDL ProgramsDokument9 SeitenVHDL ProgramsGRANDHIRIANoch keine Bewertungen

- Design Example 5.5Dokument10 SeitenDesign Example 5.5MaheshNoch keine Bewertungen

- Experiment-3: Aim: Activity1 Truth TableDokument7 SeitenExperiment-3: Aim: Activity1 Truth TableHimanshu Rajan jainNoch keine Bewertungen

- Verilog Session 1,2,3Dokument68 SeitenVerilog Session 1,2,3Santhos KumarNoch keine Bewertungen

- Digital Watch DSDDokument4 SeitenDigital Watch DSDAwais ShamsNoch keine Bewertungen

- Interface LCD and Keypad With 8051 MicroDokument7 SeitenInterface LCD and Keypad With 8051 MicroSisay ADNoch keine Bewertungen

- Problem e LabDokument60 SeitenProblem e Labaleahim576Noch keine Bewertungen

- ADXL345 Sensor I2C InterfaceDokument5 SeitenADXL345 Sensor I2C Interfaceavi kishuNoch keine Bewertungen

- Manual Adjust For RTC Clock With Arduino and 7-Segment LEDDokument21 SeitenManual Adjust For RTC Clock With Arduino and 7-Segment LEDfrasekh100% (1)

- Program To Interface GSM Module With 8051 Micro ControllerDokument13 SeitenProgram To Interface GSM Module With 8051 Micro ControllerEphrem Melka Negash80% (10)

- ES1113 Fundamental of Automation Engineering II Lab Activity - 8Dokument11 SeitenES1113 Fundamental of Automation Engineering II Lab Activity - 8Vaibhav GoelNoch keine Bewertungen

- Pic16f628a GSM SmsDokument6 SeitenPic16f628a GSM SmsSake gtrNoch keine Bewertungen

- Can Communication: Data Acquisition & ElectronicsDokument4 SeitenCan Communication: Data Acquisition & ElectronicsKarthi keyanNoch keine Bewertungen

- Code Ver4Dokument11 SeitenCode Ver4Hoàng Long Nguyễn BùiNoch keine Bewertungen

- m4 r5 o Level Iot Practical Classes Chapter 4 Diffrent Type of Sensors and ActuatorsDokument15 Seitenm4 r5 o Level Iot Practical Classes Chapter 4 Diffrent Type of Sensors and Actuatorspratikshyab685Noch keine Bewertungen

- DS Lab ManualDokument31 SeitenDS Lab ManualPiyush MittalNoch keine Bewertungen

- Digital Design and Synthesis: Fall 09Dokument35 SeitenDigital Design and Synthesis: Fall 09Lua Dinh ThiNoch keine Bewertungen

- CN Lab FileDokument35 SeitenCN Lab Filevivek kumar100% (2)

- Digital Hardware Design Assignment: Verilog Codes and SimulationsDokument16 SeitenDigital Hardware Design Assignment: Verilog Codes and SimulationsTeja Krishna Kopuri100% (2)

- Cryptography and Network Security: Practical FileDokument22 SeitenCryptography and Network Security: Practical FileanxenaNoch keine Bewertungen

- LCDDokument4 SeitenLCDPragathi P PaiNoch keine Bewertungen

- Practicles - Solution Distributed System (Google Docs)Dokument19 SeitenPracticles - Solution Distributed System (Google Docs)Chhavi gargNoch keine Bewertungen

- Assignment-5 by Kaneria Dhaval: Verilog Code For Single Cycle ProcessorDokument12 SeitenAssignment-5 by Kaneria Dhaval: Verilog Code For Single Cycle ProcessorSaiteja RayaproluNoch keine Bewertungen

- Computer Networks Practical FileDokument39 SeitenComputer Networks Practical FileNitika KumariNoch keine Bewertungen

- OSLABDokument34 SeitenOSLAB楊承晞Noch keine Bewertungen

- Digital Lab Cs 6211 VHDL ProgramsDokument13 SeitenDigital Lab Cs 6211 VHDL ProgramsMurugan GNoch keine Bewertungen

- #Define #Define #Define #Define #Define #Define #Define #DefineDokument6 Seiten#Define #Define #Define #Define #Define #Define #Define #Defineอํานาจ จันทรNoch keine Bewertungen

- Computer Networks: Q1. Simulate Cyclic Redundancy Check (CRC)Dokument25 SeitenComputer Networks: Q1. Simulate Cyclic Redundancy Check (CRC)surehatiaNoch keine Bewertungen

- F - Cpu: #Define #Include #Include #IncludeDokument8 SeitenF - Cpu: #Define #Include #Include #IncludePhenias ManyashaNoch keine Bewertungen

- Laboratory Report (For Online Lab Class Only) : ECTE333: Microcontroller Architecture and Application Spring 2020 SessionDokument8 SeitenLaboratory Report (For Online Lab Class Only) : ECTE333: Microcontroller Architecture and Application Spring 2020 SessionSaad KamranNoch keine Bewertungen

- Asynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterDokument20 SeitenAsynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterKalagadda BikshaluNoch keine Bewertungen

- Lab 13Dokument11 SeitenLab 13ubaidNoch keine Bewertungen

- Digital Signals and DesignDokument27 SeitenDigital Signals and DesignkannNoch keine Bewertungen

- Interfacing A MAX6902 RTC With An 8051-Type Microcontroller: DescriptionDokument8 SeitenInterfacing A MAX6902 RTC With An 8051-Type Microcontroller: Descriptionapi-3721578100% (3)

- Tài liệu không có tiêu đềDokument8 SeitenTài liệu không có tiêu đề21145452Noch keine Bewertungen

- VerilogexampleDokument20 SeitenVerilogexampleGayathri SankarNoch keine Bewertungen

- BCD Sumador de 1 Dígito: Library Use All Use All Entity Is Port in Downto in Out Downto Out End Architecture of IsDokument3 SeitenBCD Sumador de 1 Dígito: Library Use All Use All Entity Is Port in Downto in Out Downto Out End Architecture of IsCristian Fabian Romero RojasNoch keine Bewertungen

- E Cad Lab ManualDokument51 SeitenE Cad Lab ManualRajesh DoradlaNoch keine Bewertungen

- Optical Mouse Hacking, Part 1 - Conor PetersonDokument21 SeitenOptical Mouse Hacking, Part 1 - Conor PetersonAbhay TiwariNoch keine Bewertungen

- PC 5Dokument8 SeitenPC 5Miguel RodasNoch keine Bewertungen

- CodeDokument4 SeitenCodea dNoch keine Bewertungen

- Program ESC 2019Dokument8 SeitenProgram ESC 2019Aris100% (1)

- Lab ManualDokument145 SeitenLab ManualAgnus S Swarna LakshmiNoch keine Bewertungen

- Different Types of ModelingDokument5 SeitenDifferent Types of ModelingAgnus S Swarna Lakshmi100% (1)

- CAD SeminarDokument28 SeitenCAD SeminarAgnus S Swarna LakshmiNoch keine Bewertungen

- 11.1 Introduction To Combinational Logic SynthesisDokument17 Seiten11.1 Introduction To Combinational Logic SynthesisAgnus S Swarna LakshmiNoch keine Bewertungen

- Case Report Form (CRF) : Design and DevelopmentDokument26 SeitenCase Report Form (CRF) : Design and Developmentapi-3810976Noch keine Bewertungen

- Cybersecurity Essentials 1.0 Release Notes: PurposeDokument5 SeitenCybersecurity Essentials 1.0 Release Notes: PurposeRonny Kimer Fiestas VargasNoch keine Bewertungen

- Ina201 Industrial Network ArchitectureDokument2 SeitenIna201 Industrial Network ArchitectureFranNoch keine Bewertungen

- Svcet: Unit IV Traveling Waves On Transmission LineDokument21 SeitenSvcet: Unit IV Traveling Waves On Transmission LineDeepak CoolNoch keine Bewertungen

- 02 Traps Management Service AdminDokument134 Seiten02 Traps Management Service AdminDonovan RuizNoch keine Bewertungen

- Summer Practice Report Format For CeDokument8 SeitenSummer Practice Report Format For CesohrabNoch keine Bewertungen

- EL3020 Data PDFDokument24 SeitenEL3020 Data PDFichrakNoch keine Bewertungen

- Drainage Service GuidelinesDokument15 SeitenDrainage Service GuidelinesMarllon LobatoNoch keine Bewertungen

- CP R77.20 EndpointSecurity AdminGuideDokument168 SeitenCP R77.20 EndpointSecurity AdminGuideMSNoch keine Bewertungen

- Install OpenERP On UbuntuDokument9 SeitenInstall OpenERP On UbuntuQuynh NguyenNoch keine Bewertungen

- Laserfiche Import Agent 9 Quick StartDokument11 SeitenLaserfiche Import Agent 9 Quick StartFernando Munive ZacatzontleNoch keine Bewertungen

- Potential of Osmotic Power Generation by Pressure Retarded Osmosis Using Seawater As Feed Solution: Analysis and ExperimentsDokument8 SeitenPotential of Osmotic Power Generation by Pressure Retarded Osmosis Using Seawater As Feed Solution: Analysis and ExperimentsAugusto MeloNoch keine Bewertungen

- Dual Upright Chiller & Freezer (246 Doors)Dokument1 SeiteDual Upright Chiller & Freezer (246 Doors)DAMIA SARA BINTI MOHD DIYAH MoeNoch keine Bewertungen

- Aksesoris PumpDokument10 SeitenAksesoris PumpDido AlexanNoch keine Bewertungen

- Kode Simbol Rate TVDokument10 SeitenKode Simbol Rate TVAndri PNoch keine Bewertungen

- Observation of Defects in Cast Iron Castings by Surface AnalysisDokument19 SeitenObservation of Defects in Cast Iron Castings by Surface Analysisgonzalo gimenez100% (1)

- Aircraft Wires and CablesDokument226 SeitenAircraft Wires and Cablesjohn Bronson100% (1)

- Harmony XB4 - ZB4 Metal Push Buttons - XB4BD912R10KDokument6 SeitenHarmony XB4 - ZB4 Metal Push Buttons - XB4BD912R10KLorentzNoch keine Bewertungen

- Minitab Basic TutorialDokument32 SeitenMinitab Basic TutorialMohd Nazri SalimNoch keine Bewertungen

- Windchill Business Administrator's GuideDokument395 SeitenWindchill Business Administrator's GuidevundavilliravindraNoch keine Bewertungen

- Ford Transsit... 2.4 Wwiring DiagramDokument3 SeitenFord Transsit... 2.4 Wwiring DiagramTuan TranNoch keine Bewertungen

- Best Practices For CNIP IndustriesDokument42 SeitenBest Practices For CNIP IndustriesSaurabhDubeyNoch keine Bewertungen

- LC1D1801 Telemecanique LC1-D18-01 Contactor ReplacementDokument1 SeiteLC1D1801 Telemecanique LC1-D18-01 Contactor Replacementjamal debakNoch keine Bewertungen

- Workbook Workbook Workbook Workbook Workbook: Try Yourself QuestionsDokument14 SeitenWorkbook Workbook Workbook Workbook Workbook: Try Yourself QuestionsShubham mishraNoch keine Bewertungen

- Award Report TemplateDokument3 SeitenAward Report Templatechriscivil12Noch keine Bewertungen

- Ddal Players Guide v5Dokument12 SeitenDdal Players Guide v5Jakob Cherpovsky100% (1)

- Necco BondDokument1 SeiteNecco BondZdenko SemanNoch keine Bewertungen

- The Running and Maintenance ofDokument459 SeitenThe Running and Maintenance ofantonigor100% (1)

- EVSDokument7 SeitenEVSsubhas9804009247Noch keine Bewertungen

- Tesco Shop On The GoDokument3 SeitenTesco Shop On The GoIkram KhokharNoch keine Bewertungen

- Once Upon an Algorithm: How Stories Explain ComputingVon EverandOnce Upon an Algorithm: How Stories Explain ComputingBewertung: 4 von 5 Sternen4/5 (43)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyVon EverandChip War: The Quest to Dominate the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (227)

- Excel Essentials: A Step-by-Step Guide with Pictures for Absolute Beginners to Master the Basics and Start Using Excel with ConfidenceVon EverandExcel Essentials: A Step-by-Step Guide with Pictures for Absolute Beginners to Master the Basics and Start Using Excel with ConfidenceNoch keine Bewertungen

- How to Make a Video Game All By Yourself: 10 steps, just you and a computerVon EverandHow to Make a Video Game All By Yourself: 10 steps, just you and a computerBewertung: 5 von 5 Sternen5/5 (1)

- Learn Python Programming for Beginners: Best Step-by-Step Guide for Coding with Python, Great for Kids and Adults. Includes Practical Exercises on Data Analysis, Machine Learning and More.Von EverandLearn Python Programming for Beginners: Best Step-by-Step Guide for Coding with Python, Great for Kids and Adults. Includes Practical Exercises on Data Analysis, Machine Learning and More.Bewertung: 5 von 5 Sternen5/5 (34)

- Clean Code: A Handbook of Agile Software CraftsmanshipVon EverandClean Code: A Handbook of Agile Software CraftsmanshipBewertung: 5 von 5 Sternen5/5 (13)

- Machine Learning: The Ultimate Beginner's Guide to Learn Machine Learning, Artificial Intelligence & Neural Networks Step by StepVon EverandMachine Learning: The Ultimate Beginner's Guide to Learn Machine Learning, Artificial Intelligence & Neural Networks Step by StepBewertung: 4.5 von 5 Sternen4.5/5 (19)

- What Algorithms Want: Imagination in the Age of ComputingVon EverandWhat Algorithms Want: Imagination in the Age of ComputingBewertung: 3.5 von 5 Sternen3.5/5 (41)

- Coders at Work: Reflections on the Craft of ProgrammingVon EverandCoders at Work: Reflections on the Craft of ProgrammingBewertung: 4 von 5 Sternen4/5 (151)

- Grokking Algorithms: An illustrated guide for programmers and other curious peopleVon EverandGrokking Algorithms: An illustrated guide for programmers and other curious peopleBewertung: 4 von 5 Sternen4/5 (16)

- Chip War: The Fight for the World's Most Critical TechnologyVon EverandChip War: The Fight for the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (82)

- Microsoft 365 Guide to Success: 10 Books in 1 | Kick-start Your Career Learning the Key Information to Master Your Microsoft Office Files to Optimize Your Tasks & Surprise Your Colleagues | Access, Excel, OneDrive, Outlook, PowerPoint, Word, Teams, etc.Von EverandMicrosoft 365 Guide to Success: 10 Books in 1 | Kick-start Your Career Learning the Key Information to Master Your Microsoft Office Files to Optimize Your Tasks & Surprise Your Colleagues | Access, Excel, OneDrive, Outlook, PowerPoint, Word, Teams, etc.Bewertung: 5 von 5 Sternen5/5 (2)

- The Advanced Roblox Coding Book: An Unofficial Guide, Updated Edition: Learn How to Script Games, Code Objects and Settings, and Create Your Own World!Von EverandThe Advanced Roblox Coding Book: An Unofficial Guide, Updated Edition: Learn How to Script Games, Code Objects and Settings, and Create Your Own World!Bewertung: 4.5 von 5 Sternen4.5/5 (2)

- Python Programming For Beginners: Learn The Basics Of Python Programming (Python Crash Course, Programming for Dummies)Von EverandPython Programming For Beginners: Learn The Basics Of Python Programming (Python Crash Course, Programming for Dummies)Bewertung: 5 von 5 Sternen5/5 (1)

- Nine Algorithms That Changed the Future: The Ingenious Ideas That Drive Today's ComputersVon EverandNine Algorithms That Changed the Future: The Ingenious Ideas That Drive Today's ComputersBewertung: 5 von 5 Sternen5/5 (7)

- Blockchain Basics: A Non-Technical Introduction in 25 StepsVon EverandBlockchain Basics: A Non-Technical Introduction in 25 StepsBewertung: 4.5 von 5 Sternen4.5/5 (24)

- Python for Beginners: A Crash Course Guide to Learn Python in 1 WeekVon EverandPython for Beginners: A Crash Course Guide to Learn Python in 1 WeekBewertung: 4.5 von 5 Sternen4.5/5 (7)

- Python Programming : How to Code Python Fast In Just 24 Hours With 7 Simple StepsVon EverandPython Programming : How to Code Python Fast In Just 24 Hours With 7 Simple StepsBewertung: 3.5 von 5 Sternen3.5/5 (54)

- GAMEDEV: 10 Steps to Making Your First Game SuccessfulVon EverandGAMEDEV: 10 Steps to Making Your First Game SuccessfulBewertung: 4.5 von 5 Sternen4.5/5 (12)

- Problem Solving in C and Python: Programming Exercises and Solutions, Part 1Von EverandProblem Solving in C and Python: Programming Exercises and Solutions, Part 1Bewertung: 4.5 von 5 Sternen4.5/5 (2)

- Understanding Software: Max Kanat-Alexander on simplicity, coding, and how to suck less as a programmerVon EverandUnderstanding Software: Max Kanat-Alexander on simplicity, coding, and how to suck less as a programmerBewertung: 4.5 von 5 Sternen4.5/5 (44)

- The New New Thing: A Silicon Valley StoryVon EverandThe New New Thing: A Silicon Valley StoryBewertung: 4 von 5 Sternen4/5 (359)