Beruflich Dokumente

Kultur Dokumente

Cyber: Only For

Hochgeladen von

vetchboyOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Cyber: Only For

Hochgeladen von

vetchboyCopyright:

Verfügbare Formate

Only For CYBER

MT1379

Specificationsaresubjecttochangewithoutnotice Progressive Scan DVD Player Combo Chip

FEATURES

§ Supports power-down mode

n Super Integration DVD player single chip § Supports additional serial port

§ Servo controller and data channel processing

§ MPEG-1/MPEG-2/JPEG video decoding n DVD-ROM/CD-ROM Decoding Logic

§ Dolby AC-3/DTS/DVD-Audio audio decoding § Supports CD-ROM Mode 1, CD-ROM XA Mode 2 Form 1,

§ Unified track buffer and A/V decoding buffer CD-ROM XA Mode 2 Form 2, and CD-DA formats

§ § High-speed ECC logic capable of correcting one error per each

Video processing for scaling and video quality enhancement

§ P-codeword or Q-codeword

OSD & Sub-picture decoding §

§ Automatic sector Mode and Form detection

Built-in clock generator §

§ Automatic sector Header verification

Built-in TV encoder §

§ 8-bit counter for decode completion check

Built-in progressive video output §

§ Programmable descrambling and error correction schemes

Video input port and audio/SPDIF input port § Automatically repeated error corrections

§ 8-bit C2 Pointer counter

n Speed Performance on Servo and Decoding

§ Decoder Error Notification Interrupt that signals various decoder

§ DVD-ROM up to 8XS errors

§ CD-ROM up to 24XS § Provide error correction acceleration

§ Built-in a frequency programmable clock to µPandRSPC

Decoder to optimize the performance over power n Buffer Memory Controller

§ Supports 16Mb/32Mb/64Mb/128Mb SDRAM

n Channel Data Processor

§ Supports 16-bit/32-bit SDRAM data bus interface

§ Provides interface with analog front -end processor § Build in a DRAM interface programmable clock to optimize the

§ Analog data slicer for small jitter capability DRAM performance

§ Built-in high performance data PLL for channel data § Provide the self-refresh mode SDRAM

demodulation §

§ Programmable DRAM access cycle and refresh cycle timings

EFM/EFM+ data demodulation §

§ Block-based sector addressing

Enhanced channel data frame sync protection & DVD-ROM §

sector sync protection Programmable buffering counter for buffer status tracking

§ Maximum DRAM speed is 133MHz

n Servo Control and Spindle Motor Control § Support 5/3.3-Volt. DRAM Interface

§ Programmable frequency error gain and phase error gain of

spindle PLL to control spindle motor on CLV and CAV mode n Video Decode

§ Provide a varipitch speed control for CLV and CAV mode § Decodes MPEG1 video and MPEG2 main level, main profile

§ Built-in ADCs and DACs for digital servo control video (720/480 and 720x576)

§ § Maximum input bit-rate of 15Mbits/sec

Provide 2 general PWM

§ § Smooth digest view function with I, P and B picture decoding

Tray control can be PWM output or digital output

§ § Baseline, extended-sequential and progressive JPEG image

Built-in DSP for digital servo control

decoding

§ RLE and non-RLEBMP image decoding

§ Support CD-G titles

n Host Micro controller

n Video/OSD/SPU/HLI Processor

§ Built-in 8032 micro controller § Arbitrary ratio vertical/horizontal scaling of video, from 0.25X to

§ Built-in internal 373 and 8-bit programmable lower address port 256X

§ 1024-bytes on-chip RAM § 65535/256/16/4/2-color bitmap format OSD,

§ Up to 2M bytes FLASH-programming interface § 256/16 color RLC format OSD

§ Supports 5/3.3-Volt. FLASH interface

Page 1 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

§ Automatic scrolling of OSD image § Channel equalizer

§ Provides 4-color/32x32-pixel hardware cursor § 3D surround processing include virtual surround and speaker

§ Fade-in, Fade out, and Wipe functions as specified in the separation

DVD-Audio Specification and other slide show transition effects § Power-down control

§ Progressive scan output § HDCD certified

n Audio Processing n TV Encoder

§ Decoder format supports: § Six 54MHz/12bit DA converters

- Dolby Digital (AC-3) decoding § Support NTSC, PAL-BDGHI, PAL-N, PAL-M interlace TV format

- DTS decoding and 480p, 576p progressive TV format

§ Automatically turn off unconnected channel(s).

- MLP decoding for DVD-Audio

§ Support PC monitor (VGA)

- MPEG-1 layer 1/layer 2 audio decoding

§ Support Macrovision 7.1

- MPEG-2 layer1/layer2 2-channel audio decoding

- Dolby Pro Logic decoding

n Progressive Output

- High Definition Compatible Digital (HDCD) decoding

§ § Automatic detect film or video source

Up to 6 channel linear PCM output for DVD Audio / DVD Video

§ 3:2 pull down source detection

§ Downmix function

§ § Advanced Motion adaptive de-interlace

Support IEC 60958/61937 output

§ Minimum external memory requirement

- PCM / bit stream / mute mode

- Custom IEC latency up to 2 frames

n Audio/Video Output

§ Pink noise and white noise generator

§ Line-in/SPDIF-in for versatile audio processing

§ Karaoke functions

§ CCIR601/656 video input port

- Microphoneecho with adjustable echo level, echo -depth and

delay length § Support picture-in-picture for video decoding and input source

- Microphone tone control with three custom second-order IIR

filter n Outline

- Vocal mute/vocal assistant § 216-pin LQFP package

- Key shift up to +/- 8 keys controlled by 1/2 key § 3.3/2.5-Volt. Dual operating voltages

Page 2 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

PI N DE F I N I T I O N S

Pin Number Symbol Type Description

1 IREF Analog Input Current reference input. It generates reference current for data PLL.

Connect an external 100K resistor to this pin and PLLVSS.

2 PLLVSS Ground Ground pin for data PLL and related analog circuitry

3 LPIOP Analog Output Positive output of the low pass filter

4 LPION Analog Output Negative output of the low pass filter

5 LPFON Analog output Negative output of loop filter amplifier

6 LPFIP Analog Input Positive input of loop filter amplifier

7 LPFIN Analog Input Negative input of loop filter amplifier

8 LPFOP Analog Output Positive output of loop filter amplifier

9 JITFO Analog Output RF jitter meter output

10 JITFN Analog Input Negative input of the operation amplifier for RF jigger meter

11 PLLVDD3 Power 3.3V power pin for data PLL and related analog circuitry

12 FOO Analog Output Focus servo output. PDM output of focus servo compensator

13 TRO Analog Output Tracking servo output. PDM output of tracking servo compensator

14 TROPENPWM Analog Output Tray open output, controlled by microcontroller.

This is PWM output for TRWMEN27hRW2=1 or is digital output for

TRWMEN27hRW2=0

15 PWMOUT1 Analog Output The 1st general PWM output

16 PWMOUT2 Analog Output The 2nd general PWM output

17 DVDD2 Power 2.5V power pin for internal fully digital circuitry

18 DMO Analog Output Disk motor control output. PWM output

19 FMO Analog Output Feed motor control. PWM output

20 DVSS Ground Ground pin for internal fully digital circuitry

21 FG Input Motor Hall sensor input

22 HIGHA0 Inout Microcontroller address 8

2~16MA, SR

PU

23 HIGHA1 Inout Microcontroller address 9

2~16MA, SR

PU

24 HIGHA2 Inout Microcontroller address 10

2~16MA, SR

PU

25 HIGHA3 Inout Microcontroller address 11

2~16MA, SR

PU

26 HIGHA4 Inout Microcontroller address 12

2~16MA, SR

PU

27 HIGHA5 Inout Microcontroller address 13

2~16MA, SR

PU

28 DVSS Ground Ground pin for internal digital circuitry

29 HIGHA6 Inout Microcontroller address 14

2~16MA, SR

PU

30 HIGHA7 Inout Microcontroller address 15

2~16MA, SR

PU

31 AD7 Inout Microcontroller address/data 7

2~16MA, SR

32 AD6 Inout Microcontroller address/data 6

2~16MA, SR

33 AD5 Inout Microcontroller address/data 5

2~16MA, SR

Page 3 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Number Symbol Type Description

34 AD4 Inout Microcontroller address/data 4

2~16MA, SR

35 DVDD3 Power 3.3V power pin for internal digital circuitry

36 AD3 Inout Microcontroller address/data 3

2~16MA, SR

37 AD2 Inout Microcontroller address/data 2

2~16MA, SR

38 AD1 Inout Microcontroller address/data 1

2~16MA, SR

39 AD0 Inout Microcontroller address/data 0

2~16MA, SR

40 IOA0 Inout Microcontroller address 0 / IO

2~16MA, SR

PU

41 IOA1 Inout Microcontroller address 1 / IO

2~16MA, SR

PU

42 DVDD2 Power 2.5V power pin for internal digital circuitry

43 IOA2 Inout Microcontroller address 2 / IO

2~16MA, SR

PU

44 IOA3 Inout Microcontroller address 3 / IO

2~16MA, SR

PU

45 IOA4 Inout Microcontroller address 4 / IO

2~16MA, SR

PU

46 IOA5 Inout Microcontroller address 5 / IO

2~16MA, SR

PU

47 IOA6 Inout Microcontroller address 6 / IO

2~16MA, SR

PU

48 IOA7 Inout Microcontroller address 7 / IO

2~16MA, SR

PU

49 A16 Output Flash address 16

2~16MA, SR

50 A17 Output Flash address 17

2~16MA, SR

51 IOA18 Inout Flash address 18 / IO

2~16MA, SR

SMT

52 IOA19 Inout Flash address 19 / IO

2~16MA, SR

SMT

53 IOA20 Inout Flash address 20 / IO

2~16MA, SR OR Videoin Data PortB 0

SMT

54 APLLVSS Ground Ground pin for audio clock circuitry

55 APLLVDD3 Power 3.3V Power pin for audio clock circuitry

56 ALE Inout Microcontroller address latch enable

2~16MA, SR

PU,SMT

57 IOOE# Inout Flash output enable, active low / IO

2~16MA, SR

SMT

Page 4 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Number Symbol Type Description

58 IOWR# Inout Flash write enable, active low / IO

2~16MA,SR

SMT

59 IOCS# Inout Flash chip select, active low / IO

2~16MA, SR

PU,SMT

60 DVSS Ground Ground pin for internal digital circuitry

61 UP1_2 Inout Microcontroller port 1-2

4MA, SR

PU,SMT

62 UP1_3 Inout Microcontroller port 1-3

4MA, SR

PU,SMT

63 UP1_4 Inout Microcontroller port 1-4

4MA, SR

PU,SMT

64 UP1_5 Inout Microcontroller port 1-5

4MA, SR

PU,SMT

65 UP1_6 Inout Microcontroller port 1-6

4MA, SR

PU,SMT

66 DVDD3 Power 3.3V power pin for internal digital circuitry

67 UP1_7 Inout Microcontroller port 1-7

4MA, SR

PU,SMT

68 UP3_0 Inout Microcontroller port 3-0

4MA, SR

PU,SMT

69 UP3_1 Inout Microcontroller port 3-1

4MA, SR

PU,SMT

70 INT0# Inout Microcontroller interrupt 0, active low

2~16MA, SR

PU,SMT

71 IR Input IR control signal input

SMT

72 DVDD2 Power 2.5V power pin for internal digital circuitry

73 UP3_4 Inout Microcontroller port 3-4

74 UP3_5 Inout Microcontroller port 3-5

75 UWR# Inout Microcontroller write strobe, active low

2~16MA, SR

PU, SMT

76 URD# Inout Microcontroller read strobe, active low

2~16MA, SR

PU, SMT

77 DVSS Ground Ground pin for internal digital circuitry

78 RD7 Inout DRAM data 7

79 RD6 Inout DRAM data 6

80 RD5 Inout DRAM data 5

81 RD4 Inout DRAM data 4

82 DVDD2 Power 2.5V power pin for internal digital circuitry

83 RD3 Inout DRAM data 3

84 RD2 Inout DRAM data 2

85 RD1 Inout DRAM data 1

86 RD0 Inout DRAM data 0

Page 5 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Number Symbol Type Description

87 RWE# Output DRAM Write enable, active low

2~16MA, SR

88 CAS# Output DRAM columnaddress strobe, active low

2~16MA, SR

89 RAS# Output DRAM row address strobe, active low

2~16MA, SR

90 RCS# Output DRAM chip select, active low

2~16MA, SR

91 BA0 Output DRAM bank address 0

2~16MA, SR

92 DVSS Ground Ground pin for internal digi tal circuitry

93 RD15 Inout DRAM data 15

2~16MA, SR

PU/PD, SMT

94 RD14 Inout DRAM data 14

2~16MA, SR

PU/PD, SMT

95 RD13 Inout DRAM data 13

2~16MA, SR

PU/PD, SMT

96 RD12 Inout DRAM data 12

2~16MA, SR

PU/PD, SMT

97 DVDD3 Power 3.3V power pin for internal digital circuitry

98 RD11 Inout DRAM data 11

2~16MA, SR

PU/PD, SMT

99 RD10 Inout DRAM data 10

2~16MA, SR

PU/PD, SMT

100 RD9 Inout DRAM data 9

2~16MA, SR

PU/PD, SMT

101 RD8 Inout DRAM data 8

2~16MA, SR

PU/PD, SMT

102 DVSS Ground Ground pin for internal digital circuitry

103 CLK Output DRAM clock

2~16MA, SR

104 CLE Output DRAM clock enable

2~16MA, SR

105 RA11 Output DRAM address bit 11 or audio serial data 3 (channel 7/8)

2~16MA, SR

106 RA9 Output DRAM address 9

2~16MA, SR

107 RA8 Output DRAM address 8

2~16MA, SR

108 DMVDD3 Power 3.3V Power pin for DRAM clock circuitry

109 DMVSS Ground Ground pin for DRAM clock circuitry

110 RA7 Output DRAM address 7

2~16MA, SR

111 DVDD3 Power 3.3V power pin for internal digital circuitry

112 RA6 Output DRAM address 6

2~16MA, SR

113 RA5 Output DRAM address 5

2~16MA, SR

Page 6 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Number Symbol Type Description

114 RA4 Output DRAM address 4

2~16MA, SR

115 DVSS Ground Ground pin for internal digital circuitry

116 DQM1 Output Mask for DRAM input/output byte 1

2~16MA, SR

117 DQM0 Output Mask for DRAM input/output byte 0

2~16MA, SR

118 BA1 Output DRAM bank address 0

2~16MA, SR

119 RA10 Output DRAM address10

2~16MA, SR

120 DVDD2 Power 2.5V power pin for internal digital circuitry

121 RA0 Output DRAM address 0

2~16MA, SR

122 RA1 Output DRAM address 1

2~16MA, SR

123 RA2 Output DRAM address 2

2~16MA, SR

124 RA3 Output DRAM address 3

2~16MA, SR

125 DVSS Ground Ground pin for internal digital circuitry

126 RD31 Inout DRAM data 31

2~16MA, SR

PU/PD, SMT

127 RD30 Inout DRAM data 30

2~16MA, SR

PU/PD, SMT

128 RD29 Inout DRAM data 29

2~16MA, SR

PU/PD, SMT

129 RD28 Inout DRAM data 28

2~16MA, SR

PU/PD, SMT

130 DVDD3 Power 3.3V power pin for internal digital circuitry

131 RD27 Inout DRAM data 27

2~16MA, SR

PU/PD, SMT

132 RD26 Inout DRAM data 26

2~16MA, SR

PU/PD, SMT

133 RD25 Inout DRAM data 25

2~16MA, SR

PU/PD, SMT

134 RD24 Inout DRAM data 24

2~16MA, SR

PU/PD, SMT

135 DVSS Ground Ground pin for internal digital circuitry

136 DQM3 Output Mask for DRAM input/output byte 3

2~16MA, SR

137 DQM2 Output Mask for DRAM input/output byte 2

2~16MA, SR

138 RD23 Inout DRAM data 23 /

2~16MA, SR Videoin Data PortA 7

PU/PD, SMT

139 RD22 Inout DRAM data 22 /

2~16MA, SR Videoin Data PortA 6

PU/PD, SMT

Page 7 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Number Symbol Type Description

140 DVDD2 Power 2.5V power pin for internal digital circuitry

141 RD21 Inout DRAM data 21 /

2~16MA, SR Videoin Data PortA 5

PU/PD, SMT

142 RD20 Inout DRAM data 20 /

2~16MA, SR Videoin Data PortA 4

PU/PD, SMT

143 RD19 Inout DRAM data 19 /

2~16MA, SR Videoin Data PortA 3

PU/PD, SMT

144 RD18 Inout DRAM data 18 /

2~16MA, SR Videoin Data PortA 2

PU/PD, SMT

145 DVSS Ground Ground pin for internal digital circuitry

146 RD17 Inout DRAM data 17 /

2~16MA, SR Videoin Data PortA 1

PU/PD, SMT

147 RD16 Inout DRAM data 16 /

2~16MA, SR Videoin Data PortA 0

PU/PD, SMT

148 ABCK Output Audio bit clock

4MA

149 ALRCK Inout (1) Audio left/right channel clock

4MA, (2) Trap value in power-on reset :

PD,SMT 1 : use external 373 0: use internal 373

150 DVDD3 Power 3.3V power pin for internal digital circuitry

151 ACLK Inout Audio DAC master clock (384/256 audio sample frequency)

4MA

152 MC_DATA Input Microphone serial input

153 SPDIF Output SPDIF output

2~16MA,

SR : ON/OFF

154 ASDATA0 Inout (1) Audio serial data 0 (left/right channel)

4MA (2) Trap value in power-on reset :

PD SMT 1 : manufactory test mode 0 : normal operation

155 ASDATA1 Inout (1) Audio serial data 1 (surround left/surround right channel)

4MA (2) Trap value in power-on reset :

PD SMT 1 : manufactory test mode 0 : normal operation

156 ASDATA2 Inout (1) Audio serial data 2 (center/left channel)

4MA (2) Trap value in power-on reset :

PD SMT 1 : manufactory test mode 0 : normal operation

157 ASDATA3 Inout (1) Audio serial data 3 (surround left/surround right channel )

4MA (2) Trap value in power-on reset :

PD SMT 1 : manufactory test mode 0 : normal operation

OR Videoin Data PortB 1

158 ASDATA4 Inout (1) Audio serial data 4 (center/left channel)

4MA (2) Trap value in power-on reset :

PD SMT 1 : manufactory test mode 0 : normal operation

OR Videoin Data PortB 2

159 DACVDDC Power 3.3V power pin for VIDEO DAC circuitry

160 VREF Analog input Bandgap reference voltage

161 FS Analog output Full scale adjustment

162 YUV0/CIN Output Video data output bit 0 /

4MA, SR Compensation capacitor

163 DACVSSC Ground Ground pin for VIDEO DAC circuitry

164 YUV1/C Output Video data output bit 1 /

4MA, SR Analog chroma output

Page 8 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Number Symbol Type Description

165 DACVDDB Power 3.3V power pin for VIDEO DAC circuitry

166 YUV2/Y Output Video data output bit 2 /

4MA, SR Analog Y output

167 DACVSSB Ground Ground pin for VIDEO DAC circuitry

168 YUV3/CVBS Output Video data output bit 3 /

4MA, SR Analog composite output

169 DACVDDA Power 3.3V power pin for VIDEO DAC circuitry

170 YUV4/G Output Video data output bit 4 /

4MA, SR Green or Y

171 DACVSSA Ground Ground pin for VIDEO DAC circuitry

172 YUV5/B Output Video data output bit 5 /

4MA, SR Blue or CB

173 YUV6/R Output Video data output bit 6 /

4MA, SR Red or CR

174 ICE Input Microcontroller ICE mode enable

PD,SMT

175 BLANK# Inout Video blank area, active low /

4MA, SR Videoin Field_601

SMT

176 VSYN Inout Vertical sync /

4MA, SR Videoin Vsync_601

SMT

177 YUV7 Inout Video data output bit 7 /

4MA, SR Videoin Data PortB 3

SMT

178 DVSS Ground Ground pin for internal digital circuitry

179 HSYN Inout Horizontal sync /

4MA, SR Videoin Hsync_601

SMT

180 SPMCLK Input Audio DAC master clock of SPDIF input /

Videoin Data PortB 4

181 SPDATA Input Audio data of SPDIF input /

Videoin Data PortB 5

182 DVDD2 Power 2.5V power pin for internal digital circuitry

183 SPLRCK Input Audio left/right channel clock of SPDIF input /

Videoin Data PortB 6

184 SPBCK Input Audio bit clock of SPDIF input /

Videoin Data PortB 7

185 DVDD3 Power 3.3V power pin for internal digital circuitry

186 XTALO Output Crystal output

187 XTALI Input Crystal input

188 PRST Input Power on reset input, active high

PD,SMT

189 DVSS Ground Ground pin for internal digital circuitry

190 VFO13 Output The 1st, 3rd header VFO pulse output

191 IDGATE Output Header detect signal output

192 DVDD3 Power 3.3V power pin for internal digital circuitry

193 UDGATE Output DVD_RAM recording data gate signal output

194 WOBSI Input Wobble signal input

195 SDATA Output RF serial data output

196 SDEN Output RF serial data latch enable

197 SLCK Output RF serial clock output

198 BDO Input Flag of defect data input status

199 ADCVSS Ground Ground pin for ADC circuitry

200 ADIN Analog Input General A/D input

201 RFSUBI Analog Input RF subtraction signal input terminal

Page 9 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Number Symbol Type Description

202 TEZISLV Analog Input Tracking error zero crossing low pass input

203 TEI Analog Input Tracking error input

204 CSO Analog Input Central servo input

205 FEI Analog Input Focus error input

206 RFLEVEL Analog Input Sub beam add input or RFRP low pass input

207 RFRP_DC A Input RF ripple detect input

208 RFRP_AC Analog Input RF ripple detect input (through AC coupling)

209 HRFZC Analog Input High frequency RF ripple zero crossing

210 PWMVREF A Input A reference voltage input for PWM circuitry. A typical value of 4.0 v

211 PWM2VREF A Input A reference voltage input for PWM circuitry. A typical value of 2.0 v

212 ADCVDD3 Power 3.3V power pin for ADC circuitry

213 RFDTSLVP Analog Output Positive RF data slicer level output

214 RFDTSLVN Analog Output Negative RF data slicer level output

215 RFIN Analog Input Negative input of RF differential signal

216 RFIP Analog Input Positive input of RF differential signal

Page 10 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

26 Jul, 2002

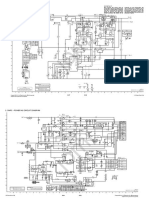

PWM2VREF Page 1 of 2

YUV3/CVBS

PWMVREF

RFDTSLVN

RFDTSLVP

DACVDDA

DACVDDB

ADCVDD3

DACVSSC

DACVSSA

DACVSSB

RFRP_DC

RFRP_AC

RFLEVEL

ADCVSS

SPMCLK

UDGATE

SPLRCK

TEZISLV

SPDATA

YUV4/G

IDGATE

YUV6/R

YUV1/C

YUV5/B

YUV2/Y

RFSUBI

HRFZC

DVDD3

DVDD3

SPBCK

DVDD2

SDATA

BLANK

WOBSI

XTALO

VFO13

SLCK

SDEN

HSYN

DVSS

DVSS

VSYN

XTALI

PRST

YUV7

ADIN

RFIN

RFIP

CSO

BDO

ICE

FEI

TEI

213

216

215

214

212

211

210

209

208

207

206

205

204

203

202

201

200

199

198

197

196

195

194

193

192

191

190

189

188

187

186

185

184

183

182

181

180

179

178

177

176

175

174

173

172

171

170

169

168

167

166

165

164

163

IREF 1 162 YUV0/CIN

PLLVSS 2 161 FS

LPIOP 3 160 VREF

LPION 4 159 DACVDDC

LPFON 5 158 ASDATA4

LPFIP 6 157 ASDATA3

LPFIN 7 156 ASDATA2

LPFOP 8 155 ASDATA1

JITFO 9 154 ASDATA0

JITFN 10 153 SPDIF

PLLVDD3 11 152 MC_DATA

FOO 12 151 ACLK

TRO 13 150 DVDD3

TROPENPWM 14 149 ALRCK

PWMOUT1 15 148 ABCK

PWMOUT2 16 147 RD16

DVDD2 17 146 RD17

DMO 18 145 DVSS

FMO 19 144 RD18

DVSS 20 143 RD19

FG 21 142 RD20

HIGHA0 22 141 RD21

HIGHA1 23 140 DVDD2

HIGHA2 24 139 RD22

HIGHA3 25 138 RD23

HIGHA4 26 MT1379 137 DQM2

HIGHA5 27 136 DQM3

DVSS 28 (216 pins) 135 DVSS

HIGHA6 29 134 RD24

HIGHA7 30 133 RD25

AD7 31 132 RD26

AD6 32 131 RD27

AD5 33 130 DVDD3

AD4 34 129 RD28

DVDD3 35 128 RD29

AD3 36 127 RD30

AD2 37 126 RD31

AD1 38 125 DVSS

AD0 39 124 RA3

IOA0 40 123 RA2

IOA1 41 122 RA1

DVDD2 42 121 RA0

IOA2 43 120 DVDD2

IOA3 44 119 RA10

IOA4 45 118 BA1

IOA5 46 117 DQM0

IOA6 47 116 DQM1

IOA7 48 115 DVSS

A16 49 114 RA4

A17 50 113 RA5

IOA18 51 112 RA6

IOA19 52 111 DVDD3

IOA20 53 110 RA7

APLLVSS 54 109 DMVSS

100

101

102

103

104

105

106

107

108

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

URD#

DMVDD3

APLLVDD3

RD15

RD14

RD13

RD12

RD11

RD10

RCS#

DVDD3

DVDD2

UWR#

DVDD2

DVDD3

RA11

ALE

IOOE#

BA0

RWE#

IR

CLK

RA9

RA8

DVSS

DVSS

DVSS

DVSS

CKE

IOWR#

IOCS#

RD7

RD6

RD5

RD4

RD3

RD2

RD1

RD0

RD9

RD8

CAS#

RAS#

UP1_2

UP1_3

UP1_4

UP1_5

UP1_6

UP1_7

UP3_0

UP3_1

UP3_4

UP3_5

INT0#

Page 11 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

FUNCTIONAL B LOCK

DVD module

Servo Analog Spindle Debug System TV encoder

IO Front end Controller Port Parser

Servo Channel CSS/ Video Video

DPU

DSP Decode CPPM Decoder Output

Playback

Controller

IR/ System DRAM Audio Audio Microphone

VFD Controller Interface Processor Output Input

Audio DAC

Flash DRAM SPDIF MIC

Servo Controller

The servo control is accomplished through the servo DSP (Servo Digital Signal Processor) and its accessory I/O circuits. This servo

DSP is capable of performing complex operations an d also provides a friendly interface for the system controller. By issuing type

1 and type 2 commands from the system controller, the servo DSP can accomplish various complicated servo control functions,

such as tracking, seeking and MT1336/MT1376 chip register programming. As for the servo I/O circuits, it provides interface

between the input servo signals and the Servo DSP. It has built-in ADCs to digitize the servo control signal and DACs to provide

signals for the actuator and sledge motor. It also has a serial interface to communicate with the MT1336/MT1376 chip.

Analog Front End

The analog front end contains a data slicer circuit and a data PLL circuit. The RF analog signal from MT1336/MT1376 is

quantized by the data slicer to form the EFM/EFM+ bit st ream, from which the channel bit clock is extracted by the data PLL.The

EFM/EFM+bit stream and bit clock are then output to DPU for channel bit processing.

DPU

Data path unit (DPU) provides protection on data with lost synchronization patterns and demodulates EFM/EFM+ bit stream into

the channel raw data that will be corrected by the decoder. The synchronization protection makes data after the synchronization

pattern to be extracted even if the synchronization pattern is not found.

Spindle Controller

Page 12 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

The spindle controller is used to control disc spindle motor. It includes a varipitch CLV clock generator, a CLV/CAV controller,

and a PWM generator. The varipitch CLV clock enerator generates a reference colck for the speed of operation. The CLV/CAV

controller changes the mode and speed of operation according to servo register setting. The PWM generator generates

pulse -width-modulated signal to drive disc spindle motor driver.

CSS/CPPM

The CSS/CPPM module provides functions necessary for decoding discs conforming to CSS/CPPM specification.

System Parser

The system parser is used to help the system controller to decode DVD/SVCD/VCD bitstream just after the channel decoder

performing error correction. Acting as a DMA master, it moves bitstream data from RSPC buffer to video, audio, or sub-picture

buffer according to system controller request. It also decrypts the scramble data of the CSS/CPPM sectors. Another function of

system parser is providing system controller/DSP a DRAM memory copy controller to enhance system controller/DSP performance.

Video Decoder

The primary function of MT1379 is to support MPEG1 and MPEG2 video decoding. The video decode engine comprises of

variable length decoder (VLD), inverse transformer (IT), motion compensator (MC), and block reconst ructor (BR). The video

decode engine decodes the variable length encoded symbols in MPEG bitstream and performs inverse scan, inverse

quantization, mismatch control and inverse discrete cosine transform onto the variable length decoded data. The motion

compensator fetches prediction data from reference picture buffer according to motion vectors and motion prediciton mode for P

and B pictures. Finally, the block reconstructor combines both the results of inverse transformer and motion compensator to derive

the reconstructed image macroblock and write back to picture buffer.

The video decode engine can also support JPEG and BMP file decoding by common image compression hardware kernels.

Video Output

The Video Output unit contains Video Processor, SPU, OSD, Cursor, TV encoder units, it performs

§ Reading decoded video from DRAM buffer

§ Scaling the image

§ Gamma/Brightness/Hue/Saturation adjustment and edge enhancement

§ Reading and decoding SPU and OSD data from DRAM buffer

§ Generating hardware cursor image

§ Merging the video data, SPU, OSD and cursor

Video Processor

The Video Processor unit controls the transfer of video data stored in the DRAM to an internal or external TV encoder. It uses

FIFOs to buffer outgoing luminance and chrominance data, and performs YUV420 to YUV422 conversion and arbitrary

vertical/horizontal decimation/interpolation, from 1/4x to 256x. With this arbitrary ratio scaling capability, the Video Processor

can perform arbitrary image conversion, such as PAL to NTSC, NTSC to PAL, MPEG1 to MPEG2, Letterbox, Pan-Scan

conversion or zoom in, zoom out. It is also capible of interlace to progressive conversion.

The Video Processor unit performs the following functions:

§ Requests and receives the decoded picture data from the picture buffer in external DRAM for display

§ Resample vertical data to create 4:2:2 sample format

§ Optionally performs vertical/horizontal resampling of both luminance and chrominance data

§ Performs optional Gamma correction, luminance/chrominance adjustment, and edge enhancement

The V ideo Processor unit contains two 2-tap vertical filters for luminance and chrominance . These filters are used to

interpolate and reposition luminance and chrominance line to improve picture quality. These filters are capble of generating

up to eight, unique subline value between two consecutive scan lines. The generation of lines depends on the ratio between

the height of the source image and the target image. In applications where DRAM bandwidth are critical the filters can be

configured as simple line-repeating to reduce the DRAM bandwidth required.

Page 13 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

The Video Processor unit integrates two separate horizontal postprocessing filter, a simple 2-tap linear horizontal filter and

an 8-tap programmable filter. These filters are provided for scaling images horizontally along the scan line. These two filters

is capable of generating up to eight, unique subpixel values between two consecutive pixels on a scan line. The generation

of pixels depends on the ratio between the width of the source image and the target image.

SPU

This is a hardware sub-picture decoder. It decodes the compressed SPU image bitstream and CHG_COLCON commands

according to SPU header information previously decoded by system controller. The SPU module also allows two SPU

objects to be displayed at the same time. SPU image is blended with main video stream.

OSD

The OSD module can operate with 2/4/16/256 -color bitmap format (1/2/4/8 bits), and 16/256 color RLC format, all have 16

levels of transparency. In addition, it accepts an special WARP mode, which inserts one programmable RLC code in the

bitmap to reduce the image size stored in DRAM. It also features automatic shadow/outline generation in 2-color mode, 2

Hilight areas, 1 ChangeColor area and 1 OSDVoid area. One OSD area can occupy the full or a partial screen, or multiple

OSDs can occur in a screen at the same time, only if they don't occupy the same horizontal line. The output image is

blended with the video-SPU mixed stream.

Cursor

A hardware cursor generator is integrated in Video Ou tput Unit. The cursor image is a 32x32 4-color bitmap image, each

colors are programmable. Cursor can be enlarged by 2 in both vertical and horizontal directions. Cursor image is multiplexed

with video-SPU-OSD mixed stream.

Audio Interface

Audio interface consists of Audio Output Interface and Microphone Input Interface.

Audio Output Interface

The MT1379 can support up to 8 channel audio outputs. The output formats can be 16, 24, or 32-bit frames. Left alignment,

2

right alignment, or I S formats are all supported.

With built-in PLL, MT1379 can provide the audio clock (ACLK) for external audio DAC at 384Fs, where Fs is usually 32KHz,

44.1KHz, 48KHz, 96KHz, or 192KHz. ACLK can also be programmed to be from outside MT1379. When ACLK is input to

MT1379, the frequency could be 128*n Fs, where n is from 1 to 7.

Audio raw (encoded) data or cooked (decoded) data can be output on a single line using S/PDIF interface. The output slew

rate and driving force of this pad are programmable.

Microphone Input Interface

The MT1379 provides a microphone input interface. Two independent microphones’ data could be input to the MT1379.

There are two independent digital volume control for these two input channels. The input data formats can also be left

2

alignment, right alignment, or I S formats.

System Controller

MT1379 uses an embedded Turbo-8032 as System Controller and provide ICE interface to increase the feasibility of F/W

development. Also, MT1379 includes an build-in internal 373 to latch lower byte address from 8032 Port 0 and provide a

glue-logic free solution. MT1379 supports up to 1M X 16 bits Flash ROM to store 8032 code, H/W related data, User data, etc.

F/W upgrade can be achieved either by debug interface or by disk.

Page 14 July, 2002

Only For CYBER MT1379

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

ELECTRICAL C HARACTERISTICS

Absolute Maximum Rating

Symbol Parameters Value Unit

VDD3 3.3V Supply voltage -0.3 to 3.6 V

VDD2 2.5V Supply voltage -0.3 to 3.0 V

VDDA Analog Supply voltage -0.3 to 3.6 V

VIN Input Voltage -0.3 to 5.5 V

VOUT Output Voltage -0.3 to VDD3+0.3 V

Ta Ambient Temperature 0 to 70 °C

DC Charateristics

Symbol Parameters Min Typ Max Unit

VIH Input voltage high 2.4 - 3.6 V

VIL Input voltage low - - 0.8 V

VOH Output voltage high 3.0 - VDD3 V

VOL Output voltage low - - 0.5 V

IIH High level input current 10 uA

IIL Low level input current -10 uA

PD Power dissapation 1.0 W

PDown Power down mode 0.1 W

Page 15 July, 2002

Das könnte Ihnen auch gefallen

- Pt3355 3360 09-2020Dokument294 SeitenPt3355 3360 09-2020MarcusNoch keine Bewertungen

- 4GV632A50-1108Dokument20 Seiten4GV632A50-1108Waelghanii GhaniNoch keine Bewertungen

- Sega Dreamcast Gd-Rom Controller (Oti-9220)Dokument17 SeitenSega Dreamcast Gd-Rom Controller (Oti-9220)ASHLEY011266Noch keine Bewertungen

- Preliminary: SPCA702ADokument60 SeitenPreliminary: SPCA702Avetchboy0% (1)

- M5705: DVD-ROM Controller With Embedded MicroprocessorDokument4 SeitenM5705: DVD-ROM Controller With Embedded MicroprocessorvetchboyNoch keine Bewertungen

- Hi 3516 CDokument6 SeitenHi 3516 Cco_stel817842100% (1)

- Adv7340 7341 PDFDokument108 SeitenAdv7340 7341 PDFTheotech EletronNoch keine Bewertungen

- 4-Channel 960H DVR with H.264 CompressionDokument2 Seiten4-Channel 960H DVR with H.264 CompressionAlexander MontoyaNoch keine Bewertungen

- TV 7 Mst726 Datasheet 535Dokument117 SeitenTV 7 Mst726 Datasheet 535Денис ДенисовNoch keine Bewertungen

- NEA-DVR - DatasheetDokument2 SeitenNEA-DVR - DatasheetRobertNoch keine Bewertungen

- Hi3798M V100 Brief Data SheetDokument3 SeitenHi3798M V100 Brief Data Sheet王先生Noch keine Bewertungen

- Gesture Recognition Using Fpga - FinalDokument51 SeitenGesture Recognition Using Fpga - FinalFranklin Geo FrancisNoch keine Bewertungen

- Sm320lf2407a Ep PDFDokument112 SeitenSm320lf2407a Ep PDFDaniel Andoney ValdezNoch keine Bewertungen

- Adv7393bcpz SMD Encoder Entegresi Lfcsp40 DatasheetDokument107 SeitenAdv7393bcpz SMD Encoder Entegresi Lfcsp40 DatasheetSabri OkurNoch keine Bewertungen

- Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only: FeaturesDokument207 SeitenMstar Confidential for 深圳市江启科技有限公司 Internal Use Only: FeaturesErroz RosadiNoch keine Bewertungen

- TSUM56AL MstarDokument95 SeitenTSUM56AL Mstarwilliam tolentinoNoch keine Bewertungen

- C1mhp T UkDokument5 SeitenC1mhp T UkkorkmazmailNoch keine Bewertungen

- Sercel SpecsDokument1 SeiteSercel SpecsNazeer AhmedNoch keine Bewertungen

- AMD-radeon-pro-w7800-datasheetDokument2 SeitenAMD-radeon-pro-w7800-datasheetPeter PanNoch keine Bewertungen

- Satellite L25-S1216 Detailed Product Specification: Operating System ExpandabilityDokument10 SeitenSatellite L25-S1216 Detailed Product Specification: Operating System ExpandabilityN ChNoch keine Bewertungen

- Digital Sprite 2 DatasheetDokument2 SeitenDigital Sprite 2 DatasheetAndres F CalleNoch keine Bewertungen

- Startup Manual: ITA-2230 Series Intel® Core™ I7 Fanless 2U Rackmount System With 3 ITAM SlotsDokument6 SeitenStartup Manual: ITA-2230 Series Intel® Core™ I7 Fanless 2U Rackmount System With 3 ITAM SlotsNghiaNoch keine Bewertungen

- Combined Pitot-Static Datasheet V2 0Dokument3 SeitenCombined Pitot-Static Datasheet V2 0Fakhri GhrairiNoch keine Bewertungen

- Introducing Samsung DVD Recorder (DVD-R128 - R129)Dokument74 SeitenIntroducing Samsung DVD Recorder (DVD-R128 - R129)tomverstratenNoch keine Bewertungen

- Compact DVCPRO Player with 23 Hours and SDI I/ODokument2 SeitenCompact DVCPRO Player with 23 Hours and SDI I/OOmen RoisNoch keine Bewertungen

- Heitel CamDisc VG ManualDokument2 SeitenHeitel CamDisc VG ManualCliff-Jacky ChengNoch keine Bewertungen

- CAmera GuideDokument18 SeitenCAmera GuidePrashantNirmalNoch keine Bewertungen

- GS1559 HD-LINX™ II Multi-Rate Deserializer With Loop-Through Cable DriverDokument74 SeitenGS1559 HD-LINX™ II Multi-Rate Deserializer With Loop-Through Cable DriverMohammad Saleh AbbasiNoch keine Bewertungen

- MST776-I Mstar PDFDokument12 SeitenMST776-I Mstar PDFBekti Yayang Mardya SaputraNoch keine Bewertungen

- Cinedeck Ex Designed To Save Time and Money: MonitorDokument2 SeitenCinedeck Ex Designed To Save Time and Money: MonitorTelejuanNoch keine Bewertungen

- AXI Multi-Bus Memory Controller: Block DiagramDokument2 SeitenAXI Multi-Bus Memory Controller: Block Diagrammark bNoch keine Bewertungen

- SIMB-A21 Startup Manual PDFDokument6 SeitenSIMB-A21 Startup Manual PDFsisindry chennupatiNoch keine Bewertungen

- Hi3798M V100 Brief Data Sheet: Key SpecificationsDokument3 SeitenHi3798M V100 Brief Data Sheet: Key SpecificationsNasrullahNoch keine Bewertungen

- Choosing the Right Processor for Embedded System DesignDokument45 SeitenChoosing the Right Processor for Embedded System DesignINTTICNoch keine Bewertungen

- Club 3D Geforce 6200 TC Pcie Turbocache Technology: WWF Panda JRDokument2 SeitenClub 3D Geforce 6200 TC Pcie Turbocache Technology: WWF Panda JRNajaci eeeNoch keine Bewertungen

- GS1559 HD-LINX™ II Multi-Rate Deserializer With Loop-Through Cable DriverDokument74 SeitenGS1559 HD-LINX™ II Multi-Rate Deserializer With Loop-Through Cable DriverKikokNoch keine Bewertungen

- Computer Graphics Graphics SystemsDokument40 SeitenComputer Graphics Graphics SystemsNusrat UllahNoch keine Bewertungen

- ALPR Parking System SolutionDokument49 SeitenALPR Parking System SolutionShawn NoorNoch keine Bewertungen

- Cdd27033-Schematic DiagramDokument14 SeitenCdd27033-Schematic DiagramRuben MonsaNoch keine Bewertungen

- Digital Cinema Processor: FeaturesDokument2 SeitenDigital Cinema Processor: FeaturesHendovaAlAzharNoch keine Bewertungen

- Vibe cp6000Dokument3 SeitenVibe cp6000Karl SoNoch keine Bewertungen

- Lecture 03Dokument35 SeitenLecture 03Muqadar AliNoch keine Bewertungen

- Toshiba: ® P25 SeriesDokument9 SeitenToshiba: ® P25 SeriesaleksandrNoch keine Bewertungen

- nb100 WellavDokument2 Seitennb100 Wellavlump coradirNoch keine Bewertungen

- Satellite A105s2051Dokument11 SeitenSatellite A105s2051Douglas Gaitan PotosmeNoch keine Bewertungen

- CD 1814146Dokument294 SeitenCD 1814146Abimilec MaestreNoch keine Bewertungen

- Features: High-Speed SDR Sdram Controller Core For Actel FpgasDokument6 SeitenFeatures: High-Speed SDR Sdram Controller Core For Actel FpgasSvraghava SripathiNoch keine Bewertungen

- PCIe NVMe FerriSSD PB ENDokument2 SeitenPCIe NVMe FerriSSD PB ENEduar AndresNoch keine Bewertungen

- LCD Screen LVDS ConnectorDokument1 SeiteLCD Screen LVDS ConnectorSIELAB C.A.Noch keine Bewertungen

- Controlador SED1335Dokument14 SeitenControlador SED1335Daniel BauerNoch keine Bewertungen

- Mpeg-2 SD Dta With Embedded Security: Features & BenefitsDokument2 SeitenMpeg-2 SD Dta With Embedded Security: Features & BenefitsLeonelNoch keine Bewertungen

- Cs4362a F2Dokument50 SeitenCs4362a F2raiksonNoch keine Bewertungen

- Tiernan AVC4000SD ManualDokument2 SeitenTiernan AVC4000SD ManualGromit32Noch keine Bewertungen

- bt869krf PDFDokument105 Seitenbt869krf PDFMariuszChreptakNoch keine Bewertungen

- Truvision NVR 22plus: Full Featured H.265 Network Video RecorderDokument2 SeitenTruvision NVR 22plus: Full Featured H.265 Network Video RecorderAlexandra CăpraruNoch keine Bewertungen

- ViaSat Secure Data Recorder Datasheet 008 WebDokument4 SeitenViaSat Secure Data Recorder Datasheet 008 WebgoucloudNoch keine Bewertungen

- RDV 780Dokument40 SeitenRDV 780Анатолий ЯковлевNoch keine Bewertungen

- Xbox Conexant-CX25870-871 DatasheetDokument291 SeitenXbox Conexant-CX25870-871 DatasheetMartin GiguereNoch keine Bewertungen

- V33500 TVDokument2 SeitenV33500 TVgoriath-fxNoch keine Bewertungen

- Audio Tda8569q Spec enDokument20 SeitenAudio Tda8569q Spec envetchboyNoch keine Bewertungen

- 120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyDokument13 Seiten120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyvetchboyNoch keine Bewertungen

- CD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)Dokument16 SeitenCD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)vetchboyNoch keine Bewertungen

- 2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsDokument10 Seiten2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsJosé VidalNoch keine Bewertungen

- Tda 7269aDokument7 SeitenTda 7269aAlexa DanNoch keine Bewertungen

- Dual Btl/Quad Power Amplifier For Car Radio: ProtectionsDokument14 SeitenDual Btl/Quad Power Amplifier For Car Radio: ProtectionsvetchboyNoch keine Bewertungen

- Audio Tda8510j Spec enDokument16 SeitenAudio Tda8510j Spec envetchboyNoch keine Bewertungen

- Audio Tda8567q Spec enDokument20 SeitenAudio Tda8567q Spec envetchboyNoch keine Bewertungen

- Audio Tda8567q Spec enDokument20 SeitenAudio Tda8567q Spec envetchboyNoch keine Bewertungen

- Tda 7313Dokument15 SeitenTda 7313jordachadiNoch keine Bewertungen

- TDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierDokument9 SeitenTDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierGerardo Moreno RenteriaNoch keine Bewertungen

- Tda 7265 2 x25 WDokument12 SeitenTda 7265 2 x25 WJavier CanaviriNoch keine Bewertungen

- 4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionDokument12 Seiten4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNoch keine Bewertungen

- 4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionDokument10 Seiten4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNoch keine Bewertungen

- Digital Controlled Stereo Audio Processor With Loudness: DescriptionDokument14 SeitenDigital Controlled Stereo Audio Processor With Loudness: DescriptionvetchboyNoch keine Bewertungen

- Tda 7296Dokument14 SeitenTda 7296Mayra GonzálezNoch keine Bewertungen

- Amplificador 20W RMS TDA2003 Con Placa PCBDokument15 SeitenAmplificador 20W RMS TDA2003 Con Placa PCBEnya Andrea Ribba Hernandez100% (5)

- Tda7294 PDFDokument16 SeitenTda7294 PDFRoger NunesNoch keine Bewertungen

- Audio Tda2002 Spec enDokument2 SeitenAudio Tda2002 Spec envetchboyNoch keine Bewertungen

- 10W Car Radio Audio Amplifier: DescriptionDokument11 Seiten10W Car Radio Audio Amplifier: DescriptionvetchboyNoch keine Bewertungen

- TDA 2822M CircuitoDokument11 SeitenTDA 2822M CircuitoDATA24Noch keine Bewertungen

- 30W Bridge Car Radio Amplifier: DescriptionDokument10 Seiten30W Bridge Car Radio Amplifier: DescriptionvetchboyNoch keine Bewertungen

- Tda 2004Dokument11 SeitenTda 2004Diana Belen Rodriguez HernandezNoch keine Bewertungen

- TDA1554Q 44W Audio AmplifierDokument11 SeitenTDA1554Q 44W Audio Amplifiersava7698Noch keine Bewertungen

- TA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyDokument18 SeitenTA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyvetchboyNoch keine Bewertungen

- Audio Tas5100a Spec enDokument15 SeitenAudio Tas5100a Spec envetchboyNoch keine Bewertungen

- STK442-110 70W Audio Power Amplifier SpecificationsDokument4 SeitenSTK442-110 70W Audio Power Amplifier SpecificationsIvan AsimovNoch keine Bewertungen

- Description: Angus Electronics Company LimitedDokument9 SeitenDescription: Angus Electronics Company LimitedvetchboyNoch keine Bewertungen

- Low Power Quad Operational Amplifiers: LM124 LM224 - LM324Dokument13 SeitenLow Power Quad Operational Amplifiers: LM124 LM224 - LM324vetchboyNoch keine Bewertungen

- Description: Angus Electronics Company LimitedDokument13 SeitenDescription: Angus Electronics Company LimitedvetchboyNoch keine Bewertungen

- Onkyo Ry-505 ManualDokument3 SeitenOnkyo Ry-505 Manualcarlos trinidad tapiaNoch keine Bewertungen

- DataDokument5 SeitenDataJomari DesioNoch keine Bewertungen

- MS-1756 Disassembly GuideDokument27 SeitenMS-1756 Disassembly GuideCarlos CuboNoch keine Bewertungen

- CM8340 Diagrama Fuente PDFDokument2 SeitenCM8340 Diagrama Fuente PDFLorenzo100% (2)

- Synchronization PCB: This Module Is One of A Series of Modules That Describe The Components of The M SystemDokument12 SeitenSynchronization PCB: This Module Is One of A Series of Modules That Describe The Components of The M SystemSatyajit KhuntiaNoch keine Bewertungen

- Fault Tracing: FMI 3: Checking The Injector CircuitDokument1 SeiteFault Tracing: FMI 3: Checking The Injector Circuituser1Noch keine Bewertungen

- Rycom Model 2172 Frequency Selective Voltmeter Maintenance-Manual W0585-6FD, 1967.Dokument27 SeitenRycom Model 2172 Frequency Selective Voltmeter Maintenance-Manual W0585-6FD, 1967.Bob Laughlin, KWØRLNoch keine Bewertungen

- Asus Notebook Certificate Repair Training Engineer (CHER) Level 2-1 PDFDokument44 SeitenAsus Notebook Certificate Repair Training Engineer (CHER) Level 2-1 PDFGerminii100% (1)

- Schneider P740 Busbar ProtectionDokument35 SeitenSchneider P740 Busbar ProtectionNguyễn Phúc ThưởngNoch keine Bewertungen

- TDA6107JFDokument20 SeitenTDA6107JFZakaria Al SharabiNoch keine Bewertungen

- Shimaden Digital Controller Shimaden Digital Controller: SR1 / SR3 SR1 / SR3 / SR4Dokument2 SeitenShimaden Digital Controller Shimaden Digital Controller: SR1 / SR3 SR1 / SR3 / SR4Paul AlvarezNoch keine Bewertungen

- Et80, Et1010, Et1080Dokument4 SeitenEt80, Et1010, Et1080KUNONoch keine Bewertungen

- ETI ElectronicsDigest 1982 Summer PDFDokument100 SeitenETI ElectronicsDigest 1982 Summer PDFIanNoch keine Bewertungen

- Nanotechnology Introduction and Future ApplicationsDokument20 SeitenNanotechnology Introduction and Future ApplicationsBaskaran KathirvelNoch keine Bewertungen

- LTE Radio Interface ProceduresDokument116 SeitenLTE Radio Interface ProceduresMuhammad Ali KhalidNoch keine Bewertungen

- 230517-VFD Compliance SampleDokument4 Seiten230517-VFD Compliance SampleShuaib MuazzamNoch keine Bewertungen

- 630 00610 01 12.01 14.0 C3-Maintenance-Repair-GuideDokument67 Seiten630 00610 01 12.01 14.0 C3-Maintenance-Repair-GuidenarobaNoch keine Bewertungen

- PMM l2-10 Amn ManualDokument21 SeitenPMM l2-10 Amn ManualMarco Vinicio BazzottiNoch keine Bewertungen

- Lecture 7: Laser Oscillation: You Can Download and Read Reading Materials PDFDokument14 SeitenLecture 7: Laser Oscillation: You Can Download and Read Reading Materials PDFAl-Ami SarkerNoch keine Bewertungen

- 06 June 1990Dokument108 Seiten06 June 1990Monitoring TimesNoch keine Bewertungen

- DC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnDokument10 SeitenDC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnRomitan AlexandraNoch keine Bewertungen

- GSM-R 6.0 Abis Over IP (OFFE00004638 - PMD188ZH A)Dokument24 SeitenGSM-R 6.0 Abis Over IP (OFFE00004638 - PMD188ZH A)gab man100% (1)

- Arduino: Arduino Is An Open-Source Single-Board Microcontroller, Descendant of The Open-Source WiringDokument2 SeitenArduino: Arduino Is An Open-Source Single-Board Microcontroller, Descendant of The Open-Source WiringratheeshbrNoch keine Bewertungen

- Gigacore Ethernet Switches: Specifications (1/2)Dokument2 SeitenGigacore Ethernet Switches: Specifications (1/2)Pablo BordinoNoch keine Bewertungen

- Open Source Development BoardsDokument20 SeitenOpen Source Development BoardsRemyaNoch keine Bewertungen

- dsp-G1 Manual v1.0Dokument6 Seitendsp-G1 Manual v1.0vicher2020Noch keine Bewertungen

- Cisco Ata 187 PDFDokument6 SeitenCisco Ata 187 PDFsankifkoNoch keine Bewertungen

- High-Efficiency 255 W ATX Power Supply Reference DesignDokument84 SeitenHigh-Efficiency 255 W ATX Power Supply Reference DesignYung SangNoch keine Bewertungen

- Huawei OptiXstar EG8245X6-8N Quick StartDokument16 SeitenHuawei OptiXstar EG8245X6-8N Quick Startbloptra18Noch keine Bewertungen

- Finder Relays Series 60 PDFDokument6 SeitenFinder Relays Series 60 PDFzrcjsyllNoch keine Bewertungen