Beruflich Dokumente

Kultur Dokumente

Atf36077 Appl2

Hochgeladen von

Johnny TienOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Atf36077 Appl2

Hochgeladen von

Johnny TienCopyright:

Verfügbare Formate

L Band Amplifier using the ATF-36077 Low Noise PHEMT

Application Note 1128

Introduction

The Agilent Technologies ATF36077 PHEMT device is described in a low noise amplifier that can be easily optimized for any spot frequency in the 900 through 1800 MHz frequency range. The ATF-36077 is intended to be used as a low noise amplifier in 12 GHz DBS applications providing 0.5 dB noise figures. The device is capable of noise figures below 0.4 dB at frequencies below 2 GHz. Although the device has an inherent noise figure of around 0.2 dB, actual circuit losses limit the minimum noise figure that can be obtained at about 0.3 dB.

pedance on the device over a wide frequency range. In the case of the ATF-36077, a 50 ohm resistor and a small amount of series inductance is used to provide shunt loading of the device. The series inductance also provides some impedance matching. An additional series resistor directly off the drain is also used to enhance stability. This circuit topology produces acceptable gain while ensuring a good output match and retaining stability over as wide a bandwidth as possible. Obtaining the lowest possible noise figure from the device requires that the input matching network convert the nominal 50

ohm source impedance to opt. In the case of the ATF-36077 at 1.3 GHz, a series inductor provides a good noise match. The source leads of the ATF-36077 must be grounded with minimal source inductance. The use of the customary bypassed source resistor technique for biasing a typical MESFET such as the ATF-10136 will not work very well with a PHEMT device. Excessive source inductance will cause the device to oscillate at frequencies around 20 to 22 GHz. The ATF-36077 will perform very well if plated through holes are placed directly under the source leads adjacent to the package and if the printed cir-

Design

Achieving the associated gain of which the device is capable is difficult since the device is not inherently stable at the desired operating frequency. It is not enough that the amplifier be stable at the operating frequency it must be stable at all frequencies. Any out-of-band oscillation will make the amplifier unusable. The simplest technique to ensure broad-band stability is to resistively load the drain. Resistive loading produces a constant im-

Table 1. ATF-36077 LNA Performance

Frequency (MHz) 1100 1150 1200 1250 1300 1350 1400 1450 1500 1550 1600 Gain (dB) 19.5 20.8 22 22.4 22.6 22 21.2 20.5 19.5 18.6 17.5 Noise Figure (dB) 0.53 0.60 0.44 0.38 0.33 0.31 0.28 0.28 0.30 0.30 0.40

cuit board thickness is kept at 0.031 inch or less. A schematic diagram and parts list are shown in Figure 1. The schematic diagram suggests the use of active biasing to preset the bias point. The device is biased at a nominal Vds of 1.5 Volts and an Ids of 10 mA. Its operation will be explained in the next section.

Passive biasing can be used but it will require that a potentiometer be connected to the output of the dc to dc converter U1 to set the gate voltage bias required for nominal drain current.

Performance

The performance of the amplifier is shown in Table 1. Since the loss of the input microstripline can

Q1 R10 C2 Zo R3 OUTPUT

INPUT Zo

C1 Zo

L1 Z1

L2

LL1/2

add appreciable loss which adds directly to noise figure, the breadboard amplifier was built without any significant microstrip etch in the input network. The optimum noise figure is about 0.3 dB and this occurs over about a 100 MHz bandwidth, centered at 1400 MHz. The noise figure rises to 0.4 dB at 1600 MHz and 0.44 dB at 1200 MHz making the amplifier usable for broadband GPS applications. The amplifier can be tuned for other frequencies in the 900 through 1800 MHz frequency range by either increasing or decreasing the value of inductor L1.

R1 C4 C7

L2

Biasing

C8

R7

Q2 R9 R6 R8 C12

3V U2 C13

VDD

R5

U1 C1 = 22 pF CHIP CAPACITOR C2 = 100 pF CHIP CAPACITOR C3 = NOT USED C4, C7 = 1000 pF CHIP CAPACITOR C5, C6 = NOT USED, GROUND SOURCES DIRECTLY C9 = NOT USED C8, C12, C13 = 0.1 F CHIP CAPACITOR C10, C11 = 10 F CHIP CAPACITOR L1 = 6T 0.007" DIA. WIRE, 0.050" ID, 0.14" LENGTH L2 = 0.18 TO 0.33 H RFC LL1, LL2 = PLATED THROUGH HOLES TO BACKSIDE GROUNDPLANE DIRECTLY UNDER EACH LEAD Q1 = AGILENT TECHNOLOGIES ATF-36077 PHEMT R1 = 100 OHM CHIP RESISTOR R2 = NOT USED R3 = 50 OHM CHIP RESISTOR R4 = NOT USED R5, R7 = 10 k OHM CHIP RESISTOR R6 = 1.3 k OHM CHIP RESISTOR R8 = 2.7 k OHM CHIP RESISTOR (SETS DRAIN VOLTAGE) R9 = 270 OHM CHIP RESISTOR (SETS DRAIN CURRENT) R10 = 16 OHM CHIP RESISTOR (UP TO 27 OHMS OK) U1 = LINEAR TECHNOLOGY LTC1044CS8 VOLTAGE CONVERTER U2 = 5 VOLT REGULATOR TOKO TK11650U U3 = OPTIONAL MMIC AMP - NOT USED Zo = 50 OHM MICROSTRIPLINE, MINIMIZE LENGTH ON INPUT TO MINIMIZE LOSS AND EFFECT ON NOISE FIGURE C10 C11

The preferred method of biasing FETs is the use of an active bias network as described in Figure 1. Although active biasing does add cost by requiring extra components, including a way of generating a negative voltage, the advantages generally outweigh the disadvantages. Active biasing offers the advantage that variations in pinchoff voltage and Idss will not necessitate a change in either the source or drain resistor value for a given bias condition. The active bias network automatically sets Vgs for the desired drain current. The typical active biasing scheme for FETs requires that the source leads be grounded and an additional supply be used to generate the negative voltage required at the gate for typical operation. Referring to Figure 1, resistors R6 and R8 provide a regulated voltage at the base of Q2. The voltage is increased by 0.7 volts by virtue of the emitter-base junction of Q2 and then applied to the drain of Q1. Since R3 and R10 are in series with the drain, the voltage drop

Figure 1. Schematic and Parts List for ATF-36077 LNA

across R3 and R10 must be taken into account when designing the bias circuitry. Resistor R9 is connected between two regulated voltage points and therefore sets the drain current. Q1 gate is connected to a voltage divider consisting of R5 and R7 connected between the collector of Q2 and a negative voltage converter. The gate voltage can then assume a value necessary to sustain the desired drain current.

2.1"

UHFLNC GaAsFET DEMO BOARD .031 FR-4 AJW12/96 C5 R10 C2 INPUT C1 U3 C3 OUTPUT L2 R1 C4

C11

C6 R2

C7

R3 C8

R4 C9 C13 Vdd

R5

R7 R6

R9 U2 R8 C12

C10

U1

GaAsFET Demo Board

A typical printed circuit board built on 0.031 inch FR-4/G-10 is shown in Figures 2 and 3. This board is described in detail in Application Note 1076. The input 50 microstripline has significant loss which can mask some of the device noise figure. The measured loss of the input microstripline excluding the blocking capacitor C1 is 0.3 dB at 1600 MHz and 0.15 dB at 900 MHz. Keep this loss in mind when evaluating the devices as most computer simulations appear to be optimistic about dielectric board losses and therefore give an optimistic (lower) prediction of noise figure. In order to best evaluate the noise performance of the ATF-36077 without excessive input etch losses, the board shown in Figures 2 and 3 was modified. The input connector was soldered to the bottom groundplane and installed as close as possible to the input inductor L1. This allowed for the removal of most of the input etch. The performance shown in Table 1 reflects the changes to the demo board as described above. An earlier version of the artwork had the locations of R1 and L2

Figure 2. GaAsFET Demo Board showing component placement

2.1"

UHFLNC AJW12/96 INPUT C1 L2 R1 C4 R5

C5 L1 C6 R2

GaAsFET DEMO BOARD 0.031 FR-4 R10 C2 U3 C3 OUTPUT R3 C7 C8

C11

R4 C9 C13 R9 U2 R8 C12 Vdd

R7 Q2 R6

C10

U1

Figure 3. GaAsFET Demo Board 1x Artwork

reversed. When R1 is nearest the 50 microstripline, the capacitive effect of the mounting pad at the junction of R1 and L2 shunts R1 to ground. The net result is increased noise figure. It is therefore better to have the inductor first then followed by the resistor since the impedance of the choke is higher than that of the resistor. It is very difficult to obtain very low noise, high gain and unconditional stability with a high performance HEMT at L Band frequencies. Therefore, resistor R10, shown in Figure 1, is used in series with the drain to reduce

gain and improve stability. Increasing this resistor much beyond 50 will have an adverse effect on noise figure, i.e. >0.2 dB.

In Case of Difficulty

Generally the noise figure should be within a couple of tenths of a dB of that indicated in the performance table and gain within a few dB. If the noise figure or gain is not as expected then check the bias conditions. Is the Vds between 1.5 and 2 volts and drain current about 10 mA? If the bias voltage and current are adjustable, does performance maximize at the rated bias conditions or at some other set of values? If so,

then the problem may be excessive source inductance which is causing a high frequency oscillation. If a device is oscillating at any frequency, even an out of the band frequency, it may be difficult to obtain rated performance. Make sure the plated through holes are as close to the device as possible, i.e., 0.02 to 0.03 inch may be too long. If the problem is inband stability, then the solution is to add series resistance between the drain and output connector. Increase the value of R10. Additional gain reduction can also be had by decreasing the length of the shunt output inductor in series with R3. In some cases, higher than expected noise figure can be attributed to noise from the dc to dc converter or the PNP transistor used for active biasing. Use of a 0.1 F bypass capacitor in parallel with C4 and at location C8 should help. The use of a lossy or low Q RF choke for L2 can contribute to an increase in noise figure. The use of a small molded RF choke for L2 works well in prototypes. For surface mount applications be sure to choose a high Q wire wound choke such as those made by CoilCraft.

In some instances, the enclosure can cause undesirable feedback across the circuit board which can cause instabilities. This phenomena is true of any amplifier design. A cross sectional view of the housing can be viewed as a piece of waveguide whose dimensions, both width and height, determine the band of frequencies that it may pass with minimal attenuation. A combination of the amplifier response along with the housing response could contribute to instabilities if not controlled. The use of low profile surface mount components will minimize this effect. Making sure that the cover is no closer to the printed circuit board than is necessary will minimize coupling from the cover. It is preferred to have the cover at least 0.3 to 0.5 inches above the circuit board. The use of ECOSORBTM can be used on the cover to minimize reflections if the cover has to be in close proximity to the board. The use of a metal divider hanging down from the cover is also another method of breaking up enclosure effects.

cuit has been shown that provides stable L Band operation. The single-element input matching network provides very good performance in this frequency range and offers the greatest bandwidth and least sensitivity to manufacturing tolerances. The resistive loading in the output network provides the best broadband stable performance by sacrificing some in-band gain.

Conclusion

The ATF-36077 can provide less than 0.4 dB noise figures over several hundred MHz of bandwidth at L Band frequencies. A simple cir-

www.semiconductor.agilent.com Data subject to change. Copyright 1999 Agilent Technologies, Inc. 5966-0783E (11/99)

Das könnte Ihnen auch gefallen

- A 100MHz To 500MHz Low Noise Feedback Amplifier Using ATF-54143 (AN5057 Avago)Dokument8 SeitenA 100MHz To 500MHz Low Noise Feedback Amplifier Using ATF-54143 (AN5057 Avago)XollloXNoch keine Bewertungen

- Quad Power Amplifier For Car Radio: Protections: DescriptionDokument18 SeitenQuad Power Amplifier For Car Radio: Protections: DescriptionMiloud ChouguiNoch keine Bewertungen

- TV Modulator Circuit: Semiconductor Technical DataDokument10 SeitenTV Modulator Circuit: Semiconductor Technical Databanduat83Noch keine Bewertungen

- An 762 Rev 0Dokument10 SeitenAn 762 Rev 0Diego MotoqueroNoch keine Bewertungen

- TDA7370B: Quad Power Amplifier For Car RadioDokument18 SeitenTDA7370B: Quad Power Amplifier For Car RadioMiloud ChouguiNoch keine Bewertungen

- 10W Car Radio Audio Amplifier: DescriptionDokument12 Seiten10W Car Radio Audio Amplifier: DescriptionAhmad MahrojiNoch keine Bewertungen

- AD831-MIXER 200-500MHzDokument17 SeitenAD831-MIXER 200-500MHzChelaru CosminNoch keine Bewertungen

- An-779 Low-Distortion 1.6 To 30 MHZ SSB Driver DesignsDokument10 SeitenAn-779 Low-Distortion 1.6 To 30 MHZ SSB Driver DesignsEdward YanezNoch keine Bewertungen

- TDA2030A: 18W Hi-Fi Amplifier and 35W DriverDokument15 SeitenTDA2030A: 18W Hi-Fi Amplifier and 35W Driverdborcic61Noch keine Bewertungen

- AtgDokument8 SeitenAtgdarenNoch keine Bewertungen

- 28W Hi-Fi Audio Power Amplifier With Mute / Stand-By: DescriptionDokument11 Seiten28W Hi-Fi Audio Power Amplifier With Mute / Stand-By: DescriptionbaczonifNoch keine Bewertungen

- Instrumentation AmplifiersDokument8 SeitenInstrumentation AmplifiersNima MoeenNoch keine Bewertungen

- Electronique - Audio - Microphone Valve PreampDokument7 SeitenElectronique - Audio - Microphone Valve PreampkoukihamedNoch keine Bewertungen

- Class D Amplifier With Maximum Power Adjustable From 20W To 300WDokument13 SeitenClass D Amplifier With Maximum Power Adjustable From 20W To 300Wramontv032428Noch keine Bewertungen

- Class D Amplifier With Maximum Power Adjustable From 20W To 300WDokument13 SeitenClass D Amplifier With Maximum Power Adjustable From 20W To 300Wramontv032428100% (1)

- La 4108Dokument12 SeitenLa 4108andrzej_w_k100% (3)

- LM1894 Dynamic Noise Reduction System DNR: General DescriptionDokument10 SeitenLM1894 Dynamic Noise Reduction System DNR: General DescriptionKoszegi AttilaNoch keine Bewertungen

- ADSL Modems That Use The LT1886 As A Line Driver Yield Long Reach and Fast Data RatesDokument2 SeitenADSL Modems That Use The LT1886 As A Line Driver Yield Long Reach and Fast Data Ratesprasad357Noch keine Bewertungen

- DN 140Dokument16 SeitenDN 140dughirNoch keine Bewertungen

- Precision Full-Wave Rectifier, Dual-Supply: TI Precision Designs: Verified DesignDokument24 SeitenPrecision Full-Wave Rectifier, Dual-Supply: TI Precision Designs: Verified DesignkumargpalaniNoch keine Bewertungen

- AD831Dokument16 SeitenAD831Vicent Ortiz GonzalezNoch keine Bewertungen

- Mosquita40m TransceiverDokument39 SeitenMosquita40m TransceiverSzakacsEnikoNoch keine Bewertungen

- Linear Amps For Mobile OperationDokument10 SeitenLinear Amps For Mobile OperationIan McNairNoch keine Bewertungen

- TDA 2030AV 0sxazk6r88ww67x153ipf6805zpy PDFDokument16 SeitenTDA 2030AV 0sxazk6r88ww67x153ipf6805zpy PDFOsman KoçakNoch keine Bewertungen

- Iraudamp 1Dokument22 SeitenIraudamp 1luizcpimentaNoch keine Bewertungen

- TDA2030A: 18W Hi-Fi Amplifier and 35W DriverDokument15 SeitenTDA2030A: 18W Hi-Fi Amplifier and 35W DriverAlex UngureanuNoch keine Bewertungen

- TDA2030ADokument15 SeitenTDA2030AAtsivatlaNoch keine Bewertungen

- Amp DesignDokument10 SeitenAmp DesignakeedtheNoch keine Bewertungen

- Low Voltage Transmission Circuit With Dialler Interface: ILA1062ADokument9 SeitenLow Voltage Transmission Circuit With Dialler Interface: ILA1062AVeer GupteNoch keine Bewertungen

- Datasheet TDA2052Dokument14 SeitenDatasheet TDA2052FrancoilNoch keine Bewertungen

- Atf36077 ApplDokument2 SeitenAtf36077 ApplJohnny TienNoch keine Bewertungen

- Datasheet Tda 7384 26w Car 4 CH Audio PDFDokument9 SeitenDatasheet Tda 7384 26w Car 4 CH Audio PDFban4444Noch keine Bewertungen

- 50 W A.F. Amplifier: Uses Only One ICDokument3 Seiten50 W A.F. Amplifier: Uses Only One ICSuda KrishnarjunaraoNoch keine Bewertungen

- lm386 PDFDokument11 Seitenlm386 PDFNicolás MoraNoch keine Bewertungen

- 10W Car Radio Audio Amplifier: DescriptionDokument10 Seiten10W Car Radio Audio Amplifier: DescriptionLuis Arturo Leiva MonjarasNoch keine Bewertungen

- Motorola AN758Dokument16 SeitenMotorola AN758xavir111Noch keine Bewertungen

- Band-Pass Filtered, Inverting - 40 DB Attenuator, 10 HZ - 100 KHZ, 0.1 DB ErrorDokument20 SeitenBand-Pass Filtered, Inverting - 40 DB Attenuator, 10 HZ - 100 KHZ, 0.1 DB ErrorSalman ZafarNoch keine Bewertungen

- LM1812 Ultrasonic Transceiver: General DescriptionDokument10 SeitenLM1812 Ultrasonic Transceiver: General DescriptionYogesh RamdasiNoch keine Bewertungen

- 10W Audio Amplifier With Bass-BoostDokument2 Seiten10W Audio Amplifier With Bass-Boostrik206Noch keine Bewertungen

- Audio Circuits Using The NE5532/34Dokument11 SeitenAudio Circuits Using The NE5532/34Jose Simon Bolivar MoranNoch keine Bewertungen

- Lm386 DatasheetDokument7 SeitenLm386 DatasheetJM Carrasco HottmanNoch keine Bewertungen

- Amplificador Final de VálvulasDokument6 SeitenAmplificador Final de VálvulasTammy WashingtonNoch keine Bewertungen

- 06616415Dokument5 Seiten06616415jitu_4Noch keine Bewertungen

- The Ovation E-Amp: A 180 W High-Fidelity Audio Power AmplifierDokument61 SeitenThe Ovation E-Amp: A 180 W High-Fidelity Audio Power AmplifierNini Farribas100% (1)

- Getting The Right: FOR SDokument12 SeitenGetting The Right: FOR SferdinandNoch keine Bewertungen

- Design Guidelines For JFET Audio Preamplifier CircuitsDokument3 SeitenDesign Guidelines For JFET Audio Preamplifier CircuitsAbegail Ada Calayo MontemayorNoch keine Bewertungen

- INA106Dokument14 SeitenINA106Juan Pablo RosalesNoch keine Bewertungen

- Data Sheet IC Ina106Dokument14 SeitenData Sheet IC Ina106Luqman BhanuNoch keine Bewertungen

- Low Voltage Audio Power AmplifierDokument9 SeitenLow Voltage Audio Power AmplifierJuan V Castro SotoNoch keine Bewertungen

- LYNX Audio Amplifier 275W 4 OhmiDokument11 SeitenLYNX Audio Amplifier 275W 4 OhmiDanut777750% (2)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Iraudamp1 PDFDokument22 SeitenIraudamp1 PDFamijoski6051Noch keine Bewertungen

- EB-104 Get 600 Watts RF From Four Power FETsDokument9 SeitenEB-104 Get 600 Watts RF From Four Power FETsEdward YanezNoch keine Bewertungen

- Unisonic Technologies Co.,: Low Voltage Audio Power AmplifierDokument7 SeitenUnisonic Technologies Co.,: Low Voltage Audio Power Amplifierantonio_forgioneNoch keine Bewertungen

- Designing With JFETSDokument4 SeitenDesigning With JFETSGreg PetersNoch keine Bewertungen

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsVon EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorVon Everand110 Waveform Generator Projects for the Home ConstructorBewertung: 4 von 5 Sternen4/5 (1)

- Sim ReportDokument17 SeitenSim ReportJohnny TienNoch keine Bewertungen

- Av02 0608en, 0Dokument6 SeitenAv02 0608en, 0Johnny TienNoch keine Bewertungen

- HP AN1129 Low Noise 2.3GHz Amplifier ATF-36077Dokument4 SeitenHP AN1129 Low Noise 2.3GHz Amplifier ATF-36077Johnny TienNoch keine Bewertungen

- HP AN1129 Low Noise 2.3GHz Amplifier ATF-36077Dokument4 SeitenHP AN1129 Low Noise 2.3GHz Amplifier ATF-36077Johnny TienNoch keine Bewertungen

- Sayre 1 0100Dokument21 SeitenSayre 1 0100Johnny TienNoch keine Bewertungen

- Sayre 1 0100Dokument21 SeitenSayre 1 0100Johnny TienNoch keine Bewertungen

- Av02 0608en, 0Dokument6 SeitenAv02 0608en, 0Johnny TienNoch keine Bewertungen

- Atf36077 ApplDokument2 SeitenAtf36077 ApplJohnny TienNoch keine Bewertungen

- Agilent HMMC-5038 38 GHZ Lna: Data SheetDokument6 SeitenAgilent HMMC-5038 38 GHZ Lna: Data SheetJohnny TienNoch keine Bewertungen

- Amt A0061Dokument4 SeitenAmt A0061Johnny TienNoch keine Bewertungen

- 5989 1609enDokument10 Seiten5989 1609enJohnny TienNoch keine Bewertungen

- Engineering, Computing and Architecture: Journal ofDokument13 SeitenEngineering, Computing and Architecture: Journal ofOsel Novandi WitohendroNoch keine Bewertungen

- 137topic No.11 Dr. Pham Xuan MaiDokument41 Seiten137topic No.11 Dr. Pham Xuan MaiJohnny TienNoch keine Bewertungen

- How To Build A Slayer ExciterDokument6 SeitenHow To Build A Slayer ExciterKevin BinnyNoch keine Bewertungen

- Ambo University Woliso Campus, Technology and Informatics School Department of Computer ScienceDokument27 SeitenAmbo University Woliso Campus, Technology and Informatics School Department of Computer ScienceNoel GirmaNoch keine Bewertungen

- Microcontroller-Based System For Voltage Monitoring, Protection and Recovery Using Proteus VSM SoftwareDokument5 SeitenMicrocontroller-Based System For Voltage Monitoring, Protection and Recovery Using Proteus VSM SoftwareFuh ValleryNoch keine Bewertungen

- MN 2 011 32Dokument3 SeitenMN 2 011 32Chris AshleyNoch keine Bewertungen

- Wire Current RatingsDokument1 SeiteWire Current Ratingszul5107Noch keine Bewertungen

- Sinusoidal Steady State Power Calculations: Assessment ProblemsDokument54 SeitenSinusoidal Steady State Power Calculations: Assessment ProblemsSantiago LeonNoch keine Bewertungen

- This Project Is Available On 3 Different PC Boards:: Diesel Sound 3 - Called Diesel Sound 4 WattDokument11 SeitenThis Project Is Available On 3 Different PC Boards:: Diesel Sound 3 - Called Diesel Sound 4 WattΔημητριος ΣταθηςNoch keine Bewertungen

- STCC2540: USB Charging Controller With Integrated Power SwitchDokument32 SeitenSTCC2540: USB Charging Controller With Integrated Power SwitchAndré Andersen PicerniNoch keine Bewertungen

- Robust Memristors Based On Layered Two-Dimensional MaterialsDokument31 SeitenRobust Memristors Based On Layered Two-Dimensional Materialssritama royNoch keine Bewertungen

- TechRef 3 W TransformerDokument22 SeitenTechRef 3 W TransformerbalboinoNoch keine Bewertungen

- Ten Tec - 1253 - Manual 12 12Dokument68 SeitenTen Tec - 1253 - Manual 12 12va3ttnNoch keine Bewertungen

- Rg214 Rgflex Coax Braided Cable: Product Data Sheet RG214-50JFDokument1 SeiteRg214 Rgflex Coax Braided Cable: Product Data Sheet RG214-50JFFaqir Khan JadoonNoch keine Bewertungen

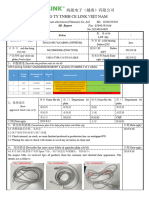

- 海能电子(越南)有限公司 Công Ty Tnhh Ce Link Việt Nam: 8D Report Fax: 02043595566Dokument5 Seiten海能电子(越南)有限公司 Công Ty Tnhh Ce Link Việt Nam: 8D Report Fax: 02043595566chosandemNoch keine Bewertungen

- Chapter 6. Biopotential Amplifiers Michael R. NeumanDokument33 SeitenChapter 6. Biopotential Amplifiers Michael R. NeumanCarl AzzopardiNoch keine Bewertungen

- As 101 PDFDokument7 SeitenAs 101 PDFHari NairNoch keine Bewertungen

- M6 Manual V1.0Dokument38 SeitenM6 Manual V1.0joehowNoch keine Bewertungen

- 3E Active Filter Material Submittal - Dubai I ProjectDokument84 Seiten3E Active Filter Material Submittal - Dubai I ProjectKhalil RamadanNoch keine Bewertungen

- Electrical Safety - HLS CMTGDokument9 SeitenElectrical Safety - HLS CMTGRery Dwi SNoch keine Bewertungen

- 520SL SLB Guide en USDokument2 Seiten520SL SLB Guide en USBruce CanvasNoch keine Bewertungen

- Microwave Theory and TechniquesDokument599 SeitenMicrowave Theory and Techniquesdhanushcm2001Noch keine Bewertungen

- Delay Calculations: Introduction To Cmos Vlsi DesignDokument27 SeitenDelay Calculations: Introduction To Cmos Vlsi DesignbiboNoch keine Bewertungen

- AMPERESDokument1 SeiteAMPERESJericho MoralesNoch keine Bewertungen

- Ats 12Dokument53 SeitenAts 12RagavanNoch keine Bewertungen

- SSC Apg001 enDokument20 SeitenSSC Apg001 enapi-279886039Noch keine Bewertungen

- Cu 0.95 LLF 0.8: Instalasi Listrik Penentuan Jumlah Titik LampuDokument28 SeitenCu 0.95 LLF 0.8: Instalasi Listrik Penentuan Jumlah Titik Lampumuhammad junaidiNoch keine Bewertungen

- Grobal Welder PDFDokument4 SeitenGrobal Welder PDFJun quiritNoch keine Bewertungen

- Battery Charger: Automotive EquipmentDokument1 SeiteBattery Charger: Automotive Equipmentwahyufirmansyah.officeNoch keine Bewertungen

- DTC Office Door LockDokument252 SeitenDTC Office Door LockBabu ChittilappillyNoch keine Bewertungen

- M II - Electrostatics Class Material@Part IDokument70 SeitenM II - Electrostatics Class Material@Part ISurendar VijayNoch keine Bewertungen

- Digital MultimeterDokument9 SeitenDigital MultimeterJon HimesNoch keine Bewertungen