Beruflich Dokumente

Kultur Dokumente

Verilog Lec 1

Hochgeladen von

Ali Ahmad0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

18 Ansichten22 Seitentrerwe

Copyright

© Attribution Non-Commercial (BY-NC)

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldentrerwe

Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

18 Ansichten22 SeitenVerilog Lec 1

Hochgeladen von

Ali Ahmadtrerwe

Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 22

1

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Section 2

Sample Design

2

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

The Verilog Module

module name (ports);

// port declarations

// data type declarations

// Iunctionality,

instantiations, timing, etc.

endmodule

Modules are the basic building

blocks in Verilog.

Every module starts with the

keyword module, a unique name,

and ends with endmodule.

The descriptions oI the logic

being modeled are placed within

the module.

Modules can represent anything

Irom a low level logic block to a

high level system.

Sample Design: 4-bit adder

Every level oI hierarchy uses the module/endmodule statements, no matter what the Iunctionality is inside. The

module is the building block Ior all designs in Verilog.

3

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

1 Bit Adder

a

b

ci

sum

co

1 1 1 1 1

0 1 0 1 1

0 1 1 0 1

1 0 0 0 1

0 1 1 1 0

1 0 0 1 0

1 0 1 0 0

0 0 0 0 0

SUM CO CI B A

Here`s the Iunctionality oI a 1-bit adder. Now let`s design it in Verilog.

4

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

1 Bit Adder Module

Module deIinition and port list.

module addbit (a, b, ci, sum, co);

// port declarations

// data type declarations

// Iunctionality,

endmodule

a

b

ci

sum

co

module is a keyword in Verilog

aaabit is a user-deIined name (identiIier), we`ll discuss the rules Ior identiIiers a little later in the course.

The port list (a, b, ci, sum, co) can be in any order. Also, the port names Iollow the same identiIier rules.

5

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

1 Bit Adder Port Declarations

Port declarations (any order)

module addbit (a, b, ci, sum, co);

output sum, co;

input a, b, ci;

// data type declarations

// Iunctionality,

endmodule

a

b

ci

sum

co

The port type declaration (input, output, or inout) can be in any order. Also, the ports can be in any order within the

declaration. For example, the Iollowing would be legal port declarations:

output co, sum;

input ci, a, b;

---

input b, ci, a;

output sum,co;

6

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

1 Bit Adder Data Type Declarations

Data type declarations

(any order)

module addbit (a, b, ci, sum, co);

output sum, co;

input a, b, ci;

wire a, b, ci;

reg sum, co;

// Iunctionality,

endmodule

a

b

ci

sum

co

Data type declarations can be an in any order. As a general rule, they Iollow the port declarations and are declared

beIore they`re used.

The wire data type is the deIault in Verilog. I have added here to show that we`re declaring all data types.

However, iI I did not include the line: wire a, b, ci, Verilog would still deIault the data type Ior a, b, and ci to a 1-

bit wire. Any signal/input that is wider than 1-bit has to be explicitly declared. For example, iI a` is a 4-bit wide

bus, it would have to be declared as such.

The reg data type declaration is required Ior any signal/output that is the LHS oI an assignment in a procedural

block. There will be much more on this topic later. For now just remember that iI a signal/output is on the LHS oI

an assignment in a procedure block, you have to declare it as a reg Iirst.

7

The concatenation construct }, saves steps in making the assignment to co and sum. Without it, you would

have to declare in intermediate 2-bit variable, and make individual assignments:

module addbit (a, b, ci, sum, co);

output sum, co;

input a, b, ci;

wire a, b, ci;

reg sum, co;

reg |1:0] temp;

always (a or b or ci) begin

temp a b ci;

co temp|1];

sum temp|0];

end

endmodule

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

1 Bit Adder Functionality

Functionality

module addbit (a, b, ci, sum, co);

output sum, co;

input a, b, ci;

wire a, b, ci;

reg sum, co;

always (a or b or ci) begin

co, sum} a b ci;

end

endmodule

a

b

ci

sum

co

-Note: }` means concatenation

8

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

4 Bit Adder Module Instantiation

Instantiate 4 1-bit adders to

create a 4-bit adder

module add4bits {result, carry, r1, r2, ci);

input [3:] r1, r2;

input ci;

output [3:] result;

output carry;

wire [3:] r1, r2, result;

wire ci, carry, c1, c2, c3;

addbit u1 {r1[], r2[], ci, result[], c1);

addbit u2 {r1[1], r2[1], c1, result[1], c2);

addbit u3 {r1[2], r2[2], c2, result[2], c3);

addbit u4 {r1[3], r2[3], c3, result[3], carry);

endmodule

a

b

ci

sum

co

a

b

ci

sum

co

a

b

ci

sum

co

a

b

ci

sum

co

carry

ci

r1|0]

r2|0]

r1|1]

r2|1]

r1|2]

r2|2]

r1|3]

r2|3]

result|0]

result|1]

result|2]

result|3]

Notice that each instance oI aaabit has a unique instance name such as u1, u2, etc. This is a requirement in

Verilog; whenever you instantiate a lower level module you must use an instance name to deIine each instance.

The instance name Iollows the rules oI Verilog identiIiers.

Notice that r1, r2, and result are 4-bit wide busses. The | ] nomenclature signiIies each individual bit oI the bus.

9

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Named vs. Positional Port Connections

There are two methods Ior making connections to

modules during instantiation:

Ordered List: The signals to be connected must appear in the module

instantiation in the same order as the port order in the module`s

deIinition.

Port Named List: The signals to be connected are speciIied using the

port name in the module deIinition. Order is irrelevant using this

method.

Given: module aa21 (Q, A, B);

Instances: aa21 u1 (myq, mya, myb); // ordered list

aa21 u2 (.A(mya), .B(myb), .Q(myq)); // port named list

The Iastest way to instantiate a lower level module is to use the Oraerea List method. Sometimes, the Iastest isn`t

always the saIest way. The saIest way to ensure that all ports are connected and connected correctly is to use the

Port Namea List method.

10

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Simulating in Verilog

Required components

Stimulus

Device Under Test

(DUT)

Response Generation

and VeriIication

DUT

Stimulus

Response

Testbench

Our DUT in this case is the 4-bit Adder that we`ve built Irom 1-bit Adders.

11

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Testbench

module testbench;

// Data type declarations

// Instantiate modules

// Apply stimulus

// Display results

endmodule

Why aren`t there ports in

the testbench?

The testbench is always the top level module in your design. In a sense, it surrounds your design. The testbench

provides stimulus to the design and receiving Ieedback Irom the design. In this example we`ll show how a simple

testbench works.

The name testbench is a user deIined name. The name you use Ior your testbench can be any legal identiIier.

12

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Testbench

module testbench;

// Data type declaration

// Instantiate modules (DUT)

// Apply stimulus

// Display results

endmodule

module testbench;

reg |3:0] r1, r2;

reg ci;

wire |3:0] result;

add4bits u1 (result, carry, r1, r2, ci);

// Apply stimulus

// Display results

endmodule

Data type declarations

Instantiate module(s)

Why isn`t carry` declared in the data type declarations?

Again, the deIault data type Ior Verilog is a 1-bit wire. A wire oI 1-bit does not need to be declared. Any other

data type, or any other vectored wire must be declared. Notice that we have to declare result because it is wider

than 1-bit.

Also, notice that we again have used an instance name Ior our instantiation oI aaa4bits.

13

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Testbench

initial

begin

r1 0; r2 0; ci 0;

#10 r1 5;

#10 r2 10;

#10 ci 1;

#10 r1 8;

#10 ci 0;

#10 $Iinish;

end

The pound sign (#) character

denotes the delay speciIication Ior

both gate instances and procedural

statements.

The initial block is a (behavioral)

procedural block that executes

only once.

The dollar sign ($) denotes Verilog

system tasks or PLI routines.

$Iinish causes the simulation to

Iinish and exit.

Apply stimulus

The initial block starts executing at simulation time zero and steps through the stimulus based on the timing control

in the procedural block. The simulation will Iinish at 60 time units. We`ll discuss how to give the time units some

meaning (i.e. nanoseconds, picoseconds, etc.) in the next Iew slides.

14

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Procedural Blocks

always (posedge clock)

begin

r1 1;

r2 0;

ci 1;

end

initial

begin

r1 0; r2 0; ci 0;

#10 r1 5;

#10 r2 10;

#10 ci 1;

#10 r1 8;

#10 ci 0;

#10 $Iinish;

end

Executes once Executes at every rising clock edge

initial and always are the ONLY procedural blocks in Verilog.

15

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Testbench (cont.)

module testbench;

// Data type declaration

// Instantiate modules

// Apply stimulus

// Display results

endmodule

module testbench;

. . .

add4bits u1 (result, carry, r1, r2, ci);

initial begin

r1 0; r2 0; ci 0;

#10 r1 5;

#10 r2 10;

#10 ci 1;

#10 r1 8;

#10 ci 0;

#10 $Iinish;

end

endmodule

. . . means that something irrelevant to the example has been leIt out. It is not legal Verilog syntax.

16

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Display Simulation Results to Screen

initial begin

$timeIormat(-9,2, ns, 10);

$monitor(timet r1b r2b cib resultb carryb, $realtime, r1, r2, ci, result, carry);

end

The $timeIormat system task globally speciIies how time values will be

displayed using the t Iormatter. (units>, precision>, suIIix>,

minwidth>)

The $monitor system task displays the values oI the argument list

whenever any oI the arguments change (except $time, $stime, $realtime)

The $realtime system task returns the current simulation time as a real

number.

NC-Verilog and VerilogXL requires the `timescale compiler directive to be used whenever the $timeIormat

command is used. This will be discussed later in the course.

17

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Viewing Simulation Results - VCD

The $dumpIile and $dumpvars

system tasks will work with any

Verilog simulator.

The commands will open a Iile

called dump.vcd and place all

oI the simulation data in that Iile.

The Iile can then be opened by

various waveIorm viewers and

other tools.

initial begin

$dumpIile (dump.vcd);

$dumpvars;

end

18

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Testbench (cont.)

module testbench;

reg |3:0] r1, r2;

reg ci;

wire |3:0] result

add4bits u1 (result, carry, r1, r2, ci);

initial begin

. . .

end

initial begin

$timeIormat(- 9,2, ns, 10);

$monitor(timet r1b r2b cib

resultb carryb, $realtime, r1, r2, ci,

result, carry);

end

endmodule

module testbench;

// Data type declaration

// Instantiate modules

// Apply stimulus

// Display results

endmodule

19

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Simulation results to screen

To Simulate the design we have to include all the Iiles

containing the design modules.

For example, our Iiles are named: testbench.v add4bits.v addbit.v

Simulation results:

Compiling source Iile testbench.v"

Compiling source Iile "add4bits.v"

Compiling source Iile "addbit.v"

Highest level modules:

testbench

0.00 ns r10000 r20000 ci0 result0000 carry0

10.00 ns r10101 r20000 ci0 result0101 carry0

20.00 ns r10101 r21010 ci0 result1111 carry0

30.00 ns r10101 r21010 ci1 result0000 carry1

40.00 ns r11000 r21010 ci1 result0011 carry1

50.00 ns r11000 r21010 ci0 result0010 carry1

L17 testbench.v": $Iinish at simulation time 60.00 ns

The various Verilog simulators require slightly diIIerent commands to compile and simulate the design. The

ModelSim and Cadence soItware demonstrations will show how to load, compile, and simulate your designs.

20

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Simulation results - WaveIorm

Simulators generally provide a way to view

the simulation waveIorms.

The waveIorm simulation results were

stored in the VCD Iile.

Both ModelSim and Cadence have a waveIorm viewer built into the simulation tool.

21

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Review

What are the two methods Ior making

connections to modules during

instantiation?

What is an Instance Name?

What are the three elements to a testbench?

What is the diIIerence between the initial`

and always` procedural blocks?

22

Verilog HDL (EE 499/599 CS 499/599) 2004 AMIS

Homework

Homework assignment #1 is on the class web

page.

Homework assignment #1 is due Wednesday,

January 21, 2004.

Das könnte Ihnen auch gefallen

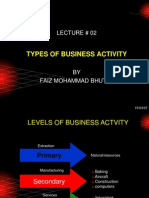

- The Purpose of Business Activity: LECTURE # 01 & 02Dokument9 SeitenThe Purpose of Business Activity: LECTURE # 01 & 02Ali AhmadNoch keine Bewertungen

- Matlab Training - SIMULINKDokument8 SeitenMatlab Training - SIMULINKAtta RehmanNoch keine Bewertungen

- Lecture 2 - 30-01-08Dokument17 SeitenLecture 2 - 30-01-08Ali AhmadNoch keine Bewertungen

- Printing The Model:: SimulinkDokument8 SeitenPrinting The Model:: SimulinkAli AhmadNoch keine Bewertungen

- Lectrue # 12 and 13 - 30-04-08Dokument26 SeitenLectrue # 12 and 13 - 30-04-08Ali AhmadNoch keine Bewertungen

- Matlab Training Session Ii Data Presentation: 2-D PlotsDokument8 SeitenMatlab Training Session Ii Data Presentation: 2-D PlotsAli AhmadNoch keine Bewertungen

- Matlab Training Session Iv Simulating Dynamic Systems: Sampling The Solution EquationDokument9 SeitenMatlab Training Session Iv Simulating Dynamic Systems: Sampling The Solution EquationAli AhmadNoch keine Bewertungen

- Introduction To VHDL: AIR University AU, E-9, IslamabadDokument29 SeitenIntroduction To VHDL: AIR University AU, E-9, IslamabadAli AhmadNoch keine Bewertungen

- Introduction To: Artificial IntelligenceDokument31 SeitenIntroduction To: Artificial IntelligenceAli AhmadNoch keine Bewertungen

- Matlab Training Session Vii Basic Signal Processing: Frequency Domain AnalysisDokument8 SeitenMatlab Training Session Vii Basic Signal Processing: Frequency Domain AnalysisAli AhmadNoch keine Bewertungen

- Matlab Training Session Iii Numerical Methods: Solutions To Systems of Linear EquationsDokument14 SeitenMatlab Training Session Iii Numerical Methods: Solutions To Systems of Linear EquationsAli AhmadNoch keine Bewertungen

- Acknowledgement - 2Dokument11 SeitenAcknowledgement - 2Ali AhmadNoch keine Bewertungen

- Air University Fall 2005 Faculty of Engineering Department of Electronics Engineering Course InformationDokument2 SeitenAir University Fall 2005 Faculty of Engineering Department of Electronics Engineering Course InformationAli AhmadNoch keine Bewertungen

- Introduction To ASIC Design: Lab Report StandardsDokument1 SeiteIntroduction To ASIC Design: Lab Report StandardsAli AhmadNoch keine Bewertungen

- 2-Level Logic ( 0', 1') .: Introduction To ASIC DesignDokument8 Seiten2-Level Logic ( 0', 1') .: Introduction To ASIC DesignAli AhmadNoch keine Bewertungen

- Operators: Introduction To ASIC DesignDokument6 SeitenOperators: Introduction To ASIC DesignAli AhmadNoch keine Bewertungen

- Example 5.1: Multiplexer #1 Using OperatorsDokument10 SeitenExample 5.1: Multiplexer #1 Using OperatorsAli AhmadNoch keine Bewertungen

- Sequential Code in VHDLDokument42 SeitenSequential Code in VHDLAli Ahmad0% (1)

- System On Chips Soc'S & Multiprocessor System On Chips MpsocsDokument42 SeitenSystem On Chips Soc'S & Multiprocessor System On Chips MpsocsAli AhmadNoch keine Bewertungen

- Introduction To ASIC Design: Lab Report InstructionsDokument1 SeiteIntroduction To ASIC Design: Lab Report InstructionsAli AhmadNoch keine Bewertungen

- Introduction To Symbian Os: AIR University AU, PAF Complex, E-9, IslamabadDokument64 SeitenIntroduction To Symbian Os: AIR University AU, PAF Complex, E-9, IslamabadAli AhmadNoch keine Bewertungen

- How Chips Are DesignedDokument46 SeitenHow Chips Are DesignedAli AhmadNoch keine Bewertungen

- State Machine Block DiagarmDokument6 SeitenState Machine Block DiagarmAli AhmadNoch keine Bewertungen

- Assignment#4Dokument1 SeiteAssignment#4Ali AhmadNoch keine Bewertungen

- Digital Filters in VHDL LabDokument5 SeitenDigital Filters in VHDL LabAli AhmadNoch keine Bewertungen

- Second SessionalCourseOutlineDokument1 SeiteSecond SessionalCourseOutlineAli AhmadNoch keine Bewertungen

- Chapter 1: Introduction To AsicsDokument15 SeitenChapter 1: Introduction To AsicsAli AhmadNoch keine Bewertungen

- Assignment # 3: The EndDokument1 SeiteAssignment # 3: The EndAli AhmadNoch keine Bewertungen

- Assignment#5Dokument1 SeiteAssignment#5Ali AhmadNoch keine Bewertungen

- Assignment 1Dokument1 SeiteAssignment 1Ali AhmadNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Kalpesh Tawde Resume Tcs StandardDokument3 SeitenKalpesh Tawde Resume Tcs StandardRohit TawdeNoch keine Bewertungen

- DataGrid Zend Framework - ManualDokument14 SeitenDataGrid Zend Framework - ManualDomingos TeruelNoch keine Bewertungen

- SIM Card StrongDokument243 SeitenSIM Card StrongFaqihNoch keine Bewertungen

- CFD Modeling of A Gas Cyclone D T: Technical University Sofia, BulgariaDokument2 SeitenCFD Modeling of A Gas Cyclone D T: Technical University Sofia, BulgariaBarny GomesNoch keine Bewertungen

- Quiz Questions - 1Dokument4 SeitenQuiz Questions - 1ajay1840Noch keine Bewertungen

- Introdution Multinet PakistanDokument23 SeitenIntrodution Multinet PakistanDemureNoch keine Bewertungen

- Web Questions UnansweredDokument13 SeitenWeb Questions UnanswereddreamsftNoch keine Bewertungen

- List of Direct Broadcast Satellite ProvidersDokument10 SeitenList of Direct Broadcast Satellite ProvidersMehedi HasanNoch keine Bewertungen

- Admit Card 2018-19 Odd-SemDokument2 SeitenAdmit Card 2018-19 Odd-SemPrajjwal ChauhanNoch keine Bewertungen

- Limits of Sequences - Brilliant Math & Science WikiDokument9 SeitenLimits of Sequences - Brilliant Math & Science WikiKunal LadhaniNoch keine Bewertungen

- Configure DHCP in SolarisDokument5 SeitenConfigure DHCP in Solarisapi-3738724Noch keine Bewertungen

- Conjunctive Normal FormDokument8 SeitenConjunctive Normal FormPiyush KochharNoch keine Bewertungen

- Design of Experiments: A 360 Development ApproachDokument24 SeitenDesign of Experiments: A 360 Development ApproachAbhijit More100% (1)

- Parallelized RSA On Multicore CPUs and GPUDokument21 SeitenParallelized RSA On Multicore CPUs and GPUkennedy beyanNoch keine Bewertungen

- SoftDEL IoT Service OfferingsDokument2 SeitenSoftDEL IoT Service OfferingsSoftDELNoch keine Bewertungen

- Knowledge Management CycleDokument49 SeitenKnowledge Management CycleMallik Kruzamidiwinata0% (4)

- Convolution of Probability Distributions PDFDokument3 SeitenConvolution of Probability Distributions PDFJosé María Medina VillaverdeNoch keine Bewertungen

- Manual Kis PDFDokument1.134 SeitenManual Kis PDFApolineoNoch keine Bewertungen

- El Oasis Nicanor Bolet Peraza 1856 PDFDokument125 SeitenEl Oasis Nicanor Bolet Peraza 1856 PDFFelipeMartínez-PinzónNoch keine Bewertungen

- AQTR2014 Technical ProgramDokument22 SeitenAQTR2014 Technical Programktrust2k6Noch keine Bewertungen

- SpssDokument50 SeitenSpssTech_MXNoch keine Bewertungen

- Pre-Requisite Form SSPC Protective Coatings Inspector (PCI) Program & Certification - Level 3Dokument6 SeitenPre-Requisite Form SSPC Protective Coatings Inspector (PCI) Program & Certification - Level 3Prakash RajNoch keine Bewertungen

- DAP-2660 A1 Manual v1.04Dokument91 SeitenDAP-2660 A1 Manual v1.04Martín E. Maldonado MaldonadoNoch keine Bewertungen

- Volte Drive TestDokument10 SeitenVolte Drive TestAli AliNoch keine Bewertungen

- ResumeDokument5 SeitenResumeMohammed AltafNoch keine Bewertungen

- DSIE ProceedingsDokument112 SeitenDSIE ProceedingsAna RebeloNoch keine Bewertungen

- N1mm+morse RunnerDokument20 SeitenN1mm+morse RunnerDennis San PedroNoch keine Bewertungen

- AViCAD UserManual PDFDokument690 SeitenAViCAD UserManual PDFbrutuseczekNoch keine Bewertungen

- Java Package PDFDokument2 SeitenJava Package PDFscribeNoch keine Bewertungen

- Letter To All SP For CCTNS Feedback FormDokument3 SeitenLetter To All SP For CCTNS Feedback FormRajdeep PhukanNoch keine Bewertungen