Beruflich Dokumente

Kultur Dokumente

Real Time FPGA Based Testbed For OFDM Development With ML Synchronization

Hochgeladen von

sreekanthreddy peramOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Real Time FPGA Based Testbed For OFDM Development With ML Synchronization

Hochgeladen von

sreekanthreddy peramCopyright:

Verfügbare Formate

ICSNC 2012 : The Seventh International Conference on Systems and Networks Communications

Real Time FPGA based Testbed for OFDM Development with ML synchronization

Tiago Pereira, Manuel Violas, Atlio Gameiro, Carlos Ribeiro, and Joo Loureno

DETI, Instituto de Telecomunicaes, University of Aveiro Aveiro, Portugal e-mails: targp@av.it.pt, manuelv@ua.pt, amg@ua.pt, cribeiro@av.it.pt, and jlourenco@av.it.pt

Abstract In this paper, we present a real-time testbed Orthogonal Frequency Division Multiplexing (OFDM) signaling scheme. The testbed is implemented in a FieldProgrammable Gate Array (FPGA) through Xilinx System Generator for DSP and includes all the blocks needed for the transmission path of OFDM. Time-domain synchronization is achieved through a joint maximum likelihood (ML) symboltime and carrier frequency offset (CFO) estimator through the redundant information contained in the cyclic prefix (CP). Results show that a rough implementation of the signal path can be implemented by using only Xilinx System Generator for DSP. This work presents a valid FPGA implementation of an OFDM receiver synchronization algorithm using a high-level design tool. Keywords OFDM; FPGA; Software Defined Radio (SDR); physical layer; time-domain synchronization.

simulations were performed and Section VI explains the simulation results. Conclusions are provided in Section VII. II. RELATED WORK

I.

INTRODUCTION

Although multicarrier techniques can be traced back to 1966 [1], the first commercial application of OFDM occurred only in 1995 with the Digital Audio Broadcasting (DAB) standard [2]. OFDM is a multicarrier bandwidth efficiency scheme for digital communications where the main difference to conventional frequency division multiplexing (FDM) is that in the frequency domain the OFDM subcarriers overlap, providing spectrum efficiency. Given that OFDM implementations are carried out in the digital domain, there are a number of platforms able to implement an OFDM system suitable for software defined radio (SDR) development. SDR has been emerging within the wireless industry and can be applied to several applications. It is defined as a radio communication system where some physical (PHY) layer components that are typically implemented in analog hardware (filters, mixers, etc.) are implemented in software instead, thus allowing the user to operate the radio in different environments providing flexibility due to its reconfigurability. The system presented was built using a high-level design tool built into Matlabs Simulink, Xilinx System Generator for DSP, providing the user with high-level abstractions of the system that can be automatically compiled into an FPGA [10]. Work presented here is divided as follows: Section II presents the literature review, the receiver critical parts and the papers aim; Section III presents a brief description of the transceiver architecture and the received signals ambiguities; Section IV is divided in three parts and presents the algorithm implemented for time-domain estimation and compensation; Section V presents the testbed used and how

Several testbeds for OFDM systems based on SDR have been reported on literature. For example, [3] presents an OFDM modulator/demodulator with two synchronization options and two error-controlling techniques. The work in [4] uses GNU radio to transfer OFDM signals with QPSK and BPSK modulation to analyze the packet-received ratio for Quality of Service purposes. Other broadly adopted research platform is WARP [5]. The work in [6] uses this testbed to present an OFDM-based cooperative system using Alamoutis block code to study its capability versus a 2 x 1 multiple input single output system. FPGA implementations of standards 802.11a and 802.16-2004 modulators using Xilinx System Generator for DSP for high level design can be found in [7][8]. Two critical parts of the receiver are the synchronization and channel estimation subsystems. The synchronization should estimate the frame arrival time and a frequency offset between the local oscillators and RF carriers. Compensation can then be applied to the incoming signal. Unlike IEEE 802.11a/g and 802.16 (WiMax), among others, this system does not use a training sequence to achieve time-domain synchronization. The aim of this paper is to present the implementation of an FPGA-based OFDM receiver with a ML time-domain synchronization algorithm using Xilinx System Generator for DSP. III. THE ORTHOGONAL FREQUENCY DIVISION

MULTIPLEXING TRANSCEIVER

Figure 1 depicts the transceiver architecture of the system discussed in this paper. On the transmitter, data is generated randomly by making an inverse fast Fourier transform (IFFT) of quadrature amplitude modulated (QAM) symbol sets with 1024 subcarriers. The CP is added after the IFFT and the symbols are turned into frames. An up-conversion of 4 is performed on the interpolation block by a set of two interpolation filters: a square-root-raised-cosine and a halfband. The mixer block performs frequency translation to an intermediate frequency (IF) and is achieved by mixing the frame with a direct digital synthesizer (DDS). On the receiver side another DDS translates the IF back to baseband on the mixer block. Down-conversion and matched filtering is performed by a similar set of filters as the ones used on the

Copyright (c) IARIA, 2012.

ISBN: 978-1-61208-231-8

197

ICSNC 2012 : The Seventh International Conference on Systems and Networks Communications

transmitter by the decimator block. Once the estimations for the offsets are performed, the data forwarding control (DFC) and CFO correction blocks perform the compensations. A fast Fourier Transform (FFT) retrieves the data. Several parameters along the system are reconfigurable at users need. Such parameters include number of symbols per frame, CP length, carrier frequency (limited by the systems frequency), modulation (QPSK, 16-QAM, 64-QAM, etc.) and the systems main clock frequency. Preventing intersymbol interference (ISI) and preserving subcarrier orthogonality is achieved by adding a preamble of L samples to each symbol that contains the information of the last N samples of each OFDM symbol. Such symbol structure (N+L samples) maintains subcarrier orthogonality, in spite of the loss in transmission power and throughput.

A. Estimation of symbol arrival time and carrier frequency offset The subsystem presented on this subsection is based on the algorithms developed by Beek [11]. The subsystem created for its purpose and adapted to the symbol pattern on Figure 2 is illustrated in Figure 3. Beek exploits the CP by correlating it with a delayed version of itself. When the repeated pattern is located, a peak is generated in order to detect the frame arrival and the phase between patterns gives the CFO. The algorithm consists of two main branches. The top one calculates an energy term. While the bottom one calculates the correlation term required for estimating both

Figure 1. Baseband and IF transceiver arquitecture

Figure 3. Estimation algorithm architecture

symbol arrival time and phase offset. Equation (2) shows the calculation of the energy term and Equation (3) shows the calculation of the correlation term.

Figure 2. OFDM Frame Format

ms1

As receiver and transmitter are physically separated, the receiver to be able to perform an efficient demodulation has to perform frame and carrier synchronization. The first operation defines the starting / ending points of the frame while the latter synchronizes the phase / frequency between transmitter and receiver. Erroneous frame detection is projected into the symbol constellation with a circular rotation, whereas the carrier frequency offset (CFO) causes all the subcarriers to shift and is projected as dispersion in the constellation points. Both ambiguities yield the received signal:

m+L1 2 2 r (k ) + r (k + N ) 2 k =m

m+ L 1

(2) (3)

ms 2

r(k )r (k + N )

* k =m

r (k ) = s(k )e j 2 k / N

(1)

where is the normalized CFO, is the unknown arrival time of a frame, s(k) is the transmitted signal, N is the number of samples per symbol and k is the sample index of each symbol ranging [0,1023]. IV. SYSTEM GENERATOR FLOW ON SYNCHRONIZATION The following subsections present the synchronization algorithm divided in three parts.

The factor is the magnitude of the correlation coefficient between r(k) and r(k+N); it depends on the signal-to-noise ratio but can be set to 1. Both moving sums were designed using infinite impulse response (IIR) filters. The complex multiplier core present on the System Generator libraries performs multiplications throughout the subsystem. In order to proceed with both estimations, two operations must be performed on the bottom branch, a complex module to create the peak when the CP correlates with its delayed version and an arctangent to calculate the angle between both IQ signals to enable CFO estimation. System Generator provides a CORDIC arctangent reference block that implements a rectangular-to-polar coordinate conversion using a CORDIC algorithm in circular vectoring mode, that given a complex-input <I,Q>, it computes a magnitude and an angle according to (4) and (5), respectively.

I, Q = I 2 + Q 2

(4) (5)

ang = 2 = arctan(Q / I )

Copyright (c) IARIA, 2012.

ISBN: 978-1-61208-231-8

198

ICSNC 2012 : The Seventh International Conference on Systems and Networks Communications

It is assumed that the offset between oscillators is lower than a single subcarrier and so || < 1/2. Reference [13] performs a division to create the necessary peak for frame arrival detection, but such operation in hardware is more expensive and should be avoided. The only difference brought by the difference operation is how the peak is generated, since the argument to be detected will be close to 0 with a subtraction and to 1 with a division. Achieving a theoretical value of 0 when a signal is detected is not a realistic approach since the fixed-point logic used is subject to quantization errors and to contention of bit propagation along the system. The computed angle is only used when the peak is detected, ensuring the CFO is only used if the correlation is complete.

TABLE I. SYSTEM PARAMETERS

Figure 5. OFDM symbol with a 6 kHz offset between oscillators. Before compensation (left) and after compensation (right).

System Parameters Baseband frequency || Bandwidth FFT size || CP size Modulation Subcarrier separation Symbol duration (Symbol+CP) IF sampling frequency Oscillator frequency

15.36 MHz || 10 MHz 1024 || 256 QPSK 15 kHz 66.66 + 16.66 = 83.32 s 61.44 MHz 7.68 MHz

B. Data forwarding control This subsystem uses the frame detection peak to process the frame in order for each symbol to be processed by the FFT. Unlike a non-deterministic simulation such as the ones ran in Simulink, a FPGA simulation doesnt have the ability to hold the information on its own while the estimations described on the previous subsection are executed. Data must be contained in a memory and forwarded when a condition is met or delayed by a constant value if the process is continuous, which is the case. The processing time required for a peak to be detected and the accurate CFO to be estimated is known, constant and introduced as a delay before the FIFOs. The peak detected on subsection A triggers the frame writing into the FIFOs. The CP is not needed anymore so its not stored. The FFT will require 3*N samples to process each symbol and send it back outside. These amount of samples needs to created given that the symbols stored on the FIFOs are continuous. Reading the data stored on the FIFOs at a sampling rate four times higher as the symbols arrive creates that gap, breaking the frame back into separate symbols. C. Carrier frequency offset correction Correction of the CFO is achieved with a CORDIC implementing a rotate function [12]. The core rotates the vector (I,Q) by an angle yielding a new vector (I,Q) such that I '(k ) = I (k ) cos Q(k ) sin (6) Q '(k ) = Q(k ) cos + I (k ) sin where (7) = 2 k N and k is the sample index of each symbol. Taking the angle achieved at subsection A, the angle is first divided by N and then accumulated along each symbol nullifying the phase offset along each symbol. V. TESTBED AND SIMULATIONS Even though there is not a targeted standard at this point, such implementation can be adapted to several OFDM standards such as 802.11a, WiMAX, 3GPP LTE, among others, given the reconfigurability of the parameters. Xilinx

Figure 4. Estimation algorithm results for a frame with 3 OFDM symbols: (a) signal, (b) peak detection and (c) computed angle.

Copyright (c) IARIA, 2012.

ISBN: 978-1-61208-231-8

199

ICSNC 2012 : The Seventh International Conference on Systems and Networks Communications

System Generator for DSP does not allow the user to replace hardware description language (HDL) completely but allows him to focus the attention on the critical parts of the design, i.e., when it comes to managing internal clocks and optimizing paths, HDL is better suited. The design was compiled through hardware co-simulation, a compilation method that allows the user to avoid HDL completely if no front-end is needed. The targeted model for the simulation was the Xilinx ML605 development board, which contains a Virtex-6 LX240T FPGA and a 4DSP FMC150 FMC daughter card with a dual 14-bit 250 MSPS ADC and a dual 16-bit 800 MSPS DAC. The tests were performed in a wired-channel and the system was run at a system clock of 61.44 MHz with an IF of 7.68 MHz. The results were obtained using the Xilinx ChipScope Pro tool. Because of the analog front-end present on the testbed, a wrapper must be created with Xilinx ISE Design Suite in order to connect both the system presented here and the daughter card where the DACs/ADCs are present. Table 2 shows the resources used for the full transceiver, without the wrapper. VI. SIMULATION RESULTS In Figure 4, a rough estimation of the frame is presented, with a peak being generated at the beginning of each symbol and the respective CFO on the bottom, thus proving an accurate arrival time and CFO estimation of each symbol. It is also possible to perform a frame-based estimation instead of a symbol-based one, but no additional complexity is brought by this change. Figure 5 proves that OFDM is sensitive to frequency offsets and even though the CORDIC corrects the phase along the symbol, it lacks the ability to compensate for the initial phase present on the oscillator. VII. CONCLUSION AND FUTURE WORK A full baseband + IF design was presented focused on the synchronization algorithm. The work presented was performed using Xilinx System Generator for DSP, ChipScope Pro, ISE Design Suite and validated with Matlab. It is possible to do FPGA simulations with a double floating-point precision, but not all blocks present on the System Generator libraries allow such precision and operations on floating point have a higher resource usage in hardware. Also, the front-end only allows a fixed point precision.

TABLE II. RESOURCE USAGE OF THE FULL SYSTEM

The next step is to direct the work presented here towards a 3GPP LTE MIMO-PHY receiver layer implementation with channel equalization and channel encoding algorithms. ACKNOWLEDGMENT The Portuguese projects CROWN, PTDC/EEATEL/115828/2009, and CelCop as well as the Mobile Network Research Group (MOBNET) from the Instituto de Telecomunicaes in Aveiro supported the work presented on this paper. REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[9] [10]

[11]

Full system resource usage for Virtex-6

Parameter Used %

[12] 17 8 14 3 18 [14]

Slices Slice registers Slice LUTs Block RAMs DSP48E

6662 24847 22059 38 141

[13]

R. W. Chang, Synthesis of band-limited orthogonal signals for multi-channel data transmission, Bell System Technical Journal 45, 1966, pp. 1775-1796. ETS 300 401, Radio broadcasting systems; Digital Audio Broadcasting (DAB) to mobile, portable and fixed receivers, ETSI, Feb. 1995. M. Maj, Design and implementation of an OFDM-based communication system for the GNU radio platform, Master Thesis, Dec. 2009. A. Marwanto, M. A. Sarijari, N. Fisal, S. K. S. Yusof and R. A. Rashid, Experimental study of OFDM implementation utilizing GNU Radio and USRP SDR, Proc. of the IEEE 9th Malaysia International Conference on Communicatons, Dec. 2009, pp. 132-135. P. Murphy, A. Sabharwal, and B. Aazhang, Design of WARP: a wireless open-access research platform, Proc. of the European Signal Processing Conference, Sept. 2006, Article No. 7. P. Murphy, A. Sabharwal, and B. Aazhang, On building a cooperative communication system: testbed implementation and first results, EURASIP Journal on Wireless Communications and Networking, June 2009, doi:10.1155/2009/972739. J. Garcia and R. Cumplido, On the design of an FPGA-based OFDM modulator for IEEE 802.11a, 2nd International Conference on Electrical and Electronics Engineering, Sept. 2005, pp. 114-117. E J. Garcia and R. Cumplido, On the design of an FPGAbased OFDM modulator for IEEE 802.16-2004, 2005 International Conference on Reconfigurable Computing and FPGAs, 2005, pp. 22-25. A. Goldsmith, Wireless Communications, Cambridge University Press, 2005. Xilinx Inc., System Generator for DSP user guide, http://www.xilinx.com/support/documentation/sw_manuals/xi linx13_3/sysgen_gs.pdf, Release 13.3, Oct. 2011 [retrieved: Nov., 2012]. J. van de Beek, M. Sandell, and P. O. Brjesson, ML estimation of time and frequency offset in OFDM systems, IEEE Transactions on Signal Processing, vol. 45, no. 7, July 1997 Xilinx Inc., DS249 LogiCORE IP CORDIC v4.0, http://www.xilinx.com/support/documentation/ip_documentat ion/cordic_ds249.pdf, March 2011 [retrieved: Nov., 2012]. O. Font-Bach, N. Bartzoudis, A. Pascual-Iserte, and D. L. Bueno, A real-time MIMO-OFDM mobile WiMAX receiver: Architecture, design and FPGA implementation, Computer Networks, 55 (16), pp. 3634-3647, 2011. Xilinx Inc., System Generator for DSP reference guide, http://www.xilinx.com/support/documentation/sw_manuals/xi linx13_3/sysgen_ref.pdf, Release 13.3, Oct. 2011 [retrieved: Nov.,2012

Copyright (c) IARIA, 2012.

ISBN: 978-1-61208-231-8

200

Das könnte Ihnen auch gefallen

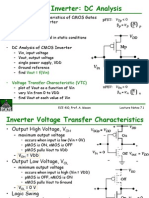

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Dokument34 SeitenDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaNoch keine Bewertungen

- Digital Logic CircuitsDokument20 SeitenDigital Logic Circuitssreekanthreddy peramNoch keine Bewertungen

- Dynamic Logic Circuits: A. MarzukiDokument25 SeitenDynamic Logic Circuits: A. Marzukisreekanthreddy peramNoch keine Bewertungen

- Dynamic Logic CircuitsDokument38 SeitenDynamic Logic Circuitssreekanthreddy peramNoch keine Bewertungen

- Electronics Ch14Dokument22 SeitenElectronics Ch14Denise NelsonNoch keine Bewertungen

- CMOS InverterDokument16 SeitenCMOS Invertersreekanthreddy peramNoch keine Bewertungen

- Dynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)Dokument29 SeitenDynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)vardhanNoch keine Bewertungen

- Behaviour of OFDM System Using MATLAB SimulationDokument5 SeitenBehaviour of OFDM System Using MATLAB Simulationsreekanthreddy peramNoch keine Bewertungen

- CMOS Inverter: DC AnalysisDokument32 SeitenCMOS Inverter: DC Analysissreekanthreddy peram50% (2)

- Cmos InverterDokument92 SeitenCmos Invertersreekanthreddy peramNoch keine Bewertungen

- Std11 Bot EM 1Dokument236 SeitenStd11 Bot EM 1Irshad Ali100% (1)

- Grazers and Browsers: How Digestive Morphology Affects Diet Selection Lisa A. ShipleyDokument8 SeitenGrazers and Browsers: How Digestive Morphology Affects Diet Selection Lisa A. Shipleysreekanthreddy peramNoch keine Bewertungen

- Morphology of The Pteridophytes SporneDokument200 SeitenMorphology of The Pteridophytes Spornesreekanthreddy peram100% (1)

- 9 YeungDokument19 Seiten9 YeungNathan PittmanNoch keine Bewertungen

- Physical Quantities Handout.........Dokument5 SeitenPhysical Quantities Handout.........sreekanthreddy peramNoch keine Bewertungen

- Dimensional Analysis A A SoninDokument57 SeitenDimensional Analysis A A SoninJeff WebbNoch keine Bewertungen

- All About Fundamental Physical QuantitiesDokument18 SeitenAll About Fundamental Physical Quantitiessreekanthreddy peramNoch keine Bewertungen

- OFDM SIMULATION in MATLAB PDFDokument59 SeitenOFDM SIMULATION in MATLAB PDFaasmabaka100% (2)

- A Survey On Digital Modulation Techniques For Software Defined Radio ApplicationsDokument8 SeitenA Survey On Digital Modulation Techniques For Software Defined Radio Applicationssreekanthreddy peramNoch keine Bewertungen

- FPGA Implementation of MIMO System Using Xilinx System Generator For Efficient Hardware/ Software Co-DesignDokument9 SeitenFPGA Implementation of MIMO System Using Xilinx System Generator For Efficient Hardware/ Software Co-Designsreekanthreddy peramNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Quad CopterDokument42 SeitenQuad CopterShanaka JayasekaraNoch keine Bewertungen

- TM SAM MF-HF 5000 Series 150&250W 98 124351Dokument60 SeitenTM SAM MF-HF 5000 Series 150&250W 98 124351citaccitacNoch keine Bewertungen

- 4g 5g 6g 7g and Future Mobile Technologies 4Dokument8 Seiten4g 5g 6g 7g and Future Mobile Technologies 4Erena KenoNoch keine Bewertungen

- Ic f1100d Non VsDokument4 SeitenIc f1100d Non VsLeandro CarvalhoNoch keine Bewertungen

- KPP 015 ManualDokument17 SeitenKPP 015 ManualPedro Ramirez RomeroNoch keine Bewertungen

- BSA Antenna TheoryDokument92 SeitenBSA Antenna TheorySandeep ShendeNoch keine Bewertungen

- Telstra Gateway Pro V7610 User GuideDokument51 SeitenTelstra Gateway Pro V7610 User GuideTom StuartNoch keine Bewertungen

- Antenna Design and Correction AlgorithmDokument24 SeitenAntenna Design and Correction AlgorithmMusa KallonNoch keine Bewertungen

- HACH FL900 Flow Logger Product Sheet PDFDokument4 SeitenHACH FL900 Flow Logger Product Sheet PDFHeyward FlowNoch keine Bewertungen

- Surfsat-L: Secured High Data Rate Communications at SeaDokument2 SeitenSurfsat-L: Secured High Data Rate Communications at Seaasokanen50% (2)

- MCQ in Est by S Cuervo of ExcelDokument10 SeitenMCQ in Est by S Cuervo of ExcelCatherine TaubNoch keine Bewertungen

- How To Flash A PhoneDokument6 SeitenHow To Flash A PhonePaul KarijaNoch keine Bewertungen

- User's Manual: Wouxun KG-UV6D Wouxun KG-UV6X VHF/UHF Handheld FM TransceiverDokument18 SeitenUser's Manual: Wouxun KG-UV6D Wouxun KG-UV6X VHF/UHF Handheld FM TransceivercatalassNoch keine Bewertungen

- List of Mobile Network OperatorsDokument14 SeitenList of Mobile Network OperatorsAbdulkader HusseinNoch keine Bewertungen

- HF Transmitter Jrs 900 JRCDokument2 SeitenHF Transmitter Jrs 900 JRCtruongvietthien19Noch keine Bewertungen

- EX7100 Training Course - Master Version 1 - 0Dokument209 SeitenEX7100 Training Course - Master Version 1 - 0PeterLOW0218Noch keine Bewertungen

- Gate Questions Bank EC CommunicationDokument10 SeitenGate Questions Bank EC CommunicationfreefreeNoch keine Bewertungen

- Wireless Lesson PlanDokument1 SeiteWireless Lesson PlanNadeem PashaNoch keine Bewertungen

- EBOSDokument5 SeitenEBOSKaptahNoch keine Bewertungen

- Combine 2g and 3g AntennaDokument4 SeitenCombine 2g and 3g AntennaTuấn Tú Lê0% (1)

- SWEDISH DA90K Drive-AwayDokument2 SeitenSWEDISH DA90K Drive-AwayAndreaNoch keine Bewertungen

- Worksheet 2.1Dokument2 SeitenWorksheet 2.1gnons1867Noch keine Bewertungen

- BSC MS BTS MSC VLR: SDCCH BlockDokument5 SeitenBSC MS BTS MSC VLR: SDCCH BlockElesta RowNoch keine Bewertungen

- MessageDokument5 SeitenMessageNew UserNoch keine Bewertungen

- Comar CSA300 TransponderDokument2 SeitenComar CSA300 Transponderarlindojl100% (1)

- Microwave ExperimentDokument37 SeitenMicrowave Experimentsufiyan aliNoch keine Bewertungen

- EL 2611CB3+ DeluxeDokument1 SeiteEL 2611CB3+ DeluxeAsep AcengNoch keine Bewertungen

- Arabia Tech - Product PricingDokument40 SeitenArabia Tech - Product PricingLechelaNoch keine Bewertungen

- Galaxy Owners Manual dx93tDokument10 SeitenGalaxy Owners Manual dx93tbellscbNoch keine Bewertungen