Beruflich Dokumente

Kultur Dokumente

The Inverter

Hochgeladen von

sreekanthreddy peramCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

The Inverter

Hochgeladen von

sreekanthreddy peramCopyright:

Verfügbare Formate

KTH/ESDlab/HT

The Inverter

Prof. Hannu Tenhunen Royal Institute of Technology Department of Electronics Electronic System Design Laboratory Email: hannu@ele.kth.se

KTH/ESDlab/HT

10/4/00

Outline

u u u

Noise margins in logic Delay definitions CMOS inverter characteristics

VTC delay

Power dissipation

KTH/ESDlab/HT

10/4/00

10/4/00

1

1

KTH/ESDlab/HT

Noise margins

KTH/ESDlab/HT

10/4/00

Noise sources in digital logic

KTH/ESDlab/HT

10/4/00

10/4/00

2

2

KTH/ESDlab/HT

DC characteristics: Voltage transfer curve

KTH/ESDlab/HT

10/4/00

From analog signals to digital values

KTH/ESDlab/HT

10/4/00

10/4/00

3

3

KTH/ESDlab/HT

Noise margins

KTH/ESDlab/HT

10/4/00

Regenerative property of digital logic

KTH/ESDlab/HT

10/4/00

10/4/00

4

4

KTH/ESDlab/HT

Simulated inverter chain response

KTH/ESDlab/HT

10/4/00

Delay definitions

KTH/ESDlab/HT

10/4/00

10

10/4/00

5

5

KTH/ESDlab/HT

Ring oscillator

KTH/ESDlab/HT

10/4/00

11

CMOS Inverter Static Behavior

KTH/ESDlab/HT

10/4/00

12

10/4/00

6

6

KTH/ESDlab/HT

NMOS transistor characteristics

KTH/ESDlab/HT

10/4/00

13

PMOS transistor characteristics

KTH/ESDlab/HT

10/4/00

14

10/4/00

7

7

KTH/ESDlab/HT

Basic CMOS inverter

KTH/ESDlab/HT

10/4/00

15

CMOS inverter layout

KTH/ESDlab/HT

10/4/00

16

10/4/00

8

8

KTH/ESDlab/HT

Switch model of MOS transistor

KTH/ESDlab/HT

10/4/00

17

Pull-up/pull-down via NMOS

KTH/ESDlab/HT

10/4/00

18

10/4/00

9

9

KTH/ESDlab/HT

CMOS inverter: steady state response

KTH/ESDlab/HT

10/4/00

19

CMOS inverter: steady state responses

KTH/ESDlab/HT

10/4/00

20

10/4/00

10

10

KTH/ESDlab/HT

PMOS load lines

KTH/ESDlab/HT

10/4/00

21

CMOS inverter load characteristics

KTH/ESDlab/HT

10/4/00

22

10/4/00

11

11

KTH/ESDlab/HT

CMOS inverter VTC

KTH/ESDlab/HT

10/4/00

23

Simulated VTC

KTH/ESDlab/HT

10/4/00

24

10/4/00

12

12

KTH/ESDlab/HT

NMOS and PMOS transistor I-V curves in inverter

KTH/ESDlab/HT

10/4/00

25

CMOS inverter VTC

KTH/ESDlab/HT

10/4/00

26

10/4/00

13

13

KTH/ESDlab/HT

CMOS static characteristics

KTH/ESDlab/HT

10/4/00

27

CMOS inverter VTC vs. transistor sizing

KTH/ESDlab/HT

10/4/00

28

10/4/00

14

14

KTH/ESDlab/HT

Gate switching threshold

KTH/ESDlab/HT

10/4/00

29

Example: VTC of CMOS inverter

KTH/ESDlab/HT

10/4/00

30

10/4/00

15

15

KTH/ESDlab/HT

Inverter Dynamic Behavour

KTH/ESDlab/HT

10/4/00

31

CMOS dynamic behavior

KTH/ESDlab/HT

10/4/00

32

10/4/00

16

16

KTH/ESDlab/HT

CMOS inverter: transient response

KTH/ESDlab/HT

10/4/00

33

CMOS inverter: propagation delay

KTH/ESDlab/HT

10/4/00

34

10/4/00

17

17

KTH/ESDlab/HT

CMOS dynamic behavior: capacitance

KTH/ESDlab/HT

10/4/00

35

CMOS inverter input & output capacitances

KTH/ESDlab/HT

10/4/00

36

10/4/00

18

18

KTH/ESDlab/HT

Gate-drain and drain-bulk capacitance

KTH/ESDlab/HT

10/4/00

37

Wiring and load capacitance

KTH/ESDlab/HT

10/4/00

38

10/4/00

19

19

KTH/ESDlab/HT

Inverter capacitance calculations (ala backannotated Spice)

KTH/ESDlab/HT

10/4/00

39

Logic delay model

KTH/ESDlab/HT

10/4/00

40

10/4/00

20

20

KTH/ESDlab/HT

CMOS inverter dynamic characteristics: high-to-low

KTH/ESDlab/HT

10/4/00

41

CMOS inverter dynamic characteristics:low-to-high

KTH/ESDlab/HT

10/4/00

42

10/4/00

21

21

KTH/ESDlab/HT

Simplified delay model (RC)

KTH/ESDlab/HT

10/4/00

43

Impact of rise time to delay

KTH/ESDlab/HT

10/4/00

44

10/4/00

22

22

KTH/ESDlab/HT

Velocity saturation

KTH/ESDlab/HT

10/4/00

45

Delay vs. operating voltage Vdd

KTH/ESDlab/HT

10/4/00

46

10/4/00

23

23

KTH/ESDlab/HT

Discharging via multiple NMOS transistors

KTH/ESDlab/HT

10/4/00

47

CMOS inverter delay summary

KTH/ESDlab/HT

10/4/00

48

10/4/00

24

24

KTH/ESDlab/HT

Power dissipation

KTH/ESDlab/HT

10/4/00

49

Power dissipation

KTH/ESDlab/HT

10/4/00

50

10/4/00

25

25

KTH/ESDlab/HT

CMOS power dissipation

KTH/ESDlab/HT

10/4/00

51

Power due to direct path currents

KTH/ESDlab/HT

10/4/00

52

10/4/00

26

26

KTH/ESDlab/HT

Dynamic power consumption

KTH/ESDlab/HT

10/4/00

53

Static vs. dynamic current dissipation in CMOS inverter

KTH/ESDlab/HT

10/4/00

54

10/4/00

27

27

KTH/ESDlab/HT

Power dissipation vs. capacitive load

KTH/ESDlab/HT

10/4/00

55

10/4/00

28

28

Das könnte Ihnen auch gefallen

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Dokument34 SeitenDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaNoch keine Bewertungen

- Dynamic Logic CircuitsDokument38 SeitenDynamic Logic Circuitssreekanthreddy peramNoch keine Bewertungen

- Dynamic Logic Circuits: A. MarzukiDokument25 SeitenDynamic Logic Circuits: A. Marzukisreekanthreddy peramNoch keine Bewertungen

- CMOS InverterDokument16 SeitenCMOS Invertersreekanthreddy peramNoch keine Bewertungen

- Dynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)Dokument29 SeitenDynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)vardhanNoch keine Bewertungen

- Digital Logic CircuitsDokument20 SeitenDigital Logic Circuitssreekanthreddy peramNoch keine Bewertungen

- Electronics Ch14Dokument22 SeitenElectronics Ch14Denise NelsonNoch keine Bewertungen

- Morphology of The Pteridophytes SporneDokument200 SeitenMorphology of The Pteridophytes Spornesreekanthreddy peram100% (1)

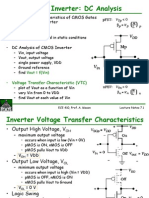

- CMOS Inverter: DC AnalysisDokument32 SeitenCMOS Inverter: DC Analysissreekanthreddy peram50% (2)

- Grazers and Browsers: How Digestive Morphology Affects Diet Selection Lisa A. ShipleyDokument8 SeitenGrazers and Browsers: How Digestive Morphology Affects Diet Selection Lisa A. Shipleysreekanthreddy peramNoch keine Bewertungen

- Std11 Bot EM 1Dokument236 SeitenStd11 Bot EM 1Irshad Ali100% (1)

- Cmos InverterDokument92 SeitenCmos Invertersreekanthreddy peramNoch keine Bewertungen

- 9 YeungDokument19 Seiten9 YeungNathan PittmanNoch keine Bewertungen

- Behaviour of OFDM System Using MATLAB SimulationDokument5 SeitenBehaviour of OFDM System Using MATLAB Simulationsreekanthreddy peramNoch keine Bewertungen

- All About Fundamental Physical QuantitiesDokument18 SeitenAll About Fundamental Physical Quantitiessreekanthreddy peramNoch keine Bewertungen

- Dimensional Analysis A A SoninDokument57 SeitenDimensional Analysis A A SoninJeff WebbNoch keine Bewertungen

- OFDM SIMULATION in MATLAB PDFDokument59 SeitenOFDM SIMULATION in MATLAB PDFaasmabaka100% (2)

- Physical Quantities Handout.........Dokument5 SeitenPhysical Quantities Handout.........sreekanthreddy peramNoch keine Bewertungen

- A Survey On Digital Modulation Techniques For Software Defined Radio ApplicationsDokument8 SeitenA Survey On Digital Modulation Techniques For Software Defined Radio Applicationssreekanthreddy peramNoch keine Bewertungen

- FPGA Implementation of MIMO System Using Xilinx System Generator For Efficient Hardware/ Software Co-DesignDokument9 SeitenFPGA Implementation of MIMO System Using Xilinx System Generator For Efficient Hardware/ Software Co-Designsreekanthreddy peramNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- List of Approved Journals For Promoting Purposes at The University of JordanDokument3 SeitenList of Approved Journals For Promoting Purposes at The University of JordanZaid MarwanNoch keine Bewertungen

- Review of Financial Statements and Its Analysis: Rheena B. Delos Santos BSBA-1A (FM2)Dokument12 SeitenReview of Financial Statements and Its Analysis: Rheena B. Delos Santos BSBA-1A (FM2)RHIAN B.Noch keine Bewertungen

- Variable Length Subnet MasksDokument4 SeitenVariable Length Subnet MaskszelalemNoch keine Bewertungen

- FMDQ Codified Rule Book FGN BondsDokument65 SeitenFMDQ Codified Rule Book FGN BondsOladipupo Mayowa PaulNoch keine Bewertungen

- 4 A Industrial RevolutionDokument41 Seiten4 A Industrial Revolutionabekhti2008Noch keine Bewertungen

- 3d Mug Tutorial in 3d MaxDokument5 Seiten3d Mug Tutorial in 3d MaxCalvin TejaNoch keine Bewertungen

- Hyster Forklift Class 5 Internal Combustion Engine Trucks g019 h13xm h12xm 12ec Service ManualsDokument23 SeitenHyster Forklift Class 5 Internal Combustion Engine Trucks g019 h13xm h12xm 12ec Service Manualsedwinodom070882sad100% (72)

- AutoCAD Civil 3D Performance Optimization 2Dokument5 SeitenAutoCAD Civil 3D Performance Optimization 2Renukadevi RptNoch keine Bewertungen

- Shareholder Agreement 06Dokument19 SeitenShareholder Agreement 06Josmar TelloNoch keine Bewertungen

- Pac All CAF Subject Referral Tests 1Dokument46 SeitenPac All CAF Subject Referral Tests 1Shahid MahmudNoch keine Bewertungen

- HK Magazine 03082013Dokument56 SeitenHK Magazine 03082013apparition9Noch keine Bewertungen

- JQuery Interview Questions and AnswersDokument5 SeitenJQuery Interview Questions and AnswersShailesh M SassNoch keine Bewertungen

- Zambia MTEF 2015 - 2017 (Green Paper)Dokument27 SeitenZambia MTEF 2015 - 2017 (Green Paper)Chola MukangaNoch keine Bewertungen

- Philippine Multimodal Transportation and Logistics Industry Roadmap - Key Recommendations - 2016.04.14Dokument89 SeitenPhilippine Multimodal Transportation and Logistics Industry Roadmap - Key Recommendations - 2016.04.14PortCalls50% (4)

- Scrum Gantt Chart With BurndownDokument4 SeitenScrum Gantt Chart With BurndownAsma Afreen ChowdaryNoch keine Bewertungen

- Timken Bearing Damage PosterDokument1 SeiteTimken Bearing Damage Postera04205100% (5)

- 20151201-Baltic Sea Regional SecurityDokument38 Seiten20151201-Baltic Sea Regional SecurityKebede MichaelNoch keine Bewertungen

- Tech Bee JavaDokument57 SeitenTech Bee JavaA KarthikNoch keine Bewertungen

- Fabric Technologist RoleDokument3 SeitenFabric Technologist RoleAnup Kumar DeyNoch keine Bewertungen

- DPWH Cost EstimationDokument67 SeitenDPWH Cost EstimationAj Abe92% (12)

- D.E.I Technical College, Dayalbagh Agra 5 III Semester Electrical Engg. Electrical Circuits and Measurements Question Bank Unit 1Dokument5 SeitenD.E.I Technical College, Dayalbagh Agra 5 III Semester Electrical Engg. Electrical Circuits and Measurements Question Bank Unit 1Pritam Kumar Singh100% (1)

- REID CatalogDokument54 SeitenREID Catalogzhaoye maoNoch keine Bewertungen

- An Overview of The Geostatistical Analyst Toolbar and ToolboxDokument1 SeiteAn Overview of The Geostatistical Analyst Toolbar and ToolboxSumit SumanNoch keine Bewertungen

- Procurement Systems and Tools RoundTable Notes (Europe) 13 Oct 2020 - 0Dokument8 SeitenProcurement Systems and Tools RoundTable Notes (Europe) 13 Oct 2020 - 0SathishkumarNoch keine Bewertungen

- Jicable DAS For Power Industry Applications 2015-A3-4Dokument6 SeitenJicable DAS For Power Industry Applications 2015-A3-4Richard KluthNoch keine Bewertungen

- FM - 30 MCQDokument8 SeitenFM - 30 MCQsiva sankarNoch keine Bewertungen

- Class B Digital Device Part 15 of The FCC RulesDokument7 SeitenClass B Digital Device Part 15 of The FCC RulesHemantkumarNoch keine Bewertungen

- Baterías YuasaDokument122 SeitenBaterías YuasaLuisNoch keine Bewertungen

- Form DVAT 27A: Intimation of Deposit of Government DuesDokument2 SeitenForm DVAT 27A: Intimation of Deposit of Government DueshhhhhhhuuuuuyyuyyyyyNoch keine Bewertungen

- LEBV4830Dokument371 SeitenLEBV4830anton100% (1)