Beruflich Dokumente

Kultur Dokumente

Ce G 3150 Lab 4 Traffic Light

Hochgeladen von

Ali AhmadOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ce G 3150 Lab 4 Traffic Light

Hochgeladen von

Ali AhmadCopyright:

Verfügbare Formate

CEG 3150: Digital Systems II (Fall 2004) Prof.

Rami Abielmona Laboratory #3: Sequential Machine Design I Trac Light Controller

October 17, 2004

Contents

1 Objective 2 Pre-Lab 3 Introduction to Synchronous Sequential 3.1 Problem Specication . . . . . . . . . . 3.2 State Diagram . . . . . . . . . . . . . . 3.3 State Table . . . . . . . . . . . . . . . . 3.4 State Minimization . . . . . . . . . . . . 3.5 State Assignment . . . . . . . . . . . . . 3.6 Transition Table . . . . . . . . . . . . . 3.7 Design Equations . . . . . . . . . . . . . 3.8 Circuit Implementation . . . . . . . . . 3.8.1 Moore vs. Mealy . . . . . . . . . 3.8.2 Moore VHDL Model . . . . . . . 3.8.3 Mealy VHDL Model . . . . . . . 3.8.4 Final Circuit . . . . . . . . . . . 4 Laboratory 4.1 Problem Specications . . . . . . . 4.2 Laboratory Hints . . . . . . . . . . 4.2.1 Component Breakdown . . 4.2.2 System-Wide Hints . . . . . 4.3 Bonus: Visualize Counter on BCDs 5 Design Restrictions 1 Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 2 2 3 3 4 4 8 10 10 12 12 13 15 16 17 17 18 18 19 20 21

. . . . . . . . . . . .

. . . . . . . . . . . .

. . . . . . . . . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

. . . . .

6 Report Reminders 7 Acknowledgements

22 22

Objective

The objective of this laboratory is to design and build a synchronous sequential machine in VHDL. Upon completion, the student must be able to: Design, realize and test a nite state machine; Design, realize and test a trac light controller; Demonstrate a complete understanding for synchronous sequential machine design.

Pre-Lab

Go through the rst six steps of the FSM method presented in section 3 for the trac light controller discussed in this laboratory. Starting with the problem specications given in section 4.1, create a state diagram, convert it to a state table, reduce the latter, choose a state assignment and synthesize a transition table for the trac light controller you are going to implement in this laboratory. Present and explain your work to the TA at the beginning of the session.

Introduction to Synchronous Sequential Machine Design

Designing sequential machines can be very daunting, with all the functional and timing requirements that are imposed on the circuit, as well as the race, hazard and synchronization conditions that could occur, and should be designed against. That said, taking a set of requirements and translating them to a digital synchronous sequential circuit should follow a systematic and dened procedure. We have already seen such a procedure in laboratory #1, namely the algorithmic state machine (ASM) methodology, and in this laboratory, we will be introduced to another systematic procedure for the design of synchronous sequential machines, known from here on simply as sequential machines : the nite state machine (FSM). It is worth noting at this point that this procedure is suitable for describing machines that have a relatively small number of inputs and outputs. For complex machines, the ASM methodology is a more scalable form of representation. Keep this in mind while going through this experiment. The FSM design procedure can be summarized as follows: 2

Problem specication Obtain the specication of the desired circuit; State diagram Create a state diagram which shows all the states that the machine can be in, and how it transitions from one state to another; State table Extract a state table from the state diagram. More advanced designers can create this table without the diagram; State minimization Reduce the number of states in the table by eliminating redundant ones; State assignment Choose a suitable assignment for the states in your table; Transition table Convert the state table into a transition table by incorporating the state minimization and assignment step results; Design equations Choose the type of ip-ops to be used in the circuit, and develop the design equations for the next-state variables and outputs of the circuit; and Circuit implementation Implement the circuit as indicated by the logic expressions in the previous step. This laboratory will attempt to

3.1

Problem Specication

Every circuit designer receives problem specications and attempts to conceive a solution that meets those specications by demonstrating the correct functionality and timing of the circuit. Let us view an example of such a specication. Conceive a synchronous sequential machine required to recognize the 4-bit sequence "1101" by producing an output 1 whenever the sequence occurs in a continuous serial input, and a 0 otherwise. For example, if the input sequence is "0101101011010", the output sequence is "0000001000010". Note that all changes in the circuit occur on the positive edge of a clock signal, and there is one input and one output to the circuit.

3.2

State Diagram

The second step of the FSM procedure is to create a state diagram based on the problem specication, which shows the states and transitions of the machine. Following through with our specication presented in the previous section, the state diagram shown in gure 1 can be synthesized. The state transitions are indicated by arrows out of a state and into another, while the input and output specications are indicated by labels on each transition. For example, the transition leaving state A and entering state B has a 1/0 label, which indicates that when an input of 1 is received while in 3

Figure 1: Sequence detector state diagram state A, transition to state B and output a 0. Note that this state diagram initializes into state A and outputs a 1 only during the transition from state D to state B, indicating that a 1101 sequence has been detected at the serial input stream. Also, note that as soon as one sequence is detected, we transition to state B, rather than the initial state A, in case another 1101 sequence is upon us (we already caught the rst bit at state D).

3.3

State Table

Having conceived a state diagram that resolves our original specication, it is now time to convert it to a state table. The state table extracted from the sequence detector state diagram is shown in table 1. This table can be devised from the problem specications directly, however a state diagram eases the ow and aids in debugging the solution. Present state A B C D Next state x=0 x=1 A B A C D C A B Output x=0 x=1 0 0 0 0 0 0 0 1

Table 1: Sequence detector state table

Now that we have seen an example of state table extraction, let us examine a more complicated state diagram, that we will be referring to throughout the theoretical discussion of this laboratory. The particular state diagram is shown in gure 2, and its extracted state table in table 2.

3.4

State Minimization

The complexity of a sequential machine depends on the number of states in the circuit. That said, it is advantageous to us to attempt and minimize (or at

Figure 2: Example state diagram least reduce) the number of allocated states, by eliminating two or more states that play identical roles (i.e. are equivalent to each other in all respects). This process is called state minimization, or state reduction. The resulting minimized table or diagram should have the same behavior as the original table or diagram with a smaller total number of states. Let us begin with two denitions that will aid us in the discussion of state minimization (extracted from chapter 8 of our textbook). Denition 3.4.1 Two states Si and Sj are said to be equivalent if and only if for every possible input sequence, the same output sequence will be produced regardless of whether Si or Sj is the initial state. Denition 3.4.2 Two states Si and Sj are said to be k-equivalent if and only if for every possible input sequence of length k , the same output sequence will be produced regardless of whether Si or Sj is the initial state. Denition 3.4.3 A partition P (k ) of a set of states in a FSM is a partitioning of the set of states such that the states in a single partition are all k equivalent. Now, we can dene the equivalence-class partitioning method (extracted from Sunggu Lee, see acknowledgements), which is one of the methods that is used in the step of state minimization: 1. Form 1 , where all states in a single partition are 1-equivalent; 5

Present state A B C D E F

Next state x=0 x=1 B A D D A C B F B E D E

Output x=0 x=1 0 0 1 0 0 0 1 0 0 0 1 0

Table 2: Example state table

2. Form 2 from 1 , where states Si and Sj are grouped together if Si and Sj have 1-equivalent next states and and are 1-equivalent; 3. Form k+1 from k , where states Si and Sj are grouped together if Si and Sj have k -equivalent next states and and are k -equivalent; 4. Repeat step 3 until no change occurs from k to k+1 ; and 5. Relabel each group of the nal partition and produce a reduced state table using states identied by the new labels. In order to illustrate the method, let us apply it to our running example. Last time we left it, we had derived the state table in table 2; now let us try and reduce that table by applying the aforementioned minimization method. The output produced for each of the states A, C and E is 0 for both x = 0 and x = 1. The output produced for each of the states B, D and F is 1 when x = 0 and 0 when x = 1. Hence, our rst partition 1 is 1 = (ACE )(BDF ) (1)

For our next partition, 2 , let us consider the rst block of states (ACE ). When x = 0, the next states are (BAB ) which are not present in the same block of 1 , and when x = 1, the next states are (ACE ), which are present in the same block of 1 . Henceforth, since states A and E are 1-equivalent with each other but not with state C, we form two separate blocks: (C )(AE ). As for our second block of states (BDF ): when x = 0, the next states are (DBD), which are present in the same block of 1 , and when x = 1, the next states are (DF E ), which are not present in the same block of 1 . Henceforth, since states B and D are 1-equivalent with each other but not with state F, we form two separate blocks: (F )(BD). Thus, our second partition becomes: 2 = (C )(AE )(F )(BD) (2)

For our next partition, 3 , the next states for both x = 0 and x = 1 for the rst block of states (AE ) are present in the same block of 2 , hence the

block is not separated. For our second block of states (BD), the next states for x = 0 are (DB ) which are present in the same block of 2 , however, for x = 1, the next states are (DF ), which are not present in the same block of 2 . Henceforth, states B and D are not 1-equivalent and have to be separated: (B )(D). Thus, our third partition becomes: 3 = (C )(AE )(F )(B )(D) Applying step 3 again to form our next partition, we obtain: 4 = (C )(AE )(F )(B )(D) (4) (3)

Since 3 and 4 are identical, we move to step 5 of the equivalence-class partitioning method of relabelling our states within our table: in our case, 3 is considered to be the equivalence partition and states A and E are considered to be equivalent. The reduced (or minimized) state table is shown in table 3, where state E has been eliminated and replaced by state A! Present state A B C D F Next state x=0 x=1 B A D D A C B F D A Output x=0 x=1 0 0 1 0 0 0 1 0 1 0

Table 3: Example reduced state table

The state diagram can, but is not required to, be updated according to the newly reduced state table. The reduced state diagram is shown in gure 3. Section 8.6.1 of your textbook take you through other examples of this minimization procedure, and the student is referred to that section for more detail on this topic, including the minimization of incompletely specied FSMs. In concluding this sub-section, it is important to take note of the following issues: Reduction does not necessarily imply minimization: throughout this discussion, we have implied this equivalence, however, state reduction is a better description of these techniques, as there is no deterministic way of guaranteeing optimal minimization of state tables; CAD tools utilize proprietary heuristic techniques to achieve state reduction that borders on optimal state minimization. The CAD vendors usually guard these techniques very cautiously as state minimization and logic minimization methodologies are two main factors that separate one tool from the next;

Figure 3: Example reduced state diagram There are other reduction techniques, such as reduction by implication, that will not be covered here due to a shortage of time and space, however the student is advised to research them on their own time.

3.5

State Assignment

Looking at our reduced state table, we notice that we have 5 states. When implemented in a logic circuit, each state is represented by a combination of state variables, the latter being the output of a ip-op. In order to realize the state table in a logic circuit, it is necessary to encode the states in binary form, a step known as state assignment. There are numerous state encodings, with the most popular ones being: Sequential Gray One-hot Random Auto (area minimization) Each has its associated advantages and disadvantages, with no deterministic method to picking which encoding is best for which circuit. Worse yet, each encoding has dierent state assignment combinations with table 4 showing that for a sequential state encoding, there are 140 unique state assignment combinations for a 5-state circuit and over 75 million for a 9-state circuit! 8

# states 2 3 4 5 8 9 10

# state variables 1 2 2 3 3 4 4

# state assignment combinations 1 3 3 140 840 10,810,800 75,675,600

Table 4: Number of state assignment combinations

All is not lost, as modern CAD tools utilize heuristic techniques to establish the best state encoding and state assignment for a particular circuit. Again, these proprietary techniques are seldom publicized. Never the matter, since we are not designing circuits with the intent of optimally minimizing their area consumption whilst optimally maximizing their operating frequency, it is interesting to attempt to encode the circuits using at least one of the aforementioned methods. Since our running example has 5 states to it, table 5 demonstrates a particular state assignment for each aforementioned state encoding (note that the area optimized one is the CAD tool-specic encoding). Sequential A=000; B=001; C=010; D=011; F=100; Gray A=000; B=001; C=011; D=010; F=110; One-hot A=00001; B=00010; C=00100; D=01000; F=10000; Random A=011; B=111; C=001; D=000; F=101;

Table 5: Example state assignment Sequential and random encodings are self-explanatory, while Gray encoding implies that just one bit in the state vector changes value when the state machine changes state. Finally, one-hot encoding has as many ip-ops as states, with only one ip-op set at any one clock cycle. It may seem that the one-hot encoding is wasteful of sequential resources, but with the new era of FPGAs with high ip-op counts, it sometimes is more eective to utilize this encoding when synthesizing to an FPGA. Also, it is quite interesting to note that it has been proven that a random encoding may produce, in certain situations, results as good as, if not better, any other encoding scheme! In this example, we will pick the Gray state encoding, but the student is advised to retry the example using the sequential as well as the one-hot encoding techniques. Thus, our nal state assignment becomes: A=000, B=001, C=011, D=010 and F=110.

3.6

Transition Table

Having chosen a state encoding and state assignment, it is now time to convert our reduced state table into a state transition table, or just transition table. This is the easiest step of the entire procedure, with our running examples transition table shown in table 6. Note that we have denoted our state variables as y2 , y1 and y0 , while our next-state variables are denoted as Y2 , Y1 and Y0 (more on this later). Present state y2 y 1 y 0 A 000 B 001 C 011 D 010 F 110 Next state x=0 x=1 Y2 Y1 Y0 Y2 Y1 Y0 001 000 010 010 000 011 001 110 010 000 Output x=0 0 1 0 1 1 x=1 0 0 0 0 0

Table 6: Example transition table

3.7

Design Equations

Having obtained a transition table for our circuit, the next step is to choose the type of ip-ops to be used as our sequential components, and develop the design equations for the next-state variables (called excitation equations ) and for our system outputs. There are three main types of ip-ops to choose from: D, J-K and T. The simplest and most common ip-op in todays FPGAs is the D-type ip-op. Let us develop the excitation equations for our D ip-ops. Referring to table 7, we can see the inputs that must be given to each ip-op to cause a specic state transition, and for that reason this table is called an excitation table. Present State Qt 0 0 1 1 Next State Qt+1 0 1 0 1 D Flip-Flop D 0 1 0 1 J-K Flip-Flop J K 0 d 1 d d 1 d 0 T Flip-Flop T 0 1 1 0

Table 7: Excitation table for ip-ops

We can hence, using 4-variable Karnaugh-maps (see gure 4), derive our excitation and output equations as follows (note that for all other state assignments, the next state variables and outputs are taken as dont cares): 10

Y2 = y2 y1 y0 x Y1 = (y2 x) + (y0 x) + (y1 y0 ) + (y2 y1 x) Y0 = (y2 y0 x) + (y1 y0 x) z = (y1 y0 x) + (y1 y0 x)

(5) (6) (7) (8)

Figure 4: Karnaugh-maps for Y2 , Y1 , Y0 and z To conclude this sub-section, let us compare the excitation tables of D vs. J-K vs. T ip-ops, as shown in table 8. A similar approach can be taken to extract the excitation and output equations for a J-K or T ip-op implementation (this is left as an exercise for the student).

Present state y 2 y1 y0 A 000 B 001 C 011 D 010 F 110 Next state Y2 Y1 Y0 001 010 000 001 010 J2 K2 0d 0d 0d 0d d1 x = 0 J1 K1 0d 1d d1 d1 d0 J0 K0 1d d1 d1 1d 0d T2 T1 T0 001 011 011 011 100 Y2 Y1 Y0 000 010 011 110 000 J2 K2 0d 0d 0d 1d d1 x = 1 J1 K1 0d 1d d0 0d d0 J0 K0 0d d1 d1 1d 0d T2 T1 T0 000 011 000 100 110 Output x = 0 0 1 0 1 1 x = 1 0 0 0 0 0

Table 8: Example excitation table

11

3.8

Circuit Implementation

The nal step of the FSM design procedure involves the realization of the circuit as indicated by the logic expressions derived in the previous step. Before we present our running examples nal circuit, it is important to discuss the dierent generic structures of a synchronous sequential circuit. Presented in gure 5 is a synchronous sequential circuit with system inputs and system outputs and sequential components to keep the system states. As we can now see, the next-state variables become the present-state variables at each edge of the system clock. The system outputs however, are generated by a combination of system inputs and the present-state variables, or by the present-state variables only. We will see the dierence in the next two (sub-)sub-sections.

Figure 5: Generic synchronous sequential circuit

3.8.1

Moore vs. Mealy

If the system outputs of a sequential circuit depend on only the state of the circuit, then it is considered to be of the Moore type, whereas if the system outputs of a sequential circuit depend on both the state and the system inputs of the circuit, then it is considered to be of the Mealy type. These types are named after their primary investigators, Edward Moore and George Mealy, who discovered their dierences in the 1950s. A Moore-type FSM, normally called a Moore machine, is customarily more common than a Mealy machine, however the latter does provide the designers with additional exibility, as the system outputs can change with the system inputs, a feature lost on Moore machines. 12

That said, the author tends to remember one over the other through the idiom less is more, which implies that with a Moore machine, less variables aect the outputs (i.e. only the state variables). Figure 6 represents the main dierence between the two types of FSMs.

Figure 6: Moore vs. Mealy machines

3.8.2

Moore VHDL Model

In a Moore machine, there are three separate actions that have to be constantly monitored: (i) updating the next-state variables, (ii) updating the system outputs, and (iii) maintaining the present state. The rst two actions are not driven by the clock and hence are combinational circuits, whilst the last action is driven by the clock and hence is a sequential circuit. All three can be modeled by VHDL processes as follows: LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY FSM IS PORT (i_clk, i_resetb : IN STD_LOGIC); i_x : IN STD_LOGIC; o_z : OUT STD_LOGIC)); END FSM; ARCHITECTURE Moore OF FSM IS 13

TYPE state_type is (A, B, C, D); SIGNAL presentState, nextState : state_type; BEGIN -- Comb. process to update the next-state variables PROCESS (presentState, i_x) BEGIN CASE presentState is WHEN A => IF i_x = 0 THEN nextState <= A; ELSE nextState <= B; END IF; WHEN B => IF i_x = 0 THEN nextState <= A; ELSE nextState <= C; END IF; WHEN C => IF i_x = 0 THEN nextState <= D; ELSE nextState <= C; END IF; WHEN D => IF i_x = 0 THEN nextState <= A; ELSE nextState <= B; END IF; END CASE; END PROCESS; -- Seq. process to maintain the present state PROCESS (i_clk, i_resetb) BEGIN IF (i_resetb = 0) THEN presentState <= state_typeLEFT -- or A ELSIF (i_clkEVENT AND i_clk = 1) THEN presentState <= nextState; END IF; END PROCESS; -- Comb. process to update the system outputs (Moore) PROCESS (presentState) BEGIN CASE presentState is when A => o_z <= 0; when B => o_z <= 0; 14

when C => when D => END CASE; END PROCESS; END Moore; 3.8.3

o_z <= 0; o_z <= 1;

Mealy VHDL Model

In a Mealy machine, there are also the same three separate actions that have to be taken as in a Moore machine, however, the system output update action will depend on the system states as well as the system inputs. Hence, the VHDL model of a Mealy machine is very similar to that of a Moore machine, except for the system outputs update process, which will look as such: -- Comb. process to update the system outputs (Mealy) PROCESS (presentState) BEGIN CASE presentState is when A => IF i_x = 0 THEN o_z <= 0; ELSE o_z <= 0; END IF; when B => IF i_x = 0 THEN o_z <= 0; ELSE o_z <= 0; END IF; when C => IF i_x = 0 THEN o_z <= 0; ELSE o_z <= 0; END IF; when D => IF i_x = 0 THEN o_z <= 0; ELSE o_z <= 1; END IF; END CASE; END PROCESS; END Moore; One nal note on VHDL coding for this laboratory, you can specify the state assignment of your machine in VHDL by either using attributes for your state types, or constants for your states. Please refer to section 8.4, and in particular 8.4.6, of your textbook for a deeper discussion on VHDL coding of Moore and Mealy machines. 15

3.8.4

Final Circuit

Assuming we are using D ip-ops, our running examples nal circuit is shown in gure 7. The reader can notice that since our example turned out to be a Mealy machine, the output z is driven by both the system states y2 , y1 and y0 , as well as the system input x.

Figure 7: D ip-op realization of our example

16

Laboratory

In this lab, you will, utilizing the eight steps of the FSM method, proceed to implement a trac light controller by rst identifying its state diagram and corresponding reduced state and transition tables (in the pre-lab), then realizing the circuit of the controller and interfacing it to real-world sensors and lights. Starting from given problem specications, your goal is to design, realize and test the synchronous sequential circuit, using the Quartus II software and the UP-2 board from Altera (for more details, see section 5).

4.1

Problem Specications

Your team has been hired to design a trac light controller. A trac light controls the trac at an intersection between a main street M S and a side street SS . The main street has higher priority than the side one, and thus stays green until at least one car on the side street arrives at the intersection. A car sensor SSCS is present on the side street for such a purpose. The sensor outputs a 1 at the presence of a car on the side street and a 0 otherwise. Normal operation of the trac light consists of the main streets trac light (MSTL) being green and the side streets (SSTL) being red. The MSTL stays green for a in-system-programmable (ISP) period of time M SC , after which if there is a car on the SS, the MSTL turns yellow for a set period M T , then turns to red. The SSTL then turns green for a ISP period of time SSC , after which it automatically turns yellow (even if there are cars at the intersection) for a set period SST , then red. The MSTL goes back to green at that point. If after M ST , there are no cars on the SS, then the MSTL stays green until a car arrives, at which time, the MSTL immediately cycles through its yellow then red changes. The input/output specications of the trac light controller is are shown in table 9.

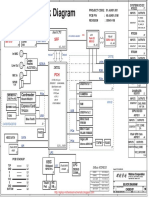

Figure 8: Trac light controller

17

Port Type Input Input Input Input Input Output Output Output Output

Name GClock GReset MSC[3..0] SSC[3..0] SSCS MSTL[2..0] SSTL[2..0] BCD1[3..0] BCD2[3..0]

Description Global clock needed to synchronize the circuitry Global reset needed to bring the internals to known states Main street counter 4-bit input Side street counter 4-bit input Side streets car sensor input Main streets trac light output using one-hot encoding Side streets trac light output using one-hot encoding BCD 4-bit output for left digit of current counter value BCD 4-bit output for right digit of current counter value

Table 9: Input/Output Specication

4.2

Laboratory Hints

The following section is meant to introduce a possible solution to the problem, while discussing the major parts of that solution. Shown in gure 9 is a potential system solution to the trac light controller problem. Included in this gure are the major inputs and outputs of the system, as well as the essential building blocks. The shaded region indicates the bonus mark block, which is not a requirement of the laboratory. 4.2.1 Component Breakdown

We can break down the system diagram into ve major components: FSM Controller This component is the kernel of the system, and drives all the system outputs, after making decisions depending on the system inputs; Main/Side Street Counters These components act as the timers of the MSTL and SSTL, respectively; Comparator This component signals back to the FSM controller that a counter maximum has been reached; Clock Divider This component is used to slow down the system clock, and eectively reduce the overall power of the design; Debouncer This component is used to handle mechanical switch debouncing, and transmit clean car sensory readings to the FSM controller; Timer This component is used to time yellow and red lights for both the main and side street trac lights; and BCD Decoder This component is used to visually demonstrate the current counter status onto a dual-digit BCD 7-segment display.

18

Figure 9: A potential system diagram 4.2.2 System-Wide Hints

It is worthy to note that a global reset is provided to the FSM controller, which eectively resets all the state registers within the FSM, as well as any outputs of the FSM (going out of the system or to other building blocks within the system). This will cause the other blocks to enter their reset condition, and thus for example, cause the timer circuit to reset back to its initial count value. This reset distribution is not shown in gure 9, but it is assumed that the designers will take care of this network. Speaking of global reset, it is up to the designer to input this asynchronous signal to the FPGA. An idea would be to use the second push-button switch available on the board, but the issue of mechanical switch debouncing has to be considered in that case. Other more elaborate ideas would involve using an

19

interrupt scheme, with the global reset being input to the system, external to the UP-2 development board, or using a scheme to detect longer periods where the rst push-button (used as the car sensor signal) is pressed down, and hence indicating a global reset. Actually, the global reset signal has to be asserted for a longer period of time than the car sensor signal in order for the system to reset. Thus, the settling time of the reset signal must be greater than that of the car sensor signal. Note that since the car sensor signal is asynchronous to the FSM controller, synchronizing it would help avoid timing issues. It is also necessary to remember that the on-board LEDs are activated through negative logic, as mentioned in the board specications: The UP Education Boards contain 16 LEDs that are pulled-up with a 330-. resistor. An LED is illuminated when a logic 0 is applied to the female header associated with the LED. The timer outputs Main Street Timer (MST) and Side Street Timer (SST) are used to time yellow lights for the main street and the side street. These can be set by the designer, and will not be in-system programmable. They are hard-wired to a set count value, which does not have to be the same for both the main and side streets. Thus, the side street trac light can stay at yellow for longer or shorter than that of the main street, although it makes sense to make it shorter, as there is a higher chance of having more cars crossing the main street at any time, compared to the side street. Now, the counters that are in-system-programmable are the main and side street counters. These are to be used alongside the DIP switches at MAX SW1 (or FLEX SW1) and MAX SW2 (or FLEX SW2) in order to be able to change the maximum value to wait for a trac light switch, on either the main street or the side street. Please refer to gure 9 for a potential solution to that specication. Presented in this sub-section are the system-wide hints that will aid the designers in the realization of the basic building blocks. There are however, two blocks, that require a bit more attention: the debouncer and the clock divider blocks. The reader is referred to the accompanying Debouncing a Switch and Dividing a Clock document if interested in the theory behind these functions, as well as their alternative realizations.

4.3

Bonus: Visualize Counter on BCDs

For an extra 5 marks, include a BCD decoder block to realize the display of the current counter values onto the 7-segment BCDs in decimal format. The displayed values must not exceed the programmable MSC maximum value, set through the 4-bit DIP switch (SW2). As for the SSC maximum value, as soon as the counter reaches that value, a switch must occur in the trac lights, and thus the displays can be updated accordingly. Thus, it is required that the displays, when reaching the MSC maximum, must remain at that value, until a car arrives at the side street, indicating that a trac light switch is

20

required. Make the necessary changes to your module and present and discuss those modications. You have to demonstrate your new design to your TA.

Design Restrictions

Verilog implementations will not be accepted. Perform all implementations in VHDL code only Behavioral level of modeling will not be accepted. Design should be done at the structural level of modeling Register Transfer Logic (RTL) design and coding is mandatory Use graphical design for the top-level entity, and use your judgement for any other sub-blocks. However, all atomic modules have to be implemented in VHDL (i.e. D ip-op, 1-bit adder, 1-bit comparator and so on) No core instantiations are allowed (i.e. LPMs from Altera or free IP cores from the Internet). All building blocks have to be designed and realized by the group The group may use any of the course-provided cores in their design (i.e. debouncer, clock divider, register, shift register, adder, counter, comparator and so on). Remember to reference all cores that the group has not themselves developed If using the clock divider core in particular, its behavioral level of modeling is accepted The group may use a Mealy or Moore machine as their FSM controller The top level entity is given in input/output specication format, but the internals are left up to the group The design has to be synchronous and globally reset-able. This means that global clock and reset signals are required in all functional blocks Simulate all designs and check your simulation results with your theoretical ones (e.g. go through dierent intersection scenarios) Download the design to the FLEX chip on your UP-2 boards, and use the on-board DIP switches to input MSC[3..0] and SSC[3..0], the on-board push-button switch to input SSCS (the car sensor), and two sets of three LEDs for the trac lights, as shown in gure 8. If implementing the bonus section, the two 7-segment BCD decoders are to be used to demonstrate correct counter functionality (BCD1[3..0] and BCD2[3..0])

21

The group may use the MAX FPGA, but must be careful to note that it is smaller in logic capacity than the FLEX FPGA, however it is a nonvolatile device, hence the design will remain in the FPGA even though the power is recycled Each group must demonstrate a working version of the laboratory to the TA, before the due date of the report

Report Reminders

Include timing simulations with explanation for all VHDL source les Describe and comment all your VHDL source les Include a owchart representation of your solution to the problem Include a block diagram of your solution to the problem If using ASM design, include all appropriate charts and paths (control and data) If using FSM design, include all appropriate diagrams, tables and circuit realizations Describe, in your own words, your solution to the problem Describe your design obstacles and how they were overcome Append all VHDL source code and graphical design les to your report Submit a soft copy of all VHDL and graphical design les with your report

Acknowledgements

Figure 5 is extracted from our course textbook: Fundamentals of Digital Logic with VHDL Design by Stephen Brown and Zvonko Vranesic. The equivalenceclass partitioning method is extracted from Design of Computers and Other Complex Digital Devices by Sunggu Lee.

22

Das könnte Ihnen auch gefallen

- Capstone ResearchProject Moore Mealy MachineDokument9 SeitenCapstone ResearchProject Moore Mealy MachineAnish ChatterjeeNoch keine Bewertungen

- Week 12 - Module 10 Finite State Machines 1Dokument7 SeitenWeek 12 - Module 10 Finite State Machines 1Ben GwenNoch keine Bewertungen

- Ee5101 Ca1 PDFDokument24 SeitenEe5101 Ca1 PDFHamid FarhanNoch keine Bewertungen

- Design A Pulse Mode Circuit Having Two InputDokument4 SeitenDesign A Pulse Mode Circuit Having Two InputSiva GuruNoch keine Bewertungen

- Phase Lead Compensator Design Using Bode PlotsDokument17 SeitenPhase Lead Compensator Design Using Bode PlotsMuhammad YounasNoch keine Bewertungen

- Helicopter Lab (Optimization and Control)Dokument41 SeitenHelicopter Lab (Optimization and Control)Espen Løkseth100% (2)

- Unit - 1 DSDDokument56 SeitenUnit - 1 DSDultimatekp144Noch keine Bewertungen

- Power Systems-On-Chip: Practical Aspects of DesignVon EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNoch keine Bewertungen

- Introduction To Control Engineering: Andy Pomfret and Tim ClarkeDokument54 SeitenIntroduction To Control Engineering: Andy Pomfret and Tim ClarkemmmNoch keine Bewertungen

- Telemark University College Faculty of Technology: M.Sc. ProgrammeDokument41 SeitenTelemark University College Faculty of Technology: M.Sc. ProgrammeSayed LezonNoch keine Bewertungen

- Finite State Machines: Moore MachineDokument4 SeitenFinite State Machines: Moore Machineborakas_borakasNoch keine Bewertungen

- Control Project ModifiedDokument4 SeitenControl Project ModifiedMohamed Elsayed HasanNoch keine Bewertungen

- Designing A Data Synchronizer Logic CircuitDokument6 SeitenDesigning A Data Synchronizer Logic CircuitbabahussainNoch keine Bewertungen

- Oscillator Ads DesignDokument22 SeitenOscillator Ads DesignayoubmalkiNoch keine Bewertungen

- Comparative study on Moore and Mealy State MachinesDokument10 SeitenComparative study on Moore and Mealy State MachinesH052 Rajesh Komaravalli ECENoch keine Bewertungen

- Fpga Implementation of Memory Controller FSM Using Simulink2Dokument57 SeitenFpga Implementation of Memory Controller FSM Using Simulink2AKNoch keine Bewertungen

- Design A Combinatorial Circuit 863832727868Dokument5 SeitenDesign A Combinatorial Circuit 863832727868Siva Guru0% (1)

- Module 5.scilabDokument7 SeitenModule 5.scilaborg25grNoch keine Bewertungen

- TexasDokument18 SeitenTexasAlysson MachadoNoch keine Bewertungen

- Part 1 - FSM DesignDokument3 SeitenPart 1 - FSM DesignMENANI ZineddineNoch keine Bewertungen

- Lab 14Dokument11 SeitenLab 14amalkatribNoch keine Bewertungen

- Comp Freq Lead PDFDokument17 SeitenComp Freq Lead PDFJAMESJANUSGENIUS5678Noch keine Bewertungen

- Experiment 3 Forward KinematicsDokument30 SeitenExperiment 3 Forward KinematicsAnshul AggarwalNoch keine Bewertungen

- DSD Lab Manual 5 21 CPDokument6 SeitenDSD Lab Manual 5 21 CPUsman AbdullahNoch keine Bewertungen

- Sequential Circuits II DocumentDokument21 SeitenSequential Circuits II DocumentBlueNoch keine Bewertungen

- Synchronous Counter Design and AnalysisDokument12 SeitenSynchronous Counter Design and AnalysisRajasekar PichaimuthuNoch keine Bewertungen

- Robotic System ModellingDokument20 SeitenRobotic System ModellingsurajNoch keine Bewertungen

- External Interface (S) Application Guide: Energyplus™ Version 8.8.0 DocumentationDokument31 SeitenExternal Interface (S) Application Guide: Energyplus™ Version 8.8.0 DocumentationffdfddNoch keine Bewertungen

- Lab 2: Quanser Hardware and Proportional Control: I. ObjectiveDokument7 SeitenLab 2: Quanser Hardware and Proportional Control: I. ObjectiveAndré LeopoldinoNoch keine Bewertungen

- External Interface (S) Application Guide: Energyplus™ Version 9.3.0 DocumentationDokument31 SeitenExternal Interface (S) Application Guide: Energyplus™ Version 9.3.0 DocumentationYin LiNoch keine Bewertungen

- DCMotorWithInertiaDisk UpdatedDokument37 SeitenDCMotorWithInertiaDisk UpdatedozcagNoch keine Bewertungen

- DC Motor Control 2017Dokument43 SeitenDC Motor Control 2017Rasheed ShahNoch keine Bewertungen

- LabVIEW HandoutDokument52 SeitenLabVIEW HandoutYatheesh KaggereNoch keine Bewertungen

- 5.CS Lab Manual R14Dokument80 Seiten5.CS Lab Manual R14Kh KhalilNoch keine Bewertungen

- A2 Electronics Project: 8bit Analogue To Digital Slope ConverterDokument48 SeitenA2 Electronics Project: 8bit Analogue To Digital Slope Converterhello12353Noch keine Bewertungen

- Finite State MachinesDokument17 SeitenFinite State Machineslashali1212Noch keine Bewertungen

- DC Motor Speed Transfer Function and State-Space ModelingDokument13 SeitenDC Motor Speed Transfer Function and State-Space ModelingMohamed Elsayed HarbNoch keine Bewertungen

- PDFDokument24 SeitenPDFOlga Joy Labajo GerastaNoch keine Bewertungen

- 03a Section3 Notes CPD SDDS1 FSMDokument34 Seiten03a Section3 Notes CPD SDDS1 FSMRohit BanerjeeNoch keine Bewertungen

- Project Report Designing Position Control System: Abu Dhabi UniversityDokument13 SeitenProject Report Designing Position Control System: Abu Dhabi UniversityMohammed ShifulNoch keine Bewertungen

- Power System Case StudyDokument18 SeitenPower System Case Studysmurf aldous100% (1)

- MatDyn1 2Dokument35 SeitenMatDyn1 2Miguel AcbNoch keine Bewertungen

- FSM ProbDokument3 SeitenFSM ProbSouhardya MondalNoch keine Bewertungen

- State Reduction and State AssDokument37 SeitenState Reduction and State AssanjugaduNoch keine Bewertungen

- Tutorial NuSMVDokument32 SeitenTutorial NuSMVRameshwar JuptimathNoch keine Bewertungen

- Boram: Balancing Robot Using Arduino and Lego: Kyungjae Baik (9193618) September 10, 2008Dokument26 SeitenBoram: Balancing Robot Using Arduino and Lego: Kyungjae Baik (9193618) September 10, 2008Carlos Solon Soares Guimarães Jr.Noch keine Bewertungen

- CPE 6204 - Logic Circuits and Switching Theory Module on Finite State MachinesDokument13 SeitenCPE 6204 - Logic Circuits and Switching Theory Module on Finite State MachinesBen GwenNoch keine Bewertungen

- FPGA Assignment 3 SMADokument15 SeitenFPGA Assignment 3 SMAScribed aliNoch keine Bewertungen

- Mentor Graphics Tutorial: Schematic Capture, Simulation, & Placement/RoutingDokument22 SeitenMentor Graphics Tutorial: Schematic Capture, Simulation, & Placement/RoutingHairil HanifNoch keine Bewertungen

- Comp Root TransDokument22 SeitenComp Root TransEdhemNoch keine Bewertungen

- TE 2019 MechatronicsDokument6 SeitenTE 2019 MechatronicsVishalNoch keine Bewertungen

- Electronics Digital : ASM2 Second Class RealizationDokument8 SeitenElectronics Digital : ASM2 Second Class RealizationSri LathaNoch keine Bewertungen

- 1DMCQDMCDokument45 Seiten1DMCQDMCErma Sulistyo RNoch keine Bewertungen

- Lab No.9 Design of Synchronous Counter ObjectivesDokument5 SeitenLab No.9 Design of Synchronous Counter Objectivesasadmehmoodsatti786Noch keine Bewertungen

- PSOC Questions on AGC controlDokument33 SeitenPSOC Questions on AGC controlsdNoch keine Bewertungen

- Phase Lag Compensator Design Using Bode Plots - Comp - Freq - LagDokument14 SeitenPhase Lag Compensator Design Using Bode Plots - Comp - Freq - LagBrian LevineNoch keine Bewertungen

- Switching Activity Estimation of Finite State Machines For Low Power SynthesisDokument4 SeitenSwitching Activity Estimation of Finite State Machines For Low Power SynthesisbrufoNoch keine Bewertungen

- VHDL FSM UNIT 5 ET&T 7th SemDokument22 SeitenVHDL FSM UNIT 5 ET&T 7th SemDEEPA KUNWARNoch keine Bewertungen

- Electrical Theory: Howard W Penrose, PH.D., CMRP InstructorDokument79 SeitenElectrical Theory: Howard W Penrose, PH.D., CMRP InstructorSandun LakminaNoch keine Bewertungen

- Matlab Training Session Iii Numerical Methods: Solutions To Systems of Linear EquationsDokument14 SeitenMatlab Training Session Iii Numerical Methods: Solutions To Systems of Linear EquationsAli AhmadNoch keine Bewertungen

- PH Alkalinity ExplainedDokument4 SeitenPH Alkalinity ExplainedDean DsouzaNoch keine Bewertungen

- AC MaintenanceDokument21 SeitenAC MaintenanceAli AhmadNoch keine Bewertungen

- Matlab Training Session Ii Data Presentation: 2-D PlotsDokument8 SeitenMatlab Training Session Ii Data Presentation: 2-D PlotsAli AhmadNoch keine Bewertungen

- Matlab Training - Basic Control TheoryDokument10 SeitenMatlab Training - Basic Control TheoryhamedNoch keine Bewertungen

- The Purpose of Business Activity: LECTURE # 01 & 02Dokument9 SeitenThe Purpose of Business Activity: LECTURE # 01 & 02Ali AhmadNoch keine Bewertungen

- Lecture 2 - 30-01-08Dokument17 SeitenLecture 2 - 30-01-08Ali AhmadNoch keine Bewertungen

- The Purpose of Business Activity: LECTURE # 01 & 02Dokument9 SeitenThe Purpose of Business Activity: LECTURE # 01 & 02Ali AhmadNoch keine Bewertungen

- Matlab Training Session Vii Basic Signal Processing: Frequency Domain AnalysisDokument8 SeitenMatlab Training Session Vii Basic Signal Processing: Frequency Domain AnalysisAli AhmadNoch keine Bewertungen

- Jan 2008 Course Outline FinanceDokument5 SeitenJan 2008 Course Outline FinanceAli AhmadNoch keine Bewertungen

- MATLAB M-files Scripts and Functions GuideDokument6 SeitenMATLAB M-files Scripts and Functions Guideederdiego2709Noch keine Bewertungen

- Business Management Process Improvement LectureDokument26 SeitenBusiness Management Process Improvement LectureAli AhmadNoch keine Bewertungen

- Matlab Training - SIMULINKDokument8 SeitenMatlab Training - SIMULINKAtta RehmanNoch keine Bewertungen

- Printing The Model:: SimulinkDokument8 SeitenPrinting The Model:: SimulinkAli AhmadNoch keine Bewertungen

- Matlab Training - SIMULINKDokument8 SeitenMatlab Training - SIMULINKAtta RehmanNoch keine Bewertungen

- Introduction To VHDL: AIR University AU, E-9, IslamabadDokument29 SeitenIntroduction To VHDL: AIR University AU, E-9, IslamabadAli AhmadNoch keine Bewertungen

- SIMULATING DYNAMIC SYSTEMS USING MATLABDokument9 SeitenSIMULATING DYNAMIC SYSTEMS USING MATLABAli AhmadNoch keine Bewertungen

- 2-Level Logic ( 0', 1') .: Introduction To ASIC DesignDokument8 Seiten2-Level Logic ( 0', 1') .: Introduction To ASIC DesignAli AhmadNoch keine Bewertungen

- Operators: Introduction To ASIC DesignDokument6 SeitenOperators: Introduction To ASIC DesignAli AhmadNoch keine Bewertungen

- Lecture 2Dokument26 SeitenLecture 2Ali AhmadNoch keine Bewertungen

- Introduction To: Artificial IntelligenceDokument31 SeitenIntroduction To: Artificial IntelligenceAli AhmadNoch keine Bewertungen

- Table of Contents DocumentDokument11 SeitenTable of Contents DocumentAli AhmadNoch keine Bewertungen

- 5.1 Multiplexer #1 Using Operators WHEN/ELSEDokument10 Seiten5.1 Multiplexer #1 Using Operators WHEN/ELSEAli AhmadNoch keine Bewertungen

- Small Neural Nets LabDokument6 SeitenSmall Neural Nets LabAli AhmadNoch keine Bewertungen

- System On Chips Soc'S & Multiprocessor System On Chips MpsocsDokument42 SeitenSystem On Chips Soc'S & Multiprocessor System On Chips MpsocsAli AhmadNoch keine Bewertungen

- Sequential Code in VHDLDokument42 SeitenSequential Code in VHDLAli Ahmad0% (1)

- Introduction To ASIC Design: Lab Report InstructionsDokument1 SeiteIntroduction To ASIC Design: Lab Report InstructionsAli AhmadNoch keine Bewertungen

- Multiply and Accumulate Circuits LabDokument5 SeitenMultiply and Accumulate Circuits LabAli AhmadNoch keine Bewertungen

- Introduction To ASIC Design: Lab Report StandardsDokument1 SeiteIntroduction To ASIC Design: Lab Report StandardsAli AhmadNoch keine Bewertungen

- Requirements ElicitationDokument5 SeitenRequirements ElicitationShivendra VermaNoch keine Bewertungen

- Chapter 3 - SelectionsDokument52 SeitenChapter 3 - Selectionsnaqibullah2022faryabNoch keine Bewertungen

- Design and Analysis Mini CNC Plotter MachineDokument23 SeitenDesign and Analysis Mini CNC Plotter MachineUsman BhattiNoch keine Bewertungen

- System Admin QuestionsDokument9 SeitenSystem Admin QuestionsNagaraju KasaNoch keine Bewertungen

- Simputer MainDokument21 SeitenSimputer MainPramiti ParasharNoch keine Bewertungen

- LogSolid Converter PDFDokument3 SeitenLogSolid Converter PDFMustaqimNoch keine Bewertungen

- UM1949 User Manual: Getting Started With STM32 Nucleo PackDokument12 SeitenUM1949 User Manual: Getting Started With STM32 Nucleo Packluis RYFNoch keine Bewertungen

- Industrial Training Report For ISPDokument31 SeitenIndustrial Training Report For ISPMahmudur RahmanNoch keine Bewertungen

- Instructions For Authors of SBC Conferences Papers and AbstractsDokument4 SeitenInstructions For Authors of SBC Conferences Papers and AbstractsWill MakenzyNoch keine Bewertungen

- WDIP - API Specifications - Release 2.1 - v0.2 - FinalDokument1.138 SeitenWDIP - API Specifications - Release 2.1 - v0.2 - FinalAnonymous QwwZmjNoch keine Bewertungen

- TMF635 Usage Management API REST Specification R14.5.1Dokument51 SeitenTMF635 Usage Management API REST Specification R14.5.1DuyHung DangNoch keine Bewertungen

- Snowflake Hands-On Lab GuideDokument58 SeitenSnowflake Hands-On Lab GuideRudransh Sharma50% (4)

- Deep NIN Models for Encrypted Network Traffic ClassificationDokument10 SeitenDeep NIN Models for Encrypted Network Traffic ClassificationPraveen KumarNoch keine Bewertungen

- Network Micro SegmentationDokument6 SeitenNetwork Micro SegmentationPranab BalaNoch keine Bewertungen

- Android Based Object Detection Application For Food ItemsDokument6 SeitenAndroid Based Object Detection Application For Food ItemsHafza GhafoorNoch keine Bewertungen

- Integrating With Oracle HCM CloudDokument432 SeitenIntegrating With Oracle HCM CloudsjawadNoch keine Bewertungen

- TelecomHall Boda Definition en-US 2019-Q3Dokument32 SeitenTelecomHall Boda Definition en-US 2019-Q3Hirak Jyoti MazumdarNoch keine Bewertungen

- Allied Telesis Network Boosts Nexus Resort (39Dokument9 SeitenAllied Telesis Network Boosts Nexus Resort (39Angelie BorjaNoch keine Bewertungen

- Xcams - EBookDokument34 SeitenXcams - EBookmerarib342Noch keine Bewertungen

- Expose An Stateless Session Bean As A Web ServiceDokument20 SeitenExpose An Stateless Session Bean As A Web Serviceviveksingh21csNoch keine Bewertungen

- D3.1.7 Training Module 1.3 Introduction To RDF - SPARQL - EUI - v0.08Dokument39 SeitenD3.1.7 Training Module 1.3 Introduction To RDF - SPARQL - EUI - v0.08Willams Clemente CavalcanteNoch keine Bewertungen

- Copa Nimi App QuestionDokument15 SeitenCopa Nimi App Questionmeethi09Noch keine Bewertungen

- Thesis Docu - Group 3Dokument163 SeitenThesis Docu - Group 3Charles Ramos KabilingNoch keine Bewertungen

- FileDokument651 SeitenFileSony Neyyan VargheseNoch keine Bewertungen

- How To Improve ASCP Data Collections PerformanceDokument6 SeitenHow To Improve ASCP Data Collections PerformancePramodNoch keine Bewertungen

- CADIZ-CP Block Diagram: Intel CPUDokument57 SeitenCADIZ-CP Block Diagram: Intel CPUvnenovNoch keine Bewertungen

- Operating Systems Scheduling Criteria ExplainedDokument21 SeitenOperating Systems Scheduling Criteria ExplainedElangovan GuruvaReddyNoch keine Bewertungen

- Security System Using RFID: A Project ReportDokument30 SeitenSecurity System Using RFID: A Project Reportdnadar881Noch keine Bewertungen

- Internet Threats To ChildrenDokument23 SeitenInternet Threats To ChildrenDr Tushar DashoraNoch keine Bewertungen

- 1.1 Motivation: 1.2 Problem StatementDokument23 Seiten1.1 Motivation: 1.2 Problem StatementzakeermasNoch keine Bewertungen