Beruflich Dokumente

Kultur Dokumente

Lect 07

Hochgeladen von

ANkit JAinOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lect 07

Hochgeladen von

ANkit JAinCopyright:

Verfügbare Formate

EECE481

Lecture 7

Lecture 7 Noise Margin in Digital Circuits

Res Saleh Dept. of ECE University of British Columbia res@ece.ubc.ca

RAS

EECE481 Lecture 7

Overview

Reading

HJS Chapter 4; Sections 4.1, 4.2, 4.3

Background

Digital IC designs must operate properly in noisy environments. We would like to have some notion of how robust a circuit is to external noise sources. There are a variety of measures of noise for logic circuits such as single stage noise margin (SSNM) and the classical noise margins are based on the unity gain points of the VTC. These metrics eventually lead us to desirable properties that logic gates must have in order to work properly. We will look at how to calculate this for inverters in the next lecture.

RAS

EECE481 Lecture 7

EECE481

Lecture 7

Noise Margins and Sensitivity

Robustness of a circuit (i.e., its ability to operate properly in the presence of noise) depends on two factors: 1. Noise margins (voltage metric) - how much noise can we apply before the gate fails - many different ways to measure this 2. Noise sensitivity - how much noise can actually couple into the gate - depends on gate type and its connection to noise source First component sets requirements on the gate to handle noise Second component captures the response of the circuit to a given noise input (will be discussed in later chapters of HJS) Start by examining the first issue using basic inverter circuit

RAS EECE481 Lecture 7 3

Ideal Inverter Characteristics

Vout

VDD Ideal 0 Gain = 0 Gain =

Gain = 0

Vin

VDD/2 VDD VDD 1

Output range for logic 1

Input range for logic 1 Input range for logic 0

VDD 1 VDD/2 0 0

Output range

0 Input range

EECE481 Lecture 7

0 Output range

for logic 0

RAS

EECE481

Lecture 7

Actual Inverter Characteristics

VOUT VOH

V

OUH

Low Gain Gain > 1

VOUT=VIN

VS

Low Gain

VOL VO U L VOL VI L V VS

IH

VDD VOH VIN

VDD 1 VIH

X (unknown)

VOH VOUH

1

X (unknown)

VIL 0 0 Input range

RAS

VOUL VOL 0 Output range

EECE481 Lecture 7 5

Noise Attenuation

What does this type of VTC imply about a noisy signal as it passes through a logic gate? Noise is reduced:

VIL 0

VIN

Valid Logic 1

Valid Logic 0

VOUT

VOH VOUH

Next, consider metrics for noise tolerance and the implications on the characteristics of the gate

RAS EECE481 Lecture 7 6

EECE481

Lecture 7

Single Stage Noise Margins

Simplest type of noise margin is the single-stage noise margin Defined as maximum noise, vn, in a single stage that still allows subsequent stages to recover to the right value (regenerative property)

VOL VOH 1 Noise + vn 2 ? 3 ? 4 ?

In the above circuit Vi2 = Vo1 - vn = VOH - vn For noise added to a high level input, the correct levels will be maintained if VOH - vn > VTH (point where Vin = Vo) For noise added to a low level input, correct levels will be maintained if VOL + vn < VTH

RAS EECE481 Lecture 7 7

Single Stage Noise Margins

VO(EVEN) V (ODD)

SSNMH = VOH - VS SSNML = VS - VOL

VS SSNML VO2 VO4 VOH VO5 VO3 V (EVEN) VO(ODD) VS

VOL ( = VO6

vn SSNMH

RAS

EECE481 Lecture 7

EECE481

Lecture 7

Multistage Noise Margins

Noise actually occurs between every gate and not at a single stage, as we have assumed so far

VOL VOH 1 Noise + vn 2 Noise ? + vn 3 ?

In the above circuit, we need to determine how much noise we can tolerate before the circuit stops working as expected We note that Vout = f(Vin) With noise Vout = f(Vin) + Vnoise x Gain + Higher-order terms If the Gain < 1, then noise is attenuated; otherwise it is amplified IDEA: Develop a metric based on keeping the Gain < 1

RAS EECE481 Lecture 7 9

Classical Noise Margins

VO slope = 1

VDD

NMH = VOH - VIH NML = VIL - VOL

VOUH slope = 1 VOUL VIL VS VDD VI H

VI N

VOL

VOH

VIH

VOL

VIL

VOH

Noise

RAS

Noise

EECE481 Lecture 7 10

EECE481

Lecture 7

Requirements for a Valid Logic Gate

Must have a high gain region between two low gain regions Gain must be below 1 for low gain regions Gain must be greater than 1 for high gain region Output must swing from valid low to valid high Low output should be below VIL High output should be above VIH

RAS

EECE481 Lecture 7

11

Next lecture: MOS Inverters

Basic structure of MOS inverter is shown below: NMOS pulldown device with a variety of possible pullup devices

INVERTER

VDD Load Device (Pull Up) VOUT Nonlinear Resistance (NMOS, PMOS) or Active Switch (PMOS)

VIN

Inverting Device (Pull Down)

Active Switch (NMOS)

We will derive the noise margin parameters for different types of inverters

RAS EECE481 Lecture 7 12

Das könnte Ihnen auch gefallen

- Adptive Antenna Array ParthDokument22 SeitenAdptive Antenna Array ParthANkit JAinNoch keine Bewertungen

- RefeDokument1 SeiteRefeANkit JAinNoch keine Bewertungen

- Unit 5 Labour LawDokument22 SeitenUnit 5 Labour LawANkit JAinNoch keine Bewertungen

- Final List - Eligible For A3Logics Second DriveDokument8 SeitenFinal List - Eligible For A3Logics Second DriveANkit JAinNoch keine Bewertungen

- Without This Message by Purchasing Novapdf : Print To PDFDokument1 SeiteWithout This Message by Purchasing Novapdf : Print To PDFANkit JAinNoch keine Bewertungen

- Jktlfkku JKT 'KSF (KD Vuqla/Kku, Oa Izf'K (K.K Lalfkku) MN Iqj FokfirDokument4 SeitenJktlfkku JKT 'KSF (KD Vuqla/Kku, Oa Izf'K (K.K Lalfkku) MN Iqj FokfirANkit JAinNoch keine Bewertungen

- Multiple Choice Questions PNJunctionDokument2 SeitenMultiple Choice Questions PNJunctionANkit JAinNoch keine Bewertungen

- Final Interested List - Wipro BPO 2013Dokument4 SeitenFinal Interested List - Wipro BPO 2013ANkit JAinNoch keine Bewertungen

- FR Ese2012 EngDokument18 SeitenFR Ese2012 EngANkit JAinNoch keine Bewertungen

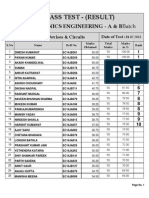

- Edc A B Result FinalDokument11 SeitenEdc A B Result FinalANkit JAinNoch keine Bewertungen

- Poornima Group of Colleges, Jaipur: Time TableDokument2 SeitenPoornima Group of Colleges, Jaipur: Time TableANkit JAinNoch keine Bewertungen

- Without This Message by Purchasing Novapdf : Print To PDFDokument1 SeiteWithout This Message by Purchasing Novapdf : Print To PDFANkit JAinNoch keine Bewertungen

- 4.table of ContentDokument1 Seite4.table of ContentANkit JAinNoch keine Bewertungen

- CertificateDokument1 SeiteCertificateANkit JAinNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)