Beruflich Dokumente

Kultur Dokumente

Digi

Hochgeladen von

Abdowlaye Smith CampoCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Digi

Hochgeladen von

Abdowlaye Smith CampoCopyright:

Verfügbare Formate

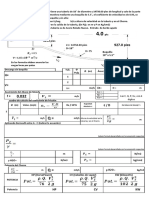

DISEO DE LA CELDA La celda de 32x4 que ofrece el sistema operativo xilinx tiene la desventaja de que la escritura y la lectura se realizan

al mismo tiempo, situacin que no es deseable, por ende se debe implementar un arreglo que evite lo mencionado. Vase la tabla de su comportamiento.

Figura 1.de la memoria del xilinx

Inputs WE 0 (read) 1 (read) 1 (read) 1 (write) 1 (read)

WCLK X 0 1

D3-D0 X X X D3-D0 X

Outputs O3-O0 Data Data Data D3-D0 Data

Data = word addressed by bits A4 A0

El diseo implementado consiste en un arreglo de compuertas, incluyendo las triestado cuya funcin ser colocar en alta impedancia las salidas evitando as la situacin anteriormente planteada; como se muestra a continuacin en la tabla de funcionamiento del circuito. Figura numero2. Celda con arreglo de compuertas.

Figura 3.Tabla de la celda ENABLE 0 1 1 READ-WRITE X 0 1 SALIDA Z Dato Z FUNCION Stand-by Lectura escritura

La alta impedancia (Z) permitir que no se generen conflictos de datos, de este modo la misma lnea por donde ingresan los datos servir de salida para los mismos. A continuacin se mostrara la simulacin del esquemtico (figura 2). EXPLICACION DE LA SIMULACION En la simulacin puede observarse que el enable es la entrada que controla la memoria, si este se encuentra en cero la deshabilitar y entrar en el estado de stand by con alta impedancia, de lo contrario estar habilitada y depender de los datos que se ingresen en la entrada read-write, (read-wriite=o lee, read-write=1 escribe). Como el bus de datos es bidireccional, cuando se escriba en la celda la salida debe permanecer en alta impedancia, anlogamente cuando se lea, para evitar conflictos de datos. Se puede ver que se est pasando cclicamente del estado stand by a escritura, y de stand by a lectura.

ENCAPSULADO DE LA CELDA

Figura N. 4 Encapsulado de la celda

Como la expansin de la memoria es de 8x8, a manera de hacer ms simple y organizada las conexiones de las celdas, se decidi encapsular la fila que forma un registro.

Figura N. 5 formacin del registro.

Figura N.6 registro encapsulado

Simulacin del registro. Esta simulacin no es muy diferente a la de la celda inicial, como podemos ver la funcin de stand by tambin depende del habilitador (EN) y la funcin de lectura escritura de la entrada W_R. el nico cambio notable, es la aparicin de un bus de direcciones (BUSADRESSSAS) que tiene como funcin seleccionar la celda especifica dentro del registro en la que se guardara o leer un dato.

CONTRUCCION DE LA MATRIZ 8X1

A continuacin se mostrara la matriz resultante de la expansin de memoria que se ha venido trabajando. Esta debera ser una matriz de 8x8, pero recordemos que ya se han encapsulado 8 celdas que conforman las filas (registros de la memoria), por esto, queda una matriz de 8X1 que se ver mucho ms simple y comprensible para el lector. La funcin de esta matriz estar dada por las entradas de lectura escritura (R_W) y el habilitador de memoria (EN) cuyas funciones fueron explicadas anteriormente. La habilitacin de registro para la funcin de lectura o escritura estar controlada por un decodificador (D3_8E), de manera que cuando uno de los registros este activo, el resto se encuentren en stand by. Y la celda en la que se guardara o leera el dato, estar controlada por el bus de direcciones (BUSADRESSSAS).

Simulacin matriz 1x8 SIMULACION MATRIZ MATRIZ 1x8

En esta simulacin se observa las entradas del decodificador

Das könnte Ihnen auch gefallen

- Presentacion UpsDokument15 SeitenPresentacion UpsAbdowlaye Smith CampoNoch keine Bewertungen

- Sangre BiotecnologiaDokument23 SeitenSangre BiotecnologiaAbdowlaye Smith CampoNoch keine Bewertungen

- Taller 3 de AnalisisDokument2 SeitenTaller 3 de AnalisisAbdowlaye Smith CampoNoch keine Bewertungen

- Problemas Morales Del AncianoDokument14 SeitenProblemas Morales Del AncianoAbdowlaye Smith CampoNoch keine Bewertungen

- PFIZERDokument18 SeitenPFIZERAbdowlaye Smith CampoNoch keine Bewertungen

- El Hombre Mediocre ResumenDokument18 SeitenEl Hombre Mediocre Resumenmariarouse830% (1)

- Empleos Marzo Industriales de EcatepecDokument24 SeitenEmpleos Marzo Industriales de EcatepecHector Eduardo Gutierrez CureñoNoch keine Bewertungen

- Brochure Seguridad Higiene y AmbienteDokument8 SeitenBrochure Seguridad Higiene y AmbienteArnaldo J Brito ÑNoch keine Bewertungen

- Propósitos de La EnseñanzaDokument1 SeitePropósitos de La EnseñanzaClauNoch keine Bewertungen

- Laboratorio n6 Fuerzas ConcurrentesDokument11 SeitenLaboratorio n6 Fuerzas ConcurrentesHugo Palacios100% (1)

- Disciplina en El Trabajo. Actividad 1Dokument5 SeitenDisciplina en El Trabajo. Actividad 1Anonymous dLpwiH60% (5)

- La Enciclopedia de Las Baterías para Móviles - Reader ViewDokument3 SeitenLa Enciclopedia de Las Baterías para Móviles - Reader ViewLuis Utrilla del CastilloNoch keine Bewertungen

- El Porque Del NodularDokument8 SeitenEl Porque Del NodularAdrian GustavoNoch keine Bewertungen

- Actividad 5 Preguntas y RespeustasDokument4 SeitenActividad 5 Preguntas y RespeustasMonica Marcela AArcosNoch keine Bewertungen

- Experimento de Metabolismo VegetalDokument2 SeitenExperimento de Metabolismo VegetalLiyiPaternina100% (1)

- ProcedimientosDokument2 SeitenProcedimientosroberto martinezNoch keine Bewertungen

- Estudio de Impacto Ambiental Del Proyecto Zona Sur Del Corredor Segregado de Alta CapacidadDokument3 SeitenEstudio de Impacto Ambiental Del Proyecto Zona Sur Del Corredor Segregado de Alta Capacidadgloria nina montielNoch keine Bewertungen

- Energia GeotermicaDokument23 SeitenEnergia GeotermicaJose GomezNoch keine Bewertungen

- Pregunta 02 - Presiones Gravedad y BoquillaDokument2 SeitenPregunta 02 - Presiones Gravedad y BoquillaYENNS VLADIMIR RODRIGUEZ RUIZNoch keine Bewertungen

- Reglamento BibliotecaDokument3 SeitenReglamento BibliotecaBraian FlorianNoch keine Bewertungen

- G-Scan Scope Septiembre Trade inDokument2 SeitenG-Scan Scope Septiembre Trade inOscar SotoNoch keine Bewertungen

- Proyecto TV Corporativa MiunicipalDokument4 SeitenProyecto TV Corporativa MiunicipalCarlos GutierrezNoch keine Bewertungen

- Estructura CMDokument1 SeiteEstructura CMMario Ivan GudiñoNoch keine Bewertungen

- Manual de TC PDFDokument14 SeitenManual de TC PDFch4rli75% (4)

- Tesis600 PDFDokument276 SeitenTesis600 PDFyampiherNoch keine Bewertungen

- Cal CuloDokument143 SeitenCal CuloPatricio Toaquiza ChiguanoNoch keine Bewertungen

- Tasacion de Predio Calle Alto Lima #1286Dokument5 SeitenTasacion de Predio Calle Alto Lima #1286Cesar QANoch keine Bewertungen

- NTP Iso 4427 1 PDFDokument22 SeitenNTP Iso 4427 1 PDFnais311Noch keine Bewertungen

- 01 Captacion LaderaDokument30 Seiten01 Captacion LaderaLorena Dueñas SotoNoch keine Bewertungen

- Práctica de Laboratorio MANTENIMIENTO I EmbraguesDokument3 SeitenPráctica de Laboratorio MANTENIMIENTO I EmbraguesStevRocha0% (1)

- Terminos de InnovacionDokument9 SeitenTerminos de InnovacionJoshua BoucherNoch keine Bewertungen

- Eric Hobsbawm. Un Tiempo de Rupturas. Sociedad y Cultura en El Siglo Xx. Barcelona: Crítica, 2013.Dokument4 SeitenEric Hobsbawm. Un Tiempo de Rupturas. Sociedad y Cultura en El Siglo Xx. Barcelona: Crítica, 2013.jorgeelofNoch keine Bewertungen

- Surichaqui LinealDokument21 SeitenSurichaqui LinealLeonardo ManuelNoch keine Bewertungen

- Todo Gases Ideales. Leyes de Boyle Charles Gay LussacDokument7 SeitenTodo Gases Ideales. Leyes de Boyle Charles Gay LussacNatalia Vanesa GuardiaNoch keine Bewertungen

- Informe Compresion Paralela en La MaderaDokument12 SeitenInforme Compresion Paralela en La MaderaLISETH PINEDANoch keine Bewertungen