Beruflich Dokumente

Kultur Dokumente

74VHC175

Hochgeladen von

Alexandre S. CorrêaOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

74VHC175

Hochgeladen von

Alexandre S. CorrêaCopyright:

Verfügbare Formate

74VHC175 Quad D-Type Flip-Flop

August 1993 Revised April 1999

74VHC175 Quad D-Type Flip-Flop

General Description

The VHC175 is an advanced high-speed CMOS device fabricated with silicon gate CMOS technology. It achieves the high-speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation. The VHC175 is a high-speed quad D-type flip-flop. The device is useful for general flip-flop requirements where clock and clear inputs are common. The information on the D inputs is stored during the LOW-to-HIGH clock transition. Both true and complemented outputs of each flip-flop are provided. A Master Reset input resets all flip-flops, independent of the Clock or D inputs, when LOW. An input protection circuit insures that 0V to 7V can be applied to the input pins without regard to the supply voltage. This device can be used to interface 5V to 3V systems and two supply systems such as battery backup. This circuit prevents device destruction due to mismatched supply and input voltages.

Features

s High Speed: fMAX = 210 MHz (typ) at VCC = 5V s Low power dissipation: ICC = 4 A (max) at TA = 25C s High noise immunity: VNIH = VNIL = 28% VCC (min) s Power down protection is provided on all inputs s Low noise: VOLP = 0.8V (max) s Pin and function compatible with 74HC175

Ordering Code:

Order Number 74VHC175M 74VHC175SJ 74VHC175MTC 74VHC175N Package Number M16A M16D MTC16 N16E Package Description 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Surface mount packages are also available on Tape and Reel. Specify by appending the suffix letter X to the ordering code.

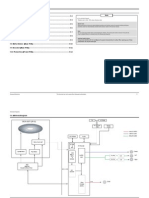

Connection Diagram

Pin Descriptions

Pin Names D0D3 CP MR Q0Q3 Q0Q 3 Description Data Inputs Clock Pulse Input Master Reset Input True Outputs Complement Outputs

Logic Symbols

IEEE/IEC

1999 Fairchild Semiconductor Corporation

DS011637.prf

www.fairchildsemi.com

74VHC175

Functional Description

The VHC175 consists of four edge-triggered D flip-flops with individual D inputs and Q and Q outputs. The Clock and Master Reset are common. The four flip-flops will store the state of their individual D inputs on the LOW-to-HIGH clock (CP) transition, causing individual Q and Q outputs to follow. A LOW input on the Master Reset (MR) will force all Q outputs LOW and Q outputs HIGH independent of Clock or Data inputs. The VHC175 is useful for general logic applications where a common Master Reset and Clock are acceptable.

Truth Table

Inputs @ tn, MR = H Dn L H

H = HIGH Voltage Level L = LOW Voltage Level tn = Bit Time before Clock Pulse tn+1 = Bit Time after Clock Pulse

Outputs @ tn+1 Qn L H Qn H L

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.fairchildsemi.com

74VHC175

Absolute Maximum Ratings(Note 1)

Supply Voltage (VCC) DC Input Voltage (VIN) DC Output Voltage (VOUT) Input Diode Current (IIK) Output Diode Current (IOK) DC Output Current (IOUT) DC VCC /GND Current (ICC ) Storage Temperature (TSTG) Lead Temperature (TL) (Soldering, 10 seconds) 260C 0.5V to +7.0V 0.5V to +7.0V 0.5V to VCC + 0.5V 20 mA 20 mA 25 mA 50 mA 65C to +150C

Recommended Operating Conditions (Note 2)

Supply Voltage (VCC) Input Voltage (VIN) Output Voltage (VOUT) Operating Temperature (TOPR) Input Rise and Fall Time (tr, tf) VCC = 3.3V 0.3V VCC = 5.0V 0.5V 0 100 ns/V 0 20 ns/V 2.0V to +5.5V 0V to +5.5V 0V to VCC 40C to +85C

Note 1: Absolute Maximum Ratings are values beyond which the device may be damaged or have its useful life impaired. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation outside databook specifications. Note 2: Unused inputs must be held HIGH or LOW. They may not float.

DC Electrical Characteristics

Symbol VIH VIL VOH Parameter HIGH Level Input Voltage LOW Level Input Voltage HIGH Level Output Voltage VCC (V) 2.0 3.0 5.5 2.0 3.0 5.5 2.0 3.0 4.5 3.0 4.5 VOL LOW Level Output Voltage 2.0 3.0 4.5 3.0 4.5 IIN ICC Input Leakage Current Quiescent Supply Current 0 5.5 5.5 1.9 2.9 4.4 2.58 3.94 0.0 0.0 0.0 0.1 0.1 0.1 0.36 0.36 0.1 4.0 2.0 3.0 4.5 TA = 25C Min 1.50 0.7 VCC 0.50 0.3 VCC 1.9 2.9 4.4 2.48 3.80 0.1 0.1 0.1 0.44 0.44 1.0 40.0 V A A IOL = 4 mA IOL = 8 mA VIN = 5.5V or GND VIN = VCC or GND V V VIN = VIH or VIL IOH = 4 mA IOH = 8 mA IOL = 50 A V Typ Max TA = 40C to +85C Min 1.50 0.7 VCC 0.50 0.3 VCC Max Units V V VIN = VIH or VIL IOH = 50 A Conditions

Noise Characteristics

Symbol VOLP (Note 3) VOLV (Note 3) VIHD (Note 3) VILD (Note 3) Parameter Quiet Output Maximum Dynamic VOL Quiet Output Minimum Dynamic VOL Minimum HIGH Level Dynamic Input Voltage Maximum LOW Level Dynamic Input Voltage VCC (V) 5.0 5.0 5.0 5.0 TA = 25C Typ 0.4 0.4 Limits 0.8 0.8 3.5 1.5 Units V V V V CL = 50 pF CL = 50 pF CL = 50 pF CL = 50 pF Conditions

Note 3: Parameter guaranteed by design.

www.fairchildsemi.com

74VHC175

AC Electrical Characteristics

Symbol fMAX Parameter Maximum Clock Frequency 5.0 0.5 tPLH tPHL Propagation Delay Time (CP to Qn or Qn) 5.0 0.5 tPLH tPHL Propagation Delay Time (MR to Qn or Qn) 5.0 0.5 tOSLH tOSHL Output to Output Skew 5.0 0.5 CIN CPD Input Capacitance Power Dissipation Capacitance

Note 4: Parameter guaranteed by design. tOSLH = |tPLHmax tPLHmin|; tOSHL =| tPHLmax tPHLmin|. Note 5: CPD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained from the equation: ICC (opr.) = CPD * VCC * fIN + ICC/4 (per F/F), and the total CPD when n pcs of the Flip-Flop operate can be calculated by the following equation: CPD (total) = 30 + 14 n

VCC (V) 3.3 0.3

TA = 25C Min 90 50 150 85 Typ 140 75 210 115 7.5 10.0 4.8 6.3 6.3 8.8 4.3 5.8 11.5 15.0 7.3 9.3 10.1 13.6 6.4 8.4 1.5 1.0 4 44 10 Max

TA = 40C to +85C Min 75 45 125 75 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 13.5 17.0 8.5 10.5 12.0 15.5 7.5 9.5 1.5 1.0 10 Max

Units MHz MHz ns ns ns ns

Conditions CL = 15 pF CL = 50 pF CL = 15 pF CL = 50 pF CL = 15 pF CL = 50 pF CL = 15 pF CL = 50 pF CL = 15 pF CL = 50 pF CL = 15 pF CL = 50 pF CL = 50 pF CL = 50 pF (Note 4)

3.3 0.3

3.3 0.3

3.3 0.3

pF pF

VCC = Open (Note 5)

AC Operating Requirements

Symbol tW(L) tW(H) tW(L) tS tH tREC Minimum Pulse Width (MR) Minimum Setup Time (Dn to CP) Minimum Hold Time (Dn to CP) Parameter Minimum Pulse Width (CP) VCC (V) (Note 6) 3.3 5.0 3.3 5.0 3.3 5.0 3.3 5.0 Minimum Removal Time (MR) 3.3 5.0

Note 6: VCC is 3.3 0.3V or 5.0 0.5V

TA = 25C Typ

TA = 40C to +85C Guaranteed Minimum 5.0 5.0 5.0 5.0 5.0 4.0 1.0 1.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 4.0 1.0 1.0 5.0 5.0 Units

ns ns ns ns ns

www.fairchildsemi.com

74VHC175

Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow Package Number M16A

16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide Package Number M16D

www.fairchildsemi.com

74VHC175

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC16

www.fairchildsemi.com

74VHC175 Quad D-Type Flip-Flop

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N16E

LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 2. A critical component in any component of a life support 1. Life support devices or systems are devices or systems device or system whose failure to perform can be reawhich, (a) are intended for surgical implant into the sonably expected to cause the failure of the life support body, or (b) support or sustain life, and (c) whose failure device or system, or to affect its safety or effectiveness. to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the www.fairchildsemi.com user.

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

Das könnte Ihnen auch gefallen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Optical Comp Exp - Edu SilvaDokument6 SeitenOptical Comp Exp - Edu SilvaAlexandre S. CorrêaNoch keine Bewertungen

- F e A T U R e SDokument2 SeitenF e A T U R e SAlexandre S. CorrêaNoch keine Bewertungen

- Vistabule 2014 Feb Brochure LRDokument10 SeitenVistabule 2014 Feb Brochure LRAlexandre S. CorrêaNoch keine Bewertungen

- Modular CNC Router 2009v1 FREE PLANSDokument10 SeitenModular CNC Router 2009v1 FREE PLANSModularCNC57% (7)

- The UltralightDokument20 SeitenThe UltralightAlexandre S. Corrêa100% (2)

- Manual Transistor PDFDokument4 SeitenManual Transistor PDFAlexandre S. CorrêaNoch keine Bewertungen

- Manual 2016 Nitro g5Dokument2 SeitenManual 2016 Nitro g5Alexandre S. CorrêaNoch keine Bewertungen

- Build "Wild Goose": A Sturdy Overnight TrailerDokument7 SeitenBuild "Wild Goose": A Sturdy Overnight TrailerAlexandre S. CorrêaNoch keine Bewertungen

- Schematic Diagrams: Special NoteDokument12 SeitenSchematic Diagrams: Special NoteAlexandre S. Corrêa100% (1)

- Sansung CL21A551MLDokument9 SeitenSansung CL21A551MLleno2Noch keine Bewertungen

- 1947 Trailer For TwoDokument7 Seiten1947 Trailer For TwoAlexandre S. CorrêaNoch keine Bewertungen

- CCE TV HPS-2071B Diagrama EsquematicoDokument1 SeiteCCE TV HPS-2071B Diagrama EsquematicoDaniel AvecillaNoch keine Bewertungen

- 4HD D0049.0611 - 06FDokument104 Seiten4HD D0049.0611 - 06FCarlosLimaNoch keine Bewertungen

- Yamaha Receiver Rxv-595 SchematicDokument7 SeitenYamaha Receiver Rxv-595 SchematicMauricio Bumba100% (1)

- Datasheet 7400Dokument9 SeitenDatasheet 7400gab50Noch keine Bewertungen

- Schematic Diagram DVD-P370Dokument8 SeitenSchematic Diagram DVD-P370Alexandre S. Corrêa0% (1)

- Cold Cold HOT HOT: QFP80 QFP80Dokument1 SeiteCold Cold HOT HOT: QFP80 QFP80Jone Ferreira Dos SantosNoch keine Bewertungen

- 74573Dokument4 Seiten74573jamesrychurdNoch keine Bewertungen

- Build Your Own VAWT by David MussellDokument17 SeitenBuild Your Own VAWT by David MussellMr Void100% (9)

- XR-A550 XR-A330: Stereo CD Cassette Deck ReceiverDokument82 SeitenXR-A550 XR-A330: Stereo CD Cassette Deck ReceiverAlexandre S. CorrêaNoch keine Bewertungen

- 74574Dokument6 Seiten74574Alexandre S. CorrêaNoch keine Bewertungen

- Tip41-2 20wDokument3 SeitenTip41-2 20wAlexandre S. CorrêaNoch keine Bewertungen

- 74688Dokument4 Seiten74688Alexandre S. CorrêaNoch keine Bewertungen

- TL 074Dokument10 SeitenTL 074Alexandre S. CorrêaNoch keine Bewertungen

- ICL7106 and ICL7107 VoltmeterDokument16 SeitenICL7106 and ICL7107 VoltmeterAntonino ScordatoNoch keine Bewertungen

- 802Dokument4 Seiten802BooksNoch keine Bewertungen

- Ta 8403 KDokument5 SeitenTa 8403 KFlorenz RemasteredNoch keine Bewertungen

- TDA2002 10wDokument21 SeitenTDA2002 10wAlexandre S. CorrêaNoch keine Bewertungen

- DC Da90Dokument24 SeitenDC Da90Alexandre S. CorrêaNoch keine Bewertungen

- 74VHCU04Dokument6 Seiten74VHCU04Alexandre S. CorrêaNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Price List Ciaz AccessoriesDokument4 SeitenPrice List Ciaz AccessoriesAsif RazviNoch keine Bewertungen

- Cbseskilleducation Com Digital Presentation Class 9Dokument11 SeitenCbseskilleducation Com Digital Presentation Class 9riscomputersirNoch keine Bewertungen

- Tower BridgeDokument6 SeitenTower BridgeCalvin PratamaNoch keine Bewertungen

- SD HospitalDokument2 SeitenSD HospitalSam PowelNoch keine Bewertungen

- 3 Filtration Lecture NotesDokument16 Seiten3 Filtration Lecture NotesRuben SIbayanNoch keine Bewertungen

- Art Research Paper OutlineDokument8 SeitenArt Research Paper Outlinefyr90d7m100% (1)

- 5 GR No. 93468 December 29, 1994 NATU Vs TorresDokument9 Seiten5 GR No. 93468 December 29, 1994 NATU Vs Torresrodolfoverdidajr100% (1)

- Economics: PAPER 1 Multiple ChoiceDokument12 SeitenEconomics: PAPER 1 Multiple ChoiceigcsepapersNoch keine Bewertungen

- Raghad Kamel's ResumeDokument7 SeitenRaghad Kamel's ResumeMostafa Mohamed GamalNoch keine Bewertungen

- ION Architecture & ION ModulesDokument512 SeitenION Architecture & ION ModulesAhmed RabaaNoch keine Bewertungen

- 21S18052 - Joshua Partogi Hutauruk - Review BUSNOV - Umbrella - WarsDokument5 Seiten21S18052 - Joshua Partogi Hutauruk - Review BUSNOV - Umbrella - WarsJoshua HutaurukNoch keine Bewertungen

- El Condor1 Reporte ECP 070506Dokument2 SeitenEl Condor1 Reporte ECP 070506pechan07Noch keine Bewertungen

- 2008 Almocera vs. OngDokument11 Seiten2008 Almocera vs. OngErika C. DizonNoch keine Bewertungen

- METHODOLOG1Dokument3 SeitenMETHODOLOG1Essa M RoshanNoch keine Bewertungen

- Case Studies Public LibraryDokument4 SeitenCase Studies Public LibraryHimalya Kaim83% (6)

- Intermediate Course Study Material: TaxationDokument34 SeitenIntermediate Course Study Material: TaxationMd IbrarNoch keine Bewertungen

- Property DigestDokument9 SeitenProperty DigestJoy OrenaNoch keine Bewertungen

- Introduction To SCILABDokument14 SeitenIntroduction To SCILABMertwysef DevrajNoch keine Bewertungen

- User Mode I. System Support Processes: de Leon - Dolliente - Gayeta - Rondilla It201 - Platform Technology - TPDokument6 SeitenUser Mode I. System Support Processes: de Leon - Dolliente - Gayeta - Rondilla It201 - Platform Technology - TPCariza DollienteNoch keine Bewertungen

- HD785-7 Fault Codes SEN05900-01-3Dokument16 SeitenHD785-7 Fault Codes SEN05900-01-3ISRAEL GONZALESNoch keine Bewertungen

- Literature Review On Climate Change in NigeriaDokument9 SeitenLiterature Review On Climate Change in Nigeriac5rn3sbr100% (1)

- Java 9 Real - TimeDokument57 SeitenJava 9 Real - TimeDiego AmayaNoch keine Bewertungen

- CHR Report 2017 IP Nat InquiryDokument30 SeitenCHR Report 2017 IP Nat InquiryLeo Archival ImperialNoch keine Bewertungen

- Appointments & Other Personnel Actions Submission, Approval/Disapproval of AppointmentDokument7 SeitenAppointments & Other Personnel Actions Submission, Approval/Disapproval of AppointmentZiiee BudionganNoch keine Bewertungen

- Periodical Increment CertificateDokument1 SeitePeriodical Increment CertificateMD.khalil100% (1)

- Penn State: The Dickinson School of LawDokument88 SeitenPenn State: The Dickinson School of LawHafiz UmmarNoch keine Bewertungen

- Hullabaloo (TV Series)Dokument3 SeitenHullabaloo (TV Series)ozNoch keine Bewertungen

- 04 Handout 1 (Midterms)Dokument14 Seiten04 Handout 1 (Midterms)Emmanuel DelarosaNoch keine Bewertungen

- Vande Bharat Exp Chair Car (CC) : Electronic Reserva On Slip (ERS)Dokument2 SeitenVande Bharat Exp Chair Car (CC) : Electronic Reserva On Slip (ERS)Subhash KumarNoch keine Bewertungen

- Case Study 1 - Signal Cable CompanyDokument5 SeitenCase Study 1 - Signal Cable CompanyTengku SuriaNoch keine Bewertungen