Beruflich Dokumente

Kultur Dokumente

Plecs Tl431

Hochgeladen von

khsniperCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Plecs Tl431

Hochgeladen von

khsniperCopyright:

Verfügbare Formate

Design of a TL431-Based Controller

for a Flyback Converter

Dr. John Schnberger

Plexim GmbH

Technoparkstrasse 1

8005 Zrich

1 Introduction

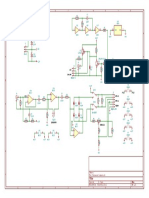

The TL431 is a reference voltage source that is commonly used in the control circuit of isolated power

supplies. Typically used to provide a precision reference voltage, the TL431 can also be congured as an

analog controller by exploiting its on-board error amplier. In this report, the design of a TL431-based

voltage controller for a yback converter is presented. The example circuit is shown in Fig. 1.

Lm

L: 9.4e-3

C: 330e-6

C: 330e-6

RL2

R: 15

RL3

R: 15

C: 470e-6 RL1

R: 1

Rs

R: 0.5 V

Vdc

V: 300

Cz

RIed

Rc1

R1

R2

Cp

TL431

0V

0V

5V

5V

Opto1

UCC38C4x

current mode

pwm controIIer

COMP OUT

CS

V

R

E

F

CND

Rc2

0V

RbIas

+12V

-12V

Vc

Vo

Fig. 1: Schematic of current-controlled yback converter with a TL431 congured as a type 2 voltage controller.

The yback converter comprises two control loops. The inner current control loop, based on peak current

mode control, is realized using a UCC38C4x current-controlled PWMmodulator. The outer voltage control

loop is a type 2 controller, which is commonly used in power supply voltage control loops. The voltage

control circuit regulates the output voltage of the 5 V winding and includes an optocoupler to maintain

isolation between the input and output stages.

The voltage controller must regulate the measured 5 V output voltage over a range of loading conditions

on the 12 V windings, which induce voltage deviations on the 5 V winding. The load resistances on the

12 V windings vary between 15 and 7.5 . The starting point for the voltage controller design is the

calculation of the converters open-loop transfer function,

V

o

(s)

V

c

(s)

, which is depicted as a Bode plot. The type

2 controller is then designed in the frequency domain to ensure that it provides a sufciently fast and

stable closed-loop transient response.

ver 12-11

Design of a TL431 controller using PLECS

R1

R2

Rs

0V

VreI

V1 Vo

A

K

Fig. 2: Use of the TL431 to generate an arbitrary reference voltage.

In this report, an example design and verication procedure for a TL431-based type 2 voltage controller

is presented. PLECS small-signal analysis tools are employed to calculate the open and closed-loop Bode

plots of the system. Example models accompany this report to illustrate the use of the PLECS small-

signal analysis tools and to demonstrate the operation of the complete system. These models can be found

in the archive Flyback_tl431.zip.

2 The TL431

2.1 The TL431 regulator

The TL431 is an adjustable shunt regulator that can be congured to provide an arbitrary reference

voltage as shown in Fig. 2. The output voltage can be set to any value between V

ref

and 36 V using two

external resistors. The output voltage is given by

V

o

= V

ref

1 +

R

1

R

2

(1)

where V

ref

is the onboard 2.5 V reference voltage source.

2.2 The TL431 type 2 error amplier

Although the TL431 is commonly used as an adjustable voltage reference source, its onboard error am-

plier can be congured as an op-amp, allowing it to be used for both voltage reference and control ap-

plications. The 1 MHz unity-gain bandwidth of its error amplier is more than adequate for most power

supply voltage control loops.

The frequency response of a type 2 controller is depicted as a Bode plot in Fig. 3. At low frequencies, the

type 2 controller is similar to a PI controller, having a pole at 0

due to the integral action, and a zero

at

z

due to the proportional action. However, the type 2 controller includes a high frequency pole at

p

,

which is used to mitigate the switching ripple. The transfer function of a type 2 controller is given as

follows:

C(s) = k

p

1 +s

s

1

1 +sT

(2)

= k

p

1 +s

s

2

T +s

(3)

It can be seen from Fig. 3 that the type 2 controller is characterized by three parameters: the gain, A

v

,

the zero frequency,

z

, and the pole frequency,

p

. These parameters are used to calculate the terms in

the transfer function as follows:

k

p

= 10

A

v

20

(4)

J. Schnberger, Plexim GmbH 2

Design of a TL431 controller using PLECS

Fig. 3: Bode plot of type 2 controller.

=

1

z

(5)

T =

1

p

(6)

The TL431 is shown congured as a type 2 controller in Fig. 4. The controller circuit, shown in Fig.

4(a), includes an optocoupler to provide isolated feedback. A single pullup resistor or a resistive divider

comprising R

c1

, R

c2

can be used to generate the control voltage, V

c

. A resistive divider allows a maximum

limit for V

c

to be set, which is useful for limiting the startup current. The equivalent small-signal collector

resistance, R

c

, is equivalent to R

c1

||R

c2

.

The block diagram of the complete system is shown in Fig. 4(b). It can be seen that the TL431 control

circuit includes a reference voltage source and summer in addition to the type 2 controller, C(s).

In the TL431-based type 2 control circuit, the proportional gain is given by

k

p

= CTR

R

c

R

led

(7)

where CTR is the current transfer ratio of the optocoupler and R

c

is the effective small-signal collector

resistance that is formed from the parallel combination of R

c1

and R

c2

. The pull-down resistor R

c2

is

optional. If included, it limits the peak control voltage, in turn limiting the peak MOSFET current.

The low frequency pole is set by the components R

1

, C

1

:

z

=

1

R

1

C

1

(8)

The high frequency pole is set by the components R

c

, C

p

:

p

=

1

R

c

C

p

(9)

It is assummed that C

p

is much larger than C

opto

, the output capacitance of the optocoupler.

3 IC modeling

Three ICs are included in the yback converter model: the TL431 reference voltage source, the UCC38C4x

current mode controller and the optocoupler. These are modeled in PLECS using simplied behavioral

models.

J. Schnberger, Plexim GmbH 3

Design of a TL431 controller using PLECS

Cz

RIed

Rc2

V

R1

R2

Opto1

TL431

Cp

Vcc

Vo

0V

Rc1

Vc

(a) Controller circuit with optocoupler for feedback loop isolation.

+

-

C(s) G(s)

TL431 controer

Vref Vo

Vc err

Converter

(b) System block diagram.

Fig. 4: The TL431 congured as an isolated type 2 controller.

(a) small-signal voltage gain.

+

-

2.5V

VI: 2.5

VreI

K

A

(b) PLECS implementation.

Fig. 5: TL431 model.

3.1 TL431 model

A practical TL431 contains an error amplier and a 2.5 V reference voltage source [1]. The PLECS model

of the TL431 is shown in Fig. 5. The small-signal voltage gain is approximated using a rst-order low-

pass lter with a gain of 750 (57.5 dB) and a cutoff frequency of 2.5 kHz. The Bode plot of the small-signal

voltage gain of the error amplier is shown in Fig. 5(a). It can be seen that the unity-gain frequency is

approximately 2 MHz.

It should be noted that the unity-gain frequency of the practical TL431 component is 1 MHz because the

practical component does not have a true rst-order characteristic. However, this difference has negligible

impact on the system model, since the cutoff frequency of the control system is approximately three orders

of magnitude lower than the unity gain frequency of the TL431.

The cathode current vs. voltage characteristic of the TL431 has an offset of 2.5V since the minimum

cathode voltage that can be generated is equal to the reference voltage. The cathode offset voltage is

modeled in PLECS using an ideal diode as shown in Fig. 5(b). Due to use of the ideal diode, the offset

voltage is 2.5V, even at zero current. In a practical TL431, the cathode offset voltage is not guaranteed to

be 2.5 V unless the cathode current is 1 mA. Therefore the TL431 should be correctly biased to ensure the

validity of the model.

J. Schnberger, Plexim GmbH 4

Design of a TL431 controller using PLECS

V 1]3

R]2R

v. dIvIder

VI: 1.15 COMP

Zener cIamp

UpperLImIt: 1

Peak Current

ControIIer

sense

reI

s

OUT

CS

V: 5

VREF

CND

(a) Simplied behavioral model.

2R

R Vz: 1.0

COMP reI

(b) Actual current reference offset and scaling

circuit.

Fig. 6: PLECS model of the UCC38C4x current-mode control IC.

A

c

A

K e

c VI: VIed

C1

C: Cvce

ctr V I(u)

LImIt

Ied

Fig. 7: PLECS optocoupler model.

3.2 UCC38C4x current-mode control IC model

The current controller model is based on the UCC38C4x series of current-mode PWM contol ICs [2]. In-

ternally, the UCC38C4x modulator consists of a peak current mode controller, oscillator, error amplier,

reference voltage generator, undervoltage lockout logic and current offset and scaling circuit. The simpli-

ed behavioral model of the UCC38C4x is shown in Fig. 6.

As seen in Fig. 6(a), the simplied behavioral model contains only those features that directly inuence

the operation of the control circuit and converter. These features are the peak current mode controller,

current offset and scaling circuit and the 5 V reference voltage. The onboard error amplier is not modeled

since the control voltage is supplied by the external type 2 control circuit.

The actual current reference offset and scaling circuit found between the COMP pin and I

ref

input of the

peak current controller is shown in Fig. 6(b). The current sense circuit comprises a voltage drop of 1.15 V

and a resistive voltage divider. The peak MOSFET current is therefore expressed as:

I

sw

=

max(V

c

1.15, 0)

3R

s

(10)

where R

s

is the current sense resistor that is connected in series with the MOSFET.

3.3 Optocoupler model

The optocoupler is modeled using a controlled current source as shown in Fig. 7. In the linear operating

region, the collecter current is given by I

c

= CTR I

led

. In the saturation region, a limit is imposed on

the CTR to prevent the collector voltage from becoming negative. A small capacitor that represents the

collecter-emitter capacitance is included in the model to prevent an algebraic loop from being formed.

It should be noted that in the PLECS optocoupler model, the CTR is assumed to be constant for simplicity.

In a practical optocoupler, the CTR varies with the forward LED current, temperature, age and even

between different production batches. Therefore the control circuit should be designed and tested for the

lowest and highest expected values for the CTR.

J. Schnberger, Plexim GmbH 5

Design of a TL431 controller using PLECS

Table 1: Steady-state control voltage required to generate 5 V

Load resistance (12 V winding) V

c

15 1.96

7.5 2.22

4 Designing the Controller

4.1 Converter open-loop transfer function

The rst step in the design process is to obtain the open-loop transfer function of the converter. The

voltage controller is then designed such that the closed-loop response of the system meets a specied

bandwidth.

The transfer function of the open-loop system, G(s) =

V

o

(s)

V

c

(s)

, is found by adding a perturbation signal to

the control signal, V

c

, and measuring the response of the output voltage, V

o

. In PLECS two tools can be

used for calculating the open-loop transfer function: the ac sweep tool and the impulse response analysis

tool. The impulse response analysis tool is much faster than the ac sweep tool for calculating the open-

loop transfer function since it applies a single impulse perturbation rather than a series of sinusoidal

perturbations.

Before the impulse response analysis can be run, the control voltage required to generate a 5 V output

voltage at nominal load must be found because the small-signal analysis is executed by perturbing the

steady-state operating point. The nominal steady-state control voltage can easily be determined by ad-

justing the control voltage in an open-loop simulation model until the desired output voltage is attained.

Assuming the nominal load is the minimum loading condition, with 15 resistors on the 12 V windings

and 1 on the 5 V winding, the control voltage was found to be 1.96 V. The control voltages for the

minimum and maximum loading conditions are given in Table 1. With the control voltage set to this

value, the impulse response analysis was run, generating the Bode plot shown in Fig. 8. It can be seen

that the current controlled converter exhibits rst order characteristic up to 1 kHz.

Note To congure the impulse response analysis tool, a small-signal perturbation component must be

placed in series with the constant control voltage signal. A small-signal response component must also be

connected to the output voltage. In the setup parameters, the system period should be set to 1/f

s

, where

f

s

is the switching frequency. Several initialization cycles should be entered in the setup parameters to

help the steady-state analysis converge before the impulse response analysis is run. Once the impulse

response analysis has run, the Bode plot should be saved to a csv le for subsequent calculation of the

closed-loop gain.

4.2 Controller specications

The controller specications for a type 2 controller can be given in terms of k

p

, f

z

, f

p

. Using these spec-

ications and the open-loop converter Bode plot, the type 2 transfer function can be calculated and the

controller designed. The controller design presented in this section is not the only possible design solution.

It is merely one design that provides a fast transient response and stable closed-loop system.

The proportional gain, k

p

, is determined by calculating the midband voltage gain the type 2 controller

must provide in order to set the cutoff frequency of the closed-loop system to a specic value. The cutoff

frequency, f

c

, is chosen to be 800 Hz to provide a fast response to voltage perturbations. It also allows k

p

to meet the minimum gain criterion, which is explained in Section 4.5.

It can be seen from the magnitude plot in Fig. 8 that the controller must provide 3 dB of gain at f

c

to

bring the magnitude response to 0 dB, or unity gain. Using Eq. (4), k

p

is calculated to be 1.4.

The zero frequency, f

z

is chosen to be 100 Hz in order to cancel the low frequency pole of the converter.

The controller pole frequency, f

p

, is chosen to be 5 kHz to provide good attenuation of the switching ripple.

J. Schnberger, Plexim GmbH 6

Design of a TL431 controller using PLECS

Magnitude

Phase

M

a

g

n

i

t

u

d

e

/

d

B

-20

-10

0

10

20

Frequency / Hz

10 100 1000 10000

P

h

a

s

e

/

-140

-120

-100

-80

-60

-40

-20

0

Fig. 8: Bode plot of open-loop converter transfer function, G(s) =

V

o

(s)

V

c

(s)

.

4.3 Controller design

1. The rst step in designing the control circuit is to set the reference voltage to 5 V. Using Eq. (1) and

selecting the bias current in the resistive divider to 0.25 mA, resistors R

1

and R

2

were calculated to

be 10 k.

2. The TL431 must have a minimum bias current of 1 mA in order to provide its stated reference volt-

age of 2.5 V [1]. The resistor R

led

is calculated to provide a maximum bias current, I

led max

, for the

TL431 of 2 mA. The maximum bias current occurs when V

k

, the cathode-anode voltage of the TL431

is at its minimum value of 2.5 V. This allows the calculation of R

led

as follows:

R

led

=

V

o

V

led

V

k min

I

k

= 725

3. Using Eq. (7), the small-signal collector resistor resistance, R

c

, is calculated to achieve the required

k

p

:

R

c

=

k

p

R

led

CTR

= 812

R

c

is chosen to be 800 and is implemented by setting R

c1

= R

c2

= 1600. Since V

ref

in the

UCC38C4x is 5 V, the peak control voltage is limited to 2.5 V and the peak MOSFET current is

limited to 0.9 A in accordance with Eq. (10).

4. C

z

is calculated from Eq. (8) to set the zero frequency, f

z

:

C

z

=

1

2f

z

R

1

= 159nF

5. C

p

is calculated from Eq. (9) to set the pole frequency, f

p

:

C

p

=

1

2f

p

R

c

= 40nF

J. Schnberger, Plexim GmbH 7

Design of a TL431 controller using PLECS

Magnitude

Phase

M

a

g

n

i

t

u

d

e

/

d

B

-5

0

5

10

15

20

25

Frequency / Hz

10 100 1000 10000

P

h

a

s

e

/

-80

-60

-40

-20

Fig. 9: Frequency response of type 2 controller.

6. To verify the controller design, an ac sweep was performed on an open-loop model of the controller.

The resultant Bode plot is shown in Fig. 9. The frequency response was saved to a csv le for

calculation of the closed-loop gain as described in Section 4.6.

4.4 Verify the controller biasing

Although the design procedure given in Section 4.3 sets the type 2 controller parameters, k

p

, f

z

, f

p

,

correctly, the bias currents in the type 2 control circuit must be checked to ensure that the minimum

required control voltage can be generated and that sufcient cathode current ows in the TL431. For the

circuit shown in Fig. 4(a), the bias currents I

led

and I

c

are set by the components R

led

, R

c1

and R

c2

.

At minimum load, sufcient collector current must ow through the optocoupler to pull V

ce

down to V

c min

,

which was measured to be 1.96 V. Peak collector current is generated when maximum current ows

through the optocoupler LED, and maximum LED current is induced when the TL431 supplies its min-

imum output voltage of 2.5 V. The LED current at minimum TL431 output voltage was set to be 2 mA

in Step 2 of Section 4.3. Therefore if the LED current required to generate V

c min

is less than 2 mA, the

minimum control voltage requirement is satised.

I

led

=

V

ref

2V

c min

2R

c

CTR

= 0.14 mA (11)

Therefore the minimum control voltage can be generated. If the required LED current is larger than

I

led max

, the cathode voltage of the TL431 would have to decrease below 2.5 V, which is not possible.

The cathode current in the TL431, equivalent to I

led

, should also be veried. The cathode current should

be at least 1 mA to ensure that the reference voltage of 2.5 V is generated. Minimum cathode current ows

at maximum load, when the control voltage is at its largest value. When V

c max

= 2.22 V is substituted

into Eq. (11), it can be seen that the minimum LED current is not fullled. Additional bias current must

therefore be added to the cathode current. This can be achieved by connecting a resistor between V

o

and

the cathode of the TL431 or directly across the LED in the optocoupler. A 1 k resistor that is connected

across the optocoupler LED provides an additional 1 mA of cathode bias current for the TL431. This

J. Schnberger, Plexim GmbH 8

Design of a TL431 controller using PLECS

bias resistor does not change the functionality of the TL431 model, since its cathode current vs. voltage

characteristic is ideal. Nevertheless, it should not be overlooked in a practical circuit.

4.5 Minimum gain criterion

The minimum gain criterion exists because for small ratios of

R

c

/R

led

, I

led

must be very large in order to

pull V

c

down to V

c min

. The minimum gain criterion is independent of the resistor values but is dependent

on k

p

and thus the ratio

R

c

/R

led

.

The minimum gain criterion is given as follows:

k

p

0.5

V

cc

V

c min

V

o

V

led

2.5

(12)

assuming that R

c1

= R

c2

. If the pulldown resistor R

c2

is not used, the scale factor of 0.5 is omitted. If

V

cc

= V

o

= 5 V and V

c min

= 1.96 V, the minimum gain criterion for k

p

is 1.05 or 0.44 dB. Referring to Fig.

8, it can be seen that this in turn restricts the minimum closed-loop bandwidth to approximately 600 Hz.

4.6 Calculate loop gain

The TL431 controller acts as a cascade controller, C(s), that is connected in series with the converter,

G(s), as shown in Fig. 4(b). The closed-loop transfer function of the system is given by

H(s) =

C(s)G(s)

1 +C(s)G(s)

(13)

The denominator expression, 1 + C(s)G(s), is known as the characteristic equation. If this term is equal

to zero, the closed-loop response is unstable. It follows that the requirement for stability is

C(s)G(s) 1 (14)

This is known as the Nyquist Stability Criterion. The product of the converter and controller frequency

responses, C(s)G(s), is known as the loop gain. The distance between the loop gain and the unstable -1

point is used as a measure of stability for the closed-loop system.

The closed-loop stability is measured from the loop gain response in terms of gain and phase margin.

The gain margin is the difference between the magnitude response and 0 dB at the frequency where the

loop gain phase is -180

. The phase margin is the difference between the phase response and -180

at the

frequency where the loop gain magnitude response is 0 dB. Generally, the phase margin should be greater

than 45

and the gain margin greater than 10 dB in order to achieve a stable frequency response.

The loop gain can be calculated by adding the magnitude and phase responses of the converter and con-

troller, which are stored in csv les. Example Matlab and Python functions for calculating the loop gain

can be downloaded with this report.

The calculated loop gain for the voltage control loop is depicted in Fig. 10. It can be seen that the cutoff

frequency is equal to its designed value of 800 Hz. The gain margin is 13 dB and the phase margin is 70

,

indicating a stable system.

The loop gain can also be determined using the ac sweep technique. An example le is included with this

report to demonstrate this technique. To speed up the loop gain sweep, the simulation should be run and

the nal operating point saved using Simulation Parameters > Initialization. This speeds up convergence

rate of the steady-state analysis that is performed at the beginning of each ac sweep.

J. Schnberger, Plexim GmbH 9

Design of a TL431 controller using PLECS

Fig. 10: Loop gain of yback converter voltage control loop.

5 Conclusion

The TL431 is a commonly-used reference voltage generator that can also function as an analog controller

in isolated converter control applications. Combining the control function with the voltage reference

generator provides a low-cost controller implementation. The minimum gain limitation of the TL431-

based type 2 controller limits the minimum cutoff frequency of the closed-loop system.

In this report, the design and implementation of a type 2 controller for a yback converter were presented.

Behavioral models of the TL431, optocoupler and current mode control IC were created in PLECS. A

design procedure for the type 2 voltage control circuit, based on the small-signal tools that are integrated

into PLECS, was presented. The Impulse Response Analysis tool was used to calculate the open-loop

frequency response of the converter and the AC sweep tool was used to calculated the open-loop frequency

response of the controller. The frequency responses were added to predict the loop gain. From the loop

gain, the gain and phase margins were measured in order to predict the stability of the closed-loop system.

References

[1] TL431 programmable shunt regulator, www.fairchildsemi.com.

[2] UCC38C4x BiCMOS low power current-mode PWM controller, www.ti.com.

J. Schnberger, Plexim GmbH 10

Design of a TL431 controller using PLECS

Appendices

A Simulation Files - PLECS Standalone

Flyback_openloop_resp.plecs: model in which the Impulse Response Analysis tool is used to obtain

the open-loop frequency response of the current-controlled converter. The result should be manually

saved to csv le.

TL431_controller_sweep.plecs: model in which the AC Sweep tool is used to obtain the frequency

response of the type 2 controller. The result should be manually saved to csv le.

bodeadd_csv.m: calculates the loop gain Bode plot in Matlab by adding the frequency responses of

the converter and controller, which stored in csv les

bodeadd_csv.py: implemention of the above function in the Python programming language.

Flyback_closedloop.plecs: complete model of the yback converter and controller for verifying the

transient response. The closed-loop gain can also be obtained from this model using the AC Sweep

tool.

B Simulation Files - PLECS Blockset

Flyback_openloop_resp.mdl: model in which the Impulse Response Analysis tool is used to obtain

the open-loop frequency response of the current-controlled converter. The result is written to the

MATLAB workspace as a struct.

TL431_controller.mdl: model for which the transfer function of type 2 controller is calculated using

the linmod function. A struct of the frequency response is returned.

bode_type2_controller.m: helper function for calculating the Bode plot of the type 2 control circuit.

plbode.m: helper function for generating Bode plots.

bodeadd.m: calculates the loop gain Bode plot by adding the frequency responses of the converter

and controller, which are stored as structs in the MATLAB workspace.

Flyback_closedloop.mdl: complete model of the yback converter and controller for verifying the

transient response.

J. Schnberger, Plexim GmbH 11

Das könnte Ihnen auch gefallen

- Pulse-Width Modulation Inverters: Pulse-Width Modulation Is The Process of Modifying The Width of The Pulses in A PulseDokument7 SeitenPulse-Width Modulation Inverters: Pulse-Width Modulation Is The Process of Modifying The Width of The Pulses in A PulseEngrAneelKumarAkhani100% (1)

- USB To RS232 Using Atmel ATtiny2313 or ATmega8Dokument4 SeitenUSB To RS232 Using Atmel ATtiny2313 or ATmega8Nugraha Indrawan100% (2)

- H-Bridge: 4.1 DefinitionDokument11 SeitenH-Bridge: 4.1 DefinitionJunaid Iftikhar100% (1)

- The 8051 Microcontroller and Embedded Systems: Motor Control: Relay, PWM, DC and Stepper MotorsDokument51 SeitenThe 8051 Microcontroller and Embedded Systems: Motor Control: Relay, PWM, DC and Stepper MotorsAmAnDeepSingh100% (1)

- PIC+l293d DocumentDokument5 SeitenPIC+l293d Documentmadduanil100% (1)

- A 2.4 GHZ Gaas-Hbt Class-E Mmic Amplifier With 65% PaeDokument4 SeitenA 2.4 GHZ Gaas-Hbt Class-E Mmic Amplifier With 65% PaeKevin Dany100% (1)

- Ucn 5821 ADokument7 SeitenUcn 5821 ACelso Conceição100% (1)

- Details of ARP and PPPDokument40 SeitenDetails of ARP and PPPYogesh Palkar100% (1)

- Silicon Controlled RectifierDokument9 SeitenSilicon Controlled RectifierFarishat Nusabbee An Nafs100% (1)

- Group 7 FinalReportDokument27 SeitenGroup 7 FinalReportJust4 Shop100% (1)

- PDF Edne Nov 2013Dokument48 SeitenPDF Edne Nov 2013torinomg100% (1)

- Default Switch/Jumper SettingsDokument16 SeitenDefault Switch/Jumper SettingsRafael Avella100% (1)

- Port PDFDokument16 SeitenPort PDFdharanika100% (1)

- TempDokument3 SeitenTempParth Joshi100% (1)

- Networking Tutorial - TCPIP Over EthernetDokument8 SeitenNetworking Tutorial - TCPIP Over EthernetAbhilash V Pillai100% (24)

- M XrutytDokument12 SeitenM XrutytDistribuidorIBoolPedregalDeSantoDomingo100% (1)

- Bidirectional Current Source-TIDokument9 SeitenBidirectional Current Source-TIestraj1954100% (1)

- Lab LCDDokument6 SeitenLab LCDJesus Cotrina100% (1)

- Lecture 7 - LCDDokument25 SeitenLecture 7 - LCDSuhaib Abugdera100% (1)

- Datasheet Sen23292pDokument15 SeitenDatasheet Sen23292pjessie100% (1)

- Induction Motor Drive Using Thyristor Based Cycloconverter For Variable Torque Load ApplicationDokument5 SeitenInduction Motor Drive Using Thyristor Based Cycloconverter For Variable Torque Load ApplicationIJIRST100% (2)

- Oscillators Module 02Dokument20 SeitenOscillators Module 02ervaishu5342100% (1)

- Document Mini Project No 1.117Dokument8 SeitenDocument Mini Project No 1.117rahmat100% (1)

- U 0712076Dokument3 SeitenU 0712076peter100% (1)

- Read Modify WriteDokument2 SeitenRead Modify WriteMisbah UrRehman100% (1)

- IrsolwibDokument4 SeitenIrsolwibleko17100% (2)

- Sound Sensor Module PDFDokument5 SeitenSound Sensor Module PDFTrần Thảo Nguyên100% (1)

- x64 AsmDokument4 Seitenx64 Asmasdmin100% (1)

- Hobby Servo Motor Control Via PIC Pulse Width Modulation: Nathan Markey April 4, 2003Dokument7 SeitenHobby Servo Motor Control Via PIC Pulse Width Modulation: Nathan Markey April 4, 2003Luciana Gutierrez Salazar100% (1)

- Oasis Technologies PVT - LTD: ReturnDokument5 SeitenOasis Technologies PVT - LTD: Returnrpsirius1100% (1)

- Mains Slave TriacDokument2 SeitenMains Slave Triacdewasuryanto100% (3)

- Program LCDDokument2 SeitenProgram LCDAngga Wijaya Kusuma100% (1)

- Microstepping TutorialDokument5 SeitenMicrostepping TutorialDave Chan100% (1)

- LCD InfDokument1 SeiteLCD Infkottee1977100% (2)

- Complete Gas Sensor CircuitDokument9 SeitenComplete Gas Sensor Circuitsethuraghul100% (1)

- Volume52 Number4Dokument64 SeitenVolume52 Number4torinomg100% (1)

- 17pw17 2Dokument1 Seite17pw17 2korodiferenc9258100% (1)

- HBridgeMotorControl With PICDokument11 SeitenHBridgeMotorControl With PICcoceicr100% (3)

- Probador rj45Dokument1 SeiteProbador rj45Manuel Rivas100% (2)

- CCP PWMDokument19 SeitenCCP PWMalaa_saq100% (1)

- Unit - Iii MPMC-1Dokument79 SeitenUnit - Iii MPMC-1gunda manasa100% (1)

- ML12 SchematicDokument1 SeiteML12 SchematicDon Bosse100% (1)

- 5 2 X 16 Parallel LCD: 3.5.1 Technical SpecificationsDokument3 Seiten5 2 X 16 Parallel LCD: 3.5.1 Technical SpecificationsManish Singh100% (1)

- Static 0 To 9 Display PDFDokument2 SeitenStatic 0 To 9 Display PDFΔημητριος Σταθης100% (1)

- 8051 Interfacing With Display SevicesDokument5 Seiten8051 Interfacing With Display Sevicesramjee26100% (1)

- Microwave ConsoleDokument1 SeiteMicrowave ConsoleMochammad Praditia100% (1)

- Book PIC Microcontrollers-Chapter 5 CCP ModulesDokument17 SeitenBook PIC Microcontrollers-Chapter 5 CCP ModulesHammamiSalah100% (1)

- What Is The Difference Between Microcontrollers and 8051Dokument6 SeitenWhat Is The Difference Between Microcontrollers and 8051Erandi Brito100% (1)

- AIS SchematicDokument6 SeitenAIS SchematicKyai Sumirat Gludug Sinawang100% (4)

- PIC PPT 13104022 (4th Year)Dokument41 SeitenPIC PPT 13104022 (4th Year)Daman Deep Singh100% (1)

- Aerosemi: Features ApplicationsDokument9 SeitenAerosemi: Features Applicationsttnaing100% (1)

- CCP ModuleDokument11 SeitenCCP ModuleAltaaf Mulani100% (1)

- Arduino TMP36 Precision Temperature Sensor-GuideDokument1 SeiteArduino TMP36 Precision Temperature Sensor-GuideMC. Rene Solis R.100% (1)

- RS 232Dokument1 SeiteRS 232Aneela Pathan100% (1)

- LCD Interfacing With ATmega32Dokument6 SeitenLCD Interfacing With ATmega32nandoclasic100% (2)

- Agribot Project PresentationDokument21 SeitenAgribot Project Presentationumaiya1990100% (1)

- SMPS Fly Back Design Using Tl431Dokument11 SeitenSMPS Fly Back Design Using Tl431reji1usNoch keine Bewertungen

- Plecs FlybackDokument4 SeitenPlecs FlybackBhargavNoch keine Bewertungen

- TLE7242G-TLE8242-2L+-Application-Note KP KI V2 0Dokument13 SeitenTLE7242G-TLE8242-2L+-Application-Note KP KI V2 0Larbi_Lakrout_7056Noch keine Bewertungen

- UC3842 Inside SchematicsDokument17 SeitenUC3842 Inside Schematicsp.c100% (1)

- Gigabit POE TheoryDokument5 SeitenGigabit POE TheoryAlexNoch keine Bewertungen

- VHDL OverviewDokument55 SeitenVHDL OverviewkhsniperNoch keine Bewertungen

- WEST COAST MAGNETICS - Application Notes: Alnt 1440, Revision 1 Flyback Converter DesignDokument6 SeitenWEST COAST MAGNETICS - Application Notes: Alnt 1440, Revision 1 Flyback Converter DesignkhsniperNoch keine Bewertungen

- 2006 Nissan Sentra PDFDokument256 Seiten2006 Nissan Sentra PDFkhsniperNoch keine Bewertungen

- Switching Power Supply Topologies Comparison and SelectionDokument3 SeitenSwitching Power Supply Topologies Comparison and SelectionkhsniperNoch keine Bewertungen

- Cutting Power Consumption With Energy-Efficient Power Over Ethernet (Eepoe) TechnologyDokument6 SeitenCutting Power Consumption With Energy-Efficient Power Over Ethernet (Eepoe) TechnologykhsniperNoch keine Bewertungen

- 01) - 2up 3Dokument70 Seiten01) - 2up 3asadraza123Noch keine Bewertungen

- P E (P E) : Ower Over Thernet ODokument3 SeitenP E (P E) : Ower Over Thernet OkhsniperNoch keine Bewertungen

- IEEE802.3at High Power POE+ Class ProgrammingDokument2 SeitenIEEE802.3at High Power POE+ Class ProgrammingkhsniperNoch keine Bewertungen

- Current Balancing PoeDokument8 SeitenCurrent Balancing PoekhsniperNoch keine Bewertungen

- Electronics Ch7Dokument30 SeitenElectronics Ch7khsniperNoch keine Bewertungen

- Integrated FlybackDokument3 SeitenIntegrated FlybackkhsniperNoch keine Bewertungen

- Power Over Ethernet Technology For Industrial Ethernet NetworksDokument8 SeitenPower Over Ethernet Technology For Industrial Ethernet NetworkskhsniperNoch keine Bewertungen

- Intro - CMOS Analog CKT DesignDokument15 SeitenIntro - CMOS Analog CKT Designgene_palenciaNoch keine Bewertungen

- Flyback ConverterDokument5 SeitenFlyback ConverterfadalmolinNoch keine Bewertungen

- Battery ChargerDokument3 SeitenBattery ChargerkhsniperNoch keine Bewertungen

- ISI 500 SpecDokument2 SeitenISI 500 SpeckhsniperNoch keine Bewertungen

- Integrated FlybackDokument3 SeitenIntegrated FlybackkhsniperNoch keine Bewertungen

- K Factor Calculation 5787Dokument2 SeitenK Factor Calculation 5787Aamir AliNoch keine Bewertungen

- Per Unit Analysis: Single-Phase SystemsDokument8 SeitenPer Unit Analysis: Single-Phase SystemsLin ChongNoch keine Bewertungen

- DN 425 FDokument2 SeitenDN 425 FkhsniperNoch keine Bewertungen

- Eeiol 2006apr24 Pow Ta 01Dokument2 SeitenEeiol 2006apr24 Pow Ta 01khsniperNoch keine Bewertungen

- LT8300Dokument2 SeitenLT8300khsniperNoch keine Bewertungen

- LT8300Dokument2 SeitenLT8300khsniperNoch keine Bewertungen

- Optimizing With eGaN FETsDokument6 SeitenOptimizing With eGaN FETskhsniperNoch keine Bewertungen

- 4275 FDokument12 Seiten4275 FkhsniperNoch keine Bewertungen

- 4257 FBDokument20 Seiten4257 FBkhsniperNoch keine Bewertungen

- Fly Back 3Dokument5 SeitenFly Back 3Hüseyin YeşilyurtNoch keine Bewertungen

- LM 2585Dokument30 SeitenLM 2585khsniperNoch keine Bewertungen

- Hardware Implementation of Real-Time Image Segmentation Algorithms Using TMS320C6713 DSP and VM3224K2 Daughter KitDokument4 SeitenHardware Implementation of Real-Time Image Segmentation Algorithms Using TMS320C6713 DSP and VM3224K2 Daughter KitJUNAID100% (1)

- LPC2478 PDFDokument93 SeitenLPC2478 PDFdecosat2012Noch keine Bewertungen

- ATS ManualDokument20 SeitenATS Manualcavcam100% (2)

- Efis & AcarsDokument7 SeitenEfis & AcarsNikhil PatelNoch keine Bewertungen

- Power Xpert Solar 250 KW Inverter - Harvest The Power of The SunDokument2 SeitenPower Xpert Solar 250 KW Inverter - Harvest The Power of The SunEmilio EscalanteNoch keine Bewertungen

- Advances in Analog Circuits PDFDokument380 SeitenAdvances in Analog Circuits PDFnskprasad89100% (1)

- 05 - Arco 400Dokument17 Seiten05 - Arco 400NgigiDanielNoch keine Bewertungen

- Counts 16-Bits at A TimeDokument3 SeitenCounts 16-Bits at A TimerajeshNoch keine Bewertungen

- Saep 350 PDFDokument15 SeitenSaep 350 PDFRami Elloumi100% (1)

- Keithly 2002 ManualDokument361 SeitenKeithly 2002 ManualSteve KirkmanNoch keine Bewertungen

- Lab 6 Arithmetic Operations IDokument3 SeitenLab 6 Arithmetic Operations IMikel_Mack100% (1)

- DMTE ABB 2csm445001d0202Dokument12 SeitenDMTE ABB 2csm445001d0202Marco VolpeNoch keine Bewertungen

- Omni Lifenet SpecsDokument2 SeitenOmni Lifenet SpecsAngel JuarezNoch keine Bewertungen

- Decca TreeDokument4 SeitenDecca Treeiuridicaprima4Noch keine Bewertungen

- Product Manual 82434 (Revision C) : Generator Loading ControlDokument26 SeitenProduct Manual 82434 (Revision C) : Generator Loading ControlAUGUSTA WIBI ARDIKTANoch keine Bewertungen

- Nfa S2Dokument1 SeiteNfa S2Amyt Srivastav100% (1)

- Vacuum Circuit Breaker (VCB) Working and ApplicationsDokument11 SeitenVacuum Circuit Breaker (VCB) Working and ApplicationsMoe Oo KoNoch keine Bewertungen

- Applications of Balanced ModulatorDokument5 SeitenApplications of Balanced ModulatorSomeshwar GaddalaNoch keine Bewertungen

- Cubigel Compressor MS26TB V R404A 220 50Dokument5 SeitenCubigel Compressor MS26TB V R404A 220 50Nikolay KapitanovNoch keine Bewertungen

- Lecture05 Ee620 Charge PumpsDokument22 SeitenLecture05 Ee620 Charge PumpsPeygamberinizi Sikiyim100% (1)

- Transformer DesigneDokument6 SeitenTransformer Designemhm770077100% (1)

- 109 MINIMAX Data Sheet of Module FMZ5000 Loop AP XPDokument1 Seite109 MINIMAX Data Sheet of Module FMZ5000 Loop AP XPlong yuNoch keine Bewertungen

- 1/2" Cellflex Low-Loss Foam-Dielectric Coaxial Cable: LCF12-50JFNDokument4 Seiten1/2" Cellflex Low-Loss Foam-Dielectric Coaxial Cable: LCF12-50JFNLuciano Silvério LeiteNoch keine Bewertungen

- Energy Management in Islanded DC Microgrid Using Fuzzy Controller To Improve Battery PerformanceDokument6 SeitenEnergy Management in Islanded DC Microgrid Using Fuzzy Controller To Improve Battery PerformanceVelid ÇelikNoch keine Bewertungen

- Gallien Krueger bl112 Poweramp 206 0151Dokument17 SeitenGallien Krueger bl112 Poweramp 206 0151electromusicworkshopNoch keine Bewertungen

- TMEIC ManualDokument2 SeitenTMEIC Manualprasna007Noch keine Bewertungen

- Manual I-24xW-S PDFDokument120 SeitenManual I-24xW-S PDFMario Junior0% (1)

- Solar Mobile ChargerDokument21 SeitenSolar Mobile ChargerSourabh BanerjeeNoch keine Bewertungen

- EE124 Lecture 12 Source Follower Cascode Amplifier and Current Source Mar 9 Spring 2020 Annotated PDFDokument13 SeitenEE124 Lecture 12 Source Follower Cascode Amplifier and Current Source Mar 9 Spring 2020 Annotated PDFSabeeq KarimNoch keine Bewertungen

- 23-24 Wiring Info MaglockDokument2 Seiten23-24 Wiring Info Maglocktonyeld100% (1)