Beruflich Dokumente

Kultur Dokumente

Timing and Synchronization For Quasi-Real-Time Systems Using IEEE 1588v2 Over Ethernet

Hochgeladen von

openid_AePkLAJcOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Timing and Synchronization For Quasi-Real-Time Systems Using IEEE 1588v2 Over Ethernet

Hochgeladen von

openid_AePkLAJcCopyright:

Verfügbare Formate

Timing and Synchronization for Quasi-Real-Time Systems Using IEEE 1588v2 Over Ethernet

Marc Cohn

Micrel, Incorporated www.micrel.com LAN Solutions Business Unit San Jose, California, USA marc.cohn@micrel.com

Abstract Ethernet and IEEE 1588 are continuing to emerge in a wide range of industries. Increasingly, they are replacing industry-specific interconnects, delivering performance and cost efficiencies. Initiatives including Industrial Ethernet, IEC 61850, and LXI are all adopting commercial off- the-shelf technologies to achieve broader communications at far lower costs. However, significant investments that are warranted for large automation systems become prohibitively expensive for a diverse set of less, ambitious Quasi-Real-Time (QRT) applications that also require distributed communications and timing. This paper proposes an approach to address the communications and timing/synchronization requirements for QRT systems, characterized by simple and low-cost devices interconnected and synchronized over a real-time network. To achieve the aggressive cost targets, a highly integrated attachment device is introduced that integrates Ethernet communications, IEEE 1588v2 distributed synchronization, and precision I/O for local synchronization in a single, energy efficient device. Systems issues are also raised affecting the applicability for applications that can exploit a QRT network. Keywords: IEEE 1588v2, Real-Time Ethernet, Precision I/O, Synchronized I/O, Industrial Ethernet, Quasi-Real-Time

Industrial Ethernet standards such as Ethernet/IP [2], Profinet [3], and PowerLink [4] seeking to capitalize upon the benefits of Commercial Off-The-Shelf (COTS) technologies, are aggressively deploying Ethernet integrated with IEEE 1588. Similarly, the power systems automation industry has specified an important standard to guide Power Substation Automation. IEC 61850 [5] breaks new ground in adopting Ethernet, IEEE 1588, and responsive fault tolerance schemes for a comprehensive communications framework for Substation Automation Systems (SAS). Industrial and Power Systems Automation market leaders are aggressively promoting Industrial Ethernet standards, as well as IEC 61850. However, significant up-front investment and comprehensive software stacks render the standards too expensive for many applications. Ultimately, there are many lower-end applications that would benefit from reliable communications and tight synchronization, but without the rich set of services and objects defined by the standard frameworks. II. QUASI-REAL-TIME (QRT) NETWORKS

I.

INTRODUCTION

Ethernet, the predominant Local Area Network standard, is emerging in a number of non-traditional applications, leveraging the tremendous momentum of an installed base in excess of one billion ports. Economic realities have motivated the adoption of Ethernet in such diverse environments ranging from the factory floor, in-vehicle, to electrical power substations. While all very different, such applications share an unmistakable and pervasive trend: point-to-point interconnects and industry-standard buses are being replaced by robust, Ethernet-based networks. Increasing intelligence, counter-balanced by the everpresent need for cost reduction, has necessitated integration of communications and timing/synchronization, germane to Industrial, Automotive, and Power Systems automation. Market and technology forces influenced the IEEE to upgrade a relatively obscure standard into prominence. Thus, IEEE 1588-2008 [1] is gaining market momentum as the basis for next-generation real-time automation systems and, in the process, is transforming the target industries.

To distinguish from the large, hierarchical automation networks, we introduce QRT systems and networks, which correspond to a broad set of relatively mid- to low-end applications built upon an integrated services network. By merging timing and communications into a unified, low-cost network, applications processing may be distributed, communications and synchronization jitter reduced, and greater precision may be achieved [6]. QRT systems are characterized by: Standardized, high-performance network architecture providing communications and synchronization Relatively low-end devices (~$100s - $1,000s): Sensors, Actuators, Motor Drives, etc. Embedded CPUs, running the host application Relatively small number of nodes per sub-network (typically less than 30) Message latencies of less than 1 ms (short, <200 byte messages) Sub-100 s synchronization jitters (typically better)

978-1-61284-893-8/11/$26.00 2011 IEEE

As with most successful technologies, availability of lowcost, standardized building blocks spawn a diverse and broad set of applications. The convergence of Ethernet and IEEE 1588 has paved the way for precision timing to catalyze development of QRT systems; by capitalizing upon the benefits of COTS, proven communications and synchronization technologies, and of course, reduction of life-cycle costs. The key to enabling such applications is availability of highly integrated silicon that simplifies QRT node designs, and adapt to the widely varying interface requirements, including: Comprehensive support for predominant standards including IEEE 802.3 (Ethernet) and IEEE 1588/PTPv2 distributed timing and synchronization Multi-megabit communications (typically 100 Mbps) Standardized copper and fiber media options to accommodate varying cable reaches Flexible topologies: o o Centralized, star-wired topologies to exploit the benefits of structured wiring Distributed, daisy-chained topologies (i.e., rings and linear buses) to facilitate dynamically changing network configurations Hybrid topologies, exploiting the benefits of both Centralized and Distributed topologies

Systems performance is driven by a complex combination of these factors, making it difficult to apply generic rules of thumb for QRT network configuration. Communications latency, synchronization jitter, ring recovery delays, etc. are all inter-related, c the need to meticulously analyze the applications (with respect to the network), in order to achieve the desired systems behavior. For instance, decreasing ring recovery times may not yield appreciable benefits if the synchronization acquisition time is orders of magnitude higher. Increasing network bandwidth will not necessarily address overcome the issue, nor will increasing the processing speed necessarily improve network availability. The challenge is architecting a QRT network architecture sufficiently broad to encompass a range of applications at a very low cost. Systems designers may then exploit standardized building blocks that attain the best of both worlds- the highperformance only achievable by silicon, at a cost-effective price. One prospective application for QRT networks is the emerging IEC 61850 standard for Power Substation Automation. IEC 61850 defines a hierarchical communications architecture, based on Ethernet and IEEE 15888 technology. The lowest layer is referred to as the Process Bus, which interconnects Intelligent Electronic Devices (IED, as defined in the standard) that provides real-time communications. Relays, switches, and other electrical power gear are controlled by the Process Bus, which is considered missioncritical by substation operators. The standard recognized the need for a multi-service, scalable, robust, and highperformance network to achieve the explicit goal of reducing overall operations costs- a key benefit of the QRT networks. III. COST REALITIES- INTEGRATED ETHERNET/IEEE 1588V2 NETWORKS

Optional, network fault tolerance mechanisms to maintain communications availability Support for distributed synchronization, which may be extended to locally connected devices Hardware assist for communications and synchronization to minimize the processing demands on the embedded processors Rich set of I/O capabilities to accommodate a range of devices with varying operating characteristics

There are a number of complementary technologies that are also needed to enable QRT systems/network design: Real-Time, Systems Timing References, referred to in IEEE 1588 as Grand Master Clocks; highly accurate timing standards for synchronizing distributed nodes Robust Ring Recovery protocols capable reconfiguring around common network faults, typically < 10 milliseconds Streamlined Real-Time Operating Systems (RTOS), to ensure efficient communications, synchronization, and applications processing Network management to enable the availability, performance, and configuration of the network to be monitored for real-time and long-term analysis

Migrating from relatively simple serial interconnects and buses to an integrated Ethernet/IEEE 1588v2 network in a costeffective manner can be challenging. Considering the cost difference between an RS-485 interface and Ethernet port, it remains cost-prohibitive to directly connect low-end devices to Ethernet networks. Typically, the Ethernet MAC and PHY functions are implemented in silicon in accordance with the IEEE 802.3 standard [7]. Ethernet LAN are commercially available from multiple vendors. IEEE 1588v2 implementations are far less common, and are typically implemented in FPGAs, Physical Layer (PHY) transceivers, or Micro-Controller Units (MCUs). Integrating Ethernet switching along with IEEE 1588v2 (and the associated logic) is not a trivial exercise, and requires additional communications and synchronization processing (in the host CPU). Ethernet/IEEE 1588 attachments will multiplex multiple devices (through I/O pins) in order to achieve cost parity with point-to-point systems (see Figure 1). Migrating to a network offers greater flexibility and a compelling range of benefits.

Figure 1. Per-Device Cost Comparison Serial Interconnect vs. Serial Bus vs. Ethernet Network

Networks enable a rich set of communications services such as multicast, Virtual LANs, and Quality of Service that offer unprecedented applications flexibility. Integrating IEEE 1588 realizes sub-s synchronization of nodes distributed throughout the network cost-effective and reliable. Far greater bandwidths, often enumerated in orders of magnitude, are readily achievable with the well-established 10/100 Ethernet standards. In addition, cabling can be simplified as well, to accommodate frequently changing operational needs. The costs for an Ethernet/1588v2 attachment (assuming a distributed topology), include: IEEE 1588v2 Facilities o o o IEEE 1588v2 Precision Clock 2 Time Stamp Units (TSUs) for PTP packets PTP hardware support 2 integrated Media Access Control (MAC) 2 10/100BaseTX PHY Transceivers

Figure 2. KSZ84xx IEEE 3-port 10/100 / IEEE 1588v2 Switch Functional Block Diagram

Wire-speed, full-featured 3-port 10/100 Mbps switch Dual IEEE 1588v2 time stamp units, Precision Clock, and distributed synchronization facility o o Synchronization performance is improved as TSUs reside between the MAC and PHY Grand Master, Master, Slave, and Transparent Clock modes are supported Lowest power 100BaseTX PHY Transceiver (< 150 mW per port) IEEE 802.3FX optical transceiver support

Dual, low-power 10BaseT / 100BaseTX PHYs o o

3-port 10/100 Ethernet switch o o

Precision I/O (synchronized to the Precision Clock) PTP Software (typically running in the Host CPU)

Hardware support for communications and precision clock synchronization, which reduces the overall processing load on the host CPU Integrated I/O that can be synchronized to the overall system synchronization hierarchy Advanced power management including IEEE 802.3az Energy Efficient Ethernet (EEE) [9] Compact size through a single-chip (64-pin package, 10 mm x 10 mm) design

Cost challenges persist. Presently, an Ethernet/1588v2 attachment implemented in an FPGA, with a pair of external Ethernet PHY Transceivers, with an estimated cost measured in $20-30 USD or more. Assuming four to eight devices share a single Ethernet/1588 attachment, the per-device costs are on the order of $3 $5; multiples of the sub $1 USD cost for an RS-485 interface transceiver. IV. INTEGRATION OPPORTUNITIES

In order to reduce the Ethernet/IEEE 1588 attachment costs so as to be on par with serial interconnects, further integration is necessary. This is primarily achievable through an ASIC. As a result, Micrel Semiconductor recently introduced the KSZ84xx family of IEEE 1588v2-enabled Ethernet 3-port 10/100 switches [8], for QRT applications. This Industrialgrade platform represents a single chip, highly integrated 1588/Ethernet attachment, offering several tangible benefits:

Figure 2 depicts the high-level block diagram for the KSZ84xx switch, illustrating the functional blocks. The KSZ84xx is available with standard (MII or RMII) and generic host bus interfaces to support CPUs with and without embedded Ethernet MACs. The Precision GPIO facility enables multiple devices to share a single Ethernet/IEEE 1588 attachment. Precision GPIO is highly flexible and configurable to support a diverse set of devices with wide ranging operational and performance characteristics.

Figure 3. IEEE 1588v2 Systems Timing Hierarchy Figure 4. QRT Node Timing Interfaces

V.

PRECISION I/O AND LOCAL SYNCHRONIZATION

Devices connected to the QRT network through the Precision GPIO facility must be synchronized to the node, and hence system reference timing. Figure 3 illustrates the system timing hierarchy implied by IEEE 1588v2, where: A global, real-time reference (i.e., GPS) synchronizes a Grand Master Clock (GMC), the system reference Multiple Master Clocks (MCs), each corresponding to a distinct synchronization domain, are synchronized to the GMC Each MC synchronizes the set of Slave Clocks (SCs) comprising a particular synchronization domain. For Industrial Ethernet, SCs are typically daisy-chained together into a distributed topology. Locally connected nodes can source or sink data and/or control information through a Precision I/O interface that is synchronized with the local precision clock

A select set of applications may require synchronization performance far better than specified in the IEEE 1588-2008 standard. Section 1 of the standard specfies 1 s Jitter (variability) value. However, the IEEE Precise Networked Clock Synchronization Working Group recognized the need for sub-s performance for a range of specialized applications, which is explicitly called out in the standard. In the Industrial Automation arena, defacto standards such as EtherCat [11], and ProfinetIRT [12] have emerged to fill the need for the most stringent real-time applications. At 100 Mbps, these technology enable real-time system cycle times below 500 s; at 1 Gbps < 500 s is feasible [13]. Synchronization accuracies are measured in 10s of ns. EtherCat and ProfinetIRT use proprietary approaches that preclude the use of standard Ethernet MACs (even though both adopted the Ethenet 10/100/1000 Mbps PHY layer). For higher-end applications, IEEE 1588v2 over Ethernet implementations may be enhanced by proactively addressing the error sources that deteriorate synchronization performance. Higher accuracy oscillators, enhanced power filtering, etc. are likely to result in synchronization performance well-below 100ns. While the synchronization performance may be on par with the real-time protocols, overall systems performance for EtherCat and ProfiNet IRT will be more suitable for precision motion, and other real-time systems which require the highest performance. VI. LOCAL TIMING & I/O IMPLEMENTATION

The distinction is drawn between timing, where real-time is distributed, and synchronization, which relates to a frequency reference distribution across multiple, disparate equipment. Synchronization may be provided through standardized timing interfaces (see Figure 4): 1 PPS reference for time distribution 10 MHz reference for synchronized clock distribution

Because timing and synchronization is application-specific, versatility is required to tailor the timing interfaces to the needs for specific designs. Additional reference signals (such as 100 PPS timing output, 1 MHz and 5 MHz, etc.) may be necessary. Also, signal characteristics may also vary (e.g., pulse width, voltage level, etc.), necessitating configurability, without compromising synchronization in accordance with the systems timing hierarchy. Real-time distribution may be achieved through such standards as IRIG-B, published by the Inter-Range Instrumentation Group. The IRIG standard [10], defines internationally recognized Time Code Formats and sentences that reduce the need for real-time references. Real-time distribution is being considered for future versions of the KSZ84xx platform.

Micrels KSZ84xx Industrial Ethernet switch platform is an ASIC specifically designed to enable QRT networks. Figure 5 depicts how multiple devices share a single Ethernet/IEEE 1588 attachment through the KSZ84xx Precision I/O facility. Precision I/O pins are synchronized with the local precision clock, which in turn is synchronized to the system timing hierarchy. In-house testing yields synchronization jitters on the order of 100 ns or less (see Figure 6), even under 99%+ network loads. Such performance is attained through positioning the time stamp units, directly between the PHY and the MAC (on-chip). As a result, measurement and time stamp errors are significantly reduced at the node-level.

Figure 5. Multiple Devices Share a Common QRT Network Attachment to Attain Cost Parity with Serial Interconnects

Figure 6. Sub-100 ns Synchronization Jitter (Master to Slave Clocks)

Most available 1588 implementations partition the MACto-PHY interface on two distinct devices, compromising synchronization performance. Multi-chip implementations also prove more costly, consume higher power, require additional board space, and are typically less reliable than an ASIC. Another factor yielding improved synchronization performance is the tightly coupled Precision Timing Protocol (PTP) stack, developed by OnTime Networks, Oslo, Norway. Hardware-assisted PTP operations (especially periodic Transparent Clock corrections) are not only more efficient, but more importantly, conserve scarce Host CPU resources which can otherwise be dedicated to applications processing. In order to support diverse interface needs anticipated for QRT systems, a broad set of I/O capabilities has been provided, as summarized in Table I. The I/O implementation is based on a set of logical I/O Event Units that may be assigned to any of the available I/O pins. By decoupling Event Units from physical pins, more sophisticated I/O operations are possible. Input Event Units provide an efficient means of monitoring external events and conditions on I/O input pins. For each Input Event, a time stamp is generated whether for an Edge or Pulse sensed on that pin. Input Event Units may be cascaded together to monitor compound events (i.e., sequences of multiple pulses, edges, and in essence bit patterns), offloading the Host CPU from low-level I/O manipulation. Once detected, the time stamp corresponding to each received event will be queued up for the host CPU to retrieve. Such an approach decouples host processing from the I/O acquisition, further offloading the Host CPU. Improving host efficiency is especially significant for QRT systems where multiple events may occur virtually simultaneously. Upon retrieving each Input Events, the Host CPU must analyze the time stamps to determine pulse widths, the time intervals when the events occurred, etc. For Output Events, a flexible range of I/O Output Units and associated operations are supported. Each Output Event will be initiated (i.e., triggered) when the local precision clock reaches a pre-configured value corresponding to the event. Thus, all Output Events are timed in concert with the local clock, and in turn the overall systems timing hierarchy.

GPIO Output performance is governed by the Host CPU selection, host interface (MII, RMII, or Generic Host Interface), and complexity of the designated output operations. For each operation, the Host must configure the appropriate registers (through the management interface), and set the appropriate trigger time.

I/O Capability

Applications

Configurability

Notes

Inputs Edge Monitor Pulse Monitor Events Alarms Interrupt Control word sensing Timing (n x PPS) Positive or Negative Polarity Polarity Pulse Width May be cascaded for more complicated bit patterns May be used as a 1 PPS input for local timing by an external system

Outputs Edge Generator Pulse Generator Positive or Negative Polarity Polarity Pulse Width May be cascaded for more complicated bit patterns May be used as a 1 PPS input for local timing by an external system

Waveform Generator

t x PPS Timing signal

Frequency Generator Register Mode

F MHz Reference Control Word outputs

Start time Cycle time # of Cycles Pulse Width Frequency, Duty Cycle Start time, Repetitions

1 Hz 12.5 MHz

Shifts out contents of a designated output register

TABLE I.

KSZ84xx Precision I/O Mechanisms

Similar to the Input Event Units, Output Event Units may be cascaded to enable more complex operations. For example, if a Logic Controller is required to send a 32-bit control word to request a Sensor reading, 2 Register Mode Output Events may be cascaded together. Once triggered (at the prescribed time), both of the Register Mode Output Units will sequentially shift out the 16-bit contents of user-data (contained in an internal register) onto a single I/O Output pin. In addition to the relatively simple Edge, Pulse, and Register modes, timing interfaces may be implemented using the highly configurable Output Trigger Unit, such as the common 1 PPS signal that distributes precision timing. The 1 PPS Output may be configured to comply with the GPS Interface Control Document (ICD) for the Precision Time and Time Interval (PTTI) Interface [14], or an alternative specification. The Waveform Generator Output Unit may be configured to address a number of applications including: N x PPS Output Interval (where N = 1 for 1 PPS) Start Time Pulse Width Number of pulses (if not continuous)

REFERENCES

[1] Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems, IEEE Standard 1588, 2008. ODVA, Ethernet/IP Technology Overview, http://www.odva.org/ PI, Profinet- A Rich, Powerful, Ethernet Solution for Automation, http://www.profibus.com/technology/profinet/ EPSG, Ethernet PowerLink, http://www.ethernet-powerlink.org/ Communication networks and systems in substations - ALL PARTS, IEC 61850, 2011. Ken Harris (January, 2009), An Application of IEEE 1588 to Industrial Automation, Rockwell-Automation Publication: 1756-WP005-EN-E Available: http://samplecode.rockwellautomation.com/idc/groups/literature/docume nts/wp/1756-wp005_-en-e.pdf IEEE Standard for Information technology - Telecommunications and information exchange between systems - Local and metropolitan area networks - Specific requirements Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method., IEEE 802.3., 2008. Micrel Inc., KSZ84xx Data Sheet, 2011 IEEE 802.3az-2010 IEEE Standard for Local and Metropolitan Area Networks - Specific requirements Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications Amendment 5: Media Access Control Parameters, Physical Layers, and Management Parameters for Energy-Efficient Ethernet Inter-Range Instrumentation Group SERIAL TIME CODE FORMATS, IRIG Standard 200-98, Telecommunications and Timing Group of the Range Commanders Council, 1998. EtherCat Technology Group, EtherCat- Ethernet for Control Automation Technology, http://www.ethercat.org PI, Profinet- A Rich, Powerful, Ethernet Solution for Automation, http://www.profibus.com/technology/profinet/ Gunnar Prytz (2008), 13th IEEE International Conference on Emerging Technologies and Factory Automation, pp. 408-415 Available: http://www.ethercat.org/pdf/english/ETFA_2008_EtherCAT_vs_PROFI NET_IRT.pdf GPS User Equipment III ICD for the Precision Time and Time Interval (PTTI) Interface, GPS ICD-GPS-060, GPS Navstar Joint Program Office (US Govt.), 2002.

[2] [3] [4] [5] [6]

[7]

[8] [9]

[10]

Multiple timing signals may be initiated with different rate, which provides a low cost, yet accurate timing reference. High-frequency reference signals may also be generated, using the Frequency Generator Output Unit. Frequency Outputs may be configured from 1 Hz to 12.5 MHz, on one or more I/O output pins. While the frequency is synchronized, phase is not; the output may be used for syntonization. VII. CONCLUSIONS Quasi-Real-Time systems, characterized by low-end devices interconnected over a distributed Ethernet/IEEE 1588v2 network in timing-based systems, are made viable through availability of highly integrated, silicon-based implementations. Cost-effective, energy efficient network attachment implementations enable a range of distributed QRT monitoring, control, and automation applications that can exploit unprecedented communications and synchronization performance while reducing life cycle costs. While QRT network performance remains coupled closely with the applications, high-performance silicon such as Micrels KSZ84xx family renders IEEE 1588 over Ethernet as a viable option for a range of diverse applications that were previously cost-prohibitive. As costs are further reduced, QRT will make it feasible to continue to migrate down-market, replacing point-to-point interconnects.

[11] [12] [13]

[14]

Das könnte Ihnen auch gefallen

- Bruno Elan Sre 3000 Stair Lift Installation Manual 05 13 2015 PDFDokument78 SeitenBruno Elan Sre 3000 Stair Lift Installation Manual 05 13 2015 PDFbarqzr davi75% (4)

- How To Convert Old Substation To A Digital SubstationDokument16 SeitenHow To Convert Old Substation To A Digital SubstationBruno Samos0% (1)

- Japanese GardensDokument4 SeitenJapanese GardensNirOoha VeeramachaneniNoch keine Bewertungen

- Trendsetter VLFDokument594 SeitenTrendsetter VLFMynor GraveeNoch keine Bewertungen

- OED9D1202 UGW9811 V900R013C10 System Operation and Maintenance ISSUE1.0Dokument69 SeitenOED9D1202 UGW9811 V900R013C10 System Operation and Maintenance ISSUE1.0fourneelNoch keine Bewertungen

- Integrating Scada Load SheddingDokument9 SeitenIntegrating Scada Load Sheddinganeesh100% (1)

- Scada Application Flyer - SmallDokument6 SeitenScada Application Flyer - Smallosto72Noch keine Bewertungen

- Ethernet Network Redundancy in SCADA and Real-Time Automation PlatformsDokument14 SeitenEthernet Network Redundancy in SCADA and Real-Time Automation PlatformssavijolaNoch keine Bewertungen

- Role of IEC 61850 & GOOSE in Substation Automation: A ReviewDokument4 SeitenRole of IEC 61850 & GOOSE in Substation Automation: A ReviewInternational Journal of Innovative Science and Research TechnologyNoch keine Bewertungen

- LTE Stretches Synchronization To New Limits: White PaperDokument6 SeitenLTE Stretches Synchronization To New Limits: White PaperShane RamaNoch keine Bewertungen

- IEC61850 Overview and Benefits Paper GeneralDokument8 SeitenIEC61850 Overview and Benefits Paper GeneralMarcWorldNoch keine Bewertungen

- Practical Applications of IEC61850 Protocol in Industrial FacilitiesDokument9 SeitenPractical Applications of IEC61850 Protocol in Industrial Facilitiesraghavendran raghu100% (1)

- Smart Metering Comm StandardsDokument6 SeitenSmart Metering Comm StandardsFernando CercanoNoch keine Bewertungen

- The Rise of Single Pair Ethernet IlotDokument8 SeitenThe Rise of Single Pair Ethernet IlotJohn StewardNoch keine Bewertungen

- New Ethernet Technologies For Substation Automation: AbstractDokument6 SeitenNew Ethernet Technologies For Substation Automation: AbstractmeraatNoch keine Bewertungen

- Designing A Deterministic Ethernet NetworkDokument10 SeitenDesigning A Deterministic Ethernet NetworkAhmed KhairiNoch keine Bewertungen

- RSRC TEL Making Substations PaperDokument9 SeitenRSRC TEL Making Substations PaperCrit TandNoch keine Bewertungen

- RostanCAN/CANopen To EtherCAT Gateways: Requirements and SolutionsDokument7 SeitenRostanCAN/CANopen To EtherCAT Gateways: Requirements and SolutionsdracunciliasizNoch keine Bewertungen

- Concept of IEC61850 Standard and Sub-Station AutomationDokument2 SeitenConcept of IEC61850 Standard and Sub-Station AutomationSandesh ThapaNoch keine Bewertungen

- 0-Gist of Industrial NetworkingDokument12 Seiten0-Gist of Industrial NetworkingsuritataNoch keine Bewertungen

- The Concept of IEC 61850Dokument7 SeitenThe Concept of IEC 61850reva_rkNoch keine Bewertungen

- Intelligent Electronic DeviceDokument17 SeitenIntelligent Electronic Devicesandeep_chauhan3770100% (1)

- Analysis of An IEC 61850 Based Electric Substation Communication ArchitectureDokument6 SeitenAnalysis of An IEC 61850 Based Electric Substation Communication ArchitectureHari NairNoch keine Bewertungen

- Iec 61850 - Communication Networks and Systems in SubstationsDokument16 SeitenIec 61850 - Communication Networks and Systems in SubstationsCamiloNoch keine Bewertungen

- OP002 Switchgear Optimization Using IEC 61850-9-2 and Non-Conventional MeasurementsDokument8 SeitenOP002 Switchgear Optimization Using IEC 61850-9-2 and Non-Conventional MeasurementsAdamNoch keine Bewertungen

- Converged NetworksDokument10 SeitenConverged Networksganjuvivek85Noch keine Bewertungen

- Integrating Scada, Load Shedding, and High-Speed Controls On An Ethernet Network at A North American RefineryDokument9 SeitenIntegrating Scada, Load Shedding, and High-Speed Controls On An Ethernet Network at A North American RefineryabdullahNoch keine Bewertungen

- Substation Automation and SCADA ProtocolsDokument6 SeitenSubstation Automation and SCADA ProtocolsDrAshok Kumar TiwariNoch keine Bewertungen

- 2010-Smart High Voltage Substation Based On IEC 61850 Process Bus and IEEE 1588 Time Synchronization PDFDokument6 Seiten2010-Smart High Voltage Substation Based On IEC 61850 Process Bus and IEEE 1588 Time Synchronization PDFNhật TàiNoch keine Bewertungen

- Chapter 2 - IoT Technologies - IoT Use Cases and TechnologiesDokument18 SeitenChapter 2 - IoT Technologies - IoT Use Cases and TechnologiesutpolaNoch keine Bewertungen

- Communication Protocols PDFDokument14 SeitenCommunication Protocols PDFChethan SNoch keine Bewertungen

- Development of CC-Link IE Field Network: 1 GbpsDokument4 SeitenDevelopment of CC-Link IE Field Network: 1 GbpsJun JoenNoch keine Bewertungen

- IEC 60870-5-104 - The New Solution For Communication in SubstationsDokument5 SeitenIEC 60870-5-104 - The New Solution For Communication in SubstationsrmbalcobiaNoch keine Bewertungen

- Unit 3 - Internet of Things - WWW - Rgpvnotes.inDokument7 SeitenUnit 3 - Internet of Things - WWW - Rgpvnotes.inShivam Pratap Singh RajawatNoch keine Bewertungen

- Iec 61850Dokument8 SeitenIec 61850Indra Utama IchsanNoch keine Bewertungen

- Industrial Fieldbus Technologies Understanding The BasicsDokument13 SeitenIndustrial Fieldbus Technologies Understanding The Basicsdjeff71100% (1)

- An Inside Look at Industrial Ethernet Communication ProtocolsDokument6 SeitenAn Inside Look at Industrial Ethernet Communication Protocolss_waqarNoch keine Bewertungen

- Substation Automation System Using IEC 61850: S.Roostaee, R.Hooshmand, and Mohammad AtaeiDokument5 SeitenSubstation Automation System Using IEC 61850: S.Roostaee, R.Hooshmand, and Mohammad AtaeiDeddy Ardyansyah Regz GedanganNoch keine Bewertungen

- Enhancement of Industrial Ethernet Performance Using Multicasting/VLAN TechniquesDokument6 SeitenEnhancement of Industrial Ethernet Performance Using Multicasting/VLAN Techniquesraghavendran raghuNoch keine Bewertungen

- Future Generation Computer Systems: Peng Zeng Zhaowei Wang Zhengyi Jia Linghe Kong Dong Li Xi JinDokument10 SeitenFuture Generation Computer Systems: Peng Zeng Zhaowei Wang Zhengyi Jia Linghe Kong Dong Li Xi JinestalinNoch keine Bewertungen

- 03 APS2020 Performance Evaluation of A NCIT in A Laboratory SetDokument6 Seiten03 APS2020 Performance Evaluation of A NCIT in A Laboratory Setali ahmadNoch keine Bewertungen

- Exploration Accessing WAN Chapter1Dokument21 SeitenExploration Accessing WAN Chapter1Reymond D. SeNoch keine Bewertungen

- 6.IJAEST Vol No 5 Issue No 1 Distributed Data Acquisition and Control System Based On Low Cost Embedded Web Servers 053 056Dokument4 Seiten6.IJAEST Vol No 5 Issue No 1 Distributed Data Acquisition and Control System Based On Low Cost Embedded Web Servers 053 056iserpNoch keine Bewertungen

- The Industrial EthernetDokument4 SeitenThe Industrial EthernetRaul GonzalezNoch keine Bewertungen

- Importance of IED Performance On Process Bus Applications L.B. Oliveira, C.A. Dutra, L.G. Silveira, I.H. Cruz, S. Richards Alstom Grid Brazil, UkDokument62 SeitenImportance of IED Performance On Process Bus Applications L.B. Oliveira, C.A. Dutra, L.G. Silveira, I.H. Cruz, S. Richards Alstom Grid Brazil, UkJose Rafael CastroNoch keine Bewertungen

- Real Time Operation of Iec 61850 Based Digital Substationinternational Journal of Engineering and Advanced TechnologyDokument6 SeitenReal Time Operation of Iec 61850 Based Digital Substationinternational Journal of Engineering and Advanced TechnologyHugoNoch keine Bewertungen

- Wireless Controller of BluetoothDokument4 SeitenWireless Controller of Bluetoothanon_163071217Noch keine Bewertungen

- Related Virtual Exhibits: Nortel NetworksDokument17 SeitenRelated Virtual Exhibits: Nortel NetworksmabvieiraNoch keine Bewertungen

- Mission Critical Utilities Network Teleprotection AppNoteDokument15 SeitenMission Critical Utilities Network Teleprotection AppNoteBook LoverNoch keine Bewertungen

- MOXA White Paper Turbo ChainDokument11 SeitenMOXA White Paper Turbo ChainErickReyesNoch keine Bewertungen

- L2 - INP-Ethernet-Based Industrial Protocols 2Dokument30 SeitenL2 - INP-Ethernet-Based Industrial Protocols 2nounkhayNoch keine Bewertungen

- IO-Link Wireless Enhanced Sensors and Actuators For Industry 4.0 NetworksDokument5 SeitenIO-Link Wireless Enhanced Sensors and Actuators For Industry 4.0 NetworksJonathan HopkinsNoch keine Bewertungen

- EtherCAT IntroductionDokument11 SeitenEtherCAT IntroductionVishnu R NairNoch keine Bewertungen

- Transmission Network SynchronizationDokument11 SeitenTransmission Network Synchronizationtxcuongit88Noch keine Bewertungen

- Pi White Paper Profinet It en v1 0Dokument28 SeitenPi White Paper Profinet It en v1 0Rafiul IslamNoch keine Bewertungen

- Overview of Iec61850 and BenefitsDokument8 SeitenOverview of Iec61850 and BenefitsdivaNoch keine Bewertungen

- Indusrial Ethernet: Powerlink Ou EtherCAT?Dokument36 SeitenIndusrial Ethernet: Powerlink Ou EtherCAT?Marco AntonioNoch keine Bewertungen

- SasDokument6 SeitenSasRaviteja Nowduru100% (1)

- Enabling Process Bus Communication For Digital Substations Using 5G Wireless SystemDokument8 SeitenEnabling Process Bus Communication For Digital Substations Using 5G Wireless SystemMarques SilvaNoch keine Bewertungen

- A Simple Introduction To Ergodic Theory: Karma Dajani and Sjoerd Dirksin December 18, 2008Dokument145 SeitenA Simple Introduction To Ergodic Theory: Karma Dajani and Sjoerd Dirksin December 18, 2008openid_AePkLAJcNoch keine Bewertungen

- Distributed File Systems: Pavel BžochDokument36 SeitenDistributed File Systems: Pavel Bžochopenid_AePkLAJcNoch keine Bewertungen

- Introduction To Nuclear Reactors, Fuels, and Materials: Heather J. Maclean Chichester, PH.DDokument62 SeitenIntroduction To Nuclear Reactors, Fuels, and Materials: Heather J. Maclean Chichester, PH.Dopenid_AePkLAJcNoch keine Bewertungen

- The Symmetry of A Tiling: March 21, 2014Dokument20 SeitenThe Symmetry of A Tiling: March 21, 2014openid_AePkLAJcNoch keine Bewertungen

- Effect of Different Design Parameters On Lift, Thrust and Drag of An OrnithopterDokument6 SeitenEffect of Different Design Parameters On Lift, Thrust and Drag of An Ornithopteropenid_AePkLAJcNoch keine Bewertungen

- D. A. Bayer: The Nonlinear Geometry of Linear Programming I. Affine and Projective Scaling TrajectoriesDokument44 SeitenD. A. Bayer: The Nonlinear Geometry of Linear Programming I. Affine and Projective Scaling Trajectoriesopenid_AePkLAJcNoch keine Bewertungen

- B-Splines and Control Theory: Hiroyuki Kano Magnus Egerstedt Hiroaki Nakata Clyde F. MartinDokument24 SeitenB-Splines and Control Theory: Hiroyuki Kano Magnus Egerstedt Hiroaki Nakata Clyde F. Martinopenid_AePkLAJcNoch keine Bewertungen

- CUDA 2D Stencil Computations For The Jacobi Method: Jos e Mar Ia Cecilia, Jos e Manuel Garc Ia, and Manuel Ujald OnDokument4 SeitenCUDA 2D Stencil Computations For The Jacobi Method: Jos e Mar Ia Cecilia, Jos e Manuel Garc Ia, and Manuel Ujald Onopenid_AePkLAJcNoch keine Bewertungen

- K BonacciDokument14 SeitenK Bonacciopenid_AePkLAJcNoch keine Bewertungen

- 08 0412Dokument21 Seiten08 0412openid_AePkLAJcNoch keine Bewertungen

- Dynrel PDFDokument167 SeitenDynrel PDFopenid_AePkLAJcNoch keine Bewertungen

- Sample Assessment - Gap AnalysisDokument7 SeitenSample Assessment - Gap AnalysisKukuh WidodoNoch keine Bewertungen

- Heating and Cooling of Buildings: Design For EfficiencyDokument16 SeitenHeating and Cooling of Buildings: Design For EfficiencyAmer GaladNoch keine Bewertungen

- 3.5 Instruction Formats: Three-Address MachinesDokument4 Seiten3.5 Instruction Formats: Three-Address Machinesلطيف احمد حسنNoch keine Bewertungen

- New Energy Efficient Car Built With 3d PrintingDokument3 SeitenNew Energy Efficient Car Built With 3d PrintingKarthi KNoch keine Bewertungen

- 5101 - ITS Chapter 2 Two PDFDokument41 Seiten5101 - ITS Chapter 2 Two PDFAkshay SinghNoch keine Bewertungen

- Etsi Eg 202 057-1Dokument34 SeitenEtsi Eg 202 057-1Dusan JokanovicNoch keine Bewertungen

- Manual de Variador de Velocidad WEG VECTORDokument32 SeitenManual de Variador de Velocidad WEG VECTORSamuel Miranda PintoNoch keine Bewertungen

- AMS Suite Machinery Health Manager - Installation Guide PDFDokument72 SeitenAMS Suite Machinery Health Manager - Installation Guide PDFJose Prado50% (2)

- Precision t1600 Spec SheetDokument2 SeitenPrecision t1600 Spec SheetGongo ZaNoch keine Bewertungen

- Webster - THE BEDOUIN IN SOUTHERN AND SOUTHEASTERN ARABIA The Evolution of Bedouin LifereconsideredDokument15 SeitenWebster - THE BEDOUIN IN SOUTHERN AND SOUTHEASTERN ARABIA The Evolution of Bedouin LifereconsideredRaas4555Noch keine Bewertungen

- 3 đề giữa kì e6Dokument6 Seiten3 đề giữa kì e6stu725701106Noch keine Bewertungen

- LCS Architecture For LTE EPSDokument3 SeitenLCS Architecture For LTE EPSgare69Noch keine Bewertungen

- Hettich FinalDokument44 SeitenHettich FinalManik LatawaNoch keine Bewertungen

- IDoc Basics For Functional ConsultantsDokument16 SeitenIDoc Basics For Functional ConsultantsKaran KumarNoch keine Bewertungen

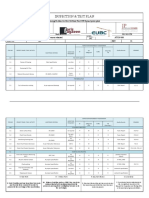

- Inspection & Test PlanDokument2 SeitenInspection & Test PlanKhaled GamalNoch keine Bewertungen

- Defensive Programming To Reduce PHP VulnerabilitiesDokument5 SeitenDefensive Programming To Reduce PHP VulnerabilitiessureshNoch keine Bewertungen

- Tolerancias FEM y Autoportantes 1Dokument53 SeitenTolerancias FEM y Autoportantes 1ybusomNoch keine Bewertungen

- DESERTATIONADIDokument30 SeitenDESERTATIONADIAdinah AnisNoch keine Bewertungen

- 1st Periodical Test in ICT - ProProfs Quiz PDFDokument10 Seiten1st Periodical Test in ICT - ProProfs Quiz PDFShaweya Sabturain Kasim SabturainNoch keine Bewertungen

- The Sims Medieval CheatsDokument5 SeitenThe Sims Medieval CheatskaizhoNoch keine Bewertungen

- Econ Ball Valves Carbon Steel Stainless SteelDokument1 SeiteEcon Ball Valves Carbon Steel Stainless SteelChristianGuerreroNoch keine Bewertungen

- Unit 1: Compiled With Reference From: Software Testing Techniques: Boris Beizer Craft of Software Testing: Brain MarrickDokument68 SeitenUnit 1: Compiled With Reference From: Software Testing Techniques: Boris Beizer Craft of Software Testing: Brain MarrickAjay100% (1)

- Learning Oracle Glassfish Server For Tomcat Users: An Oracle White Paper May 2010Dokument10 SeitenLearning Oracle Glassfish Server For Tomcat Users: An Oracle White Paper May 2010Amila KumanayakeNoch keine Bewertungen

- Royal Quay BrochureDokument8 SeitenRoyal Quay Brochureapi-26419872Noch keine Bewertungen

- Overview of A VPN: Dial This Initial Connection, and Then Click Your Dial-Up Internet ConnectionDokument4 SeitenOverview of A VPN: Dial This Initial Connection, and Then Click Your Dial-Up Internet ConnectionSwadi RajeswarNoch keine Bewertungen

- PART3 - Quality Control Manual On Concrete WorksDokument101 SeitenPART3 - Quality Control Manual On Concrete WorksKelvin NgugiNoch keine Bewertungen