Beruflich Dokumente

Kultur Dokumente

ABB ICSTT-SDS-8110 - en Plantguard TMR Processor P8110

Hochgeladen von

salic2013Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

ABB ICSTT-SDS-8110 - en Plantguard TMR Processor P8110

Hochgeladen von

salic2013Copyright:

Verfügbare Formate

ABB.

ICSTT-SDS-8110

3/$17*8$5' TMR Controller

3ODQWJXDUG TMR Processor-P8110

Dec 2002

FRONT PANEL

DESCRIPTION

3ODQWJXDUG TMR Processors

contain and execute the operating and

application software programs in a

triple redundant, fault tolerant

controller system..

The fault tolerant design contains

six fault containment regions. The

three synchronized processor fault

containment regions each contain a

600 series microprocessor, its

memory, voter, and associated

circuits.

The non-volatile memory is used

to store the configuration and

application programs for the system.

Each processor has an

independent power supply fed from

the dual-redundant 24Vdc power

supply of the 3ODQWJXDUG Controller

chassis backplane. The processor

power supplies provide short circuit

protection and regulated power to the

module electronics.

The processors operate

concurrently to achieve triple

modular redundancy and fault

tolerance. By providing 2-out-of-3

hardware voting on every inter-

processor exchange and memory data

retrieval, uncompromised fault

detection and error-free operation are

assured.

3ODQWJXDUG TMR Processors

communicate with other modules via

a backplane mounted, triplicated

Inter-Module Bus. Additionally,

interface modules are used to support

communication with I/O sub-systems

and other equipment.

Module faults are automatically

detected, time-stamped, and stored

for historical review. Transient

faults, once they are recorded, are

cleared automatically without

nuisance alarming. Permanent faults

in a processor are annunciated on the

front panel of the module, without

disturbing on-going processing in the

two remaining processors.

When a failed 3ODQWJXDUG TMR

Processor is replaced, the

replacement module is automatically

initialized without external loaders or

other equipment.

Application programs are developed

using the full suite of IEC 1131-3

languages. The user can load, run,

stop, single-step or delete the

application program. A front panel

maintenance enable keyswitch allows

the download of application

programs.

FEATURES

Triple modular redundant, Iault

tolerant 3-2-0 operation

Two-out-oI-three voting on

internal operations

Automatic Iault handling

without nuisance alarming

3ODQWJXDUG Operating System

kernel (IEC 61508 SIL3)

Time-stamped Iault historian

Module replacement without

program down-loading

Non-volatile memory Ior

program storage

Full suite oI IEC 1131-3

languages

Multiple process program

execution

TV certiIied Ior saIety, SIL3

ABB.ICSTT-SDS-8110

3/$17*8$5' TMR Controller

3ODQWJXDUG TRM Processor-P8110

ABB

Technical data sheets are intended for

information and guidance. ABB has a policy of

continual product development and

improvement. Specifications are subject to

change without notice.

BLOCK DIAGRAM

ELECTRICAL SPECIFICATION

Voltage Range 20 to 32V dc

Maximum Load 75W

Heat Dissipation 70W

Use With Chassis T8100

Processor Clock 50MHz

Memory Type And Size

DRAM

EPROM

FLASH

NVRAM

8MB/16MB/32MB/64MB EDO 60ns

512kB

2MB/4MB

128kB

I/O InterIace Triple redundant Inter-Module Bus

MECHANICAL

SPECIFICATION

Dimensions (HxWxD):

241mm x 90mm x 300mm

(9.5ins x 3.6ins x 11.8ins)

Weight:

2.71kg (5.95lbs)

ENVIROMENTAL

Operating Temperature:

-5C to 60C

(23F to 140F)

Operating Humidity:

5 to 95%, non-condensing

Vibration:

10 to 57Hz 0.075mm

57 to 150Hz 1.0g

Shock:

15g, sine wave, 11ms

EMI (IEC 801):

ESD

Air discharge to 15kV

Contact discharge to 8kV

Radiated Fields

10V/m, 27MHz to

500MHz

Transients and Bursts

2kV, 2.5kHz for

t=60 seconds

Das könnte Ihnen auch gefallen

- Pir Sensor Based Energy SaverDokument76 SeitenPir Sensor Based Energy Saverk.aparna100% (1)

- Anti Theft System For Valuable Items Using LDRDokument6 SeitenAnti Theft System For Valuable Items Using LDRKethavath Sakrunaik KNoch keine Bewertungen

- Course Title Microprocessor SystemDokument20 SeitenCourse Title Microprocessor SystemElmustafa Sayed Ali AhmedNoch keine Bewertungen

- 0506 PCX-2 V0106 enDokument127 Seiten0506 PCX-2 V0106 enspale82Noch keine Bewertungen

- VCD-D ManualDokument13 SeitenVCD-D ManualnimmuhkNoch keine Bewertungen

- Mcs 014 Systeem Design PDFDokument10 SeitenMcs 014 Systeem Design PDFMuthukrishnan NNoch keine Bewertungen

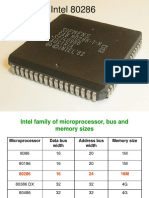

- Intel 80286Dokument24 SeitenIntel 80286Rajesh PatelNoch keine Bewertungen

- Lab 1 - OLED, GPIO, InterruptDokument6 SeitenLab 1 - OLED, GPIO, Interruptprakash_shrNoch keine Bewertungen

- Analysis of A High-Potential Business: Sqreen: Application Security Management PlatformDokument13 SeitenAnalysis of A High-Potential Business: Sqreen: Application Security Management Platformhinaya khanNoch keine Bewertungen

- 1769-If4I Analog Input ModuleDokument24 Seiten1769-If4I Analog Input ModuleHilder Ramirez PuellesNoch keine Bewertungen

- Lecture 6Dokument10 SeitenLecture 6Elmustafa Sayed Ali AhmedNoch keine Bewertungen

- Two-Wire Peripheral Expansion For The AT89C2051 MicrocontrollerDokument9 SeitenTwo-Wire Peripheral Expansion For The AT89C2051 MicrocontrollerVlaovic GoranNoch keine Bewertungen

- 80286Dokument28 Seiten80286Kavitha SubramaniamNoch keine Bewertungen

- Manual SMC Dialog Plus Controller. Allen BradleyDokument189 SeitenManual SMC Dialog Plus Controller. Allen BradleygreenlinexNoch keine Bewertungen

- Masibus 8208 ManualDokument36 SeitenMasibus 8208 ManualCraig Godfrey100% (1)

- GT30 ManualDokument83 SeitenGT30 ManualJerry ReddenNoch keine Bewertungen

- 65 KVA Perkins Diesel Generator Set - Non EPA - 50Hz TP-P65-T1-50Dokument5 Seiten65 KVA Perkins Diesel Generator Set - Non EPA - 50Hz TP-P65-T1-50AbdaljaleelAlqazeeNoch keine Bewertungen

- P211 en M A31Dokument64 SeitenP211 en M A31Koustav DasguptaNoch keine Bewertungen

- Max DemandDokument11 SeitenMax DemanddwarakeshNoch keine Bewertungen

- EMBEDDED BASED Automatic AUDITORIUM CONTROLLER 0TH REVDokument36 SeitenEMBEDDED BASED Automatic AUDITORIUM CONTROLLER 0TH REVspringsource100% (1)

- Romana T-3805-EDokument19 SeitenRomana T-3805-EjorgeNoch keine Bewertungen

- 80286Dokument74 Seiten80286Arannya MonzurNoch keine Bewertungen

- Basic ComputerDokument22 SeitenBasic ComputerKashyap Sompura100% (1)

- Intel 80286 Programmer ModelDokument276 SeitenIntel 80286 Programmer ModelsreepadaravikumarNoch keine Bewertungen

- #Ped Lab 03Dokument24 Seiten#Ped Lab 03akilaNoch keine Bewertungen

- ES Series Hardware Manual170413Dokument64 SeitenES Series Hardware Manual170413Oscar MontañezNoch keine Bewertungen

- 8085 Microproceesor - PPTDokument59 Seiten8085 Microproceesor - PPTShanagonda Manoj KumarNoch keine Bewertungen

- EPM Manual Model 42iDokument347 SeitenEPM Manual Model 42ichaling3Noch keine Bewertungen

- Mge Upsilon Sts - BrochureDokument4 SeitenMge Upsilon Sts - BrochureMetalloyNoch keine Bewertungen

- Renesas Flash Programmer Sample Circuit For Programming PC Serial PDFDokument5 SeitenRenesas Flash Programmer Sample Circuit For Programming PC Serial PDFAjay J VermaNoch keine Bewertungen

- R01an0239ej sh7125Dokument35 SeitenR01an0239ej sh7125ArmanNoch keine Bewertungen

- DsPIC30F4011 - Robotics 3Dokument33 SeitenDsPIC30F4011 - Robotics 3Senthil Kumar100% (1)

- Debugger Hc12Dokument52 SeitenDebugger Hc12carver_uaNoch keine Bewertungen

- D2-250-1 Key Features: DL250-1 CPUDokument3 SeitenD2-250-1 Key Features: DL250-1 CPUVladimir Aliro Quezada CidNoch keine Bewertungen

- 9619 Philips 32PFL3605 42PFL3605 Chassis RAM1 0A LA Televisor LCD Manual de Servicio PDFDokument66 Seiten9619 Philips 32PFL3605 42PFL3605 Chassis RAM1 0A LA Televisor LCD Manual de Servicio PDFMaya Tes100% (1)

- The VLSI Ruby II Advanced Communication ProcessorDokument1 SeiteThe VLSI Ruby II Advanced Communication ProcessorvlkumashankardeekshithNoch keine Bewertungen

- LPKF ProtoMat S103Dokument2 SeitenLPKF ProtoMat S103jhonny639Noch keine Bewertungen

- Auto ShiftDokument56 SeitenAuto Shiftshaikintiyazsultana0% (1)

- 84.vehicle Superintending System With Voice Feedback DocuDokument88 Seiten84.vehicle Superintending System With Voice Feedback DocuMoluguri KirankumarNoch keine Bewertungen

- Flyer - PCS-9691E Overcurrent Relay PDFDokument2 SeitenFlyer - PCS-9691E Overcurrent Relay PDFscottsaw50% (2)

- RC5 Protocol Decoding With 8051 Microcontroller (Embedded C) - ProEmbSys TechnologiesDokument4 SeitenRC5 Protocol Decoding With 8051 Microcontroller (Embedded C) - ProEmbSys TechnologieskhhoaNoch keine Bewertungen

- Micro Controller and Embedded Systems (Revised)Dokument2 SeitenMicro Controller and Embedded Systems (Revised)Ashok ShahNoch keine Bewertungen

- C40 Trace Manual EnglishDokument24 SeitenC40 Trace Manual EnglishBertNoch keine Bewertungen

- 05 4 ServomotorsDokument118 Seiten05 4 ServomotorsJosé Carlos Macavilca RománNoch keine Bewertungen

- General Gps Vehicle Tracker Wetrack2 User ManualDokument20 SeitenGeneral Gps Vehicle Tracker Wetrack2 User ManualDanang Irawan0% (1)

- Ec2304 LP III EceDokument5 SeitenEc2304 LP III EcesunvenkatNoch keine Bewertungen

- k120s K7MDR14UE ManualDokument11 Seitenk120s K7MDR14UE ManualAhmed Hebeshe100% (1)

- 23 Rapiscan Mvxr5000 CBTDokument2 Seiten23 Rapiscan Mvxr5000 CBTAnonymous abOKZAaNoch keine Bewertungen

- 78K0-KB2 Sample ProgramDokument58 Seiten78K0-KB2 Sample ProgramAnonymous pu1L9ZNoch keine Bewertungen

- Multiple Transformers Oil Temperature Monitoring With Automatic CircuitDokument25 SeitenMultiple Transformers Oil Temperature Monitoring With Automatic CircuitPrem Narayan Singh100% (1)

- Chapter 1: Introduction To HCS12/MC9S12 The HCS12 Microcontroller Han-Way Huang Minnesota State University, Mankato September 2009Dokument31 SeitenChapter 1: Introduction To HCS12/MC9S12 The HCS12 Microcontroller Han-Way Huang Minnesota State University, Mankato September 2009Omar LopezNoch keine Bewertungen

- 99.automatic Auditorium ControllingDokument3 Seiten99.automatic Auditorium ControllingDinesh DspNoch keine Bewertungen

- Seminar ReportDokument26 SeitenSeminar Reportharishk03Noch keine Bewertungen

- Active Disturbance Rejection Control for Nonlinear Systems: An IntroductionVon EverandActive Disturbance Rejection Control for Nonlinear Systems: An IntroductionNoch keine Bewertungen

- ABB ICSTT-SDS-8151 - en Plantguard Communications Interface P8151Dokument2 SeitenABB ICSTT-SDS-8151 - en Plantguard Communications Interface P8151salic2013Noch keine Bewertungen

- Td02600004e Emr-4000Dokument20 SeitenTd02600004e Emr-4000CristhJuliang100% (1)

- Efm32G890 Datasheet: EFM32G890 Microcontrollers Are Suited For All Battery Operated ApplicationsDokument71 SeitenEfm32G890 Datasheet: EFM32G890 Microcontrollers Are Suited For All Battery Operated ApplicationsamerosperosNoch keine Bewertungen

- ATxmega 128 A3 UDokument141 SeitenATxmega 128 A3 UsanapashokNoch keine Bewertungen

- 3bnp004720r101.PDF - en Triguard 2 TMR Safety ProductsDokument20 Seiten3bnp004720r101.PDF - en Triguard 2 TMR Safety ProductsluispedrojrNoch keine Bewertungen

- ABB ICSTT-SDS-8100 - en Plantguard Controller Chassis P8100Dokument2 SeitenABB ICSTT-SDS-8100 - en Plantguard Controller Chassis P8100salic2013Noch keine Bewertungen

- Notifier Nfs 3030 Install ManualDokument68 SeitenNotifier Nfs 3030 Install Manualgndurango100% (1)

- Volkswagen RNS 510 Pin AssignmentsDokument4 SeitenVolkswagen RNS 510 Pin Assignmentssalic2013Noch keine Bewertungen

- Volkswagen RCD 510 Pin AssignmentsDokument4 SeitenVolkswagen RCD 510 Pin Assignmentssalic2013100% (1)

- Connection: 4xwire +12V GND CAN High Can Low Gateway TPMS ControllerDokument2 SeitenConnection: 4xwire +12V GND CAN High Can Low Gateway TPMS Controllersalic2013Noch keine Bewertungen

- Connection: 4xwire +12V GND CAN High Can Low Gateway TPMS ControllerDokument2 SeitenConnection: 4xwire +12V GND CAN High Can Low Gateway TPMS Controllersalic2013Noch keine Bewertungen

- PCS 7 APACS OS Symbols and Faceplates V6.1Dokument66 SeitenPCS 7 APACS OS Symbols and Faceplates V6.1salic2013Noch keine Bewertungen

- DN 6724Dokument4 SeitenDN 6724Venkata SureshKumar KanuboyinaNoch keine Bewertungen

- Design Guide c07-462879Dokument52 SeitenDesign Guide c07-462879salic2013Noch keine Bewertungen

- Assessing The Sukhoi PAKDokument46 SeitenAssessing The Sukhoi PAKsalic2013Noch keine Bewertungen

- Valeo Passenger Cars & LCV Security Systems 2012 2013 Catalogue 956216Dokument40 SeitenValeo Passenger Cars & LCV Security Systems 2012 2013 Catalogue 956216salic2013Noch keine Bewertungen

- Test Butane Sphere SwitchingDokument1 SeiteTest Butane Sphere Switchingsalic2013Noch keine Bewertungen

- 111-D-1005 Feed Surge Drum: NotesDokument1 Seite111-D-1005 Feed Surge Drum: Notessalic2013Noch keine Bewertungen

- Coking 101Dokument26 SeitenCoking 101digecaNoch keine Bewertungen

- ESD System OperationDokument53 SeitenESD System Operationsalic2013100% (1)

- Mass Flow Vs Volumetric Flow and Unit ConversionDokument4 SeitenMass Flow Vs Volumetric Flow and Unit ConversionAinur RohmanNoch keine Bewertungen

- 3kxf800000r4201-42 18 401 en C 03 2012Dokument44 Seiten3kxf800000r4201-42 18 401 en C 03 2012salic2013Noch keine Bewertungen

- MS 02 160Dokument6 SeitenMS 02 160salic2013Noch keine Bewertungen

- HV Induction Motors Technical IEC Catalog FINAL en 092011 LowresDokument152 SeitenHV Induction Motors Technical IEC Catalog FINAL en 092011 LowresSangeet BhandariNoch keine Bewertungen

- Ieh - Chapter 6-9 - Partial-Stroke Testing of Block ValvesDokument24 SeitenIeh - Chapter 6-9 - Partial-Stroke Testing of Block ValvesKareem RasmyNoch keine Bewertungen

- INSTRUCALCDokument1 SeiteINSTRUCALCsalic2013Noch keine Bewertungen

- Appnote Pid ControlDokument2 SeitenAppnote Pid Controlsmkumar33Noch keine Bewertungen

- ValvesDokument24 SeitenValvessalic2013Noch keine Bewertungen

- ValSpeQUserManual 361Dokument199 SeitenValSpeQUserManual 361salic2013Noch keine Bewertungen

- Line Sizing, TRV Sizing SampleDokument20 SeitenLine Sizing, TRV Sizing Samplesalic2013Noch keine Bewertungen

- Brochure Simatic-Controller enDokument104 SeitenBrochure Simatic-Controller enMiloš PopovićNoch keine Bewertungen

- 2949 HSE Risk Register - 2013-06-16 RevD1-VB FreeDokument3 Seiten2949 HSE Risk Register - 2013-06-16 RevD1-VB Freesalic201388% (8)

- Dandzi SiewertDokument17 SeitenDandzi Siewertsalic2013Noch keine Bewertungen

- AXENMS0045Dokument72 SeitenAXENMS0045shareyhouNoch keine Bewertungen

- CAP Exam Application-English 2-18-10 With Fields and CAPDokument8 SeitenCAP Exam Application-English 2-18-10 With Fields and CAPsalic2013Noch keine Bewertungen

- CAP Short PresentationDokument12 SeitenCAP Short Presentationsalic2013Noch keine Bewertungen

- Survey 2 Module 2Dokument76 SeitenSurvey 2 Module 2veereshNoch keine Bewertungen

- Pre-Placement Training Program: Sample Profiling (All About You)Dokument2 SeitenPre-Placement Training Program: Sample Profiling (All About You)RISHAV RAJ GUPTANoch keine Bewertungen

- Review Chapter 2Dokument46 SeitenReview Chapter 2JennysanNoch keine Bewertungen

- Uniden Bearcat Scanner BC365CRS Owners ManualDokument32 SeitenUniden Bearcat Scanner BC365CRS Owners ManualBenjamin DoverNoch keine Bewertungen

- CertificateofAnalysis 2019 11 9 879766Dokument2 SeitenCertificateofAnalysis 2019 11 9 879766Trọng TínNoch keine Bewertungen

- Hydraulics Laboratory ManualDokument37 SeitenHydraulics Laboratory ManualHarold Taylor100% (2)

- 16 Advantages & 10 Disadvantages of Solar Panels in 2022Dokument29 Seiten16 Advantages & 10 Disadvantages of Solar Panels in 2022xaxinev359100% (1)

- European Foundation Design For Seasonally Frozen GroundDokument127 SeitenEuropean Foundation Design For Seasonally Frozen GroundLevente SikoNoch keine Bewertungen

- ABB - Composite Station Post InsulatorsDokument6 SeitenABB - Composite Station Post InsulatorsDominic SantiagoNoch keine Bewertungen

- Thermo 5th Chap17 P096Dokument19 SeitenThermo 5th Chap17 P096UTA - Std - Elvin ChantreNoch keine Bewertungen

- Management Information Systems and Corporate Decision - Making: A Literature ReviewDokument5 SeitenManagement Information Systems and Corporate Decision - Making: A Literature Reviewvaaz205Noch keine Bewertungen

- Acc Inter 3 AtsiriDokument9 SeitenAcc Inter 3 AtsiriZania Putri100% (1)

- Indian Council of Medical ResearchDokument6 SeitenIndian Council of Medical Researchram_naik_1Noch keine Bewertungen

- Sharp Service Manual Models Lc-40sh340k and Lc-40sh340e With Chassis 17mb60Dokument106 SeitenSharp Service Manual Models Lc-40sh340k and Lc-40sh340e With Chassis 17mb60murtibing100% (1)

- GS at CPP HuyHoang CodeDokument285 SeitenGS at CPP HuyHoang CodeTran Bach DangNoch keine Bewertungen

- Assignment 1Dokument12 SeitenAssignment 1Santosh SubramanyaNoch keine Bewertungen

- SSPC Monitoreo y Control de Condiciones AmbientalesDokument4 SeitenSSPC Monitoreo y Control de Condiciones AmbientalesRony Ruiz100% (1)

- Rack Interface Module 3500 20SDokument71 SeitenRack Interface Module 3500 20SmaheshNoch keine Bewertungen

- Thing in Itself Kantian: AnstoßDokument1 SeiteThing in Itself Kantian: Anstoßwhynotbequiet23Noch keine Bewertungen

- Lister Hr3 ManualDokument119 SeitenLister Hr3 ManualRichard Gomez Cueva100% (2)

- Department of Education: Activity Completion ReportDokument1 SeiteDepartment of Education: Activity Completion ReportJanineJavier100% (1)

- Grade 4 SYLLABUS Check Point 1Dokument2 SeitenGrade 4 SYLLABUS Check Point 1Muhammad HassaanNoch keine Bewertungen

- Data Science: Lecture #1Dokument22 SeitenData Science: Lecture #1khanjan varmaNoch keine Bewertungen

- Overseas Assignment 18thseptDokument6 SeitenOverseas Assignment 18thseptSuresh VanierNoch keine Bewertungen

- BCO120Dokument3 SeitenBCO120erwin_simsensohnNoch keine Bewertungen

- Staffing ProcessDokument18 SeitenStaffing ProcessEbtesam EliasNoch keine Bewertungen

- Metaphor-Spatiality-Discourse - 10-11 July 2020 - Programme - FINALDokument6 SeitenMetaphor-Spatiality-Discourse - 10-11 July 2020 - Programme - FINALkostyelNoch keine Bewertungen

- Chapter7 Ex PDFDokument5 SeitenChapter7 Ex PDFSathish Kumar100% (1)

- Topic 2 Evidencias Clase 7 L Reading - Young PilotsDokument4 SeitenTopic 2 Evidencias Clase 7 L Reading - Young PilotsJam C. PoloNoch keine Bewertungen

- Learner's Book Answers: Unit 1 CellsDokument31 SeitenLearner's Book Answers: Unit 1 CellsLyaz Antony91% (91)