Beruflich Dokumente

Kultur Dokumente

High-Performance CCSDS AOS Protocol Implementation in FPGA

Hochgeladen von

Deepa DevarajOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

High-Performance CCSDS AOS Protocol Implementation in FPGA

Hochgeladen von

Deepa DevarajCopyright:

Verfügbare Formate

High-Performance CCSDS AOS Protocol Implementation in FPGA

Telemetry receivers can use this implementation to process telemetry at high rates.

NASAs Jet Propulsion Laboratory, Pasadena, California

The Consultative Committee for Space Data Systems (CCSDS) Advanced Orbiting Systems (AOS) space data link protocol provides a framing layer between channel coding such as LDPC (low-density parity-check) and higher-layer link multiplexing protocols such as CCSDS Encapsulation Service, which is described in the following article. Recent advancement in RF modem technology has allowed multi-megabit transmission over space links. With this increase in data rate, the CCSDS AOS protocol implementation needs to be optimized to both reduce energy consumption and operate at a high rate. CCSDS AOS has been implemented as an intellectual property core so that the aforementioned problems are solved by way of operating the CCSDS AOS inside a field-programmable gate array (FPGA). The CCSDS AOS in FPGA implementation consists of both framing and deframing features. Features of the AOS Framer include: Fully customizable with respect to insert zone, virtual channel ID, and trailer fields. 8-bit parallel CCITT CRC16 calculation. First header pointer field calculation based on the data provided from the packet layers such as CCSDS Encapsulation Service or CCSDS Space Packet. Optimized for the Packet Service primitives with M_PDU. Available in byte-based or packet-based egress interface options. Statistical counters at both byte and frame levels to facilitate data product accountability. Features of the AOS De-Framer include: Ingress buffer implementation to provide ingress processing overflow. 8-bit parallel CCITT CRC16 calculation and frame discard if CRC16 fails. First header pointer field extraction and forwarding to the de-packetizing layers such as CCSDS Encapsulation Service or CCSDS Packet Service. Optimized for the Packet Service primitives with M_PDU. Statistical counters at both byte and frame levels to facilitate data product accountability. The combination of energy and performance optimization that embodies this design makes the work novel. This work was done by Loren P. Clare, Jordan L. Torgerson, and Jackson Pang of Caltech for NASAs Jet Propulsion Laboratory. For more information, contact iaoffice@jpl.nasa.gov. The software used in this innovation is available for commercial licensing. Please contact Daniel Broderick of the California Institute of Technology at danielb@caltech.edu. Refer to NPO-47166.

Advanced Flip Chips in Extreme Temperature Environments

This technology has application in avionics and electronics packaging.

NASAs Jet Propulsion Laboratory, Pasadena, California

The use of underfill materials is necessary with flip-chip interconnect technology to redistribute stresses due to mismatching coefficients of thermal expansion (CTEs) between dissimilar materials in the overall assembly. Underfills are formulated using organic polymers and possibly inorganic filler materials. There are a few ways to apply the underfills with flip-chip technology. Traditional capillary-flow underfill materials now possess high flow speed and reduced time to cure, but they still require additional processing steps beyond the typical surface-mount technology (SMT) assembly process. Studies were conducted using underfills in a temperature range of -190 to 85 C, which resulted in an increase of reliability by one to two orders of magnitude. Thermal shock of the flip-chip test articles was designed to induce failures at the interconnect sites (-40 to 100 C). The study on the reliability of flip chips using underfills in the extreme temperature region is of significant value for space applications. This technology is considered as an enabling technology for future space missions. Flip-chip interconnect technology is an advanced electrical interconnection approach where the silicon die or chip is electrically connected, face down, to the substrate by reflowing solder bumps on area-array metallized terminals on the die to matching footprints of solder-wettable pads on the chosen substrate. This advanced flip-chip interconnect technology will significantly improve the performance of high-speed systems, productivity enhancement over manual wire bonding, self-alignment during die joining, low lead inductances, and reduced need for attachment of precious metals. The use of commercially developed no-flow fluxing underfills provides a means of reducing the processing steps employed in the traditional capillary flow methods to enhance SMT compatibility. Reliability of flip chips may be significantly increased by matching/tailoring the CTEs of the substrate material and the silicon die or chip, and also the underfill materials. Advanced packaging interconnects technology such as flip-chip interconnect test boards have been subjected to various extreme temperature ranges that cover military specifications and extreme Mars and asteroid environments. The eventual goal of each process step and the entire process is to produce components with 100 percent interconnect and satisfy the reliability requirements. Underfill materials, in general, may possibly meet demanding end use requirements such as low warpage, low stress, fine pitch, high reliability, and high adhesion. This work was done by Rajeshuni Ramesham of Caltech for NASAs Jet Propulsion Laboratory. Further information is contained in a TSP (see page 1). NPO-41181

10

NASA Tech Briefs, September 2010

Das könnte Ihnen auch gefallen

- Design and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesVon EverandDesign and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesNoch keine Bewertungen

- Gallium Nitride-enabled High Frequency and High Efficiency Power ConversionVon EverandGallium Nitride-enabled High Frequency and High Efficiency Power ConversionGaudenzio MeneghessoNoch keine Bewertungen

- Techniques and Technologies For High Frequency InterconnectionsDokument2 SeitenTechniques and Technologies For High Frequency Interconnectionsarunkr1Noch keine Bewertungen

- Flip Chip Challenges: Substrate TechnologyDokument6 SeitenFlip Chip Challenges: Substrate TechnologyvaltemaNoch keine Bewertungen

- Research Statement: Patrick ChiangDokument3 SeitenResearch Statement: Patrick ChiangPardhasaradhi DamarlaNoch keine Bewertungen

- E Thesis Nitrkl AcDokument6 SeitenE Thesis Nitrkl AcRaquel Pellicier100% (1)

- Research Paper On WcdmaDokument8 SeitenResearch Paper On Wcdmab0pitekezab2100% (1)

- Ieee Research Paper On VlsiDokument6 SeitenIeee Research Paper On Vlsiebvjkbaod100% (1)

- Is 25 Gbds On-Board Signaling ViableDokument17 SeitenIs 25 Gbds On-Board Signaling Viablebinayaks248Noch keine Bewertungen

- ArticleDokument6 SeitenArticleMuthuram ANoch keine Bewertungen

- Cmos Comparator ThesisDokument5 SeitenCmos Comparator Thesisannemarieolathe100% (1)

- VLSI SymposiaDokument20 SeitenVLSI SymposiaaetherdexNoch keine Bewertungen

- Multi Chip Modules Technologies: P. Gerlach, C. Linder, K.-H. BecksDokument5 SeitenMulti Chip Modules Technologies: P. Gerlach, C. Linder, K.-H. BecksSadeeq Ali MohammadNoch keine Bewertungen

- Vlsi Thesis PDFDokument8 SeitenVlsi Thesis PDFtmexyhikd100% (2)

- Packaging of Two-Dimensional Smart Arrays: PixelDokument2 SeitenPackaging of Two-Dimensional Smart Arrays: PixelAnil Kumar GorantalaNoch keine Bewertungen

- The Fan-Out Technology On The Advanced PackagingDokument2 SeitenThe Fan-Out Technology On The Advanced PackagingpeterchondroNoch keine Bewertungen

- TTM Immonen08 11Dokument4 SeitenTTM Immonen08 11Santosa Valentinus YusufNoch keine Bewertungen

- Shang 2017Dokument4 SeitenShang 2017Matlab IEEENoch keine Bewertungen

- Part Time Optics in Data CenterDokument12 SeitenPart Time Optics in Data CenterVivekNoch keine Bewertungen

- Research Papers On Cmos TechnologyDokument7 SeitenResearch Papers On Cmos Technologyxmniibvkg100% (1)

- Epfl Thesis JuryDokument6 SeitenEpfl Thesis Jurylisanetkowiczerie100% (2)

- Superchip Packaging Issues For Advanced Signal ProcessorsDokument5 SeitenSuperchip Packaging Issues For Advanced Signal ProcessorsArhip CojocNoch keine Bewertungen

- Data Communication and Computer Networks: Submitted To: Dr. Muhammad Kaleem Ullah Submitted By: Registration #Dokument32 SeitenData Communication and Computer Networks: Submitted To: Dr. Muhammad Kaleem Ullah Submitted By: Registration #marryam nawaz100% (1)

- Wcdma ThesisDokument5 SeitenWcdma Thesisezhj1fd2100% (2)

- Data Communication in Substation Automation (SAS) - Part 3 - Original - 23369Dokument8 SeitenData Communication in Substation Automation (SAS) - Part 3 - Original - 23369Darpan SaxenaNoch keine Bewertungen

- Silicon Photonics: Heterogeneous Integration For High Bandwidth, Efficient ComputingDokument34 SeitenSilicon Photonics: Heterogeneous Integration For High Bandwidth, Efficient ComputingUCSBieeNoch keine Bewertungen

- 3 - D ICsDokument35 Seiten3 - D ICsKhusi ArnavNoch keine Bewertungen

- 3d ICs Full Seminar Report 2Dokument31 Seiten3d ICs Full Seminar Report 2Shweta R Burli0% (1)

- What Is PCB CTIDokument10 SeitenWhat Is PCB CTIjackNoch keine Bewertungen

- Density Optimization For Analog Layout Based On Transistor-ArrayDokument11 SeitenDensity Optimization For Analog Layout Based On Transistor-ArrayJack GengNoch keine Bewertungen

- 45nm Holistic WPDokument8 Seiten45nm Holistic WPkostas_papathNoch keine Bewertungen

- Chapter-1 Wireless Communication - Laser CommunicationDokument56 SeitenChapter-1 Wireless Communication - Laser Communicationyash_dk20083706Noch keine Bewertungen

- 01FW BeverDokument18 Seiten01FW BeverVarun Mech SNoch keine Bewertungen

- 具有嵌入式渐变折射率玻璃波导和光纤 - 柔性端接的大型光学背板Dokument12 Seiten具有嵌入式渐变折射率玻璃波导和光纤 - 柔性端接的大型光学背板jianan yaoNoch keine Bewertungen

- VlsiDokument32 SeitenVlsibalasaravanan0408Noch keine Bewertungen

- Simulation and Implemetation of High-Speed Data Transmission Over Aurora Protocol Using FPGADokument7 SeitenSimulation and Implemetation of High-Speed Data Transmission Over Aurora Protocol Using FPGAIJRASETPublicationsNoch keine Bewertungen

- FULLTEXT01Dokument14 SeitenFULLTEXT01Princess MiraloNoch keine Bewertungen

- I R D S: Nternational Oadmap FOR Evices and YstemsDokument23 SeitenI R D S: Nternational Oadmap FOR Evices and YstemsSnehaNoch keine Bewertungen

- Pipeline Dae S With FeedbackDokument10 SeitenPipeline Dae S With Feedbackyame asfiaNoch keine Bewertungen

- Quality-Of-Service and Error Control Techniques For Mesh-Based Network-On-Chip ArchitecturesDokument30 SeitenQuality-Of-Service and Error Control Techniques For Mesh-Based Network-On-Chip ArchitecturesSrinivas HnNoch keine Bewertungen

- Information Technology Policy: West Chester University of PA Division of Information ServicesDokument21 SeitenInformation Technology Policy: West Chester University of PA Division of Information ServicesAdipramono PutraNoch keine Bewertungen

- Ceragon Header Compression - Technical Brief PDFDokument9 SeitenCeragon Header Compression - Technical Brief PDFyassminbgNoch keine Bewertungen

- S12 - Fiber Optics Communication - HeikkinenDokument7 SeitenS12 - Fiber Optics Communication - Heikkinenstephane formontNoch keine Bewertungen

- Evaluation of Different Processor Architecture Organizations For On-Site Electronics in Harsh EnvironmentsDokument29 SeitenEvaluation of Different Processor Architecture Organizations For On-Site Electronics in Harsh EnvironmentsDave RobisoNoch keine Bewertungen

- Brand-Rex Data CenterDokument12 SeitenBrand-Rex Data CenterAmpg Jakarta TiimurNoch keine Bewertungen

- Research Paper On TCP Congestion ControlDokument9 SeitenResearch Paper On TCP Congestion Controlgz91rnat100% (1)

- PLTS 2014Dokument25 SeitenPLTS 2014cgrachanenNoch keine Bewertungen

- Research Papers On Silicon PhotonicsDokument6 SeitenResearch Papers On Silicon Photonicsjvfmdjrif100% (1)

- Advances in Logic Device ScalingDokument9 SeitenAdvances in Logic Device ScalingKrishna KumarNoch keine Bewertungen

- GetfileDokument115 SeitenGetfileJohn PapadogiannisNoch keine Bewertungen

- The Application of Parallel DSP Architectures To Radar Signal ProcessingDokument7 SeitenThe Application of Parallel DSP Architectures To Radar Signal ProcessingphithucNoch keine Bewertungen

- D ICsDokument24 SeitenD ICsKonara KiranNoch keine Bewertungen

- Adt 0218Dokument50 SeitenAdt 0218gouretNoch keine Bewertungen

- Fine-Pitch Capabilities of The Flat Ultra-Thin Chip Packaging (UTCP) TechnologyDokument7 SeitenFine-Pitch Capabilities of The Flat Ultra-Thin Chip Packaging (UTCP) TechnologySuresh SkvNoch keine Bewertungen

- 3 - D ICsDokument35 Seiten3 - D ICsSamhith ReddyNoch keine Bewertungen

- Highly Integrated Gate Drivers for Si and GaN Power TransistorsVon EverandHighly Integrated Gate Drivers for Si and GaN Power TransistorsNoch keine Bewertungen

- Design for Testability, Debug and Reliability: Next Generation Measures Using Formal TechniquesVon EverandDesign for Testability, Debug and Reliability: Next Generation Measures Using Formal TechniquesNoch keine Bewertungen

- Spec - Dappro 16Mb SRAM - 5V - QFP68Dokument23 SeitenSpec - Dappro 16Mb SRAM - 5V - QFP68Deepa DevarajNoch keine Bewertungen

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDokument3 SeitenSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDeepa DevarajNoch keine Bewertungen

- Standard Wire Gauge ListDokument3 SeitenStandard Wire Gauge ListDeepa DevarajNoch keine Bewertungen

- Tina Ti Spice ModelsDokument17 SeitenTina Ti Spice Modelsdragos_bondNoch keine Bewertungen

- Systems Advantages of 1553Dokument8 SeitenSystems Advantages of 1553Deepa DevarajNoch keine Bewertungen

- NPN 2N5671 - 2N5672: H I G H C U R R e N T F A S T S W I T C H I N G A P P L I C A T I o N SDokument0 SeitenNPN 2N5671 - 2N5672: H I G H C U R R e N T F A S T S W I T C H I N G A P P L I C A T I o N SDeepa DevarajNoch keine Bewertungen

- 2N5672Dokument13 Seiten2N5672Deepa DevarajNoch keine Bewertungen

- Vehicle Rto Exam FaqDokument1 SeiteVehicle Rto Exam FaqDeepa DevarajNoch keine Bewertungen

- 2N6849 LP PMOS IR For Neg SupplyDokument7 Seiten2N6849 LP PMOS IR For Neg SupplyDeepa DevarajNoch keine Bewertungen

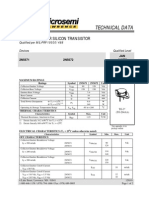

- Technical Data: NPN High Power Silicon TransistorDokument2 SeitenTechnical Data: NPN High Power Silicon TransistorDeepa DevarajNoch keine Bewertungen

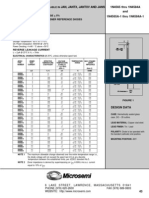

- Eatures Jan, Jantx, and Jantxv D B S P CDokument1 SeiteEatures Jan, Jantx, and Jantxv D B S P CDeepa DevarajNoch keine Bewertungen

- Description Appearance: Surface Mount Voidless-Hermetically-Sealed Ultra Fast Recovery Glass RectifiersDokument0 SeitenDescription Appearance: Surface Mount Voidless-Hermetically-Sealed Ultra Fast Recovery Glass RectifiersDeepa DevarajNoch keine Bewertungen

- 2 N 5153Dokument3 Seiten2 N 5153Deepa DevarajNoch keine Bewertungen

- Technical Data: PNP High Power Silicon TransistorDokument3 SeitenTechnical Data: PNP High Power Silicon TransistorDeepa DevarajNoch keine Bewertungen

- 1N4620Dokument4 Seiten1N4620Deepa DevarajNoch keine Bewertungen

- 2N3637Dokument0 Seiten2N3637Deepa DevarajNoch keine Bewertungen

- 1N4565 4584aDokument3 Seiten1N4565 4584aDeepa DevarajNoch keine Bewertungen

- SpecificationsDokument4 SeitenSpecificationsDeepa DevarajNoch keine Bewertungen

- Startup Design and Analysis NoteDokument6 SeitenStartup Design and Analysis NoteDeepa DevarajNoch keine Bewertungen

- IBRO News 2004Dokument8 SeitenIBRO News 2004International Brain Research Organization100% (1)

- Đề Thi Tham Khảo (Đề thi có 5 trang) : 6: The flood victims 7: Many 8Dokument7 SeitenĐề Thi Tham Khảo (Đề thi có 5 trang) : 6: The flood victims 7: Many 8Quang Đặng HồngNoch keine Bewertungen

- Cee 2005 - 06Dokument129 SeitenCee 2005 - 06iloveeggxPNoch keine Bewertungen

- M4-Lesson Transitional SignalDokument50 SeitenM4-Lesson Transitional SignalJeneros PartosNoch keine Bewertungen

- SLC 10 ScienceDokument16 SeitenSLC 10 SciencePffflyers KurnawanNoch keine Bewertungen

- ESM Module1 GE3 TCWDokument12 SeitenESM Module1 GE3 TCWDeserie Aguilar DugangNoch keine Bewertungen

- Non-Display Industrial Computers: User ManualDokument100 SeitenNon-Display Industrial Computers: User ManualJason100% (1)

- Bab 4 Ba501 Pecahan SeparaDokument24 SeitenBab 4 Ba501 Pecahan SeparaPrince ShanNoch keine Bewertungen

- Limitations of The Study - Docx EMDokument1 SeiteLimitations of The Study - Docx EMthreeNoch keine Bewertungen

- Total School Spending in Singapore: Task 1 020219Dokument6 SeitenTotal School Spending in Singapore: Task 1 020219viper_4554Noch keine Bewertungen

- Prelim Examination in Logic DesignDokument5 SeitenPrelim Examination in Logic Designdj_eqc7227Noch keine Bewertungen

- 2pages 6Dokument3 Seiten2pages 6Rachana G Y Rachana G YNoch keine Bewertungen

- Oliver vs. Philippine Savings BankDokument14 SeitenOliver vs. Philippine Savings BankAmeir MuksanNoch keine Bewertungen

- Behavan00004 0003Dokument19 SeitenBehavan00004 0003Swati GroverNoch keine Bewertungen

- My Publications and Workshops ListDokument4 SeitenMy Publications and Workshops Listraviteja tankalaNoch keine Bewertungen

- DBR G+24 Building ProjectDokument28 SeitenDBR G+24 Building ProjectShobhit Mohta100% (1)

- Do You Have Esp FinalDokument20 SeitenDo You Have Esp FinalVrasidas Poulopoulos50% (2)

- Contoh RefleksiDokument7 SeitenContoh RefleksiIzzat HanifNoch keine Bewertungen

- Practice Problems in ADSORPTION and ION EXCHANGE - SolutionsDokument8 SeitenPractice Problems in ADSORPTION and ION EXCHANGE - SolutionsJenna Brasz100% (2)

- Meeting Wise Agenda TemplateDokument1 SeiteMeeting Wise Agenda Templateapi-416923934Noch keine Bewertungen

- Reserach MethoodolgyDokument38 SeitenReserach MethoodolgyShubashPoojariNoch keine Bewertungen

- Lecture Notes For Transition To Advanced MathematicsDokument115 SeitenLecture Notes For Transition To Advanced MathematicsAngela WaltersNoch keine Bewertungen

- Biology FileDokument10 SeitenBiology FileMichael KorsNoch keine Bewertungen

- Wa0004Dokument8 SeitenWa0004Thabo ChuchuNoch keine Bewertungen

- Collaborative Planning Template W CaptionDokument5 SeitenCollaborative Planning Template W Captionapi-297728751Noch keine Bewertungen

- Partnerships Program For Education and Training (PAEC)Dokument6 SeitenPartnerships Program For Education and Training (PAEC)LeslieNoch keine Bewertungen

- LearnEnglish Reading B1 A Conference ProgrammeDokument4 SeitenLearnEnglish Reading B1 A Conference ProgrammeAylen DaianaNoch keine Bewertungen

- Disneyland (Manish N Suraj)Dokument27 SeitenDisneyland (Manish N Suraj)Suraj Kedia0% (1)

- Naeyc StandardsDokument11 SeitenNaeyc Standardsapi-266968546Noch keine Bewertungen

- Fendrick Govt 720 Global Problem EssayDokument5 SeitenFendrick Govt 720 Global Problem Essayapi-283893191Noch keine Bewertungen