Beruflich Dokumente

Kultur Dokumente

Expt 2

Hochgeladen von

toshgangwarOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Expt 2

Hochgeladen von

toshgangwarCopyright:

Verfügbare Formate

ARMY INSTITUE OF TECHNOLOGY, PUNE DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION

EXPRIMENT NO. 02 Date : TITLE: Study of IC 74LS83 as a BCD Adder AIM: Design and implement single digit BCD adder using binary adder IC. APPARATUS: Digital Trainer kit, IC 7483(4 bit full adder), IC 7408 (Quad Two Input AND Gate), IC 7432(Quad Two Input OR Gate), connectors. THEORY: A BCD adder is a circuit that adds two BCD digits and produces a sum digit also in BCD. BCD addition procedure can be summarized as follows, 1. Add two BCD numbers using normal Binary Addition. 2. If the four bit sum is equal or to less than 9 no correction is needed. The sum is in proper BCD form. 3. It the four-bit sum is greater than 9 or if carry is generated from the four bit sum, the sum is invalid according to BCD form. 4. To correct the invalid sum, Add (0110)2 i.e. 6 to the four bit sum. If carry results from this addition, add it to next higher order BCD digit. Thus to implement BCD adder we require : a. 4 bit binary adder for initial addition. b. Logic circuit to detect sum greater than 9. c. One more 4 bit adder to add (0110)2. IC 7483: A3, A2, A1, A0 and B3, B2, B1, B0 are the input of the IC 7483. Cin represents the carry input while Cout represents carry output.

represents the sum output with

MSB.

BCD adder using two 4-bit binary adder IC 7483. Case I: Sum 9 and carry = 0 The output of combinational circuit y=0. Hence B3 B2 B1 B0 = 0000 for adder 2. Hence output of adder 2 is same as that of adder 1. Case II: Sum > 9 and carry = 0 If S3 S2 S1 S0 of adder 1 is greater than 9, then output Y of combinational circuit becomes 1. Hence B3 B2 B1 B0 = 0110 (of adder 2). Hence six (0110) will be added to sum output of adder 1.

ARMY INSTITUE OF TECHNOLOGY, PUNE DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION

We get the corrected BCD result at the output of adder 2.

Case III: Sum 9 but carry = 1 As carry output of adder 1 is high, y=1. So B3 B2 B1 B0= 0110 (of adder 2) Hence six (0110) will be added to sum output of adder 1. We get the corrected BCD result at the output of adder 2.

Design Procedure BCD adder: 1. 2. 3. 4. 5. Draw the truth table of the BCD adder and the logic circuit. Make the circuit connections according logical circuit diagram. After implementing the circuit connect Vcc. Verify truth table. Try out the various combinations of BCD numbers which are added by the circuit Observe the logical output. DESIGN FOR BCD ADDER 1. Truth Table for BCD addition

ARMY INSTITUE OF TECHNOLOGY, PUNE DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION

K-MAP

Y=S4.S3+S3.S2

ARMY INSTITUE OF TECHNOLOGY, PUNE DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION

PIN CONFIGURATION FOR IC 7483

CIRCUIT DIAGRAM FOR BCD ADDER:

CONCLUSION:

ARMY INSTITUE OF TECHNOLOGY, PUNE DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION

4 BIT BINARY SUBTRACTOR: To perform binary subtraction with the adder IC, 2s complement logic is applied here. If we want to perform operation (A-B) then in this subtraction A is minuend and B is subtrahend. Following procedure will be takes place : 1. Take 2s complement of subtrahend. 2s complement of any number= 1s complement + 1 2. Add 2s complement of subtrahend in minuend. The circuit for subtracting A-B consists of an adder with inverters, placed between each data input B and the corresponding input of full adder. The input carry C0 must be equal to 1 when performing subtraction. LOGIC DIAGRAM: 4-BIT BINARY SUBTRACTOR

TRUTH TABLE:

ARMY INSTITUE OF TECHNOLOGY, PUNE DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION

Input Data A

Input Data B

Subtraction

A4

A3

A2

A1

B4

B3

B2

B1

S4

S3

S2

S1

1 0 0

0 1 1

0 1 1

1 1 0

0 0 0

0 1 0

1 0 0

1 1 1

1 1 1

0 0 0

1 0 1

1 1 0

0 0 1

PROCEDURE: (i) (ii) (iii) RESULT: Make Connections as per given in circuit diagram. Apply Logical inputs as per truth table. Observe the logical output and verify with the truth tables.

CONCLUSION:

ARMY INSTITUE OF TECHNOLOGY, PUNE DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION

Oral Question 1. Is carry look ahead generator is possible to draw with half adder? If not then why with full adder only? 2. Write truth table of full substractor. 3. What is glitch? How to avoid it? 4. Why we add 6 to BCD adder. 5. What is disadvantage of 2s complement. 6. In K-MAP why we put the terms as 00 01 11 10 instead of 00 01 10 11 7. Explain why look ahead carry is used in adder 8. Design BCD Adder. 9. What are weighted and nonweighted codes? 10. Define half adder and full adder. 11. Define half subtractor and full subtractor. 12. Draw and explain the block diagram of n-bit parallel adder. 13. Explain the method used for carry look ahead generation. 14. Explain the working of n-bit full subtractor with the help of neat block diagram. 15. What is 1s and 2s complement? 16. What is the difference between 1s and 2s complement? 17. What do you mean by comparator? 18. What is 9s and 10s complement? 19. What is the function of IC 7483? 20. What is positive and negative logic 21. What is SOP and POS. 22. What is use of Excess 3 code. 23. Give the Binary, Hexadecimal, BCD, and Excess-3 code for decimal 14. 24. Give 1's and 2's complement of 19. 25. Write 9s and 10s complement of 6.

Das könnte Ihnen auch gefallen

- Logic DesignDokument65 SeitenLogic DesignChaudhary WaseemNoch keine Bewertungen

- Assignment No:-11 Date: Assignment Name:-Design & Implement 4-Bit BCD AdderDokument5 SeitenAssignment No:-11 Date: Assignment Name:-Design & Implement 4-Bit BCD AdderAnindya Mahata100% (2)

- Verify Four Voltage and Current Parameters For TTL and Cmos (Ic 74Lsxx, 74Hcxx)Dokument8 SeitenVerify Four Voltage and Current Parameters For TTL and Cmos (Ic 74Lsxx, 74Hcxx)sonalibhagwatkar100% (1)

- Optical Fibre Matlab ThesisDokument30 SeitenOptical Fibre Matlab ThesisRaviNoch keine Bewertungen

- 8051 Interview QuestionsDokument8 Seiten8051 Interview QuestionsSudheer ReddyNoch keine Bewertungen

- Optical FibreDokument17 SeitenOptical Fibreshah alomNoch keine Bewertungen

- 4-Bit BCD Adder Digital Electronics ProjectDokument7 Seiten4-Bit BCD Adder Digital Electronics ProjectJagnur SinghNoch keine Bewertungen

- AluDokument10 SeitenAluAbhishek PatraNoch keine Bewertungen

- UbiSense User ManualDokument5 SeitenUbiSense User ManualAshok Kumar100% (1)

- Unisa Digital Logic NotesDokument8 SeitenUnisa Digital Logic NotesmmasalekNoch keine Bewertungen

- Lab Report 4Dokument10 SeitenLab Report 4abdulbabulNoch keine Bewertungen

- Practice Assignment 11 Sol 12453Dokument6 SeitenPractice Assignment 11 Sol 12453Baldeep Singh KwatraNoch keine Bewertungen

- Lab2 VerilogDokument5 SeitenLab2 VerilogHải TrầnNoch keine Bewertungen

- Courses in Electrical Engineering: Digital Electronics Chapter Two: Logic GatesDokument19 SeitenCourses in Electrical Engineering: Digital Electronics Chapter Two: Logic GatesNGOUNENoch keine Bewertungen

- ALU ReportDokument11 SeitenALU ReportAzad Kiyal100% (2)

- VHDL Design UnitsDokument20 SeitenVHDL Design UnitsEr Deepak GargNoch keine Bewertungen

- Digital Logic Basics: 2-1 Implementation Using NAND Gates: We Can Write The XOR Logical Expression ADokument19 SeitenDigital Logic Basics: 2-1 Implementation Using NAND Gates: We Can Write The XOR Logical Expression AKavya ChoudharyNoch keine Bewertungen

- Differential Amplifier Using BJTDokument11 SeitenDifferential Amplifier Using BJTAssini HussainNoch keine Bewertungen

- LM339 Comparator - Electronics Project Club PDFDokument4 SeitenLM339 Comparator - Electronics Project Club PDFCarlos MagnoNoch keine Bewertungen

- DLD Lab Report #9Dokument10 SeitenDLD Lab Report #9waleedNoch keine Bewertungen

- Veilog HDL Module 3Dokument62 SeitenVeilog HDL Module 3Mallik KglNoch keine Bewertungen

- Chapter 2 Number Systems and Logic GateDokument63 SeitenChapter 2 Number Systems and Logic GatefireworkNoch keine Bewertungen

- 8085 MICROPROCESSOR PROGRAMS FOR DATA MANIPULATIONDokument19 Seiten8085 MICROPROCESSOR PROGRAMS FOR DATA MANIPULATIONnirmal_inboxNoch keine Bewertungen

- This Set of 8051 MicroDokument21 SeitenThis Set of 8051 MicroSonaliNoch keine Bewertungen

- Frequency Divider D-Flip-flopsDokument12 SeitenFrequency Divider D-Flip-flopsSylvester Delali Dordzi0% (1)

- Model Answers HW3Dokument5 SeitenModel Answers HW3John100% (1)

- ALU 8 BIT Group NaminDokument23 SeitenALU 8 BIT Group NaminChrisEmilsonHernaezNoch keine Bewertungen

- Microprocessor All Experiment IT PDFDokument22 SeitenMicroprocessor All Experiment IT PDFSuraj KumarNoch keine Bewertungen

- Week 8 Assignment SolutionsDokument4 SeitenWeek 8 Assignment Solutionsvidhya dsNoch keine Bewertungen

- 8 Bit Alu Using Gdi TechniqueDokument7 Seiten8 Bit Alu Using Gdi TechniqueTADIBOINA PAVAN KUMARNoch keine Bewertungen

- Ramesh Mandal PPT 3rd YearDokument26 SeitenRamesh Mandal PPT 3rd YearRAMESH MANDALNoch keine Bewertungen

- DSDV MODULE 3 Implementation FabricsDokument17 SeitenDSDV MODULE 3 Implementation Fabricssalman shariffNoch keine Bewertungen

- Abdullah Khurram - Coal Lab 12Dokument9 SeitenAbdullah Khurram - Coal Lab 12muhammad saadNoch keine Bewertungen

- Part III 8051 General PgmsDokument7 SeitenPart III 8051 General PgmsHEMANoch keine Bewertungen

- Experiment 7: Magnitude ComparatorsDokument5 SeitenExperiment 7: Magnitude Comparatorsanirudh lakshminarasimhanNoch keine Bewertungen

- 4bit Array MultiplierDokument4 Seiten4bit Array MultiplierRahul TiwariNoch keine Bewertungen

- Full Adder Using 4x1 MuxDokument3 SeitenFull Adder Using 4x1 MuxRasigan UrNoch keine Bewertungen

- Combinational Circuit Adder, Subtractor and MultiplexerDokument24 SeitenCombinational Circuit Adder, Subtractor and Multiplexerram5nath-3100% (1)

- Encoders&DecodersDokument14 SeitenEncoders&DecodersAlex BongNoch keine Bewertungen

- Digital System Objective QuestionsDokument17 SeitenDigital System Objective QuestionsRanjeet pratap singh bhadoriyaNoch keine Bewertungen

- Cat1 Questions - MergedDokument24 SeitenCat1 Questions - MergedSony100% (1)

- AL ICT m3 Logic FirstDokument5 SeitenAL ICT m3 Logic FirstKanishka SeneviratneNoch keine Bewertungen

- Lecture 5Dokument31 SeitenLecture 5Ali MustafaNoch keine Bewertungen

- ASAP7 TutorialDokument52 SeitenASAP7 TutorialAtmadeep DeyNoch keine Bewertungen

- LCD and KEYBORD Interfacing Part 1Dokument25 SeitenLCD and KEYBORD Interfacing Part 1Prathamesh AmateNoch keine Bewertungen

- Design and Implementation of Floating Point ALU With Parity Generator Using Verilog HDLDokument6 SeitenDesign and Implementation of Floating Point ALU With Parity Generator Using Verilog HDLIOSRjournalNoch keine Bewertungen

- Laboratory Exercise 3: Discrete-Time Signals: Frequency-Domain RepresentationsDokument18 SeitenLaboratory Exercise 3: Discrete-Time Signals: Frequency-Domain RepresentationsNguyễn HưngNoch keine Bewertungen

- Maximum Power Transfer in DC CircuitsDokument68 SeitenMaximum Power Transfer in DC CircuitsRana Zeeshan AfzalNoch keine Bewertungen

- Final DE + VHDL Lab B18EC3080 As On 31 July 2019Dokument191 SeitenFinal DE + VHDL Lab B18EC3080 As On 31 July 2019Vishal AtharNoch keine Bewertungen

- Stucor CS3351-GKDokument269 SeitenStucor CS3351-GKNightdive StudiosNoch keine Bewertungen

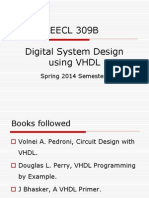

- EECL 309B Digital System Design using VHDLDokument54 SeitenEECL 309B Digital System Design using VHDLShashi Bhushan Kotwal100% (1)

- Convolutional CodesDokument26 SeitenConvolutional CodesPiyush MittalNoch keine Bewertungen

- Ex No: Introduction To DSP & DSK (Tms320C6711) DateDokument9 SeitenEx No: Introduction To DSP & DSK (Tms320C6711) DateParthaSarathyNoch keine Bewertungen

- Arduino Modules L298N Dual H Bridge Motor ControllDokument7 SeitenArduino Modules L298N Dual H Bridge Motor ControllMarius DanilaNoch keine Bewertungen

- VLSI - Carry Lookahead AdderDokument12 SeitenVLSI - Carry Lookahead AdderK.R.RaguramNoch keine Bewertungen

- Code Composer Studio v4 Assembly Project: DSP Lab Manual, Dept. of Ece, Nitk 1Dokument8 SeitenCode Composer Studio v4 Assembly Project: DSP Lab Manual, Dept. of Ece, Nitk 1Jayaram Reddy M K100% (1)

- Digital Electronics Lab ManualDokument107 SeitenDigital Electronics Lab ManualStephen Pranay ChelumallaNoch keine Bewertungen

- DT MPDokument21 SeitenDT MPKaiwalya MatreNoch keine Bewertungen

- Exp10 BCDAdderDokument4 SeitenExp10 BCDAddervk2you009Noch keine Bewertungen

- Logic Design Lab Manual 10ESL38 3rd Sem 2013Dokument61 SeitenLogic Design Lab Manual 10ESL38 3rd Sem 2013vishvakirana75% (4)

- SettingDokument1 SeiteSettingtoshgangwarNoch keine Bewertungen

- The Fault in Our Stars FilmDokument3 SeitenThe Fault in Our Stars FilmtoshgangwarNoch keine Bewertungen

- ComputerDokument117 SeitenComputertoshgangwarNoch keine Bewertungen

- Const - Pock 2Pg - Rom8fsssDokument10 SeitenConst - Pock 2Pg - Rom8fssstoshgangwarNoch keine Bewertungen

- JavaDokument1 SeiteJavatoshgangwarNoch keine Bewertungen

- Nested PackageDokument1 SeiteNested PackagetoshgangwarNoch keine Bewertungen

- Why Packages in JavaDokument2 SeitenWhy Packages in JavatoshgangwarNoch keine Bewertungen

- FinalDokument1 SeiteFinaltoshgangwarNoch keine Bewertungen

- IIT - How To Apply For An InternshipDokument33 SeitenIIT - How To Apply For An InternshiptoshgangwarNoch keine Bewertungen

- Internships Opportunity - 2014Dokument3 SeitenInternships Opportunity - 2014toshgangwarNoch keine Bewertungen

- 82 Ls Eng. & Hindi Mail Sent 27-5-2014Dokument71 Seiten82 Ls Eng. & Hindi Mail Sent 27-5-2014toshgangwarNoch keine Bewertungen

- Internfeel: National Institute of Technology HamirpurDokument12 SeitenInternfeel: National Institute of Technology HamirpurtoshgangwarNoch keine Bewertungen

- Key To Budget Documents BUDGET 2014-2015Dokument8 SeitenKey To Budget Documents BUDGET 2014-2015toshgangwarNoch keine Bewertungen

- IIT - How To Apply For An InternshipDokument33 SeitenIIT - How To Apply For An InternshiptoshgangwarNoch keine Bewertungen

- Const - Pock 2Pg - Rom8fsssDokument10 SeitenConst - Pock 2Pg - Rom8fssstoshgangwarNoch keine Bewertungen

- Cabinet Min PortDokument6 SeitenCabinet Min PorttoshgangwarNoch keine Bewertungen

- Online Journalism Internship ApplicationDokument4 SeitenOnline Journalism Internship ApplicationtoshgangwarNoch keine Bewertungen

- Gate2014 Brochure 2Dokument82 SeitenGate2014 Brochure 2अजय प्रताप सिंहNoch keine Bewertungen

- Budget SpeechDokument44 SeitenBudget SpeechOutlookMagazineNoch keine Bewertungen

- Budget 2014 FeaturesDokument21 SeitenBudget 2014 FeaturesOutlookMagazineNoch keine Bewertungen

- Anne Frank Digital Edition Teachers PackDokument42 SeitenAnne Frank Digital Edition Teachers PacktoshgangwarNoch keine Bewertungen

- IGNOU FEG-02 Solved Assignment 2013 FreeDokument6 SeitenIGNOU FEG-02 Solved Assignment 2013 FreeManish Kumar BhardwajNoch keine Bewertungen

- IGNOU FEG-01 Solved Assignment 2013Dokument10 SeitenIGNOU FEG-01 Solved Assignment 2013Biswajit Behera100% (1)

- Cabinet MinistersDokument4 SeitenCabinet MinistersShailendra SBNoch keine Bewertungen

- 82 Ls Eng. & Hindi Mail Sent 27-5-2014Dokument71 Seiten82 Ls Eng. & Hindi Mail Sent 27-5-2014toshgangwarNoch keine Bewertungen

- Online Journalism Internship ApplicationDokument1 SeiteOnline Journalism Internship ApplicationtoshgangwarNoch keine Bewertungen

- Brochure For 2014 in 2003 VersionDokument6 SeitenBrochure For 2014 in 2003 Versionbalagangadhar17Noch keine Bewertungen

- Approved Annual Programme 2015Dokument1 SeiteApproved Annual Programme 2015Sharath HegdeNoch keine Bewertungen

- Role of Gandhi in India's National MovementDokument6 SeitenRole of Gandhi in India's National MovementtoshgangwarNoch keine Bewertungen

- IAS Prosp 16Dokument19 SeitenIAS Prosp 16Jayesh RathodNoch keine Bewertungen

- Smart Host Microcontroller For Optimal Battery PDFDokument3 SeitenSmart Host Microcontroller For Optimal Battery PDFsrcembeddedNoch keine Bewertungen

- Ovation Troubleshooting - OV300Dokument3 SeitenOvation Troubleshooting - OV300Usman Younis0% (1)

- Product Description 4283241Dokument17 SeitenProduct Description 4283241Bs BarbarianNoch keine Bewertungen

- Ee 411 - Vlsi Design: Week 1Dokument30 SeitenEe 411 - Vlsi Design: Week 1Ashar AsifNoch keine Bewertungen

- Service Bulletin: Serdia 2000 / Version 1.5.6Dokument9 SeitenService Bulletin: Serdia 2000 / Version 1.5.6Juan Carlos ParedesNoch keine Bewertungen

- Fabric v2.4 AppDevDokument27 SeitenFabric v2.4 AppDevBilgehan SavguNoch keine Bewertungen

- Embedded System Design Introduction To SoC System ArchitectureDokument213 SeitenEmbedded System Design Introduction To SoC System Architecturexxxx xxxx100% (2)

- Ontrac Major Technical FeaturesDokument3 SeitenOntrac Major Technical FeaturesAnnie De WildeNoch keine Bewertungen

- 2240-Article Text-6476-1-10-20230324Dokument6 Seiten2240-Article Text-6476-1-10-20230324drs.nasihin mkesNoch keine Bewertungen

- Systems Information Technology Engineer in Charlotte NC Resume Judy RumlikDokument3 SeitenSystems Information Technology Engineer in Charlotte NC Resume Judy RumlikJudyRumlikNoch keine Bewertungen

- MDM XU ReleaseNotesDokument22 SeitenMDM XU ReleaseNotessunilchopseyNoch keine Bewertungen

- Comprehensive Abap Oops Tutorial Document 1 PDFDokument78 SeitenComprehensive Abap Oops Tutorial Document 1 PDFSaimuraliNoch keine Bewertungen

- Last Minute Notes - Operating Systems: Types of Operating System (OS)Dokument9 SeitenLast Minute Notes - Operating Systems: Types of Operating System (OS)bruhNoch keine Bewertungen

- Kirchhoff's LawsDokument3 SeitenKirchhoff's Lawsحسين ابو حامدNoch keine Bewertungen

- Microcontroller Based System For Power Factor Control of Squirrel Cage Induction Motor SCIMDokument2 SeitenMicrocontroller Based System For Power Factor Control of Squirrel Cage Induction Motor SCIMZeeshan KhanNoch keine Bewertungen

- Introduction to Computers: Understanding the BasicsDokument57 SeitenIntroduction to Computers: Understanding the BasicsAyush SharanNoch keine Bewertungen

- FsffasaDokument2 SeitenFsffasaHamid SaifNoch keine Bewertungen

- SMP Gateway User ManualDokument269 SeitenSMP Gateway User ManualgusfajNoch keine Bewertungen

- 1.2.5. UCP Board Instruction Manual PDFDokument16 Seiten1.2.5. UCP Board Instruction Manual PDFHabibulla Bavaji100% (1)

- SC PDFDokument58 SeitenSC PDFRomani FahmiNoch keine Bewertungen

- Laptop Power SequencingDokument14 SeitenLaptop Power SequencingOlivier Ouina100% (2)

- Java Lab ManualDokument27 SeitenJava Lab ManualDr Narayana Swamy Ramaiah100% (1)

- User Guide QHx220Dokument22 SeitenUser Guide QHx220rickrackrunNoch keine Bewertungen

- QB KI 1901 DatasheetDokument3 SeitenQB KI 1901 Datasheetsailesh psNoch keine Bewertungen

- Sanmina Corporation: Product Design and DevelopmentDokument3 SeitenSanmina Corporation: Product Design and DevelopmentJoseph KymmNoch keine Bewertungen

- Internet in Botswana - Problems and ConstraintsDokument11 SeitenInternet in Botswana - Problems and ConstraintsKevin DavidsNoch keine Bewertungen

- Acer Chromebook C740 - Quanta ZHNB DAZHNMB1AD0 RADokument39 SeitenAcer Chromebook C740 - Quanta ZHNB DAZHNMB1AD0 RAmike onciucNoch keine Bewertungen

- STM Unit 1 Taxonomy of BugsDokument56 SeitenSTM Unit 1 Taxonomy of Bugsmohan konakallaNoch keine Bewertungen

- How to Make a Simple Paper AirplaneDokument5 SeitenHow to Make a Simple Paper AirplaneDinda MayaNoch keine Bewertungen