Beruflich Dokumente

Kultur Dokumente

Error Tolerant Adder

Hochgeladen von

Sajeesh ArCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Error Tolerant Adder

Hochgeladen von

Sajeesh ArCopyright:

Verfügbare Formate

IEEE-Interational Conference On Advances In Engineering, Science And Management (ICAESM -2012) March 30, 31, 2012 661

LLIIl I IIYIYLII LLL NIILLL

\`JLN

Iprabakaran.R, 2Famila.S, 3Gowri.s, 4Arvind.R

1&2 Asst.Prof, 3p.G Student, 4U.G.student,

1&3 Anna University Trichy, 2&4Dr.Paul's Engineering college.

Email: Ihiprabakaran@gmail.com.2sivakgowri@yahoo.com.3selvafam@rediffail.com.4arvind6464@yahoo.in

Abstract - The design of adder

subsystem is the most focused area in VLSI

design of processing units. So far there are a

variety of such adders like RCA, CSA, CLA

and ETA. ETA is the Error Tolerant Adder and

is the latest of the adders which has better

performance when compared with the other

adders in terms of power consumption, delay

etc. Whereas the designs so far is by font end

tools that performs simulations with ideal

parameters instead of real time conditions. So,

here in this paper, the design is approached

through backend tool under real time

simulation conditions. The results showed that

the adder performance in terms of accuracy,

delay, size and with 70% lesser power

consumption than that of the conventional c

MOS adders.

Key terms: Back end, adder, cadence, ETA,

Front end.

I. INTRODUCTION

Arithmetic operations are widely used in most

microelectronic systems. Addition is a

fundamental arithmetic operation and is the

base of many other commonly used arithmetic

operations. Also, the other operations such as

the subtraction, multiplication and division can

be derived fom addition and hence adders are

ofen seen as the most signifcant parts of the

arithmetic unit. Designing low-power VLSI

systems has become an important performance

goal because of the fast growing technology in

mobile computation and communication. The

world accepts analog computation," which

generates good enough" results rather than

totally accurate results [4][3][1]. Also in digital

VLSI systems, we do not get accurate results

as in the case of communication systems the

analog signals are sampled, digitized and

transmitted over a noisy channel. Error may

occur anywhere in this process. With the

explosive growth the demand and popularity of

portable electronics is driving designers to

strive for smaller silicon area, higher speeds,

longer battery life, and more reliability. Power

is one of the premium resources a designer tries

to save when designing a system. The aim to

increase battery life of portable electronic

devices is to decrease the energy expended per

arithmetic operation, however lower power

consumption does not necessarily bring about

lower energy dissipation and higher

performance. To perform arithmetic operations,

a device can use up very low power by

functioning at very low frequency but it may

spend a very long time to fnish the operation.

Therefore, we measure the energy dissipation

and evaluate the performance of the system by

calculating the

Power-Delay Product (PDP), which is the

product of average power consumption and

worst case delay.

Also the performance of the processors

in several application specifc processors in

terms of its speed is another important factor

that relies totally on the adder's performance.

II. ERROR TOLERANT ADDER

The Error Tolerant truncation low power adder

[ref. IEEE tran, Zhu[3]] the ETA is the basic

ISBN: 978-81-909042-2-3 2012 IEEE

IEEE-Interational Conference On Advances In Engineering, Science And Management (ICAESM -2012) March 30, 31, 2012 662

concept of this paper, Before going into the

explanation, let us have a look at the

defnitions of some commonly used

terminologies shown in this paper are given as

follow. Error (E): E = Oca - Oela, where Oca is

the result obtained by the adder, and Oela

denotes the correct result (all the results are

represented as decimal numbers).

Accuracy (A): In the error-tolerant

design, the accuracy of an adder is used to

indicate how "correct" the output of an adder is

for a particular input [3]. It is defned as:

A= (l-(E/0

ca

x 100%

Its value ranges from 0% to 100%.

Minimum acceptance accuracy [1] (MAA):

Although some errors are allowed to exist at

the output of an ETA, the accuracy of an

acceptable output should be "high enough"

(higher than a threshold value) to meet the

requirement of the whole system. Minimum

acceptable accuracy is just that threshold value.

The result obtained whose accuracy is

higher than the minimum acceptable accuracy

is called acceptable result. Acceptance

probability (AP): Acceptance probability is the

probability that the accuracy of an adder is

higher than the minimum acceptable accuracy.

It can be expressed as AP = P (ACC > MAA),

with its value ranging from 0 to 1.

Increasingly huge data sets and the need for

instant response require the adder to be large

and fast. The traditional ripple-carry adder

(RCA) is therefore no longer suitable for large

adders because of its low speed performance.

Many different types of fast adder, such as the

carry-skip adder (CSK), carry select adder

(CLA) have been developed.

Also, there are many low power adder

design techniques that have been proposed.

However, there are always trade-offs between

speed and power. The error-tolerant design can

be a potential solution to this problem. By

sacrifcing on accuracy, the ETA can attain

great improvement in both the power

consumption and speed performance.

III. ADDITION ARITHMETIC OF ETA

In the conventional adder circuit, the

delay is mainly attributed to the carry

propagation chain along the critical path, from

the least signifcant bit (LSB) to the most

signifcant bit (MSB). Also glitches in the carry

propagation chain dissipate a signifcant

proportion of dynamic power dissipation.

Therefore, if the carry propagation can be

eliminated or curtailed, a great improvement in

speed performance and power consumption

(Zhu et aI. , 2010) can be achieved.

Oerational direction

Oerational direction

talti n& point

Accurate pa IccWate pa

l11i Q 11

:

,

i

Io1i : i' l

: I

,

:

.

i!3

: !

Al bilS &!U bC1 O 1

Fig.1 Addition arithmetic of ETA

Here, we discuss about the addition arithmetic

proposed in (Zhu et aI. , 2010) where the input

operand is split into two parts: with higher

order bits grouped into accurate part and

remaining lower order bits into inaccurate part.

The length of each part need not necessary be

equal. The addition process starts from the

demarcation line toward the two opposite

directions simultaneously. In the example of

Fig. 2, the two 8-bit input operands, A=

"10110111" (183) and B= "10111101" (189),

are divided equally into 4 bits each for the

accurate and inaccurate parts. The addition of

the higher order bits ( accurate part) of the input

operands is performed from right to lef (LSB

to MSB) starting from the demarcation line

with normal addition method applied. This is to

preserve its correctness since the higher order

bits play a more important role than the lower

order bits. The lower order bits of input

operands (inaccurate part) are added using

ISBN: 978-81-909042-2-3 2012 IEEE

IEEE-Interational Conference On Advances In Engineering, Science And Management (ICAESM -2012) March 30, 31, 2012 663

error tolerant addition mechanism. No carry

signal will be generated or taken in at any bit

position to eliminate the carry propagation

path. To minimize the overall error due to the

elimination of the carry chain, a special

strategy is adapted (Zhu et aI. , 2010), and can

be described as follows: (1) check every bit

position from lef to right (MSB - LSB) starting

from right of demarcation line; (2) if both input

bits are "0" or different, normal one-bit

addition is performed and the operation

proceeds to next bit position; (3) the checking

process is stopped when both input bits are

encountered as high i. e. , 1, and from this bit

onwards, all sum bits to the right (LSB) are set

to "1. " This is how this adder saves carry

propagation delay and enhances the overall

performance.

IV. PREVIOUS WORK

The design of this error tolerant adder consists

of the design of two main parts namely the

normal addition and the carry free controlled

addition part. The normal addition block

consists of the conventional CMOS adder part

(accurate part) which concentrates on the MSB

of the inputs. While the LSB addition, which is

the carry free addition and is carried out by the

controlled addition block (inaccurate part) [ref.

[4] [6] [11]. Both the blocks were designed

through the front-end tools till simulation.

The designed adder's performance

comparison was then done and compared with

the previous conventional adders. All the

design and logic were implemented only in the

front-end; the proved outputs such as the power

consumption, area and delay can be more

effectively derived through back-end design

In the proposed work, the ETA is designed

using the back-end (cadence) tool and the

improved performances in delay, power

consumption and area required by the ETA

adder are explained.

V. PROPOSED WORK

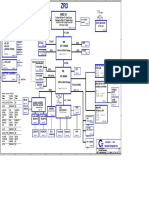

Proposed error tolerant adder: The block

diagram of the Error Tolerant adder that adapts

to our proposed addition arithmetic is shown in

Fig.l. This most straightforward structure

consists of two parts: an accurate part and an

inaccurate part. The accurate part is

constructed using conventional adder, ere the

RCA( 28T used usually) is replaced by a lOT

full-adder. The carry-in of this accurate part

adder is connected to ground. The inaccurate

part constitutes two blocks: a carry-free

addition block and a control block as shown in

Fig.2.

7

B7

AO-3

Bo3

Fig. 2 ETA Architecture. (ref. Zhu et [3])

The control block is used to generate the

control signals to determine the working mode

of the carry-free addition block. In addition, the

Least Signifcant Bit(LSB) of the multiplier(bit

B(O)) is used as control bit P for both accurate

part and inaccurate part of the proposed adder.

For B(O) is one, the adder cells performs

normal addition operation. For B(O) equals to

zero, the adder Cells are brought into OFF state

with NMOS and PMOS transistor driven by P

brought into open state and the line from

supply to ground is cut off, thus minimizing

leakage power dissipation. Based on the

proposed methodology, an 8-bit Error tolerant

adder is designed by considering 4 bits II

accurate part and 4 bits in inaccurate part.

Design of the accurate part: In the proposed

8-bit ETA, the inaccurate and accurate parts

consist of 4 bits each. Ripple carry addition is

the most power saving conventional addition

ISBN: 978-81-909042-2-3 2012 IEEE

IEEE-Interational Conference On Advances In Engineering, Science And Management (ICAESM -2012) March 30, 31, 2012 664

technique[ll] [13] [7]; with the lOT replacing

the usual ripple carry adder, the performance

can be further improved. It has been chosen for

the design of accurate part of the adder circuit.

Design of the inaccurate part: The inaccurate

part is the most critical section in the proposed

ETA as it determines the accuracy, speed

performance, and power consumption of the

adder.

The inaccurate part consists of two

blocks: the carry free addition block and the

control block. The carry-free addition block is

designed using 4 modifed XOR gates to

generate a sum bit individually for LSBs. The

block diagram of the carry free addition block

and the schematic implementation of the

modifed XOR gate are shown in Fig.3.

Inaccurate part consists of the CTL

input fed with the carry out of the individual

addition of LSB bits. This CTL input controls

the output of the carry fee addition block of

the inaccurate part.

Fig. 3. CMOS adder schematic

When both or either of the bits in the LSB of

the inputs are 0, then CTL remains 0, and it

goes to logic '1' whenever both the inputs are

'1' making one of the input of the OR gate in

the adder to go high thereby making the output

, l' for any input that comes afer the bits that

produced' 1 '. The blocks of the modifed XOR

and control block are shown in fgure. 4. l and

fgure 4. 2 respectively.

Fig. 4. J Modified XOR

ISBN: 978-81-909042-2-3 2012 IEEE

IEEE-Interational Conference On Advances In Engineering, Science And Management (ICAESM -2012) March 30, 31, 2012 665

The entire block diagram explaining the carry fee addition of the ETA is shown in the fgure below:

(a

L --

2

b

Fig.5. ETA- inaccurate part. a) Carr free addition block. b) Modiied XOR with Control. (ref Zhu et [3J)

The above logic is implemented in the

backend and the overall ETA for adding two

8bit inputs are designed and its performance

is calculated and evaluated. The schematic

of the ETA is shown in fgure.6 below:

Fig. 6 Schematic of ETA

The above logic is for 2-bits addition and

then it is implemented for 8bit addition as

well and its layout is extracted for

calculation of area and power delay product

and power dissipation at various points of

this adder.

ISBN: 978-81-909042-2-3 2012 IEEE

IEEE-Interational Conference On Advances In Engineering, Science And Management (ICAESM -2012) March 30, 31, 2012 666

Fig. 7 Schematic C)8bit ETA

Fig. 9. Output graph C)1 bit ETA adder

iM05|8M Rospons,

r--i '-l

_ !

....... .

1 ' ...... " .. 1

c... _

.._ m .

I

[

.

r

\

'

.__

'

...

; ...... -... . " ........ , ...... " .... , t. ---

,

1

:

;,

:

.

[

.

, \

:

.

t t

v v

'

V VV

lim.(s)

ISBN: 978-81-909042-2-3 2012 IEEE

IEEE-Interational Conference On Advances In Engineering, Science And Management (ICAESM -2012) March 30, 31, 2012 667

VI. PERFORMANCE COMPARISON

The layouts are designed and the

power consumption values and area required

by the circuit are calculated and the parasitic

capacitance and resistances are exposed for

calculating the delay and power product in

the adder circuit in detail.

The comparison between the

existing and the proposed adder designed by

backend design for their various important

parameters such as the delay, power

consumed are tabled. The area is as low as

457. 25Jm2.

Type of

Adder

RCA

CSK

CSL

CLA

ETA

a) Fig. 10 Performance of previous work

Power Delay PDP PDP laving Tran i tor

(mW

(ns)

(pJ) (%)

Cout

0.22 4.0 0.89 6.29 896

0.46 2.90 1.33 7.4 1728

0.60 3.06 1.84 8170 2176

0.51 2.37 1.21 75.21 2208

0.13 2.29 0.30 N,A. 10

b) Fig. 11 Performance of proposed work

VII. SIMULATION AND OUTPUTS

The designed circuits are simulated

using the cadence tool(IC 6.1. 4. 500.8) and

the waveforms of different outputs are

displayed.

a) Fig. 12 Outut of adder (accurate part)

I

c

':

:

>

1

IF

k

-

b ) Fig. 13 Output of XOR gate

VIII. CONCLUSION

So far from the various types of

adders we have known, this logic proves to

be more promising and optimal in the feld

of application specifc processing units.

With the results obtained from improved

design and extensive simulation, these

adders are effective to be implemented

practically.

IX. FUTURE WORK

In future we are going to implement

this logic in multipliers and work on its

performance improvement with different

techniques in multiplication.

ISBN: 978-81-909042-2-3 2012 IEEE

IEEE-Interational Conference On Advances In Engineering, Science And Management (ICAESM -2012) March 30, 31, 2012 668

X. REFERENCES

[1] "Design of low- power high-speed error

Tolerant shif and add multiplier" Journal of

computer science 7 (12): 1839-1845, 20111ssn 1549-

3636 2011 science publications Corresponding

author: 1 k.n. vieyakumar,

[2] "Design of low-power high-speed

truncationerror- tolerant adder and its application in

digital signal processing" ning zhu, wang ling goh,

weia zhang, kiat seng yeo, and zhi hui kong ieee

transactions on ver large scale integration (vlsi

systems, vol. 18, no. 8, august 2010

[3] "Design and error-tolerance in the presence

of massive numbers of defects," m.A. Breuer, s. K.

Gupta, and t. M Mak, ieee des. Test Comput., vol.

24, no. 3, pp. 216-227, may-jun. 2004. [4] "A novel

testing methodology Based on error-rate to support

error-tolerance," k J Lee, t. Y Hsieh, and m. A.

Breuer, in proc. 1nt. Test conj, 2005, pp. Jl 36-Jl 44.

[5] S Chong and a. Ortega, "Hardware testing

for error tolerant multimedia compression based on

linear tansforms," in proc. Defect and Fault

tolerance in vlsi syst. Symp., 2005, pp. 5230-531. [6]

. Y Hsieh, k J Lee, and m. A. Breuer, "reduction of

detected acceptable faults for yield improvement via

error-tolerance" in proc. Des., automation and test

eur. Conj Exhib., 2007, pp. 1-6.

[7] s. Cheemalavagu, p. Korkmaz, and k V

Palem, "Ultra low energy Computing via

probabilistic algorithms and devices: cmos device

Primitives and the energy-probability relationship,"

in proc. 2004 int. Conj Solid state devices and

materials, toko, japan, sep. 2004, pp. 402-403.

[8] p. Korkmaz, b. E. S. Akgul, k V. Palem, and

I N Chakrapani, "advocating noise as an agent for

ultra-low energy computing: probabilistic

Complementary metal-oxide-semiconductor devices

and their characteristics," jpn. J Appl. Phys., vol. 45,

no. 4b, pp. 3307-3316, 2006.

[9] l.-d Van and c.-c. Yang, "generalized

owerror area-effcient fxed-Width multipliers," ieee

trans. Circuits syst. l, reg. Papers, vol. 25, No. 8, pp.

1608-1619, aug. 2005.

[10] m. Lehman and n. Bur/a, "skip techniques

or high-speed carry propagation in binary arithmetic

units," ire trans. Electron. Comput., vol. Ec-10, pp.

691-698, dec. 1962.

[11] o. Bedri, "carry select adder," ire trans.

Electron. Comput., vol. Ec-11, pp. 340-346, 1962.

[12] o. Macsorley, "high speed arithmetic i

binary computers," ire proc., Vol. 49, pp. 67-91,.

1961

[13] y. Kiat-seng and r. Kaushik, "Low-voltage,

low-power vlsi subsystems". New york: mcgraw-hill,

2005.

[14] D. Radhakrishnan, "Low-voltage low

power CMOS full adder," in Proc. lEE Circuits

Devices Syst., vol. 148, Feb. 2001, pp. 19-24.

ISBN: 978-81-909042-2-3 2012 IEEE

Das könnte Ihnen auch gefallen

- Practical Guides to Testing and Commissioning of Mechanical, Electrical and Plumbing (Mep) InstallationsVon EverandPractical Guides to Testing and Commissioning of Mechanical, Electrical and Plumbing (Mep) InstallationsBewertung: 3.5 von 5 Sternen3.5/5 (3)

- Ug949 Vivado Design Methodology PDFDokument306 SeitenUg949 Vivado Design Methodology PDFIvan AlyaevNoch keine Bewertungen

- Power Reduction Through RTL Clock GatingDokument10 SeitenPower Reduction Through RTL Clock GatingAishwarya TekkalakotaNoch keine Bewertungen

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsVon EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNoch keine Bewertungen

- Low Power Design of Digital SystemsDokument28 SeitenLow Power Design of Digital SystemssuperECENoch keine Bewertungen

- Design of A Full Adder Using PTL and GDI TechniqueDokument6 SeitenDesign of A Full Adder Using PTL and GDI TechniqueIJARTETNoch keine Bewertungen

- Packard Bell Easynote Tj75 - Wistron Sjv50-Cp - Rev SBDokument67 SeitenPackard Bell Easynote Tj75 - Wistron Sjv50-Cp - Rev SBsanvivicente100% (1)

- Reflow Soldering: Apparatus and Heat Transfer ProcessesVon EverandReflow Soldering: Apparatus and Heat Transfer ProcessesNoch keine Bewertungen

- Design of High Performance Adder With Tolerable Error and Acceptable Output and It's Application in Image ProcessingDokument6 SeitenDesign of High Performance Adder With Tolerable Error and Acceptable Output and It's Application in Image ProcessingPrajwalRamakrishnaNoch keine Bewertungen

- Low Power High Speed Error Tolerant Adder VecDokument7 SeitenLow Power High Speed Error Tolerant Adder VecSrini VasuluNoch keine Bewertungen

- High-Performance Low-Power Carry Speculative Addition With Variable LatencyDokument13 SeitenHigh-Performance Low-Power Carry Speculative Addition With Variable LatencyPiyush ParasharNoch keine Bewertungen

- Dmatm: Dual Modified Adaptive Technique Based MultiplierDokument6 SeitenDmatm: Dual Modified Adaptive Technique Based MultiplierTJPRC PublicationsNoch keine Bewertungen

- Paralle ProcessingDokument8 SeitenParalle ProcessingRavi RavikiranNoch keine Bewertungen

- Multiplexer-Based Design of Adders/Subtractors and Logic Gates For Low Power VLSI ApplicationsDokument8 SeitenMultiplexer-Based Design of Adders/Subtractors and Logic Gates For Low Power VLSI ApplicationssunilNoch keine Bewertungen

- Processor Design Using Square Root Carry Select AdderDokument6 SeitenProcessor Design Using Square Root Carry Select AdderAJER JOURNALNoch keine Bewertungen

- Design of Low-Power High-Speed Error Tolerant Shift and Add MultiplierDokument8 SeitenDesign of Low-Power High-Speed Error Tolerant Shift and Add Multipliergolden compassNoch keine Bewertungen

- Roba MulDokument56 SeitenRoba MulNishitha NishiNoch keine Bewertungen

- Student Name Ali Abdullah Mohammed Ameen: Class 3 BDokument13 SeitenStudent Name Ali Abdullah Mohammed Ameen: Class 3 Bالزهور لخدمات الانترنيتNoch keine Bewertungen

- Analysis of Different Bit Carry Look Ahead Adder Using Verilog Code-2Dokument7 SeitenAnalysis of Different Bit Carry Look Ahead Adder Using Verilog Code-2IAEME PublicationNoch keine Bewertungen

- Comparative Analysis of Different Architectures of CMOS ComparatorDokument4 SeitenComparative Analysis of Different Architectures of CMOS Comparatorj4everNoch keine Bewertungen

- J.vivek Kumar Ijmece131103Dokument5 SeitenJ.vivek Kumar Ijmece131103jvivekkumarmeNoch keine Bewertungen

- Chapter 1Dokument8 SeitenChapter 1NIKHIL PUJARINoch keine Bewertungen

- A Study On The Conventional and Fuzzy Control Steel-Cutting ProcessDokument5 SeitenA Study On The Conventional and Fuzzy Control Steel-Cutting ProcessGökhan BaytekinNoch keine Bewertungen

- Implementationof Time Efficient VLSI Designusing Kogge Stone AdderDokument6 SeitenImplementationof Time Efficient VLSI Designusing Kogge Stone AdderIJRASETPublicationsNoch keine Bewertungen

- Speed-Power-Accuracy TradeoffDokument8 SeitenSpeed-Power-Accuracy TradeoffbackspaceTABNoch keine Bewertungen

- Energy Efficient Approximate AdderDokument12 SeitenEnergy Efficient Approximate AdderNMANoch keine Bewertungen

- (IJCST-V9I2P10) :DR - Shine N DasDokument6 Seiten(IJCST-V9I2P10) :DR - Shine N DasEighthSenseGroupNoch keine Bewertungen

- Design and Implementation of 4-Bit Arithmetic and Logic Unit Chip With The Constraint of Power ConsumptionDokument8 SeitenDesign and Implementation of 4-Bit Arithmetic and Logic Unit Chip With The Constraint of Power ConsumptionRaja ArslanNoch keine Bewertungen

- 39ICRASE130513Dokument4 Seiten39ICRASE130513Kanaga VaratharajanNoch keine Bewertungen

- The Design of A Low Power Asynchronous Multiplier: Yijun Liu, Steve FurberDokument6 SeitenThe Design of A Low Power Asynchronous Multiplier: Yijun Liu, Steve FurberMishi AggNoch keine Bewertungen

- A Simple Yet Efficient Accuracy-Configurable Adder DesignDokument14 SeitenA Simple Yet Efficient Accuracy-Configurable Adder DesignVinay KelurNoch keine Bewertungen

- Microelectronics Journal: Shuo Yang, Jun Cheng, Pei WangDokument8 SeitenMicroelectronics Journal: Shuo Yang, Jun Cheng, Pei WangShylu SamNoch keine Bewertungen

- Design and Development of Novel WeighingDokument4 SeitenDesign and Development of Novel WeighingaatifdNoch keine Bewertungen

- Design of Efficient Multiplier Using VHDLDokument50 SeitenDesign of Efficient Multiplier Using VHDLNagendra KashyapNoch keine Bewertungen

- Theory and Applications of IncrementalDokument13 SeitenTheory and Applications of Incremental翁偉倫Noch keine Bewertungen

- Addition Algorithms For Vlsi - A Review: Kapilramgavali1, Sandeepdubey, Gaurav Shete, Sushant GawadeDokument8 SeitenAddition Algorithms For Vlsi - A Review: Kapilramgavali1, Sandeepdubey, Gaurav Shete, Sushant GawadeKapilGavaliNoch keine Bewertungen

- Design & Analysis of High Speed Low and Area CMOS Based Comparator With Different ArchitecturesDokument4 SeitenDesign & Analysis of High Speed Low and Area CMOS Based Comparator With Different ArchitecturesijeteeditorNoch keine Bewertungen

- High-Speed Area-Efficient VLSI Architecture of Three-Operand Binary AdderDokument6 SeitenHigh-Speed Area-Efficient VLSI Architecture of Three-Operand Binary Adderk NiroshaNoch keine Bewertungen

- A Novel Approximate Adder Design Using Error Reduced Carry Prediction and Constant TruncationDokument15 SeitenA Novel Approximate Adder Design Using Error Reduced Carry Prediction and Constant Truncationkrishna sNoch keine Bewertungen

- Application and Analysis of Approximate Bus and Shift-Invert Encoding Technique For Image Data Transfer Over Serial BusDokument11 SeitenApplication and Analysis of Approximate Bus and Shift-Invert Encoding Technique For Image Data Transfer Over Serial BusIJRASETPublicationsNoch keine Bewertungen

- An Efficient 64-Bit Carry Select Adder With Less Delay and Reduced Area ApplicationDokument5 SeitenAn Efficient 64-Bit Carry Select Adder With Less Delay and Reduced Area ApplicationkumaranrajNoch keine Bewertungen

- 9 .Efficient Design For Fixed Width AdderDokument45 Seiten9 .Efficient Design For Fixed Width Addervsangvai26Noch keine Bewertungen

- PCX - ReportDokument15 SeitenPCX - ReportChristopher crNoch keine Bewertungen

- A1101010108Dokument8 SeitenA1101010108sudip mandalNoch keine Bewertungen

- Tvlsi00 GuptaDokument11 SeitenTvlsi00 GuptakbkkrNoch keine Bewertungen

- Bit Comparator Using Different Logic Style of Full AdderDokument3 SeitenBit Comparator Using Different Logic Style of Full Adderfabio-delima8012Noch keine Bewertungen

- Booth RecodingDokument3 SeitenBooth RecodingJournalNX - a Multidisciplinary Peer Reviewed JournalNoch keine Bewertungen

- Implementation of 2-Bit Multiplier Circuit Using Pass Transistor LogicDokument10 SeitenImplementation of 2-Bit Multiplier Circuit Using Pass Transistor LogicIJRASETPublicationsNoch keine Bewertungen

- A New Vlsi Architecture For Modi EdDokument6 SeitenA New Vlsi Architecture For Modi Edsatishcoimbato12Noch keine Bewertungen

- VHDL Microproject ReportDokument15 SeitenVHDL Microproject ReportHitesh TumsareNoch keine Bewertungen

- CH 33509513Dokument5 SeitenCH 33509513Shakeel RanaNoch keine Bewertungen

- Design and Implementation of Low-Power Digital Signal Processing Using Approximate AddersDokument7 SeitenDesign and Implementation of Low-Power Digital Signal Processing Using Approximate AddersijsretNoch keine Bewertungen

- DRDDokument16 SeitenDRDAnushree SaranNoch keine Bewertungen

- ROBADokument11 SeitenROBAJyothi67% (3)

- Analytical Estimation of Signal Transition Activity From Word-Level StatisticsDokument16 SeitenAnalytical Estimation of Signal Transition Activity From Word-Level StatisticsKumar N KrishnaMurthyNoch keine Bewertungen

- Introduction To Behavioral ModelingDokument5 SeitenIntroduction To Behavioral ModelingRakotomalala Mamy TianaNoch keine Bewertungen

- Report SemiFinal PDFDokument8 SeitenReport SemiFinal PDFBiyadglgne Eskezia AyalewNoch keine Bewertungen

- Irjet V7i4232Dokument7 SeitenIrjet V7i4232PrajwalRamakrishnaNoch keine Bewertungen

- Xstat: Statistical X-Filling Algorithm For Peak Capture Power Reduction in Scan TestsDokument25 SeitenXstat: Statistical X-Filling Algorithm For Peak Capture Power Reduction in Scan TestsAdireddy SatyatrinadhNoch keine Bewertungen

- 9bus System, Power FlowDokument17 Seiten9bus System, Power FlowZeeshan AhmedNoch keine Bewertungen

- Design and Implementation of High Speed Carry Select AdderDokument6 SeitenDesign and Implementation of High Speed Carry Select AdderseventhsensegroupNoch keine Bewertungen

- VlsiDokument32 SeitenVlsibalasaravanan0408Noch keine Bewertungen

- I/O Interfacing of 8086 Using 8255Dokument19 SeitenI/O Interfacing of 8086 Using 8255SAURABH AGRAWALNoch keine Bewertungen

- B75 Pro3Dokument68 SeitenB75 Pro3CosstyNoch keine Bewertungen

- E-Frog Game: Senior Design I EEL 4914C Group #6Dokument111 SeitenE-Frog Game: Senior Design I EEL 4914C Group #6Darrius Dela PeñaNoch keine Bewertungen

- Part 66 Module 5 SyllabusDokument2 SeitenPart 66 Module 5 SyllabusamaiscNoch keine Bewertungen

- Simulation Set 2Dokument4 SeitenSimulation Set 2Harsh ThakurNoch keine Bewertungen

- Acer Aspire 3050, 5050 Quanta ZR3 DA0ZR3MB6E0 DA0ZR3MB6C1Dokument31 SeitenAcer Aspire 3050, 5050 Quanta ZR3 DA0ZR3MB6E0 DA0ZR3MB6C1essemirNoch keine Bewertungen

- 4026 DatasheetDokument12 Seiten4026 Datasheetatmega168100% (1)

- FYGP Board Imlementations Lab 2Dokument21 SeitenFYGP Board Imlementations Lab 2Arshad RasheedNoch keine Bewertungen

- Use of Digital Technologies in EducationDokument5 SeitenUse of Digital Technologies in EducationOpen Access JournalNoch keine Bewertungen

- RP 5810Dokument45 SeitenRP 5810Yolanda Fernandez Del AmoNoch keine Bewertungen

- Technical College: Maintenance of Computer SystemsDokument65 SeitenTechnical College: Maintenance of Computer SystemsAbhay VermaNoch keine Bewertungen

- TechnicalReferenceManual CY8C29x66 CY8C27x43Dokument568 SeitenTechnicalReferenceManual CY8C29x66 CY8C27x43trnealNoch keine Bewertungen

- Digital Circuits - Shift RegistersDokument7 SeitenDigital Circuits - Shift RegistersB.Prashant JhaNoch keine Bewertungen

- Power Macintosh 9600/200 and 9600/200MPDokument2 SeitenPower Macintosh 9600/200 and 9600/200MPscri100% (1)

- Sequential Circuits and Seven Segment Display: Lab Assignment 10Dokument7 SeitenSequential Circuits and Seven Segment Display: Lab Assignment 10Ahmed UzairNoch keine Bewertungen

- Tutorial Using SPI in F2833x F2803x TargetDokument22 SeitenTutorial Using SPI in F2833x F2803x TargetAnDres RodriguezNoch keine Bewertungen

- Computer Fundaments Unit-I: Assistant Professor Department of Computer Science Govt. N. P. G. College of Science, RaipurDokument17 SeitenComputer Fundaments Unit-I: Assistant Professor Department of Computer Science Govt. N. P. G. College of Science, RaipurDNikksNoch keine Bewertungen

- Secondary Storage Devices (1) :: Magnetic DisksDokument56 SeitenSecondary Storage Devices (1) :: Magnetic DisksSamahir AlkleefaNoch keine Bewertungen

- Example of Classification EssayDokument1 SeiteExample of Classification EssayAddi MuhammadNoch keine Bewertungen

- Off. Inputs and OutputsDokument9 SeitenOff. Inputs and OutputsOnoseNoch keine Bewertungen

- Digital Electronics (MCQ) PART-1Dokument7 SeitenDigital Electronics (MCQ) PART-101ABHIGYAN MAJINoch keine Bewertungen

- Lab8 2-Bit Binary Adder-SubtractorDokument11 SeitenLab8 2-Bit Binary Adder-SubtractorAhmed Razi UllahNoch keine Bewertungen

- Unit 3Dokument66 SeitenUnit 3Venky VellankiNoch keine Bewertungen

- Chapt Er EL EVEN: 8 2 5 5 I/O ProgrammingDokument22 SeitenChapt Er EL EVEN: 8 2 5 5 I/O ProgrammingHackathon PDA CEKNoch keine Bewertungen

- Control Unit Operation: Roselle Manalang Manuel Vincent Galdo Ron CastroDokument10 SeitenControl Unit Operation: Roselle Manalang Manuel Vincent Galdo Ron CastroVincent GaldoNoch keine Bewertungen

- Automata Lecture15Dokument20 SeitenAutomata Lecture15RIMSHANoch keine Bewertungen

- Ulcreforr.: AnsmacrDokument4 SeitenUlcreforr.: AnsmacrarcNoch keine Bewertungen

- Pengenalan Komputer & Teknologi Maklumat Ch. 8Dokument41 SeitenPengenalan Komputer & Teknologi Maklumat Ch. 8محمد شكري عبد الحليمNoch keine Bewertungen