Beruflich Dokumente

Kultur Dokumente

Circuitos Digitales 1

Hochgeladen von

Circulo Es NivelCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Circuitos Digitales 1

Hochgeladen von

Circulo Es NivelCopyright:

Verfügbare Formate

959645315.

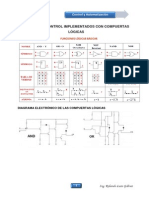

Informe de Laboratorio de Circuitos Digitales: Resultados de los experimentos con las compuertas lgicas:

Experimento 1: Compuerta NOT. Esta compuerta lgica cumple la funcin de negar la entrada de la seal lgica y obedece a la siguiente tabla de verdad: A 0 1 Salida 1 0

Procedimiento: Armar el siguiente esquema con la compuerta Not (7404) siguiendo las instrucciones de la gua.

Llenar el siguiente cuadro con los resultados: A 0 1 Resultados F1 1 0 F2 0 1 F3 1 0

Exposicin: 1. Escriba las funciones lgicas que describen las salidas F1, F2 y F3 como Funcion de A.

959645315. 2. Dnde se complementa A dos veces en el circuito? En F1 y F3 se nos da el complemento de A. 3. Si conectramos mas compuertas Not en serie, Qu seria F6 (la salida de las sexta compuerta Not) como funcin de A?, Qu seria Fn si se conectaran n compuertas Not en serie?. F6 seria igual a A (seis veces negada) Fn es cuando el nmero de compuertas Not es impar. Fn es A cuando el nmero de compuertas Not es par.

Experimento 2: Compuerta OR. Esta compuerta lgica cumple la funcin de sumar la entrada de dos seales lgicas y obedece a la siguiente tabla de verdad:

A 0 0 1 1

B 0 1 0 1

Salida 0 1 1 1

Procedimiento: 1.- Verifique la tabla de verdad de la compuerta Or mediante el siguiente esquema. A 0 0 1 1 B 0 1 0 1 Resultados F1 0 1 1 1

959645315. 2.- Mediante dos compuertas OR de dos entradas implemente una funcin OR de tres entradas: Conecte las entradas de una compuerta OR a A y B mientras que su salida a la entrada de otra compuerta OR mientras que la otra entrada de esa segunda compuerta debe conectarse a C y de acuerdo a la salida de esa compuerta complete la tabla: Ver Grafico.

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

Resultados

F2 0 1 1 1 1 1 1 1

Exposicin: 1.- Mediante el mapa de Karnaugh simplifique F2 y demuestre que el circuito corresponde a un OR de tres variables.

Experimento 3: Compuerta NOR. Esta compuerta lgica cumple la funcin de negar la suma de dos seales lgicas y obedece a la siguiente tabla de verdad: A 0 0 1 1 B 0 1 0 1 Salida 1 0 0 0

959645315. Procedimiento: 1.- Verifique la tabla de verdad de la compuerta NOR mediante el siguiente esquema.

A 0 0 1 1

B 0 1 0 1

Resultados

F1 1 0 0 0

2.- Trate de implementar una compuerta NOR de tres entradas mediante dos compuertas NOR de dos entradas: Conecte las entradas de una compuerta NOR a A y B mientras que su salida a la entrada de otra compuerta NOR mientras que la otra entrada de esa segunda compuerta debe conectarse a C y de acuerdo a la salida de esa compuerta complete la tabla: Ver Grafico.

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

Resultados

Terico 1 0 0 0 0 0 0 0

F2 0 0 1 0 1 0 1 0

959645315. Exposicin: 1.- Mediante el mapa de Karnaugh simplifique F2 El circuito corresponde realmente a un NOR de tres variables?

( El circuito no representa a una compuerta NOR.

2.- Si el circuito no ejecuta un NOR de tres variables, sugiera un circuito que si lo haga.

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

Resultados

Salida 1 0 0 0 0 0 0 0

3.- Cambiar la salida del circuito si modifica las variables B y C? Solo en el caso de que A sea 0, una combinacin de B y C podr modificar la salida del circuito. Experimento 4: Compuerta AND. Esta compuerta lgica cumple la funcin de multiplicar dos seales lgicas y obedece a la siguiente tabla de verdad: A 0 0 1 1 B 0 1 0 1 Salida 0 0 0 1

959645315. Procedimiento: 1.- Verifique la tabla de verdad de la compuerta AND mediante el siguiente esquema.

A 0 0 1 1

B 0 1 0 1

Resultados

F1 0 0 0 1

2.- Mediante dos compuertas AND de dos entradas implemente una funcin AND de tres entradas: Conecte las entradas de una compuerta AND a A y B mientras que su salida a la entrada de otra compuerta AND mientras que la otra entrada de esa segunda compuerta debe conectarse a C y de acuerdo a la salida de esa compuerta complete la tabla: Ver Grafico.

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

Resultados

F2 0 0 0 0 0 0 0 1

959645315. Exposicin: 1.- Mediante el mapa de Karnaugh simplifique F2 y demuestre que el circuito corresponde a un AND de tres variables. A BC 0 1 00 01 1 11 10

F2 = ABC

Experimento 5: Compuerta NAND. Esta compuerta lgica cumple la funcin de negar la multiplicacin de dos seales lgicas y obedece a la siguiente tabla de verdad: A 0 0 1 1 B 0 1 0 1 Salida 1 1 1 0

Procedimiento: 1.- Verifique la tabla de verdad de la compuerta NAND mediante el siguiente esquema.

A 0 0 1 1

B 0 1 0 1

Resultados

F1 1 1 1 0

959645315. 2.- Trate de implementar una compuerta NAND de tres entradas mediante dos compuertas NOR de dos entradas: Conecte las entradas de una compuerta NAND a A y B mientras que su salida a la entrada de otra compuerta NAND mientras que la otra entrada de esa segunda compuerta debe conectarse a C y de acuerdo a la salida de esa compuerta complete la tabla: Ver Grafico.

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

Resultados

Terico 1 1 1 1 1 1 1 0

F2 1 0 1 0 1 0 1 1

Exposicin:

1.- Mediante el mapa de Karnaugh simplifique F2 El circuito corresponde realmente a un NOR de tres variables?

El circuito no representa a una compuerta NAND.

959645315. 2.- Si el circuito no ejecuta un NAND de tres variables, sugiera un circuito que si lo haga. A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 Resultados Salida 1 1 1 1 1 1 1 0

3.- Cambiar la salida del circuito si modifica las variables B y C? Solo en el caso de que A sea 1, una combinacin de B y C podr modificar la salida del circuito. Experimento 6: Compuerta XOR. Esta compuerta lgica cumple la funcin de detectar un nmero de seales impares de entrada 1 y 0 y obedece a la siguiente tabla de verdad: A 0 0 1 1

l

B 0 1 0 1

Salida 0 1 1 0 Procedimiento: 1.- Verifique la tabla de verdad de la compuerta XOR mediante el siguiente esquema. A 0 0 1 1 B 0 1 0 1 Resultados F1 0 1 1 0

959645315. 2.- Trate de implementar una compuerta XOR de cuatro entradas mediante tres compuertas XOR de dos entradas: Conecte las entradas de una compuerta XOR a A y B mientras que su salida a la entrada de otra compuerta XOR mientras que la otra entrada de esa segunda compuerta debe conectarse a C, luego la salida de esta compuerta debe conectarse a la entrada de una tercera compuerta XOR y su otra entrada a D y de acuerdo a la salida de esa compuerta complete la tabla: Ver Grafico.

A 0 0 0 0 0 0 0 0 1 Exposicin: 1.- Mediante el mapa de Karnaugh Puede simplificarse F2?. AB CD 00 01 11 10 00 1 1 1 1 1 1 1 1 01 11 1 10 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Resultados

F2 0 1 1 0 1 0 0 1 1 0 0 1 0 1 1 0

Este arreglo de la tabla no permite agrupar los valores en lazo de 4 ni de 2 y por lo tanto la funcion F2 resulta ser simplemente la suma de todos los minters. 2.- El circuito modelado, Realmente ejecuta una funcion XOR de cuatro variables? Si, porque cuando hay una cantidad par de entrada de unos y ceros, la salida es 0 y cuando hay una cantidad de entrada impar de unos y ceros, la salida es 1.

959645315. Experimento 7: Implementacin de una funcin dada. Objetivo: en este experimento implementara la funcin: ( Procedimiento: 1.- Dibuje el formulario de resultados esperados en la tabla de verdad, el diagrama lgico y luego implemente la funcin con el menor nmero de compuertas que desea usar. ) ( )

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Esperado 1 0 0 0 0 1 1 1 0 1 1 1 0 1 1 1

Resultados

F1 1 0 0 0 0 1 1 1 0 1 1 1 0 1 1 1

959645315. 2.- Dibuje el formulario de resultados esperados en la tabla de verdad, el diagrama lgico y luego implemente la siguiente funcin:

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Esperado 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Resultados

F1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

3.- El circuito acta como detector, su salida es 1 solo si se le aplican ciertos modelos binarios Cul de los dos casos siguientes se aplica? El circuito detecta un numero de 4 bit cuyo valor es (0000).

Das könnte Ihnen auch gefallen

- Guia Diseños Logicos - Intensivo 2013Dokument40 SeitenGuia Diseños Logicos - Intensivo 2013Josea Arvelo33% (3)

- Informe 2 - Electrónica DigitalDokument21 SeitenInforme 2 - Electrónica DigitalKevin Santiago Aguirre LondonoNoch keine Bewertungen

- Taller 1 Lógica Digital 1Dokument5 SeitenTaller 1 Lógica Digital 1jesusNoch keine Bewertungen

- TallerPrimerCorte ED1 2022 1Dokument3 SeitenTallerPrimerCorte ED1 2022 1Boy NiggaNoch keine Bewertungen

- Examen Parcial Sistemas 2020-0Dokument13 SeitenExamen Parcial Sistemas 2020-0YAIR ROBERTO MALASQUEZ VILCHEZNoch keine Bewertungen

- Informe Previo N°2Dokument10 SeitenInforme Previo N°2Jorge HuamanNoch keine Bewertungen

- Laboratorio 1 Lógicos AND OR NOTDokument12 SeitenLaboratorio 1 Lógicos AND OR NOTdeoli1990Noch keine Bewertungen

- 4 KarnaughDokument15 Seiten4 KarnaughRoberto CantoNoch keine Bewertungen

- Practica 3Dokument0 SeitenPractica 3Enrique GonzalesNoch keine Bewertungen

- Practica 2 Sistemas Digitales EspeDokument22 SeitenPractica 2 Sistemas Digitales EspeJulio RamírezNoch keine Bewertungen

- Laboratorio 1Dokument21 SeitenLaboratorio 1Carol CardenasNoch keine Bewertungen

- SISTEMAS DIGITALES I PREVIO: CONVERSION BINARIO A BCDDokument15 SeitenSISTEMAS DIGITALES I PREVIO: CONVERSION BINARIO A BCDMiguel Obispo ChaguaNoch keine Bewertungen

- Reporte 3Dokument14 SeitenReporte 3damianserna18Noch keine Bewertungen

- 2007-08 Ejercicios SeptDokument18 Seiten2007-08 Ejercicios SeptJulian PerezNoch keine Bewertungen

- Diseño Sumador RestdorDokument10 SeitenDiseño Sumador RestdorRamiro David MNoch keine Bewertungen

- Problemas ResueltosDokument23 SeitenProblemas ResueltosAndyManuelNoch keine Bewertungen

- IDL2020 Pca2Dokument7 SeitenIDL2020 Pca2Electro MotiveNoch keine Bewertungen

- 4 Practicas Electronic A Digital Tsu Mi 2009 UtccDokument93 Seiten4 Practicas Electronic A Digital Tsu Mi 2009 UtccmanuelscribdgonzalesNoch keine Bewertungen

- Parcial Final Sistemas DigitalesDokument22 SeitenParcial Final Sistemas DigitalesFredy Moreno BallesterosNoch keine Bewertungen

- 075 - Digital Actividades 1Dokument4 Seiten075 - Digital Actividades 1Felipe Homero López Toledo100% (1)

- PRÁCTICAS LÓGICA CIRCUITOSDokument98 SeitenPRÁCTICAS LÓGICA CIRCUITOSGonzalo CurielNoch keine Bewertungen

- Practica 2 Electrónica Equipo 14Dokument23 SeitenPractica 2 Electrónica Equipo 14Ximena J LanderosNoch keine Bewertungen

- Lab 06 Circuitos Digitales UNMSMDokument10 SeitenLab 06 Circuitos Digitales UNMSMDianaNoch keine Bewertungen

- Multiplexores y Cicuito SecuencialDokument7 SeitenMultiplexores y Cicuito SecuencialEduardo Condori Ochoa100% (1)

- Informe Compuertas LogicasDokument8 SeitenInforme Compuertas LogicasRuben Darío AyalaNoch keine Bewertungen

- Problemas Resueltos Electronica DigitalDokument7 SeitenProblemas Resueltos Electronica DigitalkazutoNoch keine Bewertungen

- Sumador Binario de 4 BitsDokument10 SeitenSumador Binario de 4 BitsBere Ramírez AguileraNoch keine Bewertungen

- Control Con Compuertas Logicas PDFDokument27 SeitenControl Con Compuertas Logicas PDFAlison ReedNoch keine Bewertungen

- 10) Sumador y ComparadorDokument7 Seiten10) Sumador y Comparadorjaja1978100% (1)

- Prácticas de laboratorio de puertas lógicas y funciones combinacionalesDokument12 SeitenPrácticas de laboratorio de puertas lógicas y funciones combinacionalesJorge Santiago MontielNoch keine Bewertungen

- Ejercicios PropuestosDokument65 SeitenEjercicios PropuestosSonia Aguilar HuichoNoch keine Bewertungen

- Ejercicios Electronica DigitalDokument13 SeitenEjercicios Electronica DigitaltecnoensenyamentNoch keine Bewertungen

- Sistemas de producción automatizadosDokument7 SeitenSistemas de producción automatizadosvaleria castañonNoch keine Bewertungen

- Ejercicios Electronica DigitalDokument6 SeitenEjercicios Electronica DigitalJesus Ivan Herrera LopezNoch keine Bewertungen

- Puertas lógicas y circuitos de controlDokument30 SeitenPuertas lógicas y circuitos de controlLuiz GarciaNoch keine Bewertungen

- Circuitos secuenciales máquina dulcesDokument7 SeitenCircuitos secuenciales máquina dulcesMaria StewartNoch keine Bewertungen

- Implementación y análisis de circuitos digitales usando álgebra de Boole y mapas de KarnaughDokument6 SeitenImplementación y análisis de circuitos digitales usando álgebra de Boole y mapas de KarnaughNilsa Yohanna Niño HernandezNoch keine Bewertungen

- Actividad 1 - Compuertas Lógicas y Tablas de VerdadDokument16 SeitenActividad 1 - Compuertas Lógicas y Tablas de VerdadMayerling RamirezNoch keine Bewertungen

- Ejercicios 2Dokument5 SeitenEjercicios 2Daniel AguilarNoch keine Bewertungen

- Compuertas digitales de colector abierto y conexiones Y cableadoDokument3 SeitenCompuertas digitales de colector abierto y conexiones Y cableadoVic VigaNoch keine Bewertungen

- Practica ALUDokument6 SeitenPractica ALUJuan Carlos Villagran OrdonezNoch keine Bewertungen

- P4 Alvarado Aviles Escobar Moran MendezDokument20 SeitenP4 Alvarado Aviles Escobar Moran MendezSamuel MoralesNoch keine Bewertungen

- Reporte de Practica de MatematicasDokument27 SeitenReporte de Practica de MatematicasDonaldo Hernandez ReyesNoch keine Bewertungen

- Practica 3Dokument7 SeitenPractica 3Santiago Ayabaca LandiNoch keine Bewertungen

- Boletín de Práctica 1 FCO UPVDokument9 SeitenBoletín de Práctica 1 FCO UPVRiwa DainNoch keine Bewertungen

- Actividad 1 PLCDokument7 SeitenActividad 1 PLCVictor Bohorquez AlfonsoNoch keine Bewertungen

- Practica 2Dokument6 SeitenPractica 2Vin Doyle BravoNoch keine Bewertungen

- Segundo Previo DIGITALESDokument8 SeitenSegundo Previo DIGITALESMateo ForeroNoch keine Bewertungen

- Aplicaciones de Circuitos DigitalesDokument15 SeitenAplicaciones de Circuitos DigitalesAlex Pomier AliagaNoch keine Bewertungen

- Ejercicios de Integrales de Línea, Superficie y VolumenVon EverandEjercicios de Integrales de Línea, Superficie y VolumenBewertung: 4 von 5 Sternen4/5 (2)

- Servicios complementarios en sistemas eléctricos de potencia: Análisis y modelamientoVon EverandServicios complementarios en sistemas eléctricos de potencia: Análisis y modelamientoBewertung: 5 von 5 Sternen5/5 (1)

- Problemas resueltos de Hidráulica de CanalesVon EverandProblemas resueltos de Hidráulica de CanalesBewertung: 4.5 von 5 Sternen4.5/5 (7)

- Insta UnoDokument7 SeitenInsta UnoCirculo Es NivelNoch keine Bewertungen

- Diagrama de de BancosDokument2 SeitenDiagrama de de BancosCirculo Es NivelNoch keine Bewertungen

- Manual Instalacion Electrica Domiciliaria Bvci0005043Dokument100 SeitenManual Instalacion Electrica Domiciliaria Bvci0005043Carlos E. Alave Ugarte100% (5)

- Ejercicios de circunferencias y tangenciasDokument3 SeitenEjercicios de circunferencias y tangenciasCirculo Es NivelNoch keine Bewertungen

- Examen parcial de Electricidad Industrial 2014-1Dokument4 SeitenExamen parcial de Electricidad Industrial 2014-1Circulo Es NivelNoch keine Bewertungen

- Trabajo de Insta Predios UnifamiliaresDokument1 SeiteTrabajo de Insta Predios UnifamiliaresCirculo Es NivelNoch keine Bewertungen

- Especificaciones de InstaDokument1 SeiteEspecificaciones de InstaCirculo Es NivelNoch keine Bewertungen

- Conversiones Octal, Hexadecimal, DecimalDokument8 SeitenConversiones Octal, Hexadecimal, Decimalvils1976988Noch keine Bewertungen

- Atomo I-1Dokument1 SeiteAtomo I-1Circulo Es NivelNoch keine Bewertungen

- AMPLIDINADokument6 SeitenAMPLIDINACirculo Es Nivel0% (1)

- Medición resistividad sueloDokument8 SeitenMedición resistividad sueloCirculo Es NivelNoch keine Bewertungen

- Geo ColeDokument2 SeitenGeo ColeCirculo Es Nivel0% (1)

- SEMANA 2 CsDokument4 SeitenSEMANA 2 CsRafael Cardenas MoranNoch keine Bewertungen

- Funciones Trigonometricas OkDokument3 SeitenFunciones Trigonometricas OkCirculo Es Nivel50% (2)

- Nomenclatura 1Dokument4 SeitenNomenclatura 1Circulo Es NivelNoch keine Bewertungen

- Sistema de Medida AngularDokument2 SeitenSistema de Medida AngularCirculo Es Nivel0% (1)

- Ecuacion Cubica de Tercer GradoDokument4 SeitenEcuacion Cubica de Tercer GradoCirculo Es NivelNoch keine Bewertungen

- Guia 3 - Razones Trigonométricas de Ángulos NotablesDokument4 SeitenGuia 3 - Razones Trigonométricas de Ángulos Notablesrcartolin824573% (22)

- PO23NA3Dokument3 SeitenPO23NA3Circulo Es NivelNoch keine Bewertungen

- Guia 2Dokument7 SeitenGuia 2lrivasNoch keine Bewertungen

- Guia 12121Dokument6 SeitenGuia 12121Circulo Es NivelNoch keine Bewertungen

- 4 Lineas1Dokument28 Seiten4 Lineas1Laura GilNoch keine Bewertungen

- 4 Lineas1Dokument28 Seiten4 Lineas1Laura GilNoch keine Bewertungen

- Resolucion de Triangulos RectanguloDokument3 SeitenResolucion de Triangulos RectanguloCirculo Es NivelNoch keine Bewertungen

- Guia 12121Dokument6 SeitenGuia 12121Circulo Es NivelNoch keine Bewertungen

- Ruedas y Numero de VueltasDokument5 SeitenRuedas y Numero de VueltasCirculo Es NivelNoch keine Bewertungen

- Dimensionamiento de Conductores Eléctricos de Cobre MéxicoDokument0 SeitenDimensionamiento de Conductores Eléctricos de Cobre MéxicoCirculo Es NivelNoch keine Bewertungen

- Fisica Moderna CompletoDokument7 SeitenFisica Moderna CompletoCirculo Es NivelNoch keine Bewertungen

- Generador de Inducción AutoexcitadoDokument22 SeitenGenerador de Inducción AutoexcitadoalphaelectroNoch keine Bewertungen

- Poligonos AgrDokument3 SeitenPoligonos AgrCirculo Es NivelNoch keine Bewertungen

- Act2 Unidad Logica Aritmetica (Alu)Dokument15 SeitenAct2 Unidad Logica Aritmetica (Alu)Hector QuiñonesNoch keine Bewertungen

- TP 14 LocoDokument12 SeitenTP 14 LocoNombre PendienteNoch keine Bewertungen

- Practica 1 Digital Verificacion de Estados de Una Señal LogicaDokument4 SeitenPractica 1 Digital Verificacion de Estados de Una Señal LogicapaeslomaNoch keine Bewertungen

- Prob 4Dokument7 SeitenProb 4Leandro SchenoneNoch keine Bewertungen

- Análisis y síntesis de circuitos lógicos secuencialesDokument19 SeitenAnálisis y síntesis de circuitos lógicos secuencialesCarlo RamirezNoch keine Bewertungen

- MicrocontroladoresDokument25 SeitenMicrocontroladoresJ.a. Tenshi ExecutionerNoch keine Bewertungen

- Practica N°1 Compuertas Logicas en VHDLDokument6 SeitenPractica N°1 Compuertas Logicas en VHDLMarianoNoch keine Bewertungen

- Final 2 IntentoDokument25 SeitenFinal 2 Intentopedro0% (1)

- Curso Básico de Microcontroladores PICDokument50 SeitenCurso Básico de Microcontroladores PICEdison Correa0% (1)

- Fichas Tecnicas - Lab. ElectromecanicaDokument110 SeitenFichas Tecnicas - Lab. ElectromecanicaFidGio ShiNoch keine Bewertungen

- Sistemas Digitales - 2° TareaDokument27 SeitenSistemas Digitales - 2° TareaCarlos Andrés67% (3)

- Compuertas NOTDokument7 SeitenCompuertas NOTFernando AlbertoNoch keine Bewertungen

- Practica 18Dokument5 SeitenPractica 18eduardo martinesNoch keine Bewertungen

- Trab-Pract-N1 18Dokument22 SeitenTrab-Pract-N1 18HANS ALEJANDRO CAMPOS DAVILANoch keine Bewertungen

- FMSDokument8 SeitenFMSelectrotecnia123Noch keine Bewertungen

- 5 Memoria RamDokument10 Seiten5 Memoria RamPabloAgustínPerramonNoch keine Bewertungen

- Tarea 5 FpgaDokument6 SeitenTarea 5 FpgaHIGH SAPIENSNoch keine Bewertungen

- Logica Digital IDokument6 SeitenLogica Digital IJhonatan RodriguezNoch keine Bewertungen

- Intro Herr Diseño LTR (28 Abril) PDFDokument9 SeitenIntro Herr Diseño LTR (28 Abril) PDFJUAN CARLOS ARAGON BAMACANoch keine Bewertungen

- Instalación CPU: Guía paso a paso para montar un procesadorDokument19 SeitenInstalación CPU: Guía paso a paso para montar un procesadoraluzNoch keine Bewertungen

- Procesadores Superescalares (I) - Microarquitecturas y Principios de Funcionamiento - Cap3 - GrupobDokument143 SeitenProcesadores Superescalares (I) - Microarquitecturas y Principios de Funcionamiento - Cap3 - GrupobwbejarNoch keine Bewertungen

- Satuquinga Evelin Contador SincronoDokument16 SeitenSatuquinga Evelin Contador SincronoEvelin SatuquingaNoch keine Bewertungen

- Estructura y Funcion Del CpuDokument29 SeitenEstructura y Funcion Del Cpudevsco63Noch keine Bewertungen

- Análisis Combinatorio de Circuitos DigitalesDokument13 SeitenAnálisis Combinatorio de Circuitos DigitalesSebas R.Noch keine Bewertungen

- CIAA Hardware v1.1Dokument7 SeitenCIAA Hardware v1.1Josbaney PereiraNoch keine Bewertungen

- Trabajo de InvestigacionDokument11 SeitenTrabajo de Investigacionmarioloco94746100% (1)

- Saber Electrónica #312Dokument52 SeitenSaber Electrónica #312David Ocampo Gonzalez100% (2)

- Sistemas Digitales ProblemasDokument17 SeitenSistemas Digitales ProblemasROBINSON ANDRES NIEVES ACOSTANoch keine Bewertungen

- Manual NE300 ascensorDokument91 SeitenManual NE300 ascensorAriel Alexis Pinto Pinto100% (1)