Beruflich Dokumente

Kultur Dokumente

Space Vector PWM

Hochgeladen von

Mohamed NabilOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Space Vector PWM

Hochgeladen von

Mohamed NabilCopyright:

Verfügbare Formate

CHAPTER 7

SPACE VECTOR PULSEWIDTH-MODULATED (SV-PWM) INVERTERS

7-1

INTRODUCTION

In Chapter 5, we briefly discussed current-regulated PWM inverters using current-hysteresis control, in which the switching frequency f s does not remain constant. The desired currents can also be supplied to the motor by calculating and then applying appropriate voltages, which can be generated based on the sinusoidal pulse-width-modulation principles discussed in basic courses in electric drives and power electronics [1]. However, the availability of digital signal processors in control of electric drives provides an opportunity to improve upon this sinusoidal pulse-width modulation by a procedure described in this chapter [2, 3], which is termed space vector pulse-width modulation (SV-PWM). We will simulate such an inverter using Simulink for use in ac drives. 7-2

a SYNTHESIS OF STATOR VOLTAGE SPACE VECTOR vs

In terms of the instantaneous stator phase voltages, the stator space voltage vector is

7-1

a vs (t ) van (t )e j 0 vbn (t )e j 2 /3 vcn (t )e j 4 /3

(7-1)

In the circuit of Fig. 7-1, in terms of the inverter output voltages with respect to the negative dc bus and hypothetically assuming the stator neutral as a reference ground

van vaN vNn ; vbn vbN vNn ; vcn vcN vNn ;

Substituting Eqs. 7-2 into Eq. 7-1 and recognizing that

(7-2)

e j0 e j 2 /3 e j 4 /3 0 ,

(7-3)

the instantaneous stator voltage space vector can be written in terms of the inverter output voltages as

a vs (t ) vaN e j 0 vbN e j 2 / 3 vcN e j 4 / 3

(7-4)

A switch in an inverter pole of Fig. 7-1 is in the up position if the pole

ia b ib

c

v c vb

Vd

ic

v a

N qa qb qc

Figure 7-1 Switch-mode inverter.

7-2

switching function q 1 , otherwise in the down position if q 0 . In terms of the switching functions, the instantaneous voltage space vector can be written as

a vs (t ) Vd (qae j 0 qbe j 2 / 3 qce j 4 / 3 )

(7-5)

With three poles, eight switch-status combinations are possible. In Eq. 7-5, the

a stator voltage vector vs (t ) can take on one of the following seven distinct

instantaneous values where in a digital representation, phase "a" represents the least significant digit and phase c the most significant digit (for example, the resulting voltage vector due to the switch-status combination 011 is represented

(3)

as v3 ):

a vs (000) v0 0 a vs (001) v1 Vd e j 0 a vs (010) v2 Vd e j 2 / 3 a vs (011) v3 Vd e j / 3 a vs (100) v4 Vd e j 4 / 3 a vs (101) v5 Vd e j5 / 3 a vs (110) v6 Vd e j a vs (111) v7 0

(7-6)

In Eq. 7-6, v0 and v7 are the zero vectors because of their values. The resulting instantaneous stator voltage vectors, which we will call the basic vectors, are plotted in Fig. 7-2. The basic vectors form six sectors as shown in Fig. 7-2. The objective of the PWM control of the inverter switches is to synthesize the desired reference stator voltage space vector in an optimum manner with the following objectives: A constant switching frequency f s 7-3

v2 (010)

v3 (011) sector 2

sector 3 v6 (110)

vs

sector 1

v1(001)

a-axis

sector 4

v4 (100)

sector 6

sector 5

v5 (101)

Figure 7-2 Basic voltage vectors (v0 and v7 not shown).

Smallest instantaneous deviation from its reference value Maximum utilization of the available dc-bus voltages Lowest ripple in the motor current, and Minimum switching loss in the inverter.

The above conditions are generally met if the average voltage vector is synthesized by means of the two instantaneous basic non-zero voltage vectors that form the sector (in which the average voltage vector to be synthesized lies) and both the zero voltage vectors, such that each transition causes change of only one switch status to minimize the inverter switching loss. In the following analysis, we will focus on the average voltage vector in sector 1 with the aim of generalizing the discussion to all sectors. To synthesize an

a se js ) over a time period Ts in Fig. 7-3, the ( V average voltage vector vs

adjoining basic vectors v1 and v3 are applied for intervals xTs and yTs respectively, and the zero vectors v0 and v7 are applied for a total duration of

7-4

v3 Vd e j / 3

yv3

se js vs V

v1 Vd e j 0

xv1 Figure 7-3 Voltage vector in sector 1.

zTs . In terms of the basic voltage vectors, the average voltage vector can be

expressed as

a 1 vs [ xTsv1 yTsv3 zTs 0] Ts

or

(7-7)

a vs xv1 yv3

where,

(7-8) (7-9)

x y z 1

In Eq. 7-8, expressing voltage vectors in terms of their amplitude and phase angles results in

se js xVd e j 0 yVd e j / 3 V

(7-10)

By equating real and imaginary terms on both sides of Eq. 7-10, we can solve for

s , s and Vd ) to synthesize the desired x and y (in terms the given values of V

average space vector in sector 1 (see Problem 7-1). Having determined the durations for the adjoining basic vectors and the two zero vectors, the next task is to relate the above discussion to the actual poles ( a, b and c). Note in Fig. 7-2 that in any sector, the adjoining basic vectors differ in one position, for example in sector 1 with the basic vectors v1(001) and v3 (011) , only 7-5

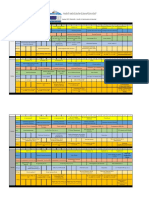

the pole b differs in the switch position. For sector 1, the switching pattern in Fig. 7-4 shows that pole-a is in up position during the sum of xTs , yTs , and

z7Ts intervals, and hence for the longest interval of the three poles. Next in the

length of duration in the up position is pole-b for the sum of yTs , and z7Ts intervals. The smallest in the length of duration is pole-c for only z7Ts interval. Each transition requires a change in switch state in only one of the poles, as shown in Fig. 7-4. Similar switching patterns for the three poles can be generated for any other sector (see Problem 7-2). 7-3 COMPUTER SIMULATION OF SV-PWM INVERTER

vtri

vcontrol ,a

vcontrol ,b vcontrol ,c

Vd vaN

0

Vd vbN

0

Ts

Vd vcN

0

z0 2

x 2

y 2

z7 Ts

y 2

x 2

z0 2

Figure 7-4 Waveforms in Sector 1 ; z z0 z7 In computer simulations, for example using Simulink, as well as in hardware implementation using rapid prototyping tools such as from DSPACE [4], the above described pulse-width modulation of the stator voltage space vector can be carried out by comparing control voltages with a triangular waveform signal at the 7-6

switching-frequency to generate switching functions. It is similar to the sinusoidal PWM approach only to the extent of comparing control voltages with a triangular waveform signal. However, in SV-PWM, the control voltages do not have a purely sinusoidal nature as those in the sinusoidal PWM. In an induction machine with an isolated neutral, the three phase voltages sum to zero (see Problem 7-3)

van (t ) vbn (t ) vcn (t ) 0

(7-11)

a To synthesize an average space vector vs with phase components va , vb and vc

(the dc-bus voltage Vd is specified), the control voltages can be written in terms

tri (the amplitude of the of the phase voltages as follows, expressed as a ratio of V

constant switching-frequency triangular signal vtri used for comparison with these control voltages):

vcontrol ,a van vk 1 tri Vd Vd 2 V vcontrol ,b vbn vk 1 tri Vd Vd 2 V vcontrol ,c vcn vk 1 tri Vd Vd 2 V

where, (7-12)

vk

max(van , vbn , vcn ) min(van , vbn , vcn ) 2

(7-13)

Deriving Eqs. 7-12 and 7-13 is left as a homework problem (Problem 7-5).

7-7

7-4

s OF THE STATOR VOLTAGE LIMIT ON THE AMPLITUDE V

a SPACE VECTOR vs

s of the average stator First we will establish the absolute limit on the amplitude V

voltage space vector at various angles. The limit on the amplitude equals Vd (the dc-bus voltage) if the average voltage vector lies along a non-zero basic voltage vector. In between the basic vectors, the limit on the average voltage vector amplitude is that its tip can lie on the straight lines shown in Fig. 7-7 forming a hexagon (see Problem 7-6).

a However, the maximum amplitude of the output voltage vs should be limited to the circle within the hexagon in Fig. 7-7 to prevent distortion in the resulting currents. This can be easily concluded from the fact that in a balanced sinusoidal a steady state, the voltage vector vs rotates at the synchronous speed with its

constant amplitude. At its maximum amplitude,

jsynt a vs ,max (t ) Vs,maxe

(7-14)

s can attain is Therefore, the maximum value that V

0 s,max Vd cos( 60 ) 3 Vd V 2 2

(7-15)

Vd

s,max V

30

0

Vd

s . Figure 7-7 Limit on amplitude V

7-8

From Eq. 7-15, the corresponding limits on the phase voltage and the line-line voltages are as follows:

phase,max 2 V s,max Vd V 3 3

and

(7-16)

VLL,max (rms) 3

phase,max V 2

V d 0.707Vd 2

(7-17)

The sinusoidal pulse-width modulation in the linear range discussed in the previous course on electric drives and power electronics results in a maximum voltage

VLL,max (rms)

3 Vd 0.612Vd (sinusoidal PWM) 2 2

(7-18)

Comparison of Eqs. 7-17 and 7-18 shows that the SV-PWM discussed in this chapter better utilizes the dc bus voltage and results in a higher limit on the available output voltage by a factor of (2/ 3) , or by approximately 15 percent higher, compared to the sinusoidal PWM. SUMMARY In this chapter, an approach called SV-PWM is discussed, which is better than the sinusoidal PWM approach in utilizing the available dc-bus voltage. Its modeling using Simulink is described. REFERENCES 1. N. Mohan, Electric Drives An Integrative Approach, year 2001 edition, published by MNPERE (WWW.MNPERE.COM).

7-9

2. H. W. van der Broek et al, Analysis and Realization of a Pulse Width Modulator based on Voltage Space Vectors, IEEE Industry Applications Society Proceedings, pp. 244-251, 1986 3. J. Holtz, Pulse Width Modulation for Electric Power Converters, Chapter 4 in a book Power Electronics and Variable Frequency Drives, edited by B. K. Bose, IEEE Press, 1997. 4. WWW.DSPACE.DE PROBLEMS 7-1 In a converter Vd 700V . To synthesize an average stator voltage vector

7-2 7-3

a vs 563.38 e j 0.44 V , calculate x , y and z a v 563.38 e j 2.53 V . Plot results similar to those in Fig. 7-4. Repeat if s

Show that in an induction machine with isolated neutral, at any instant of

v (t ) vb (t ) vc (t ) 0 . time, a

7-4 7-5 7-6

a 563.38 e j 0.44 V , calculate the phase voltage components. Given that vs

Derive Eqs. 7-11 and 7-12. Derive that the maximum limit on the amplitude of the space vector forms the hexagonal trajectory shown in Fig. 7-7.

7-10

Das könnte Ihnen auch gefallen

- Control y VaiacionDokument20 SeitenControl y VaiacionDarness Castillo RodriguezNoch keine Bewertungen

- A Vector Controlled Induction Motor Drive With Neural Network Based Space Vector Pulse Width ModulatorDokument8 SeitenA Vector Controlled Induction Motor Drive With Neural Network Based Space Vector Pulse Width ModulatorTiruchengode VinothNoch keine Bewertungen

- Novel, Switch, Z-Source Three-Phase InverterDokument6 SeitenNovel, Switch, Z-Source Three-Phase InverterJanjanam PraveenNoch keine Bewertungen

- A Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsDokument9 SeitenA Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsInternational Journal of Engineering Inventions (IJEI)Noch keine Bewertungen

- Simplifi Ed SVPWM Based Hybrid PWM For Induction Motor Drives For The Reduction of Torque RipplesDokument6 SeitenSimplifi Ed SVPWM Based Hybrid PWM For Induction Motor Drives For The Reduction of Torque RipplesKoukou AmkoukouNoch keine Bewertungen

- Modified Space Vector Pulse Width Modulation For Z-Source InvertersDokument3 SeitenModified Space Vector Pulse Width Modulation For Z-Source InvertersRamana ReddyNoch keine Bewertungen

- InvertersDokument7 SeitenInverterslohitashriyaNoch keine Bewertungen

- SpaceVector PWM InverteDokument27 SeitenSpaceVector PWM InverteShoaib KhizerNoch keine Bewertungen

- SpaceVector PWM InverterDokument35 SeitenSpaceVector PWM Invertersolomong50% (2)

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerDokument12 SeitenDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaNoch keine Bewertungen

- Implementation of Space Vector Pulse Width Modulation Technique On Three Phase Two Level InverterDokument11 SeitenImplementation of Space Vector Pulse Width Modulation Technique On Three Phase Two Level InverterАлексей ЯмаNoch keine Bewertungen

- Q02201300137Dokument8 SeitenQ02201300137Vikas PatelNoch keine Bewertungen

- Comparative Study of Five Level and SeveDokument12 SeitenComparative Study of Five Level and Sevemahmoud yarahmadiNoch keine Bewertungen

- Three Level InverterDokument5 SeitenThree Level InverterManish PrajapatiNoch keine Bewertungen

- A Novel Scheme To Eliminate Common Mode Voltage in Multilevel InvertersDokument4 SeitenA Novel Scheme To Eliminate Common Mode Voltage in Multilevel InvertersJavier MaldonadoNoch keine Bewertungen

- Low Cost Digital Signal Generation For Driving Space Vector PWM InverterDokument12 SeitenLow Cost Digital Signal Generation For Driving Space Vector PWM InverterJunaid AhmadNoch keine Bewertungen

- Chen 2016Dokument5 SeitenChen 2016srilakshmisiriNoch keine Bewertungen

- Harmonic and Loss Analysis of Space-Vector Modulated ConvertersDokument6 SeitenHarmonic and Loss Analysis of Space-Vector Modulated Convertersahmet ozturkNoch keine Bewertungen

- 06jpf06de13 PDFDokument50 Seiten06jpf06de13 PDFviji_pondicherryNoch keine Bewertungen

- Common Voltage Eliminating of SVM Diode Clamping Three-Level Inverter Connected To GridDokument4 SeitenCommon Voltage Eliminating of SVM Diode Clamping Three-Level Inverter Connected To GridveguruprasadNoch keine Bewertungen

- Inverter and SV-PWMDokument5 SeitenInverter and SV-PWMcoep05Noch keine Bewertungen

- Space Vector Modulated Three Phase Voltage Source InverterDokument24 SeitenSpace Vector Modulated Three Phase Voltage Source InverterАлексей ЯмаNoch keine Bewertungen

- SVPWM VTRDokument14 SeitenSVPWM VTRAtiqMarwatNoch keine Bewertungen

- SPWM SVPWMDokument44 SeitenSPWM SVPWMAravind MohanaveeramaniNoch keine Bewertungen

- Paper 2 - PEL20120014 - 2ndDokument5 SeitenPaper 2 - PEL20120014 - 2ndSherif M. DabourNoch keine Bewertungen

- Space Vector PWM - 3Dokument6 SeitenSpace Vector PWM - 3guanitouNoch keine Bewertungen

- Modeling and Simulation of A PWM Rectifier Inverter Induction Motor Drive System Implementing Speed Sensor Less Direct Vector ControlDokument6 SeitenModeling and Simulation of A PWM Rectifier Inverter Induction Motor Drive System Implementing Speed Sensor Less Direct Vector ControlFarhan SarwarNoch keine Bewertungen

- Research PaperDokument10 SeitenResearch PaperVikas PatelNoch keine Bewertungen

- Space Vector Pulse Width Modulation Schemes For Two-Level Voltage Source InverterDokument5 SeitenSpace Vector Pulse Width Modulation Schemes For Two-Level Voltage Source InverterIDESNoch keine Bewertungen

- 2007-Comparison of 3D-SVPWM and Carrier-Based PWM of Three-PhaseDokument9 Seiten2007-Comparison of 3D-SVPWM and Carrier-Based PWM of Three-PhaseTài Nguyễn Minh NhậtNoch keine Bewertungen

- A SVM Based Four-Level Open-End Winding-Induction Motor Drive With Voltage Balancing of DC-link Capacitors Using SVM Based HCC Front-End ConverterDokument5 SeitenA SVM Based Four-Level Open-End Winding-Induction Motor Drive With Voltage Balancing of DC-link Capacitors Using SVM Based HCC Front-End ConverterGanesh ChallaNoch keine Bewertungen

- An SVM Algorithm To Balance The Capacitor Voltages of The Three-Level NPC APFDokument9 SeitenAn SVM Algorithm To Balance The Capacitor Voltages of The Three-Level NPC APFTran Quoc HoanNoch keine Bewertungen

- Ijret - Study of Sinusoidal and Space Vector Pulse Width Modulation Techniques For A Cascaded Three-Level InverterDokument6 SeitenIjret - Study of Sinusoidal and Space Vector Pulse Width Modulation Techniques For A Cascaded Three-Level InverterInternational Journal of Research in Engineering and TechnologyNoch keine Bewertungen

- FQC IISC-250kvaDokument23 SeitenFQC IISC-250kvaDeepak GehlotNoch keine Bewertungen

- Letters: Harmonic Analysis of Advanced Bus-Clamping PWM TechniquesDokument6 SeitenLetters: Harmonic Analysis of Advanced Bus-Clamping PWM TechniquesunnvishnuNoch keine Bewertungen

- Matlab-Simulink Model Three-Phase Voltage Source InverterDokument5 SeitenMatlab-Simulink Model Three-Phase Voltage Source InverterDương Tấn TàiNoch keine Bewertungen

- Minimization of Torque Ripple in PWM AC Drives: Kaushik Basu, J. S. Siva Prasad, and G. Narayanan, Member, IEEEDokument6 SeitenMinimization of Torque Ripple in PWM AC Drives: Kaushik Basu, J. S. Siva Prasad, and G. Narayanan, Member, IEEECharles KellyNoch keine Bewertungen

- Implementation of SVPWM Based Three Phase Inverter Using 8 Bit MicrocontrollerDokument5 SeitenImplementation of SVPWM Based Three Phase Inverter Using 8 Bit MicrocontrollermitulNoch keine Bewertungen

- Three-Level Inverter Performance Using Adaptive Neuro-Fuzzy Based Space Vector ModulationDokument14 SeitenThree-Level Inverter Performance Using Adaptive Neuro-Fuzzy Based Space Vector ModulationiisteNoch keine Bewertungen

- 06125602Dokument6 Seiten06125602Ahmad Sadam SyaeroziNoch keine Bewertungen

- Implementation of SVPWM Control On FPGA For Three Phase MATRIX CONVERTERDokument6 SeitenImplementation of SVPWM Control On FPGA For Three Phase MATRIX CONVERTERIDESNoch keine Bewertungen

- Analysis of Space Vector PWM For Three Phase Inverter and Comparison With SPWMDokument8 SeitenAnalysis of Space Vector PWM For Three Phase Inverter and Comparison With SPWMАлексей ЯмаNoch keine Bewertungen

- Cad Lab ManualDokument15 SeitenCad Lab ManualSougata Ghosh100% (2)

- Simulation of A Space Vector PWM Controller For A Five-Level Voltage-Fed Inverter Motor DriveDokument7 SeitenSimulation of A Space Vector PWM Controller For A Five-Level Voltage-Fed Inverter Motor DriveIOSRjournalNoch keine Bewertungen

- Hysteresis ControllerDokument9 SeitenHysteresis ControllerengrarNoch keine Bewertungen

- Evaluation of Current Ripple Amplitude in Three-Phase PWM Voltage Source InvertersDokument6 SeitenEvaluation of Current Ripple Amplitude in Three-Phase PWM Voltage Source InvertersluanleNoch keine Bewertungen

- Plecs SVMDokument5 SeitenPlecs SVMashikhmd4467Noch keine Bewertungen

- Three-Phase Diode Bridge RectifierDokument17 SeitenThree-Phase Diode Bridge RectifierLê Thiên ThanhNoch keine Bewertungen

- Modified Space Vector Modulated Z Source Inverter With Effective DC Boost and Lowest Switching StressDokument8 SeitenModified Space Vector Modulated Z Source Inverter With Effective DC Boost and Lowest Switching StressMounika DivyaNoch keine Bewertungen

- Space Vector ControlDokument21 SeitenSpace Vector ControlPoras KhetarpalNoch keine Bewertungen

- Comparison of New DPC Methods For Two-And Three-Level AC/DC ConvertersDokument6 SeitenComparison of New DPC Methods For Two-And Three-Level AC/DC ConvertersarezkifekikNoch keine Bewertungen

- Osciladores Ingles 1Dokument6 SeitenOsciladores Ingles 1Edwin Mauricio ArizaNoch keine Bewertungen

- SV ConceptDokument9 SeitenSV Conceptnaveen_90Noch keine Bewertungen

- Paper PublishDokument14 SeitenPaper PublishAshish PorwalNoch keine Bewertungen

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsVon EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNoch keine Bewertungen

- Some Power Electronics Case Studies Using Matlab Simpowersystem BlocksetVon EverandSome Power Electronics Case Studies Using Matlab Simpowersystem BlocksetNoch keine Bewertungen

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetVon EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetBewertung: 2 von 5 Sternen2/5 (1)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetVon EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNoch keine Bewertungen

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsVon EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNoch keine Bewertungen

- Implementation of Space Vector Pulse Width Modulation (SVPWM) For Three Phase Voltage Source Inverter Using Matlab Simulink - 24 PagesDokument24 SeitenImplementation of Space Vector Pulse Width Modulation (SVPWM) For Three Phase Voltage Source Inverter Using Matlab Simulink - 24 PagesMohamed Nabil100% (1)

- PV SimDokument4 SeitenPV SimAneek IslamNoch keine Bewertungen

- Development of A MATLAB/Simulink Model of A Single-Phase Grid-Connected Photovoltaic SystemDokument8 SeitenDevelopment of A MATLAB/Simulink Model of A Single-Phase Grid-Connected Photovoltaic SystemMohamed NabilNoch keine Bewertungen

- Direct Torque Control of Double Star Synchronous MachineDokument5 SeitenDirect Torque Control of Double Star Synchronous MachineMohamed NabilNoch keine Bewertungen

- Pangasinan State University Urdaneta Campus Urdaneta CityDokument11 SeitenPangasinan State University Urdaneta Campus Urdaneta CityNephtali Pinos-anNoch keine Bewertungen

- Blue Eyes Technology ReportDokument31 SeitenBlue Eyes Technology ReportShubham Chauhan S.Noch keine Bewertungen

- Nvidia DGX Os 4 Server: Software Release NotesDokument19 SeitenNvidia DGX Os 4 Server: Software Release Notesloreto07Noch keine Bewertungen

- CS-C12BKPG Cu-2c24bkp5gDokument70 SeitenCS-C12BKPG Cu-2c24bkp5gDũng LêNoch keine Bewertungen

- Knowledge Park: IT CBS & NONCBS: (Updated Upto 01.04.2023)Dokument20 SeitenKnowledge Park: IT CBS & NONCBS: (Updated Upto 01.04.2023)Surendra Kumar SethNoch keine Bewertungen

- Familiarization of Measuring Instruments and Tools HandoutDokument9 SeitenFamiliarization of Measuring Instruments and Tools HandoutVineeth WilsonNoch keine Bewertungen

- Mitsubishi RobotDokument48 SeitenMitsubishi RobotdanielNoch keine Bewertungen

- Pa0043 Sub Conor O'donnell PDFDokument7 SeitenPa0043 Sub Conor O'donnell PDFTheNewChildrensHospitalNoch keine Bewertungen

- Training Manual: TOTAL STATION Handling Guideline: Traverse and Detailing Summery GuidelineDokument10 SeitenTraining Manual: TOTAL STATION Handling Guideline: Traverse and Detailing Summery Guidelinenilmo surveyorsNoch keine Bewertungen

- Brilla SpaDokument16 SeitenBrilla SpaRaman SainiNoch keine Bewertungen

- LIFI PresentationDokument15 SeitenLIFI PresentationAditya SinghNoch keine Bewertungen

- DS01071 XNX Universal Transmitter FLR 8-3-11Dokument4 SeitenDS01071 XNX Universal Transmitter FLR 8-3-11itskittylimNoch keine Bewertungen

- 3.6.3 Function Block Diagram: 3 Operation TheoryDokument2 Seiten3.6.3 Function Block Diagram: 3 Operation TheoryAC DCNoch keine Bewertungen

- Guide To Computer Forensics InvestigationDokument65 SeitenGuide To Computer Forensics InvestigationAnthony WilsonNoch keine Bewertungen

- Cisco IOS For DummiesDokument29 SeitenCisco IOS For DummiesGary LuNoch keine Bewertungen

- UM HDL Buspro Setup Tool 2 (2020!05!23)Dokument32 SeitenUM HDL Buspro Setup Tool 2 (2020!05!23)crisma tariNoch keine Bewertungen

- Fyp ProposalDokument37 SeitenFyp ProposalNimra AzharNoch keine Bewertungen

- Time Table Spring 2022-2023 V2Dokument3 SeitenTime Table Spring 2022-2023 V2moad alsaityNoch keine Bewertungen

- Fully Automated 3D Colon Segmentation and Volume Rendering in Virtual RealityDokument9 SeitenFully Automated 3D Colon Segmentation and Volume Rendering in Virtual RealityJamil Al-idrusNoch keine Bewertungen

- Bocada GuideDokument24 SeitenBocada GuideKarthikeyan SundaramNoch keine Bewertungen

- Oscillating Cylinder With Git OpenFoamDokument9 SeitenOscillating Cylinder With Git OpenFoamM AliNoch keine Bewertungen

- S4 Analytics OptionsDokument6 SeitenS4 Analytics Optionsnewkaox2009Noch keine Bewertungen

- RTN 300 TrainingDokument21 SeitenRTN 300 TrainingJim Jr . OyolaNoch keine Bewertungen

- How To Configure An Anybus Controlnet Adapter/Slave Module With Rsnetworx For ControlnetDokument26 SeitenHow To Configure An Anybus Controlnet Adapter/Slave Module With Rsnetworx For ControlnetEcaterina IrimiaNoch keine Bewertungen

- Application Whitelisting: Approaches and ChallengesDokument6 SeitenApplication Whitelisting: Approaches and ChallengesijcseitjournalNoch keine Bewertungen

- Prime Time FeaturesDokument15 SeitenPrime Time FeaturesPruthwish PatelNoch keine Bewertungen

- Hex Inverter: BU4069UB / BU4069UBF / BU4069UBFVDokument4 SeitenHex Inverter: BU4069UB / BU4069UBF / BU4069UBFVjose omañaNoch keine Bewertungen

- 4ipnet Solution HotelDokument27 Seiten4ipnet Solution HotelAdrian Gamboa MarcellanaNoch keine Bewertungen

- Onto 1Dokument16 SeitenOnto 1DavidTumini Ogolo100% (1)

- Excel 2010 Data AnalysisDokument6 SeitenExcel 2010 Data AnalysisHugo MartinsNoch keine Bewertungen