Beruflich Dokumente

Kultur Dokumente

Analog Ders 1

Hochgeladen von

Eren TelifOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Analog Ders 1

Hochgeladen von

Eren TelifCopyright:

Verfügbare Formate

EECE488: Analog CMOS Integrated Circuit Design

Set 2: Background

1 SM

EECE 488 Set 2: Background

Shahriar Mirabbasi

Department of Electrical and Computer Engineering

University of British Columbia

shahriar@ece.ubc.ca

Technical contributions of Pedram Lajevardi in revising the slides is greatly acknowledged.

Overview

1. Reading Assignments

2. Structure of MOS Transistors

3. Threshold Voltage

4. Long-Channel Current Equations

5. Regions of Operation

6. Transconductance

7. Second-Order Effects

2 SM

EECE 488 Set 2: Background

7. Second-Order Effects

8. Short-Channel Effects

9. MOS Layout

10. Device Capacitances

11. Small-signal Models

12. Circuit Impedance

13. Equivalent Transconductance

Reading Assignments

Reading:

Chapter 2 of the textbook

Section 16.2 of the textbook

Chapter 17

3 SM

EECE 488 Set 2: Background

All the figures in the lecture notes are Design of Analog CMOS Integrated Circuits,

McGraw-Hill, 2001, unless otherwise noted.

Transistor

Transistor stands for

Transistor are semiconductor devices that can be classified as

Bipolar Junction Transistors (BJTs)

Field Effect Transistors (FETs)

4 SM

EECE 488 Set 2: Background

Field Effect Transistors (FETs)

Depletion-Mode FETs or (e.g., JFETs)

Enhancement-Mode FETs (e.g., MOSFETs)

Simplistic Model

MOS transistors have three terminals: Gate, Source, and Drain

The voltage of the Gate terminal determines the type of connection

between Source and Drain (Short or Open).

Thus, MOS devices behave like a switch

5 SM

EECE 488 Set 2: Background

Thus, MOS devices behave like a switch

Device is ON

D is shorted to S

Device is OFF

D & S are disconnected

V

G

low

Device is OFF

D & S are disconnected

Device is ON

D is shorted to S

V

G

high

PMOS NMOS

Physical Structure - 1

Source and Drain terminals are identical except that Source provides

charge carriers, and Drain receives them.

MOS devices have in fact 4 terminals:

Source, Drain, Gate, Substrate (bulk)

6 SM

EECE 488 Set 2: Background

Microelectronic Circuits, 2004 Oxford University Press

Physical Structure - 2

Charge Carriers are electrons in NMOS devices, and holes in

PMOS devices.

Electrons have a higher mobility than holes

So, NMOS devices are faster than PMOS devices

We rather to have a p-type substrate?!

7 SM

EECE 488 Set 2: Background

L

D

: Due to Side Diffusion

Poly-silicon used instead of Metal

for fabrication reasons

Actual length of the channel (L

eff

) is less than the length of gate

Physical Structure - 3

N-wells allow both NMOS and PMOS devices to reside on the

same piece of die.

8 SM

EECE 488 Set 2: Background

As mentioned, NMOS and PMOS devices have 4 terminals:

Source, Drain, Gate, Substrate (bulk)

In order to have all PN junctions reverse-biased, substrate of

NMOS is connected to the most negative voltage, and substrate

of PMOS is connected to the most positive voltage.

Physical Structure - 4

MOS transistor Symbols:

In NMOS Devices: Drain Source

electron

9 SM

EECE 488 Set 2: Background

In NMOS Devices:

Current flows from Drain to Source

In PMOS Devices:

Current flows from Source to Drain

Current flow determines which terminal is Source and which one

is Drain. Equivalently, source and drain can be determined based

on their relative voltages.

Drain Source

Drain Source

hole

Threshold Voltage - 1

Consider an NMOS: as the gate voltage is increased, the surface

under the gate is depleted. If the gate voltage increases more,

free electrons appear under the gate and a conductive channel is

formed.

10 SM

EECE 488 Set 2: Background

(a) An NMOS driven by a gate voltage, (b) formation of depletion region, (c) onset of inversion,

and (d) channel formation

As mentioned before, in NMOS devices charge carriers in the

channel under the gate are electrons.

Threshold Voltage - 2

Intuitively, the threshold voltage is the gate voltage that forces the

interface (surface under the gate) to be completely depleted of charge (in

NMOS the interface is as much n-type as the substrate is p-type)

Increasing gate voltage above this threshold (denoted by V

TH

or V

t

)

induces an inversion layer (conductive channel) under the gate.

11 SM

EECE 488 Set 2: Background

Microelectronic Circuits, 2004 Oxford University Press

Threshold Voltage - 3

Analytically:

ox

dep

F MS TH

C

Q

V + + = 2

Where:

Potential in - Built = =

Silicon gate MS

12 SM

EECE 488 Set 2: Background

substrate silicon the and gate n polysilico the

of functions work the between difference the =

|

|

\

|

= =

i

sub

F

n

N

q

T K

ln potential) atic (electrost Function Work

sub F si dep

N q Q = = 4 region depletion the in Charge

Threshold Voltage - 4

In practice, the native threshold value may not be suited for

circuit design, e.g., V

TH

may be zero and the device may be on for

any positive gate voltage.

Typically threshold voltage is adjusted by ion implantation into the

channel surface (doping P-type material will increase V

TH

of

NMOS devices).

13 SM

EECE 488 Set 2: Background

When V

DS

is zero, there is no horizontal electric field present in the

channel, and therefore no current between the source to the drain.

When V

DS

is more than zero, there is some horizontal electric field

which causes a flow of electrons from source to drain.

Long Channel Current Equations - 1

The voltage of the surface under the gate, V(x), depends on the

voltages of Source and Drain.

If V

DS

is zero, V

D

= V

S

=V(x). The charge density Q

d

(unit C/m) is uniform.

) (

TH GS ox d

V V WC Q =

( ) ( )

L

V V WL C

L

V C

L

Q

Q

TH GS ox

d

=

=

=

14 SM

EECE 488 Set 2: Background

) ) ( ( ) (

TH GS ox d

V x V V WC x Q =

If V

DS

is not zero, the channel is tapered, and V(x) is not constant. The

charge density depends on x.

Long Channel Current Equations - 3

velocity Q

dt

dx

dx

dQ

dt

dQ

I

d

= = =

dt

dV

E E velocity = = ,

)

) (

(

dx

x dV

velocity

=

Current :

Velocity in terms of V(x):

Q

d

in terms of V(x):

15 SM

EECE 488 Set 2: Background

) ) ( ( ) (

TH GS ox d

V x V V WC x Q =

= =

DS

V

V

TH GS n ox

L

x

D

dV V x V V WC dx I

0 0

] ) ( [

]

2

1

) [(

2

DS DS TH GS ox n D

V V V V

L

W

C I =

dx

x dV

V x V V WC I

n TH GS ox D

) (

] ) ( [ =

Current in terms of V(x):

Long-channel current equation:

Microelectronic Circuits, 2004 Oxford University Press

Long Channel Current Equations - 4

( )

(

=

2

2

1

DS DS TH GS ox n D

V V V V

L

W

C I

Current in Triode Region:

If V

DS

V

GS

-V

TH

we say the device is operating in triode (or linear) region.

16 SM

EECE 488 Set 2: Background

Terminology:

eff TH GS

V V V Voltage Effective Voltage Overdrive

L

W

Ratio Aspect

= = =

=

Long Channel Current Equations - 5

For very small V

DS

(deep Triode Region):

I

D

can be approximated to be a linear function of V

DS

.

The device resistance will be independent of V

DS

and will

only depend on V

eff

.

The device will behave like a variable resistor

17 SM

EECE 488 Set 2: Background

( )

( )

( )

TH GS ox n

D

DS

ON

DS TH GS ox n D

TH GS DS

V V

L

W

C

I

V

R

V V V

L

W

C I

V V V If

= =

=

<<

1

: 2

Long Channel Current Equations - 6

Increasing V

DS

causes the channel to acquire a tapered shape. Eventually,

as V

DS

reaches V

GS

V

TH

the channel is pinched off at the drain. Increasing

V

DS

above V

GS

V

TH

has little effect (ideally, no effect) on the channels

shape.

18 SM

EECE 488 Set 2: Background

Microelectronic Circuits, 2004 Oxford University Press

When V

DS

is more than V

GS

V

TH

the channel is pinched off, and the

horizontal electric field produces a current.

Long Channel Current Equations - 7

If V

DS

> V

GS

V

TH

, the transistor is in saturation (active) region,

and the channel is pinched off.

=

TH GS

V V

L'

19 SM

EECE 488 Set 2: Background

= =

TH GS

V V

V

TH GS n ox

L

x

D

dV V x V V WC dx I

0

'

0

] ) ( [

2

) (

' 2

1

TH GS ox n D

V V

L

W

C I =

Lets, for now, assume that L=L. The fact that

L is not equal to L is a second-order effect

known as channel-length modulation.

Since I

D

only depends on V

GS

, MOS transistors in saturation can be

used as current sources.

Long Channel Current Equations - 8

Current Equation for NMOS:

( )

<< >

<

= =

) ( ) ( 2 , ;

) ( ; 0

Triode Deep V V V V V if V V V

L

W

C

off Cut V V if

I I

TH GS DS TH GS DS TH GS ox n

TH GS

20 SM

EECE 488 Set 2: Background

( ) [ ]

> >

< >

= =

) ( , ; ) (

2

1

) ( , ;

2

1

2

2

Saturation V V V V V if V V

L

W

C

Triode V V V V V if V V V V

L

W

C

I I

TH GS DS TH GS TH GS ox n

TH GS DS TH GS DS DS TH GS ox n

DS D

Long Channel Current Equations - 9

Current Equation for PMOS:

( )

<< >

<

= =

) ( ) ( 2 , ;

) ( ; 0

Triode Deep V V V V V if V V V

L

W

C

off Cut V V if

I I

TH SG SD TH SG SD TH SG ox p

TH SG

21 SM

EECE 488 Set 2: Background

( ) [ ]

> >

< >

= =

) ( , ; ) (

2

1

) ( , ;

2

1

2

2

Saturation V V V V V if V V

L

W

C

Triode V V V V V if V V V V

L

W

C

I I

TH SG SD TH SG TH SG ox p

TH SG SD TH SG SD SD TH SG ox p

SD D

Regions of Operation - 1

Regions of Operation:

Cut-off, triode (linear), and saturation (active or pinch-off)

22 SM

EECE 488 Set 2: Background

Microelectronic Circuits, 2004 Oxford University Press

Once the channel is pinched off, the current through the channel is

almost constant. As a result, the I-V curves have a very small slope in

the pinch-off (saturation) region, indicating the large channel

resistance.

Regions of Operation - 2

The following illustrates the transition from pinch-off to triode region for

NMOS and PMOS devices.

23 SM

EECE 488 Set 2: Background

For NMOS devices:

If V

D

increases (V

G

Const.), the device will go from Triode to Pinch-off.

If V

G

increases (V

D

Const.), the device will go from Pinch-off to Triode.

** In NMOS, as V

DG

increases the device will go from Triode to Pinch-off.

For PMOS devices:

If V

D

decreases (V

G

Const.), the device will go from Triode to Pinch-off.

If V

G

decreases (V

D

Const.), the device will go from Pinch-off to Triode.

** In PMOS, as V

GD

increases the device will go from Pinch-off to Triode.

Regions of Operation - 3

NMOS Regions of Operation:

24 SM

EECE 488 Set 2: Background

Microelectronic Circuits, 2004 Oxford University Press

Relative levels of the terminal voltages of the enhancement-type NMOS

transistor for different regions of operation.

Regions of Operation - 4

PMOS Regions of Operation:

25 SM

EECE 488 Set 2: Background

Microelectronic Circuits, 2004 Oxford University Press

The relative levels of the terminal voltages of the enhancement-type

PMOS transistor for different regions of operation.

Regions of Operation - 5

Example:

For the following circuit assume that V

TH

=0.7V.

When is the device on?

What is the region of operation if the device is on?

26 SM

EECE 488 Set 2: Background

Sketch the on-resistance of transistor M

1

as a function of V

G

.

Transconductance - 1

The drain current of the MOSFET in saturation region is ideally a

function of gate-overdrive voltage (effective voltage). In reality, it is also

a function of V

DS

.

It makes sense to define a figure of merit that indicates how well the

device converts the voltage to current.

Which current are we talking about?

27 SM

EECE 488 Set 2: Background

Which current are we talking about?

What voltage is in the designers control?

What is this figure of merit?

. Const V V

I

g

DS GS

D

m

=

=

Transconductance - 2

Transconductance in triode:

( ) [ ]

V V V V

W

C g

|

|

=

1

2

Example:

Plot the transconductance of the following circuit as a function of V

DS

(assume V

b

is a constant voltage).

28 SM

EECE 488 Set 2: Background

Transconductance in saturation:

( ) [ ]

DS ox n

DS

DS DS TH GS ox n

GS

m

V

L

W

C

Const V

V V V V

L

W

C

V

g

=

=

|

\

|

. 2

1

2

) (

.

) (

2

1

2

TH GS ox n

DS

TH GS ox n

GS

m

V V

L

W

C

Const V

V V

L

W

C

V

g

=

=

|

\

|

Moral: Transconductance drops if the device enters the triode region.

Transconductance - 3

Transconductance, g

m

, in saturation:

TH GS

D

D ox n TH GS ox n m

V V

I

I

L

W

C V V

L

W

C g

= = =

2

2 ) (

If the aspect ratio is constant: g

m

depends linearly on (V

GS

- V

TH

).

Also, g

m

depends on square root of I

D

.

If I

D

is constant: g

m

is inversely proportional to (V

GS

- V

TH

).

29 SM

EECE 488 Set 2: Background

D m GS TH

Also, g

m

depends on square root of the aspect ratio.

If the overdrive voltage is constant: g

m

depends linearly on I

D

.

Also, g

m

depends linearly on the aspect ratio.

Second-Order Effects (Body Effect)

Substrate Voltage:

So far, we assumed that the bulk and source of the transistor are at the

same voltage (V

B

=V

S

).

If V

B

>V

s

, then the bulk-source PN junction will be forward biased, and

the device will not operate properly.

If V

B

<V

s

,

the bulk-source PN junction will be reverse biased.

the depletion region widens, and Q

dep

increases.

30 SM

EECE 488 Set 2: Background

the depletion region widens, and Q

dep

increases.

V

TH

will be increased (Body effect or Backgate effect).

It can be shown that (what is the unit for ?):

ox

sub si

F SB F TH TH

C

N q

V V V

=

|

\

|

+ + =

2

2 2

0

where

Body Effect - 2

Example:

Consider the circuit below (assume the transistor is in the active region):

If body-effect is ignored, V

TH

will be constant, and I

1

will only depend on

V

GS1

=V

in

-V

out

. Since I

1

is constant, V

in

-V

out

remains constant.

In general, I

1

depends on V

GS1

- V

TH

=V

in

-V

out

-V

TH

(and with body effect

V

TH

is not constant). Since I

1

is constant, V

in

-V

out

-V

TH

remains constant:

. . Conts D C V V V Const C V V V

TH out in TH out in

= = + = = =

31 SM

EECE 488 Set 2: Background

No Body Effect With Body Effect

C V V V Const C V V V

TH out in TH out in

+ = = = .

As V

out

increases, V

SB1

increases, and as a result V

TH

increases.

Therefore, V

in

-V

out

Increases.

V

TH

is not constant). Since I

1

is constant, V

in

-V

out

-V

TH

remains constant:

Body Effect - 3

Example:

For the following Circuit sketch the drain current of transistor M

1

when V

X

varies from -

to 0. Assume V

TH0

=0.6V, =0.4V

1/2

, and 2

F

=0.7V.

32 SM

EECE 488 Set 2: Background

Channel Length Modulation - 1

L

When a transistor is in the saturation region (V

DS

> V

GS

V

TH

),

the channel is pinched off.

The drain current is

L L- L' V V

W

C I

TH GS ox n D

= = where

2

) (

1

33 SM

EECE 488 Set 2: Background

( )

L

L

L

L

L

L L L L

=

= 1

1

1

1 1 1

'

1

The drain current is

L L- L' V V

L

W

C I

TH GS ox n D

= = where

2

) (

' 2

1

Assuming we get:

DS

V

L

L

=

( ) ( )

DS

V

L

L

L

L L

+ =

+ 1

1

1

1

'

1

The drain current is

( ) ( )

DS TH GS ox n TH GS ox n D

V V V

L

W

C V V

L

W

C I + = 1

2

1

) (

' 2

1

2

2

As I

D

actually depends on both V

GS

and V

DS

, MOS transistors are

not ideal current sources (why?).

Channel Length Modulation - 2

represents the relative variation in effective length of the channel for a given

increment in V

DS

.

For longer channels is smaller, i.e., 1/L

Transconductance:

In Triode:

. Const V V

I

g

DS GS

D

m

=

=

DS ox n m

V

L

W

C g =

34 SM

EECE 488 Set 2: Background

In Saturation (ignoring channel length modulation):

In saturation with channel length modulation:

The dependence of I

D

on V

DS

is much weaker than its dependence on V

GS

.

DS ox n m

V

L

C g =

TH GS

D

D ox n TH GS ox n m

V V

I

I

L

W

C V V

L

W

C g

= = =

2

2 ) (

( ) ( )

TH GS

D

DS D ox n DS TH GS ox n m

V V

I

V I

L

W

C V V V

L

W

C g

= + = + =

2

1 2 1 ) (

Channel Length Modulation - 3

Example:

Given all other parameters constant, plot I

D

-V

DS

characteristic of an NMOS

for L=L

1

and L=2L

1

( ) ( )

2

1

2

1

V V V

L

W

C I

DS TH GS ox n D

+

In Triode Region:

In Saturation Region:

( ) [ ]

L

W

V

I

V V V V

L

W

C I

DS

D

DS DS TH GS ox n D

: Therefore

2

2

1

35 SM

EECE 488 Set 2: Background

( )

2

2

2

1

2

L

W

L

W

V

I

V V

L

W

C

V

I

L

DS

D

TH GS ox n

DS

D

: Therefore

: get we So

Changing the length of the device from L

1

to 2L

1

will flatten the I

D

-V

DS

curves (slope will be divided by two in triode and by four in saturation).

Increasing L will make a transistor a better current source, while

degrading its current capability.

Increasing W will improve the current capability.

Sub-threshold Conduction

If V

GS

< V

TH

, the drain current is not zero.

The MOS transistors behave similar to BJTs.

In BJT:

In MOS:

T

BE

V

V

S C

e I I =

T

GS

V

V

e I I

=

36 SM

EECE 488 Set 2: Background

In MOS:

As shown in the figure, in MOS transistors, the drain current drops by

one decade for approximately each 80mV of drop in V

GS

.

In BJT devices the current drops faster (one decade for approximately

each 60mv of drop in V

GS

).

This current is known as sub-threshold or weak-inversion conduction.

T

D

e I I =

0

CMOS Processing Technology

Top and side views of a typical CMOS process

37 SM EECE 588 Set 1: Introduction and Background

CMOS Processing Technology

Different layers comprising CMOS transistors

38 SM EECE 588 Set 1: Introduction and Background

Photolithography (Lithography)

Used to transfer circuit layout information to the wafer

39 SM EECE 588 Set 1: Introduction and Background

Typical Fabrication Sequence

40 SM

Self-Aligned Process

Why source and drain junctions are formed after the gate oxide

and polysilicon layers are deposited?

41 SM EECE 588 Set 1: Introduction and Background

Back-End Processing

Oxide spacers and silicide

42 SM EECE 588 Set 1: Introduction and Background

Back-End Processing

Contact and metal layers fabrication

43 SM EECE 588 Set 1: Introduction and Background

Back-End Processing

Large contact areas should be avoided to minimize the

possibility of spiking

44 SM EECE 588 Set 1: Introduction and Background

MOS Layout - 1

It is beneficial to have some insight into the layout of the MOS devices.

When laying out a design, there are many important parameters we

45 SM

EECE 488 Set 2: Background

When laying out a design, there are many important parameters we

need to pay attention to such as: drain and source areas,

interconnects, and their connections to the silicon through contact

windows.

Design rules determine the criteria that a circuit layout must meet for a

given technology. Things like, minimum length of transistors, minimum

area of contact windows,

MOS Layout - 2

Example:

Figures below show a circuit with a suggested layout.

46 SM

EECE 488 Set 2: Background

The same circuit can be laid out in different ways, producing different

electrical parameters (such as different terminal capacitances).

Device Capacitances - 1

The quadratic model determines the DC behavior of a MOS transistor.

The capacitances associated with the devices are important when

studying the AC behavior of a device.

There is a capacitance between any two terminals of a MOS transistor.

So there are 6 Capacitances in total.

The Capacitance between Drain and Source is negligible (C

DS

=0).

47 SM

EECE 488 Set 2: Background

These capacitances will depend on the region of operation (Bias

values).

Device Capacitances - 2

The following will be used to calculate the capacitances between

terminals:

1. Oxide Capacitance: ,

2. Depletion Capacitance:

3. Overlap Capacitance:

4. Junction Capacitance:

ox

C L W C =

1

ox

ox

ox

t

C

=

F

sub si

dep

N q

L W C C

= =

4

2

fringe ox D ov

C C L W C C C + = = =

4 3

48 SM

EECE 488 Set 2: Background

Sidewall Capacitance:

Bottom-plate Capacitance:

m

B

R

j

jun

V

C

C

(

+

=

1

0

jsw

C

j

C

jsw j

C C C C + = =

6 5

Device Capacitances - 3

In Cut-off:

1. C

GS

: is equal to the overlap capacitance.

2. C

GD

: is equal to the overlap capacitance.

3. C

GB

: is equal to C

gate-channel

= C

1

in series with C

channel-bulk

= C

2

.

4. C

SB

: is equal to the junction capacitance between source and

bulk.

3

C C C

ov GS

= =

4

C C C

ov GD

= =

49 SM

EECE 488 Set 2: Background

5. C

DB

: is equal to the junction capacitance between source and

bulk.

5

C C

SB

=

6

C C

DB

=

Device Capacitances - 4

In Triode:

The channel isolates the gate from the substrate. This means that if V

G

changes, the charge of the inversion layer are supplied by the drain

and source as long as V

DS

is close to zero. So, C

1

is divided between

gate and drain terminals, and gate and source terminals, and C

2

is

divided between bulk and drain terminals, and bulk and source

terminals.

1. C

GS

:

2

1

C

C C

ov GS

+ =

50 SM

EECE 488 Set 2: Background

1. C

GS

:

2. C

GD

:

3. C

GB

: the channel isolates the gate from the substrate.

4. C

SB

:

5. C

DB

:

0 =

GB

C

2

C C

ov GS

+ =

2

2

5

C

C C

SB

+ =

2

2

6

C

C C

DB

+ =

2

1

C

C C

ov GD

+ =

Device Capacitances - 5

In Saturation:

The channel isolates the gate from the substrate. The voltage across

the channel varies which can be accounted for by adding two

equivalent capacitances to the source. One is between source and

gate, and is equal to two thirds of C

1

. The other is between source and

bulk, and is equal to two thirds of C

2

.

1. C

GS

:

2. C

GD

:

1

3

2

C C C

ov GS

+ =

C C =

51 SM

EECE 488 Set 2: Background

2. C

GD

:

3. C

GB

: the channel isolates the gate from the substrate.

4. C

SB

:

5. C

DB

:

0 =

GB

C

2 5

3

2

C C C

SB

+ =

6

C C

DB

=

ov GD

C C =

Device Capacitances - 6

In summary:

C

GB

C

GD

C

GS

Saturation Triode Cut-off

ov

C

ov

C

ov

C

1

3

2

C C

ov

+

0

2

1

C

C

ov

+

2

1

C

C

ov

+

0

1

2 1

C C

C C

C C

GB

+

52 SM

EECE 488 Set 2: Background

C

DB

C

SB 2 5

3

2

C C +

6

C

2

2

6

C

C +

2

2

5

C

C +

1

2 1

C C

GB

+

6

C

5

C

Importance of Layout

Example (Folded Structure):

Calculate the gate resistance of the circuits shown below.

53 SM EECE 588 Set 1: Introduction and Background

Folded structure:

Decreases the drain capacitance

Decreases the gate resistance

Keeps the aspect ratio the same

Passive Devices

Resistors

54 SM EECE 588 Set 1: Introduction and Background

Passive Devices

Capacitors:

55 SM EECE 588 Set 1: Introduction and Background

Passive Devices

Capacitors

56 SM EECE 588 Set 1: Introduction and Background

Passive Devices

Inductors

57 SM EECE 588 Set 1: Introduction and Background

Latch-Up

Due to parasitic bipolar transistors in a CMOS process

58 SM EECE 588 Set 1: Introduction and Background

Small Signal Models - 1

Small signal model is an approximation of the large-signal model

around the operation point.

In analog circuits most MOS transistors are biased in saturation region.

In general, I

D

is a function of V

GS

, V

DS

, and V

BS

. We can use this Taylor

series approximation:

59 SM

EECE 488 Set 2: Background

BS mb

o

DS

GS m BS

BS

D

DS

DS

D

GS

GS

D

D

BS

BS

D

DS

DS

D

GS

GS

D

D D

V g

r

V

V g V

V

I

V

V

I

V

V

I

I

V

V

I

V

V

I

V

V

I

I I

+

+ =

+ = s order term second : Expansion Taylor

0

Small Signal Models - 2

Current in Saturation:

Taylor approximation:

Partial Derivatives:

( ) ( )

DS TH GS ox n TH GS ox n D

V V V

L

W

C V V

L

W

C I + = 1

2

1

) (

' 2

1

2

2

BS

BS

D

DS

DS

D

GS

GS

D

D

V

V

I

V

V

I

V

V

I

I

( )

m DS TH GS ox n

GS

D

g V V V

L

W

C

V

I

= + =

1 ) (

60 SM

EECE 488 Set 2: Background

( )

mb m

SB F

m

SB F

DS TH GS ox n

BS

TH

TH

D

BS

D

o

D TH GS ox n

DS

D

GS

g g

V

g

V

V V V

L

W

C

V

V

V

I

V

I

r

I V V

L

W

C

V

I

L V

= =

(

(

+

=

(

(

+

(

+ =

= =

2 2

2 2

1 ) (

1

) (

2

1

2

Small Signal Models - 3

Small-Signal Model:

BS mb

o

DS

GS m D

v g

r

v

v g i + + =

Terms, g

m

v

GS

and g

mb

v

BS

, can be modeled by dependent sources.

These terms have the same polarity: increasing v

G

, has the same

effect as increasing v

B

.

The term, v

DS

/r

o

can be modeled using a resistor as shown below.

61 SM

EECE 488 Set 2: Background

Small Signal Models - 4

Complete Small-Signal Model with Capacitances:

62 SM

EECE 488 Set 2: Background

Small signal model including all the capacitance makes the intuitive

(qualitative) analysis of even a few-transistor circuit difficult!

Typically, CAD tools are used for accurate circuit analysis

For intuitive analysis we try to find a simplest model that can represent

the role of each transistor with reasonable accuracy.

Circuit Impedance - 1

It is often useful to determine the impedance of a circuit seen from a

specific pair of terminals.

The following is the recipe to do so:

1. Connect a voltage source, V

X

, to the port.

2. Suppress all independent sources.

3. Measure or calculate I

X

.

63 SM

EECE 488 Set 2: Background

X

X

X

I

V

R =

Circuit Impedance - 2

Example:

Find the small-signal impedance of the following current

sources.

We draw the small-signal model, which is the same for both

circuits, and connect a voltage source as shown below:

64 SM

EECE 488 Set 2: Background

o

X

X

X

o

X

GS m

o

X

X

r

i

v

R

r

v

v g

r

v

i

= =

= + =

Circuit Impedance - 3

Example:

Find the small-signal impedance of the following circuits.

We draw the small-signal model, which is the same for both

circuits, and connect a voltage source as shown below:

65 SM

EECE 488 Set 2: Background

mb m

o

mb m

o

X

X

X

X mb X m

o

X

BS mb GS m

o

X

X

g g

r

g g

r

i

v

R

v g v g

r

v

v g v g

r

v

i

1 1

1

1

=

+ +

= =

+ + = =

Circuit Impedance - 4

Example:

Find the small-signal impedance of the following circuit. This

circuit is known as the diode-connected load, and is used

frequently in analog circuits.

We draw the small-signal model and connect the voltage

source as shown below:

v v 1 | |

66 SM

EECE 488 Set 2: Background

m

o

m

o

X

X

X

m

o

X X m

o

X

GS m

o

X

X

g

r

g

r

i

v

R

g

r

v v g

r

v

v g

r

v

i

1

1

1

1

=

+

= =

|

|

\

|

+ = + = + =

If channel length modulation is ignored (r

o

=) we get:

m m m

o X

g g g

r R

1 1 1

= = =

Circuit Impedance - 5

Example:

Find the small-signal impedance of the following circuit. This

circuit is a diode-connected load with body effect.

mb m X

X mb X m

o

X

BS mb GS m

o

X

X

g g

r

v

v g v g

r

v

v g v g

r

v

i

1

|

|

\

|

+ + =

+ + = =

67 SM

EECE 488 Set 2: Background

mb m

o

mb m

o

mb m

o

X

X

X

mb m

o

X

g g

r

g g

r

g g

r

i

v

R

g g

r

v

1 1 1

1

1

=

+

=

+ +

= =

|

|

\

+ + =

If channel length modulation is ignored (r

o

=) we get:

mb m mb m mb m mb m

o X

g g g g g g g g

r R

1 1 1 1 1

=

+

=

+

=

+

=

Equivalent Transconductance - 1

Recall that the transconductance of a transistor was a a figure of

merit that indicates how well the device converts a voltage to current.

It is sometimes useful to define the equivalent transconductance of a

circuit as follows:

. Const V V

I

g

DS GS

D

m

=

=

. Const V V

I

G

OUT

m

=

=

68 SM

EECE 488 Set 2: Background

. Const V V

G

OUT IN

m

=

=

The following is a small-signal block diagram of an arbitrary circuit

with a Norton equivalent at the output port. We notice that:

V

OUT

=Constant so v

OUT

=0 in the small signal model.

0 =

=

OUT IN

OUT

m

v v

i

G

Equivalent Transconductance - 2

Example:

Find the equivalent transconductance of an NMOS transistor

in saturation from its small-signal model.

69 SM

EECE 488 Set 2: Background

m

IN

OUT

m

IN m GS m OUT

g

v

i

G

v g v g i

= =

= =

Equivalent Transconductance - 3

Example:

Find the equivalent transconductance of the following circuit

when the NMOS transistor in saturation.

70 SM

EECE 488 Set 2: Background

( )

( )

S S mb S m O O

O m

O

S

S mb S m

m

IN

OUT

m

IN m

O

S

S mb S m OUT

O

S OUT

S OUT mb S OUT IN m

O

S

BS mb GS m OUT

S OUT GS S GS IN

R R g R g r r

r g

r

R

R g R g

g

v

i

G

v g

r

R

R g R g i

r

R i

R i g R i v g

r

v

v g v g i

R i v v v v

+ + +

=

+ + +

= =

=

|

|

\

|

+ + +

+ = + =

+ = + =

1

1

) (

Short-Channel Effects

Threshold Reduction

Drain-induced barrier lowering (DIBL)

Mobility degradation

Velocity saturation

71 SM

EECE 488 Set 2: Background

Velocity saturation

Hot carrier effects

Substrate current

Gate current

Output impedance variation

Threshold Voltage Variation in Short Channel Devices

The Threshold of transistors fabricated on the same chip decreases as

the channel length decreases.

72 SM

EECE 488 Set 2: Background

Intuitively, the extent of depletion regions associated with drain and

source in the channel area, reduces the immobile charge that must be

imaged by the charge on the gate.

Drain-Induced Barrier Lowering (DIBL)

When the channel is short, the drain

voltage increases the channel surface

potential, lowering the barrier to flow

charge from source (think of increased

electric field) and therefore, decreasing

the threshold.

73 SM

EECE 488 Set 2: Background

Effects of Velocity Saturation

Due to drop in mobility at high electric fields

74 SM

EECE 488 Set 2: Background

(a) Premature drain current saturation and (b) reduction in g

m

Hot Carrier Effects

Short channel devices may experience high lateral drain-source

electric field

Some carriers that make it to drain have high velocity (called

hot carriers)

Hot carriers may hit silicon atoms at high speed and cause

75 SM

EECE 488 Set 2: Background

Hot carriers may hit silicon atoms at high speed and cause

impact ionization

The resulting electron and holes are absorbed by the drain and

substrate causing extra drain-substrate current

Really hot carriers may be injected into gate oxide and flow out

of gate causing gate current!

Output Impedance Variation

Recall the definition of .

76 SM

EECE 488 Set 2: Background

Output Impedance Variation in Short-Channel Devices

77 SM

EECE 488 Set 2: Background

Das könnte Ihnen auch gefallen

- Electronics Ch5Dokument30 SeitenElectronics Ch5Santi Navarro MoralNoch keine Bewertungen

- TalkDokument27 SeitenTalksonsfhsdlfhsadhNoch keine Bewertungen

- Chapter 1Dokument78 SeitenChapter 1hwangzang.nguyenkhacNoch keine Bewertungen

- MOSFET DC AnalysisDokument20 SeitenMOSFET DC AnalysisAllen ChandlerNoch keine Bewertungen

- Complete Vlsi NotesDokument160 SeitenComplete Vlsi NotesTarun SinghalNoch keine Bewertungen

- 02 Iniguez MOS-AKDokument50 Seiten02 Iniguez MOS-AKChristopher Praveen KumarNoch keine Bewertungen

- Introduction To Digital ElectronicsDokument22 SeitenIntroduction To Digital ElectronicsLeandroRicardoNoch keine Bewertungen

- Mos ModelsDokument39 SeitenMos Modelsch0071Noch keine Bewertungen

- Mos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorDokument14 SeitenMos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorKumar Amit VermaNoch keine Bewertungen

- FETDokument91 SeitenFETpawan_32Noch keine Bewertungen

- MOS Rabaey PDFDokument32 SeitenMOS Rabaey PDFalamgirNoch keine Bewertungen

- Lect 2 New (Capacitors)Dokument39 SeitenLect 2 New (Capacitors)Vineeth KamisettyNoch keine Bewertungen

- MOS Transistor Theory: OutlineDokument24 SeitenMOS Transistor Theory: OutlineCarlos AzevedoNoch keine Bewertungen

- Long Channel MOSFET 4Dokument27 SeitenLong Channel MOSFET 4Cruise_IceNoch keine Bewertungen

- Short Channel EffectsDokument15 SeitenShort Channel Effectsgene_palencia100% (1)

- (NAAC Accredited "A++" Grade University) : Koneru Lakshmaiah Education FoundationDokument13 Seiten(NAAC Accredited "A++" Grade University) : Koneru Lakshmaiah Education FoundationLakshmi JagupillaNoch keine Bewertungen

- 3.5 MOSFET Scaling and Small-Geometry EffectsDokument19 Seiten3.5 MOSFET Scaling and Small-Geometry Effectspraritlamba25Noch keine Bewertungen

- Vlsi Design: Mos TransistorDokument162 SeitenVlsi Design: Mos TransistorBasheer V.PNoch keine Bewertungen

- Analog Circuit Design Notes-2Dokument85 SeitenAnalog Circuit Design Notes-2itsnirosNoch keine Bewertungen

- Vlsi Topic2bDokument4 SeitenVlsi Topic2bsyabseeshoesNoch keine Bewertungen

- Field Effect TransistorsDokument40 SeitenField Effect TransistorsRatanNoch keine Bewertungen

- Unit-I VLSI & CDDokument39 SeitenUnit-I VLSI & CD21EC17- JAYA PRASAD.PNoch keine Bewertungen

- Lecture10 MOS Field Effect Transistors v1Dokument33 SeitenLecture10 MOS Field Effect Transistors v1Dr-Suraj Kumar SawNoch keine Bewertungen

- VLSI Design Lecture NotesDokument117 SeitenVLSI Design Lecture NotesRaji SharmiNoch keine Bewertungen

- Basic MOS Device Physics: Zou Zhige 2007 HUSTDokument62 SeitenBasic MOS Device Physics: Zou Zhige 2007 HUSTSHIVA VERMANoch keine Bewertungen

- Analog & Digital Electronics: Course No: Ph-218 Lec-26: Metal Oxide Field Effect Transistors (Mosfets)Dokument16 SeitenAnalog & Digital Electronics: Course No: Ph-218 Lec-26: Metal Oxide Field Effect Transistors (Mosfets)Udai SinghNoch keine Bewertungen

- DIC PPT Unit I, II & III PDFDokument371 SeitenDIC PPT Unit I, II & III PDFyeswanthNoch keine Bewertungen

- VLSI Notes 1 PDFDokument305 SeitenVLSI Notes 1 PDFKishore KumarNoch keine Bewertungen

- MOS Transistor Operation: S/D GateDokument10 SeitenMOS Transistor Operation: S/D GateConcetto CantoneNoch keine Bewertungen

- Mosfet ScalingDokument0 SeitenMosfet ScalingKeith FernandesNoch keine Bewertungen

- NMOS FundamentalsDokument71 SeitenNMOS FundamentalsManjit KaurNoch keine Bewertungen

- MOS Field-Effect Transistor (Mosfet)Dokument40 SeitenMOS Field-Effect Transistor (Mosfet)Trần Minh NhậtNoch keine Bewertungen

- Lec 15Dokument9 SeitenLec 15Mohammed Ahmad OsamaNoch keine Bewertungen

- Mosfet SDokument25 SeitenMosfet SZZZZZ5Noch keine Bewertungen

- Mosfet Lab 1Dokument11 SeitenMosfet Lab 1Pramod SnkrNoch keine Bewertungen

- Mosfet: Device StructureDokument15 SeitenMosfet: Device StructureNoorullah ShariffNoch keine Bewertungen

- MOS Field-Effect Transistor MOSFETDokument34 SeitenMOS Field-Effect Transistor MOSFETFrank WanderiNoch keine Bewertungen

- Csce 3303 - Fundamental MicroelectronicsDokument16 SeitenCsce 3303 - Fundamental MicroelectronicsSameh SherifNoch keine Bewertungen

- IEEE Presentation On Properties of Digital Switching Currents (C'MOS)Dokument21 SeitenIEEE Presentation On Properties of Digital Switching Currents (C'MOS)Trivendra JoshiNoch keine Bewertungen

- L #5: Mosfet C A: Sfsu - E 301 - E L AB Haracteristics and PplicationsDokument14 SeitenL #5: Mosfet C A: Sfsu - E 301 - E L AB Haracteristics and PplicationsRudra MishraNoch keine Bewertungen

- FETDokument49 SeitenFETPalak Agrawal100% (2)

- Basic Electrical Properties of MosDokument10 SeitenBasic Electrical Properties of Mosmayamohan725Noch keine Bewertungen

- Vlsi Design - Ec - 701 - Unit - 2Dokument18 SeitenVlsi Design - Ec - 701 - Unit - 2angelcrystl4774Noch keine Bewertungen

- Electrical Properties of Mos DeviceDokument28 SeitenElectrical Properties of Mos Devicemayamohan7250% (1)

- Mosfet OperationDokument70 SeitenMosfet OperationTanmayBangaloreNoch keine Bewertungen

- Ee3 Mosfet ReviewDokument58 SeitenEe3 Mosfet ReviewkaaashuNoch keine Bewertungen

- DC Characteristics of A MOS Transistor (MOSFET) : Created in COMSOL Multiphysics 5.3Dokument20 SeitenDC Characteristics of A MOS Transistor (MOSFET) : Created in COMSOL Multiphysics 5.3Anika TabassumNoch keine Bewertungen

- Pid00050 2 CmosDokument8 SeitenPid00050 2 CmosSaurabh ChakravartyNoch keine Bewertungen

- MOS Integrated Circuit DesignVon EverandMOS Integrated Circuit DesignE. WolfendaleNoch keine Bewertungen

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterVon EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1Von EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1Noch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- It Is Quite Another Electricity: Transmitting by One Wire and Without GroundingVon EverandIt Is Quite Another Electricity: Transmitting by One Wire and Without GroundingBewertung: 4.5 von 5 Sternen4.5/5 (2)

- Differential Forms on Electromagnetic NetworksVon EverandDifferential Forms on Electromagnetic NetworksBewertung: 4 von 5 Sternen4/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Von EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Bewertung: 4.5 von 5 Sternen4.5/5 (3)

- Xenophanes' ScepticismDokument22 SeitenXenophanes' Scepticismvince34Noch keine Bewertungen

- Past Simple (Regular/Irregular Verbs)Dokument8 SeitenPast Simple (Regular/Irregular Verbs)Pavle PopovicNoch keine Bewertungen

- Retaining Talent: Replacing Misconceptions With Evidence-Based StrategiesDokument18 SeitenRetaining Talent: Replacing Misconceptions With Evidence-Based StrategiesShams Ul HayatNoch keine Bewertungen

- The "Write" Way: A Judicial Clerk's Guide To Writing For The CourtDokument92 SeitenThe "Write" Way: A Judicial Clerk's Guide To Writing For The Courtunknown07blackstarNoch keine Bewertungen

- Unit 9:: What Did You See at The Zoo?Dokument11 SeitenUnit 9:: What Did You See at The Zoo?ARiFin MoHaMedNoch keine Bewertungen

- Brenda Alderman v. The Philadelphia Housing Authority, 496 F.2d 164, 3rd Cir. (1974)Dokument16 SeitenBrenda Alderman v. The Philadelphia Housing Authority, 496 F.2d 164, 3rd Cir. (1974)Scribd Government DocsNoch keine Bewertungen

- Principles of Natural Justice Justice Brijesh Kumar: Judge, Allahabad High CourtDokument7 SeitenPrinciples of Natural Justice Justice Brijesh Kumar: Judge, Allahabad High CourtTarake DharmawardeneNoch keine Bewertungen

- Case KohortDokument37 SeitenCase KohortNasir AhmadNoch keine Bewertungen

- Convert 2.0 - Frank Kern Official Full Download + FREEDokument127 SeitenConvert 2.0 - Frank Kern Official Full Download + FREETwo Comma Club100% (1)

- GALVEZ Vs CADokument2 SeitenGALVEZ Vs CARyannCabañeroNoch keine Bewertungen

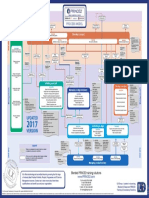

- p2 Process Model 2017Dokument1 Seitep2 Process Model 2017Miguel Fernandes0% (1)

- John 20 Study GuideDokument11 SeitenJohn 20 Study GuideCongregation Shema YisraelNoch keine Bewertungen

- HistogramDokument7 SeitenHistogramTesfaye MinaleNoch keine Bewertungen

- 3rd Sunday After TrinityDokument11 Seiten3rd Sunday After TrinityHmkEnochNoch keine Bewertungen

- 4th Quarter Grade 9 ExamDokument4 Seiten4th Quarter Grade 9 ExamAnnie Estaris BoloNoch keine Bewertungen

- Literature Review SampleDokument13 SeitenLiterature Review SampleKrishna Prasad Adhikari (BFound) [CE Cohort2019 RTC]Noch keine Bewertungen

- Credit Transactions Case Digestpdf PDFDokument241 SeitenCredit Transactions Case Digestpdf PDFLexa L. DotyalNoch keine Bewertungen

- March 2009 Caro-Kann B12 by Sasa Velickovic Informant83Dokument6 SeitenMarch 2009 Caro-Kann B12 by Sasa Velickovic Informant83kiprijanovNoch keine Bewertungen

- Curriculum Vitae: Lungnila Elizabeth School of Social Work, Senapati, Manipur August 2016-June 2018Dokument4 SeitenCurriculum Vitae: Lungnila Elizabeth School of Social Work, Senapati, Manipur August 2016-June 2018Deuel khualNoch keine Bewertungen

- Srs For College WebsiteDokument6 SeitenSrs For College WebsiteShree Kumar33% (3)

- Kalki ProjectDokument3 SeitenKalki ProjectMandar SohoniNoch keine Bewertungen

- Agvan DorzhievDokument7 SeitenAgvan DorzhievMichael FelicianoNoch keine Bewertungen

- Rights As Bribes ResaltadoDokument89 SeitenRights As Bribes ResaltadoAndresAmarillaNoch keine Bewertungen

- A Vagabond SongDokument4 SeitenA Vagabond SongLiLiana DewiNoch keine Bewertungen

- Leadership PaperDokument6 SeitenLeadership PaperSTANCIU VALENTINNoch keine Bewertungen

- Prejudicial QuestionDokument1 SeitePrejudicial QuestionlmafNoch keine Bewertungen

- Longman Communication 3000Dokument37 SeitenLongman Communication 3000irfanece100% (5)

- Cosmology NotesDokument22 SeitenCosmology NotesSaint Benedict Center100% (1)

- Maria Da Piedade Ferreira - Embodied Emotions - Observations and Experiments in Architecture and Corporeality - Chapter 11Dokument21 SeitenMaria Da Piedade Ferreira - Embodied Emotions - Observations and Experiments in Architecture and Corporeality - Chapter 11Maria Da Piedade FerreiraNoch keine Bewertungen

- Chapter 1Dokument13 SeitenChapter 1Jerard AnciroNoch keine Bewertungen