Beruflich Dokumente

Kultur Dokumente

Buses

Hochgeladen von

parquedigitalsacCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Buses

Hochgeladen von

parquedigitalsacCopyright:

Verfügbare Formate

EC

Ignacio Rojas

BUSES

5.1

1. Evolucin y prestaciones de los computadores 2. Unidades funcionales de un computador. 3. Nivel de lenguaje mquina. 4. Desarrollo de programas en ensamblador.

5. Buses del sistema. Bus PCI.

6. Sistema de memoria interna. 7. Sistema de memoria externa. 8. Sistema de entrada/salida.

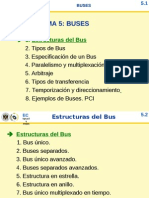

TEMA 5: BUSES

� 1. Estructuras del Bus 2. Tipos de Bus 3. Especificacin de un Bus 4. Paralelismo y multiplexacin 5. Arbitraje 6. Tipos de transferencia 7. Temporizacin y direccionamiento 8. Ejemplos de Buses. PCI

EC

Ignacio Rojas

Estructuras del Bus

5.2

� Estructuras del Bus 1. Bus nico. 2. Buses separados. 3. Bus nico avanzado. 4. Buses separados avanzados. 5. Estructura en estrella. 6. Estructura en anillo. 7. Bus nico multiplexado en tiempo.

EC

Ignacio Rojas

Bus nico

5.3

Bus nico:

Memoria para programas/datos

- La Cpu necesita.

E/S para almacenamiento/comunicacin con usuario

- Solucin: usar las mismas lneas para conectarlo todo cortocircuito.

- Cortocircuito: slo un dispositivo puede escribir en un instante dado.

EC

Ignacio Rojas

Bus nico

5.4

Inicia todas las transferencias y controla si el dispositivo lee, escribe o es triestado.

CPU

Memoria

Perifrico 0

Perifrico 1

Bus del sistema

Problema: La velocidad de transferencia de la CPU y de la memoria es muy superior a la de los perifricos. Por ello si el bus es sncrono todo ira regido por la velocidad del ms lento

EC

Ignacio Rojas

Buses separados

5.5

Buses separados:

- Uno rpido (memoria) y otro lento (E/S).

Va a la velocidad de la memoria

Memoria Bus de memoria CPU

Va a la velocidad del ms lento

Perifrico 0

Perifrico 1

Bus de E/S

EC

Ignacio Rojas

Buses separados

5.6

- Mejoras: Asincronismo Bus E/S (requiere una lnea de control adicional Ready)

T1 CLK RDY Ready

T2

T3

TW

T4

Periodo de espera TW entre T3 y T4 1. La CPU intenta transferir en T3. El perifrico no est listo, RDY 2. La CPU inserta estados TW (wait). Perifrico preparado ya, RDY 3. La CPU no inserta ms TW. Pasa a T4.Se transfiere el dato.

EC

Ignacio Rojas

Bus nico avanzado

5.7

Bus nico avanzado:

-Objetivo: que la CPU pueda seguir trabajando con memoria mientras que los perifricos terminan su operacin.

CPU

Cache Memoria principal

Per. 00

Per. 01

..

Per. 0n

Per. 10

Per. 11

..

Per. 1n

Controlador de E/S

Controlador de E/S

Bus del sistema

EC

Ignacio Rojas

Bus nico avanzado

5.8

Controlador E/S:

- CPU programa el controlador indicando tipo de operacin (R/W) perifrico (0..n) tamao del bloque dado

- CPU sigue trabajando con memoria. - El controlador interrumpe a la CPU si perifrico no est preparado pide (W) el primer dato proporciona (R) el primer dato

- CPU lee/escribe el dato. - CPU sigue trabajando hasta la prxima interrupcin.

EC

Ignacio Rojas

Bus nico avanzado

5.9

Buffers:

- El controlador puede disponer de un pequeo bloque de memoria propia (1KB). - La CPU puede escribir/leer datos de E/S de 1KB en 1KB por lo que se interrumpe menos frecuentemente (1024 veces menos). Es ms rpida transfiriendo 1Kb que 1024 veces 1B. - Los perifricos pueden tener buffer propio; esto ocasiona que el controlador quede libre para manejar otro perifrico mientras tanto. - La CPU tambin puede tener Buffer propio (Cach).

EC

Ignacio Rojas

Bus nico avanzado

5.10

Interrupciones:

- Son un mecanismo ( hardware, lnea INTR) por el cual la CPU:

Memoriza el estado actual o CONTEXTO: contador de programa, flags de estado, otros registros... Ejecuta la Rutina de Servicio de Interrupcin ISR la cual debe:

IRQ vectorizadas: el Controlador pone un vector en el bus que identifica el perifrico y el ISR 1.- Identificar el dispositivo: consulta (polling) ISR comprueba estado de los perifricos hasta localizar el causante de la IRQ 2.- Atenderlo (R/W). 3.- Atender el Controlador, (re)(des)programar?

Retorna al contexto anterior IRET

EC

Ignacio Rojas

Buses separados avanzados

MEM. ..

Per. 1n

5.11

Buses Separados:

Objetivo: liberar a la CPU de trfico E/S

Per. 00 Per. 01

..

Per. 0n

Per. 10

Per. 11

Controlador E/S

Controlador E/S

CPU

Bus de E/S DMA Memoria principal

Cache

Bus de sistema

Controlador Cache

Controlador DMA

EC

Ignacio Rojas

Buses separados avanzados

5.12

Controlador DMA (Direct Memory Access):

Tipo de operacin R/W

1.- CPU programa al controlador indicndole:

Tamao de bloque de memoria Direccin inicial de memoria

2.- El Controlador DMA aprovecha cuando el Bus de Sistema queda libre:

Lee de memoria y escribe el dato en E/S o escribe en memoria el dato ledo en el BUS E/S. Incrementa la direccin y as sucesivamente.

3.- El Controlador E/S debe haber sido programado para actuar conjuntamente.

EC

Ignacio Rojas

Buses separados avanzados

5.13

Controlador Cache:

- Principio de localidad de las referencias de memoria: Temporal: tendencia de la CPU a referenciar dentro de poco datos recientemente referenciados. Espacial: tendencia de la CPU a referenciar datos cercanos (direccin) al ltimo referenciado. Secuencial: tendencia de la CPU a referenciar el siguiente dato (direccin+1) al ltimo referenciado. - Controlador intenta que la CPU encuentre en Cach lo que necesita. - Transfiere Memoria Cach en pequeos bloques. - CPU / Cache=E/S / Buffer - La Cache es ms rpida, cara y pequea que la memoria normal.

EC

Ignacio Rojas

Buses separados avanzados

5.14

Otras necesidades de velocidad:

- Deseo de reducir el tiempo de ejecucin y el coste de los procesadores. Se toman estas medidas:

Varios procesadores iguales: repartir tiempo, tolerancia de fallos... Coprocesadores especficos: grficos, matemticos... Controladores Cache, DMA, E/S... Todo esto trabajando simultneamente en paralelo.

- Es viable slo si:

- Cada uno puede trabajar bastante tiempo aisladamente. - Acceden ocasionalmente al bus para transferir rfagas de datos.

Estructura en estrella

Dos estructuras tpicas

Estructura en anillo

EC

Ignacio Rojas

Estructura en estrella

5.15

Estructura en estrella:

Interconexin Procesadores-Memoria compartida Modulo central:

Gestor de comunicaciones Sistema de conmutadores: -Barras cruzadas -Barril -etc... Una avera en G inutiliza el sistema N de procesadores limitado por la capacidad de G

M G

EC

Ignacio Rojas

Estructura en anillo

5.16

Estructura en anillo:

Interconexin de los procesadores mediante Paso de Testigo

Cada procesador:

- Espera testigo - Lee mensajes de otros procesadores - Retira los que no le correspondan - Aade los que desee transmitir - Escribe mensajes al siguiente procesador

Ventajas: +Barato (2 hilos, coaxial, altas velocidades) +Sencillo, ampliable (insertar otro procesador en cadena) Desventajas: La avera de un procesador inutiliza el sistema.

EC

Ignacio Rojas

BUSES

5.17

1. Evolucin y prestaciones de los computadores 2. Unidades funcionales de un computador. 3. Nivel de lenguaje mquina. 4. Desarrollo de programas en ensamblador.

5. Buses del sistema. Bus PCI.

6. Sistema de memoria interna. 7. Sistema de memoria externa. 8. Sistema de entrada/salida.

TEMA 5: BUSES

1. Estructuras del Bus � 2. Tipos de Bus 2.1 Segn dedicacin (dedicados/no dedic.) 2.2. Segn particionamiento 2.3. Segn nivel de jerarqua

EC

Ignacio Rojas

Buses segn dedicacin

5.18

Buses dedicados Pueden establecer ms comunicaciones simultneamente. Pueden realizar ms funciones en paralelo (E/S, Datos, ...) Pero el coste es mucho mayor (n contactos y cables ) Slo interesa si hay muchos elementos (CPU, Mem) muy rpidos y muy caros (ms que el bus).

Bus de Instrucciones Bus de datos Bus de E/S

CPU

Instruccin en memoria

Datos en memoria

Sistema E/S

Estructura tpica de un bus dedicado

EC

Ignacio Rojas

Buses segn dedicacin

5.19

Buses no dedicados Son ms baratos y ms lentos:

Slo hay 1 comunicacin simultneamente.

Requieren mecanismo de arbitraje:

Conceder el bus a quien lo necesite pero no a ms de 1.

Si hay muchos elementos, bus = cuello de botella.

Bus

Memoria

CPU

Sistema E/S

Estructura tpica de un bus no dedicado

EC

Ignacio Rojas

Buses segn particionamiento

5.20

Particionamiento:

POR RECURSOS POR FUNCIN

Por recursos: (Ej. VME): Recursos del mismo tipo se agrupan en tarjetas. Particionamiento por funcin

1. 2. Cada tarjeta es un sistema (casi) independiente. Slo requieren ocasionalmente pasarse datos o sincronizarse.

Ej. Multibus II y Futurebus.

EC

Ignacio Rojas

Buses segn Particionamiento

Bus del sistema

5.21

Memoria

Memoria

CPU

E/S

E/S

Bus particionado por recursos

Bus del sistema

Interfaz

Bus local

Interfaz

Bus local

CPU

Memoria

Funcin 1

E/S

CPU

Memoria

Funcin N

E/S

Bus particionado por funcin

EC

Ignacio Rojas

BUSES

5.22

1. Evolucin y prestaciones de los computadores 2. Unidades funcionales de un computador. 3. Nivel de lenguaje mquina. 4. Desarrollo de programas en ensamblador.

5. Buses del sistema. Bus PCI.

6. Sistema de memoria interna. 7. Sistema de memoria externa. 8. Sistema de entrada/salida.

TEMA 5: BUSES

1. Estructuras del Bus 2. Tipos de Bus � 3. Especificacin de un Bus 4. Paralelismo y multiplexacin 5. Arbitraje 6. Tipos de transferencia 7. Temporizacin y direccionamiento 8. Ejemplos de Buses. PCI

EC

Ignacio Rojas

Especificacin de un Bus

5.23

Debe incluir toda la informacin necesaria para saber conectar un dispositivo al bus. Hay varios niveles: Mecnico: Define el soporte (rack, PCB), n lneas, tipo conector,

dimensiones tarjetas,...

Elctrico: Tipo transceivers (tensin/corriente), alimentacin,

impedancias, nivel seal,...

Lgico: Define n seales y su significado, activas alta/baja, ... Temporizacin: Tipos de ciclo (R/W, IO/M, Tw) y sus

cronogramas.

Transferencia simple: Define protocolos arbitraje, transmisin,

ciclo partido, deteccin errores.

Transferencia doble: Posibilidad transferencia bloque,

mecanismos de reintento/recuperacin bloque.

EC

Ignacio Rojas

Especificacin de un Bus

5.24

Nivel Mecnico:

Backplane Bus

Placa STD

A veces el estndar de fbrica (Ej. RS-232-C) no especifica conector (DB-25 o DB-9)

EC

Ignacio Rojas

Especificacin de un Bus

Circuito equivalente RS-232-C

5.25

Nivel Elctrico:

Estrechamente relacionado con nivel mecnico. Ambos niveles influyen en: Distancia maxima conexin / n tarjetas. Inmunidad al ruido Velocidad Mxima de transferencia. Paralelismo / Multiplexacin Transceiver IEEE 802.5 Coste ( cables, conectores, ...)

EC

Ignacio Rojas

BUSES

5.26

1. Evolucin y prestaciones de los computadores 2. Unidades funcionales de un computador. 3. Nivel de lenguaje mquina. 4. Desarrollo de programas en ensamblador.

5. Buses del sistema. Bus PCI.

6. Sistema de memoria interna. 7. Sistema de memoria externa. 8. Sistema de entrada/salida.

TEMA 5: BUSES

1. Estructuras del Bus 2. Tipos de Bus 3. Especificacin de un Bus � 4. Paralelismo y multiplexacin 5. Arbitraje 6. Tipos de transferencia 7. Temporizacin y direccionamiento 8. Ejemplos de Buses. PCI

EC

Ignacio Rojas

Paralelismo y multiplexacin

5.27

Idealmente, todos los dispositivos debieran tener el mismo ancho palabra del bus. Paralelismo total: Bus datos y Bus direcciones separados. Aumenta la velocidad de transferencia. Aumenta el coste. Sin embargo interesa disminuir el n de pines en dispositivos, complejidad conectores, tamao tarjetas, n hilos, coste, etc.

EC

Ignacio Rojas

Paralelismo y multiplexacin

5.28

Multiplexacin Datos/Direcciones:

El bus lleva datos/dir separados. Dispositivos cargan dir en latch

Demultiplexacin

No es tan grave la prdida de velocidad, ya que en una lectura cpu-mem la cpu debe esperar tiempo de acceso.

EC

Ignacio Rojas

Paralelismo y multiplexacin

5.29

Multiplexacin MSB / LSB:

Bus lleva ancho palabra completo. Dispositivos acceden LSB primero. En siguiente ciclo, MSB.

Multiplexacin

EC

Ignacio Rojas

Paralelismo y multiplexacin

5.30

Bus Serie:

Caso extremo de multiplexacin. Paralelismo Nulo. Toda la informacin (Datos, Dir, Control) va por 2 hilos. Muy apropiado para grandes distancias (bajo coste).

Elementos necesarios para bus serie.

EC

Ignacio Rojas

BUSES

5.31

1. Evolucin y prestaciones de los computadores 2. Unidades funcionales de un computador. 3. Nivel de lenguaje mquina. 4. Desarrollo de programas en ensamblador.

5. Buses del sistema. Bus PCI.

6. Sistema de memoria interna. 7. Sistema de memoria externa. 8. Sistema de entrada/salida.

TEMA 5: BUSES

1. Estructuras del Bus 2. Tipos de Bus 3. Especificacin de un Bus 4. Paralelismo y multiplexacin � 5. Arbitraje 6. Tipos de transferencia 7. Temporizacin y direccionamiento 8. Ejemplos de Buses. PCI

EC

Ignacio Rojas

Arbitraje y Temporizacin

5.32

Tipos de dispositivo (o Tarjetas):

Activos: Eventualmente pueden requerir el uso del bus para iniciar un transferencia. Pasivos: Slo pueden responder a una transferencia, nunca iniciarla. Master: En cada instante el bus est siendo usado por l. Slave: Dispositivo(s) que responde(n) al master. Pasivo Activo Esclavo siempre Master ocasionalmente

Situacin de Contencin del bus.

Con Bus nico

Activos deben acordar quin usa el bus, si no cortocircuito.

EC

Ignacio Rojas

Arbitraje y temporizacin

5.33

Tipos de bus nico:

Maestro nico: (CPU) Controla bus siempre. No hay contencin. Por robo de ciclo: (DMA) Hay un elemento activo que usualmente es maestro (CPU). Hay otro activo (DMA) que ocasionalmente pide el bus por muy poco tiempo (HOLD-HLDA). No hay arbitraje: CPU siempre cede el bus y lo recupera pronto. Arbitraje: Varios elementos activos (Ej. Multiproceso simtrico). Requiere protocolo justo (no dejar a ninguno esperando eternamente).

EC

Ignacio Rojas

Arbitraje y temporizacin

Activos: CPU, DMA Pasivos: Mem, E/S (E/S solo puede interrumpir) Master: Usualmente CPU Slave: Usualmente MEM

5.34

Ej. Bus nico, robo ciclo DMA, CPU, Mem, E/S.

CPU Contr. DMA

MEM

Master: DMA Slave: MEM E/S

Contr. E/S

Fuente: E/S Destino: MEM

Controlador E/S dispone de 1 buffer de datos para CPU; interrumpe CPU Controlador DMA roba bus (HOLD) y transfiere buffer E/S a MEM.

CPU recupera bus y lee de memoria.

Master: CPU Slave: MEM Fuente: MEM Destino: CPU

EC

Ignacio Rojas

Arbitraje y temporizacin

5.35

En el caso ms general (arbitraje) la secuencia de operaciones se llama transaccin.

Peticin bus Arbitraje Direccionamiento Transferencia Datos Deteccin Errores.

Transaccin del Bus

EC

Ignacio Rojas

Arbitraje y temporizacin

5.36

Deteccin de Errores: Error: Se transmiten datos incorrectos o se pierden datos. Tipos Comunes (deben detectarse para poder reintentar la transferencia) Direccionamiento: Intentar acceder a direcciones inexistentes (memoria o dispositivos) o direcciones protegidas (ej. Cdigo del SO).

Soluciones: Si bus asncrono (seal RDY) dispositivo inexistente no responde. Modulo temporizador: Espera Time-Out y fuerza repeticin ciclo. Si memoria local a 1 CPU, cpu suele detectar/ proteger.

EC

Ignacio Rojas

Arbitraje y temporizacin

5.37

Datos: Crosstalk, ruido, fluctuacin alimentacin

Soluciones: Cdigos detectores (Paridad), correctores (Hamming), CRC, Checksum. Al detectar, reintentar transferencia.

Arbitraje: Se concede el bus a varios dispositivos (corrupcin) o a ninguno (deadlock).

Soluciones: Bus datos/dir cortocircuitable (se detectar error paridad). Mdulo temporizador: Deadlock Time-Out Reintentar.

EC

Ignacio Rojas

Polticas de Arbitrio

5.38

Polticas de Arbitrio Esttica

DE PETICIN FIFO PRIORIDAD FIJA EQUIDAD COMBINADA ROR RWD PREEMPTION

Dinmicas

DE LIBERACIN

EC

Ignacio Rojas

Polticas de Arbitrio

5.39

Esttica: Repetir turnos (transaction slots) entre masters de una manera prefijada.

Ej. 4 tarjetas activas, potenciales maestros.

M1 t T1 M2 T2 T3 M3 T4 M4 T5 T6

El reparto se denomina Frame (marco) Tpico en sistemas sncronos (duracin T fija). Esquema simple, sencillo de implementar. Desperdicia slots (ancho de banda del bus)

T7

T8 T9 T10 T11 T12

EC

Ignacio Rojas

Polticas de Arbitrio

5.40

DINMICAS: Permiten cambiar MASTER segn la situacin actual. Requieren HARDWARE. PETICIN: Cmo decidir, de entre tarjetas activas que solicitan el bus, el prximo MASTER.

FIFO: First-in, First Out. Bus se concede a quien lleva ms tiempo pidindolo. PRIORIDAD: Cada tarjeta tiene una prioridad. La peticin de mayor prioridad gana. EQUIDAD: Garantizar que no se concede al mismo 2 veces habiendo otra peticin pendiente. Ej. Round-Robin Ir concediendo en ronda (entre los que lo soliciten). Evita STARVATION: si mxima prioridad solicita mucho, restantes prioridades mueren de hambre. COMBINADA: Tpico en sistemas (multiprocesador | E/S) y multiproceso asimtrico. Usar Poltica Prioridad para tareas ocasionales y de duracin corta. Equidad para tareas normales. Ej. E/S se atienden inmediatamente (si hay varias, en orden de prioridad). Procesadores atienden cclicamente mientras no haya E/S.

EC

Ignacio Rojas

Polticas de Arbitrio

5.41

DINMICAS: LIBERACIN: Cmo decidir cuando deja libre el bus el Master actual.

ROR: Release on Request (liberar cuando haya otra peticin). Tpico en sistemas monoprocesador. CPU posee el bus casi siempre Slo cede si DMA, robo ciclo, etc. Ahorra tiempo arbitraje: CPU accede frecuentemente sin tener que competir. RWD: Release When Done (liberar al acabar). Tpico multiprocesador. Master slo usa bus durante 1 transaccin, si quiere ms, debe competir. PREEMPTION: Una transferencia en curso puede ser interrumpida (Master libera bus) por una peticin de mayor prioridad.

EC

Ignacio Rojas

Hardware de Arbitrio

5.42

GESTIN CENTRALIZADA DAISY CHAIN HBRIDA (COMBINADA) GESTIN DISTRIBUIDA

Cada poltica de arbitrio puede realizarse (en hardware) de diversas maneras: - Mdulo rbitro: Programable para implementar diversas polticas. - Lgica Distribuida: Cada tarjeta activa contiene circuitera de arbitrio.

EXTREMOS:

EC

Ignacio Rojas

Hardware de Arbitrio: Gestin Centralizada

5.43

Cada tarjeta Activa dispone de lneas de arbitrio: Bri (PETi): Peticin del Bus al rbitro. BGi (CONi): rbitro concede Bus a Tarjeta i Tarjeta Arbitro programable para cualquier poltica. Ej: N=16, 8 tarjetas E/S, 8 tarjetas procesador Tratar N=1..8 E/S por prioridad decreciente. N=9..16 Procesadores, prior. Round-Robin

GESTIN GESTIN CENTRALIZADA CENTRALIZADA DAISY DAISY CHAIN CHAIN HBRIDA HBRIDA (COMBINADA) (COMBINADA) GESTIN GESTIN DISTRIBUIDA DISTRIBUIDA

Gestin de Prioridades Centralizada

EC

Ignacio Rojas

Hardware de Arbitrio: Gestin Centralizada

5.44

Demandas Independientes con rbitro central

�Esquema flexible � Velocidad arbitraje �Coste: rbitro, lneas BR/BG �Expansibilidad: mx N activas.

EC

Ignacio Rojas

Hardware de Arbitrio: Gestin Centralizada

5.45

Opcionalmente: 3 lnea comn open-colector BB (Bus Busy, Ocupado). Ej. BR1,BR3 2 peticiones. Supongamos rbitro decide BG1 Master1 lee BG1 e indica BB a todos (rbitro y dems activas); puede desactivar Br1 una vez ocupado BB rbitro Espera BB y entonces decide entre Bri pendientes Retira BG1

Tolerancia a Fallos: En multiproceso simtrico, al fallar una tarjeta CPU el Sistema Operativo: Puede reprogramar rbitro para ignorar CPU y repartir carga CPU entre el resto.

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

BG IN BG OUT

5.46

GESTIN CENTRALIZADA

DAISY CHAIN

HBRIDA (COMBINADA) GESTIN DISTRIBUIDA

Algunos autores consideran Daisy-Chain una variante de Centralizada (hay rbitro). BR compartida y BG daisy-chain.

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

5.47

rbitro slo 3 lneas:

Lee BR compartida entre activas (open-colector). Lee BB compartida tarjetas activas Cede BG si hay alguna BR y no est bus BB

Cada tarjeta Activa 4 lneas: Escribe BR Lee BG IN si quiere pedir bus cadena Bus Grant puede quedarse BG y negarlo al siguiente mientras ocupe bus

Escribe BG OUT Lee y escribe BB

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

Prioridad fija por posicin

5.48

Puede retirar 1 BR inmediatamente

Varias tarjetas 2 (M2, M5) activan BR.

Se comienza con M1 que no pide el bus,

M2 pidi BR Escribe BB M2 termina

lee BG IN concedido

escribe BGOUT denegado (M5 no recibir BG) libera bus BB

Como bus libre, (BB ), rbitro cede BG Problema:

rbitro recupera bus BG y lee peticin BR, volver a empezar.

Suponer que mientras M2 ocupa BB , M1 quiere pedir BR.

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

5.49

Tambin se puede considerar Daisy-Chain una variante Distribuida: Cada tarjeta tiene circuitera propia La tarea del rbitro es casi trivial (no programable)

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

5.50

PETI = BR Peticin Bus. Open-colector. CONC = BG Concesin Bus. Daisy-chain BIPET = Biestables para latchear peticiones. E = Enable. Fuerza BIPETi = PETPERi BICON = Biestables para latchear concesin = Activados en flanco subida

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

5.51

CONC =1 mientras nadie pide el bus. E permite BIPETi � PETPERi PETPER1 BIPET1 PETI1 PETI

Si un perifrico no pide el control del bus y CONC en alta, la salida de puerta b , que funciona como BG es 1

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

5.52

0 1 1 1 1 1 1

Se pondr a 1 cuando cambie CONC

Perf. 1 NO pide el control del bus

Perf. 2 pide el control del bus

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

Latch de BICONi Cadena ORa ORb= 1 BIPETi Enabled otra vez

5.53

CONC

Observar 1er pulso CONC: PETPER1 mientras propagacin daisy-chain CONC = 0 E=0 (BIPET1 PETPER1 ) Evita PRE-EMPTION Cuando CONC Se supone tiempo suficiente para propagacin. BICON2 =1, tarjeta 2 toma el bus PETPER2 Puede Retirarse PETI1 Sigue Pendiente

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

5.54

El esquema anterior Requiere sealar fin de transferencia. TEMP = BB. Bus ocupado, open-colector. Tarjeta 2 seala que acab. TEMP y libera bus (biestable BICON ) ARBITRO lee TEMP , pendiente PETPER1 concede CONC BICONi =1 BIPETi = 0 (BIPETi =1) ORa(i) = 0 (ORb(i-1) = 0 y CONC = 0) Slo toma el bus quien lo haya pedido y le llegue el daisy-chain ORb(i) = 0 ORa(i) = 0 y BIPETi =0 Slo se propaga Daisy-chain si llega hasta all y no se pidi el bus Cada OR tiene un tiempo de respuesta (orden ns). CONC = 0 tiempo suficiente para propagar a final.

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

5.55

Cronograma de concesin de servicio por encadenamiento. Perf.2 pide primero y despus Perf.1

Cuando tiene control retira peticiones Control bus

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

5.56

�Simplicidad lgica de control: poca circuitera, pocas lneas, � Expansibilidad: n maestros limitado slo por tiempo

propagacin... ilimitado.

� Inequidad: � Lentitud: � Esttico:

Prioridad fija por posicin en cadena (posible STARVATION) Ciclo arbitraje suficientemente largo como para garantizar propagacin. Cambiar prioridades implica cambiar orden FISICO de las tarjetas en daisy-chain. Ruptura puerta OR de tarjeta activa implica ruptura de la cadena (no tolerancia a fallos).

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

5.57

Conexin en Daisy-chain del sub-bus rbitro del VME

Ej. Bus VME permite puentear tarjetas daisy-chain que debieran estar contiguas, vecinas fsicamente en el rack. Cambiar prioridad Tarjeta Rota o pasiva cambiar orden. Puentear (jumper)

VME permite 4 cadenas: es sistema hbrido.

EC

Ignacio Rojas

Hardware de Arbitrio: Daisy Chain

5.58

Bus VME daisy-chain

EC

Ignacio Rojas

Hardware de Arbitrio: Gestin Hbrida

5.59

GESTIN CENTRALIZADA DAISY CHAIN

HBRIDA (COMBINADA)

GESTIN DISTRIBUIDA

Un daisy-chain a cada lnea del rbitro central. Poltica Programable entre cadenas. Prioridad fija dentro de cada cadena.

EC

Ignacio Rojas

Hardware de Arbitrio: Gestin Distribuida

5.60

GESTIN CENTRALIZADA DAISY CHAIN HBRIDA (COMBINADA)

�No hay rbitro central. �Cada tarjeta Activa su circuitera. � Tpico en sistemas multiprocesador optimizados.

GESTIN DISTRIBUIDA

Ej. Multibus II 1. Cada tarjeta tiene un Arbitration Number (AN) y una poltica de Prioridad Fija. 2. Peticin: tarjetas escriben AN al rbitro (local)

Escriben AN en bus datos/dir (open-colector) RBITROS Leen AN resultante (OR- lgico) Retiran AN si resultante > local

EC

Ignacio Rojas

Gestin Distribuida

MULTIBUS II

5.61

Tras algunas oscilaciones, gana rbitro con mayor AN. rbitro ganador espera a que acabe transferencia actual (datos, BB), se apodera del bus y notifica a tarjeta (BG, BB)

EC

Ignacio Rojas

Ejemplo: NUBUS

5.62

Arbitration priority number

Arbitraje por Prioridad ( =Multibus II )

Arbitraje Equidad-Prioridad

EC

Ignacio Rojas

NUBUS

5.63

SBRG: Shared Bus Request / Grant Bus separado de arbitraje (open colector). Para Equidad-Prioridad se aade lnea BR (compartida, OR cableado). Una tarjeta que ha sido atendida no tiene derecho a pedir bus hasta que las dems hayan sido atendidas. En ese momento, BR , empieza otra ronda).

EC

Ignacio Rojas

NUBUS

BR AP#4 gana, BB , acaba. BB AP#3 gana, BB , acaba. BB pero ya fueron atendidas

5.64

Ej. 1 ronda: solicitan bus AP# 1,2,3,4

Arbitraje:

Vuelven a solicitar bus AP#3,4 Arbitraje: AP#2, BB AP#1, BB

an hay BR pendientes, #1,2 rbitros 3,4 no activan BR

EC

Ignacio Rojas

NUBUS

5.65

Cuando AP#1 hizo BB (ocupar bus), desactiv la ltima BR pendiente. BR Los rbitros locales con AP#3,4 inician 2 ronda de arbitraje. Arbitraje para prxima transferencia: en paralelo con transferencia actual y aprovechar bus separado de arbitraje. 2 Ronda: Dos rbitros pendientes han observado BR (AP#3,4) Arbitraje: AP#4 gana. Cuando AP#1 libere BB , lo ocupar #4 AP#3 gana.

EC

Ignacio Rojas

BUSES

5.66

1. Evolucin y prestaciones de los computadores 2. Unidades funcionales de un computador. 3. Nivel de lenguaje mquina. 4. Desarrollo de programas en ensamblador.

5. Buses del sistema. Bus PCI.

6. Sistema de memoria interna. 7. Sistema de memoria externa. 8. Sistema de entrada/salida.

TEMA 5: BUSES

1. Estructuras del Bus 2. Tipos de Bus 3. Especificacin de un Bus 4. Paralelismo y multiplexacin 5. Arbitraje � 6. Tipos de transferencia 7. Temporizacin y direccionamiento 8. Ejemplos de Buses. PCI

EC

Ignacio Rojas

Tipos de transferencia

5.67

Tipos de transferencia:

Segn contenido: - Lectura. - Escritura. - DMA (THREE-PARTY) Segn procedimiento: - Conectada (Ciclo completo) (Circuit Switching) - Partida (Ciclo Partido) (Packet Switching) Segn tamao: - Vaca (DUMMY) - Palabra (Single) - Bloque (Burst)

EC

Ignacio Rojas

Tipos de transferencia: Segn contenido 5.68

1 Ciclo Direcciones 2 Ciclo Datos

Escritura: Master proporciona datos a Slave.

- Si bus multiplexado: Direcciones/Datos

- Si no, Master puede dar Dir/Dato SIMULTANEAMENTE. De todas formas SLAVE lee el dato cuando se active (Tiempo de seleccin por direccionamiento.

Lectura: Master requiere dato de Slave. Slave escribe el dato cuando se active (Tiempo de acceso) No es tan grave multiplexar el Bus Modificacin: Master lee, INMEDIATAMENTE escribe. INDIVISIBLE. Ej: operacin TEST&SET para semforos. Comprobacin: Master escribe. INMEDIATAMENTE lee. INDIVISIBLE. til para chequeo.

EC

Ignacio Rojas

Tipos de transferencia: Segn contenido 5.69

Three-Party (DMA):

- Transferencia a tres partes. Tpico para DMA. - El MASTER (DMA) no es fuente ni destino (Disp1 Disp2) - Hay 2 SLAVES. - Tpico en sistemas monoprocesador donde los SLAVES no soportan transferencias en bloque y/o son demasiado lentos.

DISP. 1

DISP. 2

DMA

EC

Ignacio Rojas

Tipos de transferencia: Segn procedimiento

5.70

Conmutacin de circuitos:

Se establece la conexin (circuito) y se trasmiten los datos. Es el tipo de comunicacin usado en las transferencias:

Normales Conectadas De ciclo completo

Conmutacin de Paquetes:

La transferencia se divide en varios Trozos (Paquetes). Cada trozo se transmite independientemente. Puede seguir un camino (enrutamiento) distinto. Puede llegar en distinto orden secuencial.

EC

Ignacio Rojas

Tipos de transferencia: Segn procedimiento

5.71

Ejemplo: ETHERNET

Dispone de dos protocolos a nivel de red:

TCP: Trasmission Control Protocol: Implementa CircuitSwitching.

- Se establece un circuito ( tal vez a travs de varios gatewaysrouters). - Todos los mensajes siguen el mismo camino, llegan en el mismo orden. Ej: rlogin, telnet.

UDP: User Datagram Protocol: Implementa PacketSwitching.

- Los datos se trocean en Datagramas. - Para cada Datagrama se establece una conexin y se enva. - En el destino se reordenean en orden secuencial. Ej: ftp

EC

Ignacio Rojas

Tipos de transferencia: Segn procedimiento

5.72

Es la filosofa implcita en las transferencias CICLO PARTIDO.

Ranura Ranura Ranura 1 2 3 Ranura Ranura Ranura 5 6 4 Ranura Ranura 7 8

....

Ranuras del bus de ciclo compartido En vez de dividir el mensaje en datagramas dividimos la TRANSFERENCIA: Direccin Dato

Tiempo

Ejemplo: Lectura en ciclo partido: - MASTER direcciona a SLAVE - MASTER libera bus !!! (ciclo PARTIDO) otros MASTER pueden usar bus. - SLAVE es muy lento. Pasa tiempo acceso. - SLAVE direcciona maestro!!! - SLAVE escribe datos. - SLAVE reconoce fin de ciclo (MAK)

EC

Ignacio Rojas

Tipos de transferencia: Segn procedimiento

5.73

Lectura en memoria mediante bus de ciclo compartido

EC

Ignacio Rojas

Tipos de transferencia

5.74

Ciclo partido:

La secuencia peticin / transferencia realizada est partida. El bus est libre durante el tiempo invertido. LECTURA:

El dispositivo (lento) hace latch de la direccin. Responde al cabo del tiempo de acceso. Debe direccionar al maestro (maestro debe leer dato).

ESCRITURA:

El dispositivo hace latch de dir/dato. No tiene mucho sentido en bus sncrono (no hay confirmacin). S tendra sentido COMPROBACION sncrona partida (write-read).

Asncronismo: Temporizacin para conectar dispositivos lentos a buses rpidos

EC

Ignacio Rojas

Tipos de transferencia: Segn procedimiento

5.75

El concepto de ciclo partido (tipo de transferencia) es independiente del sincronismo (modo de temporizacin).

ranura Peticin lectura ranura ranura ranura ranura ranura ranura Contest. con el dato ranura ranura

Lectura sncrona en bus de ciclo partido

Tiempo

ranura Peticin escritur.

ranura

ranura

ranura

ranura

ranura

ranura

ranura

ranura

Escritura sncrona en bus de ciclo partido

Tiempo

EC

Ignacio Rojas

Tipos de transferencia: Segn procedimiento

5.76

ranura Peticin lectura

ranura Contest. Direc. Correct.

ranura

ranura

ranura

ranura

ranura Contest. con el dato

ranura

ranura

Lectura asncrona en bus de ciclo partido

ranura Peticin Escritur. ranura ranura ranura ranura ranura ranura Confirm. Escritur.

Tiempo

ranura ranura

Lectura semisncrona en bus de ciclo partido

Tiempo

EC

Ignacio Rojas

BUSES

5.77

1. Evolucin y prestaciones de los computadores 2. Unidades funcionales de un computador. 3. Nivel de lenguaje mquina. 4. Desarrollo de programas en ensamblador.

5. Buses del sistema. Bus PCI.

6. Sistema de memoria interna. 7. Sistema de memoria externa. 8. Sistema de entrada/salida.

TEMA 5: BUSES

1. Estructuras del Bus 2. Tipos de Bus 3. Especificacin de un Bus 4. Paralelismo y multiplexacin 5. Arbitraje 6. Tipos de transferencia � 7. Temporizacin y direccionamiento 8. Ejemplos de Buses. PCI

EC

Ignacio Rojas

Temporizacin

5.78

TEMPORIZACION: SINCRONA:

Tpico en buses locales (TIPO 1) o monoprocesador (1 MASTER) Master proporciona dir (T1) y datos (T2) si espera escritura lee datos (T3) si operacin lectura asume que datos ledos si operacin escritura No hay mecanismo por el cual CPU pueda recibir reconocimiento. CPU asume que todos los dispositivos funcionan correctamente y a la misma velocidad que la CPU.

EC

Ignacio Rojas

Temporizacin

5.79

- Todas las trasferencias suceden en un ciclo/flanco predeterminado de reloj. - Hay una seal CLK comn a todos los dispositivos. - Ventajas: Circuitera de control mnima menor coste.

- Desventajas: El Bus debe ir a la velocidad del dispositivo ms lento (o el dispositivo no reaccionar a tiempo)

CPU no tiene forma de garantizar que transferencia OK

EC

Ignacio Rojas

Temporizacin

Cronogramas de las trasferencias Sncronas: Escritura D0-Dn-1

5.80

Datos estables

CPU WR

t1

t2

t3

PERIF

CARGA

EC

Ignacio Rojas

Temporizacin

Cronogramas de las trasferencias Sncronas: Lectura

5.81

RD CPU CARGA PERIF D0-Dn-1

Datos estables

EC

Ignacio Rojas

Temporizacin

5.82

TEMPORIZACION:

SEMISINCRONA:

- Aadir lnea de control adicional RDY ( Wait) - MASTER inserta ESTADOS DE ESPERA hasta que Slave reacciona. - Ventajas: Circuitera sencilla Inmunidad a ruido Relativa en comparacin con asncrona

- Desventajas: Tiempo de uso del Bus incrementado en mltiplos ciclos bus.

EC

Ignacio Rojas

Temporizacin

Lectura a memoria con espera T1 T2 Tw T3

5.83

Reloj B. Dir B. Dat. IO/M R/W TEMP WAIT

EC

Ignacio Rojas

Temporizacin

5.84

TEMPORIZACION: ASINCRONA:

- No existe reloj comn CLK. - Conversacin Master/Slave mediante HANDSHAKE. - Handshake: Estrechar la mano (ofrece 1, ofrece 2, agitar, retira 1, retira 2). - Ventajas: Permite conexin de perifricos de cualquier velocidad. - Desventajas: Circuitera ms compleja, por lo que se incrementa el coste.

EC

Ignacio Rojas

Temporizacin

5.85

Bus sncrono mediante reloj

EC

Ignacio Rojas

Temporizacin

5.86

Bus asncrono mediante interbloqueo a 4 flancos

EC

Ignacio Rojas

Temporizacin

5.87

INTERBLOQUEO A 4 FLANCOS:

EJ: WRITE

- MASTER pone datos en Bus seala a slave (1) - SLAVE lee datos seala a master (2)

- MASTER libera bus (3) - SLAVE libera bus (4)

EC

Ignacio Rojas

Direccionamiento

5.88

Direccionamiento

Una vez en posesin del bus, MASTER debe Establecer comunicacin con SLAVE Seleccionarlo Ponerlo en funcionamiento (CS) Direccionarlo Despus, transferencia de datos. Cada tarjeta tiene Una Direccin Base (nica, que la distingue del resto de tarjetas) Un Rango de Direcciones por el que se reparten sus elementos direccionables, memoria, registros control/estado, registros E/S...

EC

Ignacio Rojas

Direccionamiento

SEGN MTODO DE SELECCIN:

5.89

Direccionamiento Lgico

EC

Ignacio Rojas

Direccionamiento

5.90

Direccionamiento Lgico:

Las tarjetas tienen Conmutadores (manuales) Comparadores (switch/address MsBits)

El operador

Disea el Mapa de Direcciones (qu tarjeta va en qu direccin Base) Configura los conmutadores

Ej: Bus direcciones 24 bits, todas las tarjetas 4 conmutadores. Hasta 16 tarjetas. Rango: 220 = 1 Mbyte / tarjeta Direcciones Base: 000000, 100000, 200000 ...

... E00000, F00000

No todas las tarjetas tienen que tener el mismo n de switches.

EC

Ignacio Rojas

Direccionamiento

5.91

Direccionamiento Geogrfico: (Fastbus, MultibusII, Nubus)

El rack (bastidor) tiene conectores-ranura para tarjetas (slots). Los slots llevan Cableado un nmero, en orden secuencial (slot number). El nmero de ranura (posicin de tarjeta en el rack) determina Base y Rango Direccionamiento. Usualmente, buses con direccionamiento geogrfico, pueden conmutar a direcc. Lgico mediante una lnea de control (GEO/LOG). D. Geogrfico se usa durante inicializacin sistema, S.O. Chequea tosas las tarjetas/excluye las que fallen. Las tarjetas tienen un registro Base (equivalente a switches dir. Lgico) Programable. S.O. Reparte Mapa de Direcciones entre tarjetas que superan chequeo y conmuta a direccionamiento lgico. S.O. Puede volver a dir. Geogrfico y reconfigurar sistema de nuevo.

EC

Ignacio Rojas

Direccionamiento

5.92

SEGN NMERO DE SLAVES:

Direccionamiento Normal: Slo 1 slave responde al master. Direccionamiento Extendido: (Broad) Varios slaves (incluso todas las tarjetas). BROADCAST : Escritura simultnea a varias tarjetas (memoria, mensajes a CPUs) BROADCALL : Lectura simultnea de varias tarjetas. Usualmente restringido a OR-cableado. Ej. Arbitraje: AP# podan escribirse simultneamente IRQs A cada interrupcin puede asignarse una posicin. Broadcall implicando a 32 tarjetas

EC

Ignacio Rojas

Direccionamiento

5.93

Implementacin. Direccin Reservada: 000...0h FFF...Fh

Leer dir. Res. Provoca broadcall Escribir dir. Res. Provoca broadcast

Broadcast/call Universal, se dirige a Todas las tarjetas. Comando rusers UNIX hace broadcall Ej. Ethernet: Otros ordenadores van respondiendo Acabar comando con ^C Utilidad: Coherencia Cache:

Sistema multiprocesador, cada procesador con cach propia, datos compartidos. Procesador modifica su cach: Debe actualizar memoria compartida Debe avisar a otros procesadores. Cach propia Solucin: BROADCAST: Escribir simultneamente Memoria compartida Cach de los otros

EC

Ignacio Rojas

BUSES

5.94

1. Evolucin y prestaciones de los computadores 2. Unidades funcionales de un computador. 3. Nivel de lenguaje mquina. 4. Desarrollo de programas en ensamblador.

5. Buses del sistema. Bus PCI.

6. Sistema de memoria interna. 7. Sistema de memoria externa. 8. Sistema de entrada/salida.

TEMA 5: BUSES

1. Estructuras del Bus 2. Tipos de Bus 3. Especificacin de un Bus 4. Paralelismo y multiplexacin 5. Arbitraje 6. Tipos de transferencia 7. Temporizacin y direccionamiento � 8. Ejemplos de Buses. PCI

EC

Ignacio Rojas

Ejemplos de Buses. PCI

5.95

PCI significa: interconexin de los componentes perifricos (Peripheral

Component Interconnect). Fue desarrollado por Intel. El bus PCI es independiente de la CPU, ya que entre la CPU y el bus PCI se instalar siempre un controlador de bus PCI, lo que facilita en gran medida el trabajo de los diseadores de placas.

EC

Ignacio Rojas

Ejemplos de Buses. PCI

5.96

1. El bus PCI no depende del reloj de la CPU, porque est separado de ella por el controlador del bus. 2. El lmite prctico en la cantidad de conectores para buses PCI es de tres/seis; ms conectores aumentaran la capacitancia del bus y las operaciones a mxima velocidad resultaran menos fiables. 3. A pesar de presentar un rendimiento similar al de un bus local conectado directamente, en realidad PCI no es ms que la eliminacin de un paso en el micropocesador. En lugar de disponer de su propio reloj, un bus PCI se adapta al empleado por el microprocesador y su circuitera, por tanto los componentes del PCI estn sincronizados con el procesador. El actual estndar PCI trabaja con un ancho de datos de 32/ 64 bits y a una velocidad de 132 MB/s o 264 MB/s

EC

Ignacio Rojas

Ejemplos de Buses. SCSI

5.97

SCSI: Small Computer System Interface.

Es un estndar universal para la conexin paralela de perifricos

� Podramos definir SCSI como un subsistema de E/S inteligente,

completa y bidireccional. Un solo adaptador host SCSI puede controlar desde 7 dispositivos inteligentes SCSI conectados a l (SCSI-1) hasta 127 (SCSI-3). � Una ventaja del bus SCSI frente a otros interfaces es que los dispositivos del bus se direccionan lgicamente en vez de fsicamente. Esto sirve para 2 propsitos: - Elimina cualquier limitacin que el PC-Bios imponga a las unidades de disco. - El direccionamiento lgico elimina la sobrecarga que el host podra tener en manejar los aspectos fsicos del dispositivo como la tabla de pistas daadas.. � Ideado para entornos UNIX y Macintosh, permite un ancho de datos de 8 bits para SCSI-1 hasta 16 bits para SCSI-3, con velocidades de transferencia de 4MB/s a 40 MB/s respectivamente.

EC

Ignacio Rojas

Ejemplos de Buses.

5.98

USB: (Universal Serial Bus). Es un bus serie que permite velocidades de hasta 12 Mbps, all que se pueden conectar hasta 127 dispositivos lentos, tales como ratn, cmaras de fotos, teclado, impresoras, etc. Ancho de datos=1 bits, vel. Transf. 1,5 MB/s FireWire (IEEE 1394) o bus serie de altas prestaciones. Se pueden conectar hasta 63 dispositivos y se logran altas velocidades de 400 Mbps. Una de sus lineas es de suministro de energia. Debido a su bajo costo y sencillez se utiliza en computadoras embebidas, tales como televisores de altas prestaciones, cmaras de video digitales Futurebus + (IEEE 896.1) Es una normalizacin proyectada para equipos de muy altas prestaciones, que puede considerarse como una evolucin de las normas Multibus II y VME. Permite la construccin de sistemas multiprocesardor (de hasta 32 procesadores) compartiendo memoria. Ancho de datos: 64,128,256 bits y vel. Transf: 95.2MB/s, 3.2 GB/s

Das könnte Ihnen auch gefallen

- Buses de DatosDokument98 SeitenBuses de DatosKing AuxNoch keine Bewertungen

- Tema BUSES PDFDokument72 SeitenTema BUSES PDFJuanjo herrera arandaNoch keine Bewertungen

- UNIDAD 3 Clase 08 Buses y ChipsetDokument129 SeitenUNIDAD 3 Clase 08 Buses y ChipsetDaniel JimenezNoch keine Bewertungen

- L3.11 Conectando Todo Estructura de Un PCDokument12 SeitenL3.11 Conectando Todo Estructura de Un PCJosé Carlos PagánNoch keine Bewertungen

- Taller Nº2 OrganizacionDokument12 SeitenTaller Nº2 OrganizacionMartinezMelloNoch keine Bewertungen

- 02 Unidad IIDokument25 Seiten02 Unidad IIBraian Stalin Pineda ReyesNoch keine Bewertungen

- UTP - Capítulo 5 Arquitectura Del ComputadorDokument60 SeitenUTP - Capítulo 5 Arquitectura Del ComputadorMichel AndersonNoch keine Bewertungen

- 1 - Introducción A La InformáticaDokument42 Seiten1 - Introducción A La InformáticaANA BORONDONoch keine Bewertungen

- Resumen Parcial 01 ODokument3 SeitenResumen Parcial 01 Ofisica1Noch keine Bewertungen

- Entrada Salida Sistemas OperativosDokument33 SeitenEntrada Salida Sistemas OperativosKosi Gar100% (1)

- 1 Tipos de ArquitecturasDokument9 Seiten1 Tipos de ArquitecturasKenia CruzNoch keine Bewertungen

- Resumen BusesDokument2 SeitenResumen BusesSantino Nicolás MartínezNoch keine Bewertungen

- Arquitectura de Computadoras y Modelos de ArquitecturasDokument15 SeitenArquitectura de Computadoras y Modelos de ArquitecturasPabloGomezPerezNoch keine Bewertungen

- Actividad 2 Tema 2Dokument2 SeitenActividad 2 Tema 2Javi PJNoch keine Bewertungen

- FH T1.4 UnidadESDokument9 SeitenFH T1.4 UnidadESRaul RodriguezNoch keine Bewertungen

- Tema 5 Documento - Administracion Dispositivos de Entrada-Salida - 2020Dokument45 SeitenTema 5 Documento - Administracion Dispositivos de Entrada-Salida - 2020Rocker TrcksNoch keine Bewertungen

- T2 Arquitectura de Un ComputadorDokument7 SeitenT2 Arquitectura de Un ComputadorSamuelNoch keine Bewertungen

- Esquema Del Funcionamiento de Una ComputadoraComputadoraDokument85 SeitenEsquema Del Funcionamiento de Una ComputadoraComputadoraMi Lord RicardoNoch keine Bewertungen

- T3. Buses, Procesadores y MemoriasDokument71 SeitenT3. Buses, Procesadores y MemoriasbyhsrwgdNoch keine Bewertungen

- Fundamentos M1Dokument37 SeitenFundamentos M1Manuel MorenoNoch keine Bewertungen

- El ComputadorDokument4 SeitenEl ComputadorEloy José BanquetNoch keine Bewertungen

- Montar Una Red Inalambrica Ad-Hoc.Dokument5 SeitenMontar Una Red Inalambrica Ad-Hoc.Miguel VillegasNoch keine Bewertungen

- Arquitectura ComputadoraDokument4 SeitenArquitectura ComputadoraEthiel Morales CNoch keine Bewertungen

- Revisión Del Hardware de ComputadoraDokument21 SeitenRevisión Del Hardware de ComputadoraAnonymous U1yUg3Noch keine Bewertungen

- 5.4 Estandares de BusesDokument12 Seiten5.4 Estandares de BusesPedro Alfonso Granados GarciaNoch keine Bewertungen

- Buses 1.2.4Dokument10 SeitenBuses 1.2.4Alejandro Valencia100% (1)

- Buses Interrupciones Estructura y FuncioDokument5 SeitenBuses Interrupciones Estructura y Funciochristian mendozaNoch keine Bewertungen

- Cuestionario Arquitectura de Las ComputadorasDokument5 SeitenCuestionario Arquitectura de Las ComputadorasHumberto FlorencioNoch keine Bewertungen

- U1.2-Arquitectura Von Newmann y BusesDokument8 SeitenU1.2-Arquitectura Von Newmann y BusesAngel JimenezNoch keine Bewertungen

- Ciclo Fetch CodeDokument25 SeitenCiclo Fetch CodeFernando Cruz AlvizoNoch keine Bewertungen

- 5 Buses Del SistemaDokument50 Seiten5 Buses Del SistemaGalo TarapuésNoch keine Bewertungen

- 5 Buses Del SistemaDokument56 Seiten5 Buses Del Sistematobey maximoNoch keine Bewertungen

- UTP. SO. s11. Hardware ES e InterrupcionesDokument15 SeitenUTP. SO. s11. Hardware ES e InterrupcionesElmer CeladitaNoch keine Bewertungen

- Placa Base PDFDokument7 SeitenPlaca Base PDFmariachi_tNoch keine Bewertungen

- Arquitectura HarvardDokument4 SeitenArquitectura HarvardJose Giovanni GfNoch keine Bewertungen

- Perifericos y Memoria ExternaDokument42 SeitenPerifericos y Memoria ExternaGoldMaverickNoch keine Bewertungen

- Cap - 7 BusesDokument48 SeitenCap - 7 BusesRenzoMahrNoch keine Bewertungen

- Bus de DatosDokument4 SeitenBus de Datosed00mNoch keine Bewertungen

- AMD K7 Processor AnalysisDokument7 SeitenAMD K7 Processor AnalysisjosegalavizcNoch keine Bewertungen

- TP de AlanDokument6 SeitenTP de AlanBraian GonzalezNoch keine Bewertungen

- Guia Sistemas 3er Parcial PDFDokument9 SeitenGuia Sistemas 3er Parcial PDFRolando Aguilar CalvilloNoch keine Bewertungen

- Ejercicios HardwareDokument6 SeitenEjercicios HardwarenandoNoch keine Bewertungen

- 3 Unidad Entrada / Salida: ObjetivosDokument28 Seiten3 Unidad Entrada / Salida: ObjetivostercoxNoch keine Bewertungen

- Tarea 2. - InvestigaciónDokument7 SeitenTarea 2. - InvestigaciónAlejandra Diaz DamianNoch keine Bewertungen

- Tarea 6 Sistemas DigitalesDokument5 SeitenTarea 6 Sistemas DigitalesAlexisNoch keine Bewertungen

- Arquitectura Del Interior Del GabineteDokument5 SeitenArquitectura Del Interior Del Gabineteyanina CastroNoch keine Bewertungen

- CAP 11 Gestión de ES y Planificación de Discos PDFDokument64 SeitenCAP 11 Gestión de ES y Planificación de Discos PDFHanibbal LecterNoch keine Bewertungen

- Gestion Entrada SalidaDokument11 SeitenGestion Entrada SalidaAmparo OrtizNoch keine Bewertungen

- HW Tema1 Arquitectura de Un OrdenadorDokument17 SeitenHW Tema1 Arquitectura de Un OrdenadorjoansanchiswebNoch keine Bewertungen

- Examen Final Arquitectura de Computadoras Semipresencial 2019-IDokument3 SeitenExamen Final Arquitectura de Computadoras Semipresencial 2019-Iroger vegaNoch keine Bewertungen

- 3 DescripcionDokument8 Seiten3 DescripcionAnonymous 1a41w9kKQENoch keine Bewertungen

- Arquitectura de Las ComputadorasDokument5 SeitenArquitectura de Las ComputadorasHermes MejíaNoch keine Bewertungen

- Cuaderno SODokument8 SeitenCuaderno SOtyco urribarriNoch keine Bewertungen

- El BusDokument5 SeitenEl BusEduardo GonzalezNoch keine Bewertungen

- Actividad Unidad 2Dokument5 SeitenActividad Unidad 2Matias PirisNoch keine Bewertungen

- Apuntes de La Unidad 2Dokument53 SeitenApuntes de La Unidad 2López SantiagoNoch keine Bewertungen

- Programacion General Trabajo 1Dokument8 SeitenProgramacion General Trabajo 1Carlos DanielNoch keine Bewertungen

- Taller MicroprocesadoresDokument5 SeitenTaller MicroprocesadoresDanielNoch keine Bewertungen

- UF0852 - Instalación y actualización de sistemas operativosVon EverandUF0852 - Instalación y actualización de sistemas operativosBewertung: 5 von 5 Sternen5/5 (1)

- Computadores para bases de datos. IFCT0310Von EverandComputadores para bases de datos. IFCT0310Noch keine Bewertungen

- Formula Plaz Fijo PDFDokument1 SeiteFormula Plaz Fijo PDFparquedigitalsacNoch keine Bewertungen

- Formto Reclamo PDFDokument1 SeiteFormto Reclamo PDFparquedigitalsacNoch keine Bewertungen

- Infor Adicional PDFDokument2 SeitenInfor Adicional PDFparquedigitalsacNoch keine Bewertungen

- Itrimestre PDFDokument1 SeiteItrimestre PDFparquedigitalsacNoch keine Bewertungen

- Formula CTS PDFDokument1 SeiteFormula CTS PDFparquedigitalsacNoch keine Bewertungen

- Autismo LogopedaDokument15 SeitenAutismo LogopedaparquedigitalsacNoch keine Bewertungen

- Manual PLSQL BasicoDokument108 SeitenManual PLSQL BasicoAna SantosNoch keine Bewertungen

- Como Estructurar Un Informe TecnicoDokument2 SeitenComo Estructurar Un Informe TecnicoRückseiteA.MatosNoch keine Bewertungen

- Informe Internado - Ups Puno - Imprimir para EmpastadoDokument129 SeitenInforme Internado - Ups Puno - Imprimir para Empastadoparquedigitalsac67% (3)

- Ley Del Ejercicio Profesional Bibliotecologia y Ciencias de La InformacionDokument2 SeitenLey Del Ejercicio Profesional Bibliotecologia y Ciencias de La InformacionparquedigitalsacNoch keine Bewertungen

- Micro Proce Sad orDokument40 SeitenMicro Proce Sad orparquedigitalsacNoch keine Bewertungen

- Indicadores Precio Economia 2010Dokument123 SeitenIndicadores Precio Economia 2010Cesar RamosNoch keine Bewertungen

- Librosunam2010 6dicDokument12 SeitenLibrosunam2010 6dicparquedigitalsacNoch keine Bewertungen

- AUTOMATA UnlockedDokument106 SeitenAUTOMATA UnlockedYonatan Hernandez AlvaradoNoch keine Bewertungen

- Intro Tgs TDokument34 SeitenIntro Tgs TCarlos Hernan Acero CharañaNoch keine Bewertungen

- Libros Electronicos 1ra ParteDokument25 SeitenLibros Electronicos 1ra ParteJulio Antonio Aguilar VillenaNoch keine Bewertungen

- A Sistemas de Información PDFDokument22 SeitenA Sistemas de Información PDFSaulo Patrick Linares ChumbeNoch keine Bewertungen

- SI-Sistemas de Informacion PDFDokument27 SeitenSI-Sistemas de Informacion PDFJosé Espejo PantigosoNoch keine Bewertungen

- Conexion Basica PICDokument5 SeitenConexion Basica PICJuan LivingstonNoch keine Bewertungen

- Proyecto Fuente VariableDokument13 SeitenProyecto Fuente VariableRonny TigreroNoch keine Bewertungen

- Laboratorio 1 - InformeDokument8 SeitenLaboratorio 1 - InformeAnderson QuirozNoch keine Bewertungen

- P7 Ruiz CHDokument10 SeitenP7 Ruiz CHJMartin Herdez TNoch keine Bewertungen

- Actividad 1 Resonancia Richard ArrolloDokument26 SeitenActividad 1 Resonancia Richard ArrolloRichard ArrolloNoch keine Bewertungen

- Televisión Digital HDTVDokument10 SeitenTelevisión Digital HDTVChristian Antonio100% (1)

- Configuracion Basica de Switch Enterasys A SeriesDokument9 SeitenConfiguracion Basica de Switch Enterasys A SeriesedmoxaNoch keine Bewertungen

- SDC Lam 2Dokument62 SeitenSDC Lam 2VERONICA TALIA GUANOLUISA MORETANoch keine Bewertungen

- ManualDokument23 SeitenManualPedro Mario CatireNoch keine Bewertungen

- Guía de Armado de Sensor Infrarrojo para PC - Parte 1Dokument5 SeitenGuía de Armado de Sensor Infrarrojo para PC - Parte 1David SormanniNoch keine Bewertungen

- Fig. 1.3 Atomic Structure of (A) Silicon (B) Germanium and (C) Gallium and ArsenicDokument24 SeitenFig. 1.3 Atomic Structure of (A) Silicon (B) Germanium and (C) Gallium and ArsenicalanNoch keine Bewertungen

- Manual de Electronica Aplicada PDFDokument33 SeitenManual de Electronica Aplicada PDFGerman Varez100% (1)

- Tarea 3 (DISCO DURO Y SOLIDO)Dokument7 SeitenTarea 3 (DISCO DURO Y SOLIDO)erick ramosNoch keine Bewertungen

- Teorema SuperposicionDokument6 SeitenTeorema Superposicionerick izaNoch keine Bewertungen

- Microprocesador 8086Dokument33 SeitenMicroprocesador 8086Ronald Isaac Cabrera VieraNoch keine Bewertungen

- Componentes de Un Sistema CCTVDokument3 SeitenComponentes de Un Sistema CCTVOcon MartínNoch keine Bewertungen

- Calibración de TORREY - VariasDokument48 SeitenCalibración de TORREY - VariasFrancisco Becerra ANoch keine Bewertungen

- PBCDokument5 SeitenPBCRamiro Marca SarzuriNoch keine Bewertungen

- Curso Estructuras de Datos Parte I - 100 ReactivosDokument24 SeitenCurso Estructuras de Datos Parte I - 100 ReactivosJLDN2202100% (1)

- Practica - 6 Mosfet Como InterruptorDokument4 SeitenPractica - 6 Mosfet Como InterruptorAlejandro Marin100% (1)

- Saber Electrónica No. 210 PDFDokument76 SeitenSaber Electrónica No. 210 PDFheribertosfa0% (1)

- List A ActualDokument6 SeitenList A ActualLuis Fernando Guerra TorricoNoch keine Bewertungen

- Teoria LtaDokument3 SeitenTeoria LtaobetNoch keine Bewertungen

- Inversores DC - ACDokument24 SeitenInversores DC - ACeldennisoacNoch keine Bewertungen

- Libro Fundamentos MicroprocesadoresDokument5 SeitenLibro Fundamentos Microprocesadoresrivamara59600% (1)

- Practica de CompuertasDokument17 SeitenPractica de CompuertasFelipe LlerenaNoch keine Bewertungen

- ¿Cómo Testear PLCs - Guía Básica de Diagnóstico de PLCsDokument8 Seiten¿Cómo Testear PLCs - Guía Básica de Diagnóstico de PLCsJuanCarlosGranadoNoch keine Bewertungen

- Ejemplo de AstableDokument4 SeitenEjemplo de AstableDaniel Ñahuis TisnadoNoch keine Bewertungen

- Act I Vida Des Complement Aria Su 2Dokument6 SeitenAct I Vida Des Complement Aria Su 2Sergiusz Sam0% (1)