Beruflich Dokumente

Kultur Dokumente

Yang Errorcontrol

Hochgeladen von

Naveen GuptaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Yang Errorcontrol

Hochgeladen von

Naveen GuptaCopyright:

Verfügbare Formate

Performance Analysis of Error Control Codes for Wireless Sensor Networks

Gopinath Balakrishnan, Mei Yang, Yingtao Jiang, and Yoohwan Kim* Texas Instruments Inc., Dallas, TX 75243 Department of Electrical and Computer Engineering * School of Computer Science University of Nevada, Las Vegas, NV 89154 Emails: gopi@ti.com, { meiyang, yingtao}@egr.unlv.edu, *yoohwan@cs.unlv.edu Abstract

In wireless sensor networks, the data transmitted from the sensor nodes are vulnerable to corruption by errors induced by noisy channels and other factors. Hence it is necessary to provide a proper error control scheme to reduce the bit error rate (BER). Due to the stringent energy constraint in sensor networks, it is vital to use energy efficient error control scheme. In this paper, we focus our study on the performance analysis of various error control codes in terms of their BER performance and power consumption on different platforms. In detail, error control codes with different constraints are implemented and simulated using VHDL. Implementation on FPGA and ASIC design is carried out and the energy consumption is measured. The error control performance of these codes is evaluated in terms of Bit Error Rate (BER) by transmitting randomly generated data through a Gaussian channel. Based on the study and comparison of the three different error control codes, we identify that binary-BCH codes with ASIC implementation are best suitable for wireless sensor networks. Keywords - Wireless sensor network; Error Control Code; BER; power consumption. In [7], the Minimum Energy (ME) coding scheme for sources with unknown statistics and a new method of code-by-code detection that can detect and correct certain errors in the received codeword is proposed. This research combines the modulation with the error control scheme to minimize power consumption. The on/off key modulation performance is improved with a ME-Coding. However, the ME codes have no capability of error correction [7]. To identify energy-efficient error control codes for sensor networks, in this paper, we study and analyze the performance of several error control codes. Power consumption in a circuit is directly proportional to its complexity. In general, the encoder consumes negligible power when compared to the decoder. Thus, the challenge is to choose an error control code with less complex decoding circuit. In our study, we consider two types of codes: linear block codes and convolutional codes. Linear block codes can be either cyclic or non-cyclic. Cyclic codes are of interest and importance due to their rich algebraic structure which has extremely concise specifications and can be efficiently implemented using simple shift registers [5]. The most widely used cyclic codes for wireless applications are BCH codes [4]. For the purpose of our study, binary-BCH codes and the most popular non-binary BCH codes, namely Reed Solomon (RS) codes, are studied and analyzed. For comparison purpose, we also studied and analyzed the convolutional code with Viterbi algorithm. The rest of the paper is organized as follows. Section 2 discusses the methodology used to conduct the performance analysis. Section 3 presents and compares the BER performance and power consumption of several error correction codes and identifies the energy-efficient error control code with the results obtained.

1. Introduction

The low-cost, rapid deployment, ability of self-organization and cooperative data-processing, have made wireless sensor networks a practical solution for a wide range of application areas, including military and homeland security, health, environment, industry and commercial, and home [1]. The most significant challenge in sensor networks is to overcome the energy constraints since each sensor node has limited energy to consume. Since data transmitted over the wireless media is vulnerable to corruption by noise, error control schemes are necessary to keep the Bit Error Rate (BER) low. Due to the stringent energy constraint, it is impossible to increase the signal power of the transmitted signal in wireless sensor networks. Hence an alternative way is to use the error control codes to reduce the BER. The encoding and decoding circuitry for error control codes may consume a sizable amount of power. This motivates us to study energy-efficient error detection/correction codes. In the literature, there is limited work on energy-efficient error control schemes for sensor networks and some of them are reviewed as follows. In [1], it is shown that usage of ARQ is limited for sensor networks due to the additional retransmission energy cost and overhead. In [8], convolutional codes are analyzed for power in a frequency nonselective, slow Rayleigh fading channel. Results show that the energy required for encoding data is negligible. However, performing Viterbi decoding on a Strong-ARM processor using a C compiler is energy-intensive as the average energy consumption per useful bit grows exponentially with the constraint length of the code and independent of code rate. Using forward error correction (FEC) is inefficient if the decoding is performed using a microprocessor, for which a dedicated onboard Viterbi decoder is suggested [8]. To the best of our knowledge, study of other error control codes for sensor networks is not available in the literature.

2.

Methodology

In this work, we evaluate the power consumption of three different FEC codes, BCH, RS, and convolution codes on different platforms. The implementation on general processors may be inefficient due to the limitation of the compiler and other factors [8]. Hence, we implement the three codes with different constraints using hardware description language and estimate their power consumption on FPGA and ASIC. The code with the least power consumption is identified. All the comparison is based on the assumption of the same error control performance which is evaluated by the BER test. In the following, we explain the methods used in our study.

2.1. Implementation of Codes

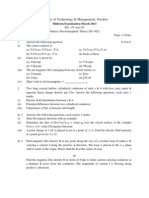

The three types of error correction codes are implemented using VHDL. Fig. 1 illustrates the procedure of encoding and decoding in a communication system, where u is the information word, v is the codeword, v is the received word and u is the decoded word. The encoder circuits of linear block codes and convolutional codes have simple hardware and are easy to implement. Some of the issues considered while implementing the decoder circuits are as follows. In binary-BCH and RS codes, the Euclid's Algorithm (EA) [9] the Berlekamp-Massey Algorithm (BMA) [1][5] can be used to compute the coefficients of error polynomial (x) = 0 + 1x + ... + txt. In EA, all the steps used for computation are identical

and easy to implement in hardware. Hence for efficient hardware implementation EA is preferred than BMA [6]. The information received by the receiver shown in Fig. 1 is quantized before decoding. Depending on the level of quantization, the decoding can be classified into Hard Decision Decoding (HDD) or Soft Decision Decoding (SDD) [6]. The HDD is used when the quantization level is two while SDD is used for quantization level greater than two. The SDD performs better than HDD but requires highly complex circuitry [6]. Hence HDD is implemented to minimize the power in the decoder [6].

on Source

Noisy Medium u v

Information Informati Source

Encoder

Modulator

Information destination

Decoder

Demodulator

The Gaussian random number G obtained by using Rayleigh random variable R is given by Eq. (2). G = +R*cos(2**T), (2) where T is a uniformly distributed random number and is the mean of the Gaussian random variable. The generated Gaussian noise is then added to the encoded bits and transmitted. The received symbols are quantized and fed to the decoder to obtain the information bits. Quantization refers to the process of approximating the continuous set of values with a finite set of values. As explained in Section 2.1, the 2-level quantization is used to reduce the complexity of the decoder. In the 2-level quantization, the received signal is mapped to 0 if the signal level is greater than zero and mapped to one if the signal level is less than 0. The result obtained in this way is called hard decision. The hard decision decoder is used to decode the quantized data which are 1s and 0s. The decoded data is then compared with the corresponding input given to the encoder and the BER is calculated. The BER of the uncoded channel is theoretically calculated using Eq. (3). P(e) = *erfc(sqrt(Eb/No) = Q(sqrt(2Eb/No)). (3) The performance of the coded and uncoded channels is compared based on the calculated BER.

Figure 1. Procedure of encoding and decoding in a communication system.

2.3. Power Estimation in FPGA Design

The FPGA used for this work is Xilinx Virtex-E XCV200E6CS144 [12]. The Xilinx Integrated Software Environment (ISE) 7 along with Xilinx Power (XPower) [12] is used for estimating power. XPower calculates the power in the design by summing up the power consumed by each element. The power consumed by each switching element in the design is given by Eq. (4). P = C*V2*E*F, (4) where P represents the power in mW, C represents the capacitance in Farads, V represents the voltage in Volts, E represents the switching activity (average number of transitions per clock cycle), and F represents the frequency in Hz.

2.2. Performance Measure

The next step is to measure the error correcting capability of the implemented codes which is given by BER, which is obtained by the number of erroneous bits divided by the total number of transmitted bits. BER is affected by several factors including noise in the channel, quantization technique used, code rate R, energy per symbol to noise ratio Es/No and transmitter power level Pout. The code rate is given by R = k/n, where k is the number of bits at the input of the encoder and n is the number of bits at the output of the encoder. The BER is shown to be directly proportional to the code rate and inversely proportional to energy per symbol noise ratio and transmitter power level [2]. The encoder encodes the data with code rate R and transmits it over the noisy channel. If the transmitter power level Pout is unchanged, then the received energy per symbol E decreases to R*E. Hence, the BER measured at the input of the decoder is larger than the BER of the data transmitted without coding [2]. This increase in BER is overcome by using a decoder that can correct errors. Proper choice of error correction codes will reduce the BER to several orders of magnitude. The difference in BER achieved by using error correction codes to that of uncoded transmission is referred to as coding gain. The BER test is performed by simulations on Matlab following the procedure shown in Fig. 1. First the information bits are generated using a random number generator. The randomly generated data is then sent to the encoder circuit and encoded into code words, which are transmitted over the noisy channel. Before transmitting, the encoded data is modulated using Phase Shift Keying (BPSK), which is done by mapping 1/0 at the output of the encoder to -1/+1 of an antipodal baseband signal [3]. To evaluate the performance of the error control codes in the noisy channel, an Additive White Gaussian Noise (AWGN) channel is modeled. Adding Gaussian noise to the encoded data is done by generating Gaussian random numbers with desired energy per symbol to noise ratio. The variance 2 of additive Gaussian noise which has the power spectrum of No/2 Watts/Hz is equal to No/2. If the energy per symbol Es is set to 1, then we have Es/No = 1/2 2 and the standard deviation is given by = sqrt(1/2(Es/No)). Hence, the standard deviation with desired Es/No is calculated and used to obtain a Rayleigh random variable R as shown in Eq. (1). R = sqrt(2*2*ln(1/1-U)), (1) where 2 is the variance of the Rayleigh random variable and U is a uniformly distributed random number.

2.4. Power Estimation in ASIC Design

Power estimation in ASIC is studied using Synopsyss Design Compiler (DC) and Design Vision [10]. The power analysis in ASIC is performed in the following procedure. First the VHDL design is analyzed to check if it uses the synthesizable VHDL subset. Then the design is elaborated, where the design is built with generic and technology-independent components like Gates, Flip Flops, MUX, etc. It is followed by uniquify, where multiple copies of the subdesign are made whenever it is referred in the upper level of the hierarchy, and each copy is optimized in a unique way according to the conditions and constraints. The last step of synthesis is compiling, where the network generic components is translated into a netlist of the target library. Compilation can be constrained in terms of power. The power report is then generated.

3.

Performance Analysis

In this section, we present and compare the performance of the binary-BCH, RS codes, and Viterbi codes in terms of their error correction capability in bit error rate (BER) and complexity and power consumption on FPGA and ASIC.

3.1. BER Test

Fig. 2 compares the BER of uncoded channel, binary-BCH and RS codes. A (n, k, t) binary-BCH and RS code can correct up to terrors, where t is directly proportional to the number of parity bits (nk) [4]. Hence the performance of various binary-BCH and RS codes are analyzed by varying n and k and their corresponding energy consumption is measured. For this purpose, implementation is done by varying (n-k). For binary-BCH codes, n is chosen as 31 and k varies in {26, 21, 16, 11}. It is clear from Fig. 2 that the BCH(31,11,5) code, which can correct up to 5 errors has the lowest BER curve with the highest

coding gain of 5 dB and the lowest code rate of 0.355. While the BCH(31,26,1) code, which can correct up to 1 error has very minimal coding gain with the highest code rate of 0.839. The BCH(31,16,3) and BCH(31,21,2) have coding gain of 4 dB and 2 dB with code rate of 0.516 and 0.677, respectively.

example, considering BCH(31,16,3) and RS(31,15,8) with code rate 0.5, for BER greater than 10-2, the BCH code performs better than the RS code, while for BER less than 10-2 the RS codes perform better. Unlike block codes, low BER and large coding gain in (n, k, m) convolutional codes are achieved not by increasing k and n but by increasing the memory order m. Hence to analyze the performance of these codes, various convolutional codes of different memory orders are implemented and their energy consumption is measured. In this thesis, simulation is done for convolutional encoders with fixed code rate R = and by varying memory order m in {3, 4, 5, 6}. Fig. 3 shows that the coding gain increases with the increased memory order m. The Viterbi (VIT) (2,1,3), (2,1,4), (2,1,5), and (2,1,6) codes approximately have a coding gain of 1 dB, 2 dB, 3 dB and 4 dB, respectively. Convolutional codes implemented using soft decision decoder improves the coding gain by 3 dB than that implemented using hard decision decoder [3]. The tradeoff is that soft decision decoder requires highly complex hardware [6].

3.2. Complexity and Power Analysis in FPGA

2400 2200 2000 1800 1600 1400

N umber of Slic es

Encoder Decoder

1200 1000 800 600 400 200 0

Figure 2. BER of linear cyclic block codes.

Figure 4. Complexities of BCH, RS, and Viterbi Codes.

420 400 380 360 340 320 300 280 260 240 220 200 180 160 140 120 100 80 60 40 20 0

Figure 3. BER of convolutional codes. For RS codes, n is chosen as 31 and k varies in {25, 21, 15, 11}. Fig. 2 clearly shows that the coding gains of RS codes are not the same for all the BER. They perform worse than the uncoded channel for higher values of BER and provide asymptotically high gain at lower values of BER. From the figure, we can see that using RS codes for BER of 10-1 or higher results in channel loss while using them for BER lesser than 10-1 results in extremely high gain. Because the RS codes correct symbol errors, they are more suitable for applications with BER lesser than 10-1. For BER lower than 10-1, the RS(31,11,10) code, which can correct up to 10 symbol error, has the lowest BER curve with a coding gain of approximately 6 dB and a minimum code rate of 0.355. While the RS(31,25,3) code capable of correcting 3 symbol errors has the largest BER curve with a coding gain of 2 dB and a maximum code rate of 0.806. The RS (31,15,8) code and the RS (31,21,5) code have coding gain of 4 dB and 3 dB and code rate of 0.4838 and 0.677, respectively. Fig. 2 also compares the binary-BCH codes with the RS codes based on code rates. The binary-BCH codes show a better performance at higher BER than the RS codes. But for lower BER, the RS codes perform better than the binary-BCH codes. For

Figure 5. Power consumption in FPGA design. The complexity of the FPGA implementation is measured by the number of slices used on Xilinx XCV200E. The slice utilization of each of the codes obtained from the synthesis report is plotted in Fig. 4. From the figure, it can be inferred that the complexity of the encoder and decoder circuitry of BCH codes and RS codes increases linearly with the number of parity bits (n-k) increasing. On the other hand, the complexity of the Viterbi decoder circuitry increases alarmingly with memory order m increasing. It can be observed that the encoder circuit of the convolutional codes and the binary-BCH codes are less complex than that of the RS codes. This is because the RS codes use non-binary encoders. For decoder, the binary-BCH codes have less complex circuit than those of the RS codes and the convolutional codes. Power estimation of all

BC H BC (15 H ,11 BC (31 ,1) H ,26 BC (31 ,1) H ,21 B (31 ,2) C ,1 H (3 6,3 R 1,1 ) S (1 1,5 R 5,1 ) S( 1 3 ,2 R 1,2 ) S( 5 3 ,3 R 1,2 ) S( 1 , R 31, 5) S( 15 31 ,8 ,1 ) 1 Vi ,10 t(2 ) Vi ,1,3 t(2 ) Vi ,1,4 t(2 ) Vi ,1,5 t(2 ) ,1 ,6 )

Codes

Dynamic Power/bit (mW)

BC H (1 BC 5,1 1 H (3 ,1) 1, B 26 C H (3 ,1) BC 1,2 1 H (3 ,2) 1, B 16 C H (3 ,3) 1, 11 R S( , 15 5) ,1 R 1, S 2 (3 1, ) 2 R S( 5,3 31 ) ,2 R S( 1,5 31 ) R S ,15 (3 1, ,8) 11 ,1 0) V it( 2, 1, 3 Vi t(2 ) ,1 ,4 V ) it( 2, 1, 5 Vi ) t( 2, 1, 6)

Codes

Encoder(mW) Decoder(mW) Error Control

the codes using XPower is plotted in Fig. 5. Among all the codes, the binary-BCH codes consume the least power.

Hence, linear cyclic block codes consume significantly less power than uncoded channel.

1200 1100 1000 900 800 700 600 500 400 300 200 100 0 Power/ bit (nW)

Coded Channel Uncoded Channel

3.3. Power Analysis in ASIC

Power consumption in ASIC design is obtained as explained in Section 2. The target library used is lsi_10k.db [10]. Fig. 6 shows the power consumed by the encoder and decoder circuitry of all three type of codes in ASIC. It is clear that the power consumption in binary-BCH and RS codes are directly proportional to the number of parity bits and the power consumption of the convolutional code is proportional to the memory order m. Also the power consumed by the decoder circuit is significantly higher than that consumed by the encoder circuit of all the codes. The decoding of RS codes and convolutional codes consume significantly larger amount of power compared to that of the binary-BCH codes. And the binary-BCH codes consume the least power among all the codes.

320 300 280 260 240 220 200 180 160 140 120 100 80 60 40 20 0

Encoder(nW) Decoder(nW) Error Control

Figure 7. Power consumption in sensor node for coded and uncoded Channels.

1200 1100 1000 900 800 700 600 500 400 300 200 100 0

Power/bit (nW)

Power/bit (nW)

BC H ( BC 15,1 1, H ( 1 BC 31,2 ) 6, H (3 1 BC 1,2 ) 1, H 2 ( BC 31,1 ) 6 H (3 ,3) 1 R ,11 S( 15 ,5) R , 11 S( 31 ,2) R , 25 S( 31 ,3) R , 21 S( 3 ,5 R 1, 1 ) S( 31 5,8 ,1 ) 1 Vi ,10) t (2 ,1 Vi , 3) t (2 ,1 Vi , 4) t (2 ,1 Vi , 5) t (2 ,1 ,6 )

Codes

Figure 6. Power consumption in ASIC design.

3.4. Power Analysis for Sensor Nodes

In the following, we analyze the power consumption of the encoding/decoding circuit in a sensor node. As the power consumption in ASIC implementation is much less than that in FPGA implementation, we use the power results in ASIC implementation for the analyze based on TSMC 0.18m by taking 2.5 times the results obtained using lsi_10k.db (as we measured through experiments). The total power consumed in the sensor node for communication with coded channel is given by Eq. (5) [8]. E(k,d) = {ET(k,d)+Eencode}+{ER(k)+Edecode}, (5) where ET is the energy used by the transmitter circuitry, which is a function of the no. of message bits (k) and the distance between the sensor nodes (d); ER is the energy used by the receiver circuitry, which is given by Eelec*k; Eencode and Edecode is the energy used to encode and decode respectively, which can be obtained from the results in Section 2.2. For uncoded channel, the receiving power is same as that of the coded channel, while the transmission power is given by Eq. (6). ET(k,d)=Eelec*k + Eamp*k*d2, (6) where Eelec is the energy consumed by transmitter/receiver circuit; Eamp is the energy consumed by the amplifier; k is the no. of message bits; d is the distance between the sensor nodes. For our analysis d2 is chosen as 500, k = 1201200, Eelec = 50nJ/bit and Eamp = 100pJ/bit/m2. Fig. 7 compares the power consumption of the coded channel and uncoded channel with encoders/decoders implemented in ASIC. It can be inferred that the power consumed by the binary-BCH codes and RS codes for coded channel is less than that of the uncoded channel. While coded channel using convolutional encoder with Viterbi decoder consumes more power than that of the uncoded channel. Hence it is clear that convolutional codes are not suitable for wireless sensor networks. Fig. 8 clearly shows that the significant amount of power consumed by the sensor node goes for error control if convolutional codes are used while power consumed by transceivers dominate the total power consumption if binary-BCH codes or RS codes are used.

Figure 8. Power consumption in transceivers and error control circuitry.

References

I.F. Akyildiz, W. Su, Y. Sankarasubramaniam, and E. Cayirci, A survey on sensor networks, IEEE Communications Magazine, pp. 102114, Aug. 2002. [2] I.F. Akyildiz, W. Su, Y. Sankarasubramaniam, and E. Cayirci, Wireless sensor networks: a survey, Computer Networks: The Intl Journal of Comp. and Telecom. Net., vol. 38, no.4, pp.393-422, Mar. 2002. [3] Chip Fleming, A Tutorial on Convolutional Coding with Viterbi Decoding, Spectrum applications, Derwood, USA, 1999. [4] S. Lin and D.J. Castello, Error control coding, Fundamentals and applications, Premtice-Hall, New Jersey, 1983. [5] J.L. Massey, Shift-register synthesis and BCH decoding, IEEE Trans. Inf. Theory, vol. 15, pp. 122-127, January 1969. [6] Robert H. Morelos-Zaragoza, The Art of Error Correcting Coding, John Wiley & sons, New York, 2002. [7] Y. Prakash and S.K.S. Gupta, Energy efficient source coding and modulation for wireless applications, IEEE Trans. Inform. Theory, pp. 212-217, Mar. 2003. [8] E. Shih et al., Physical layer driven protocol and algorithm design for energy-efficient wireless sensor networks, Proc. ACM MobiCom 01, Rome, Italy, pp. 27286, Jul. 2001. [9] Y. Sugiyama, M. Kasahara, S.Hirasawa, and T. Namekawa, A method for solving key equation for decoding Goppa codes, Inf and Control, vol. 27, pp. 87-99, 1975. [10] Synopsys Inc., http://www.synopsys.com/products/logic/design_compiler.html. [11] TSMC Inc., http://www.mosis.org/products/fab/vendors/tsmc/tsmc018. [12] XILINX, The Programmable Logic Data Book, Xilinx Inc, San Jose, CA, 2002. [1]

BC H BC (1 H 5,1 BC (3 1, 1 1 BCH(3 ,26, ) H 1 1 BC (3 ,21, ) H 1,1 2) ( R 31, 6,3) S( 11 R 15, ,5) S 1 R (31 1,2 S( ,2 ) R 31, 5,3 S R (31 21, ) S( , 5) 31 15 ,1 ,8 Vi 1,1 ) t(2 0 Vi ,1 ) t( ,3 Vi 2,1 ) t(2 ,4 Vi ,1 ) t(2 ,5 ,1 ) ,6 )

Codes

BC H BC (1 H 5, B (3 11, CH 1, 1) B (3 26, CH 1, 1) BC (3 21, H 1,1 2) ( 6 R 31, ,3) S( 11 R 15, ,5) S( 1 1 R 31, ,2) S( 2 5 R 31, ,3) S 2 R (31 1,5 S( , ) 31 15 ,1 ,8 V 1,1 ) it( 0 2 Vi ,1, ) t(2 3) Vi ,1, t(2 4 Vi ,1, ) t(2 5) ,1 ,6 )

Codes

Error Control/bit Transceiver/bit Coded Channel

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- IEEE 802.11nDokument10 SeitenIEEE 802.11nNaveen GuptaNoch keine Bewertungen

- Ericsson W-Cdma Bbu/rru SystemDokument2 SeitenEricsson W-Cdma Bbu/rru SystemAbdeladhim Stich67% (3)

- SushantaDas TalkDokument1 SeiteSushantaDas TalkNaveen GuptaNoch keine Bewertungen

- Special Corporate Rate in Qatar Crystal PalaceDokument3 SeitenSpecial Corporate Rate in Qatar Crystal PalaceNaveen GuptaNoch keine Bewertungen

- Abhinav 2012121 DCS HW1Dokument2 SeitenAbhinav 2012121 DCS HW1Naveen GuptaNoch keine Bewertungen

- AE05 SolDokument135 SeitenAE05 SolVipul MahajanNoch keine Bewertungen

- Event Poster Mathematica 10 - IIITDokument1 SeiteEvent Poster Mathematica 10 - IIITNaveen GuptaNoch keine Bewertungen

- Event Poster Mathematica 10 - IIITDokument1 SeiteEvent Poster Mathematica 10 - IIITNaveen GuptaNoch keine Bewertungen

- MSR Summer SchoolDokument12 SeitenMSR Summer SchoolNaveen GuptaNoch keine Bewertungen

- Mtech Student NIT Warangal ProjectDokument3 SeitenMtech Student NIT Warangal ProjectNaveen GuptaNoch keine Bewertungen

- Inner Product Space: Make A DonationDokument10 SeitenInner Product Space: Make A DonationNaveen GuptaNoch keine Bewertungen

- Ascent 30.4.14Dokument1 SeiteAscent 30.4.14Naveen GuptaNoch keine Bewertungen

- Basic Circuit Elements and Waveforms: Andrè-Marie AmpèreDokument5 SeitenBasic Circuit Elements and Waveforms: Andrè-Marie AmpèreNaveen GuptaNoch keine Bewertungen

- Friendship Iz A Language Spoken by HeartDokument1 SeiteFriendship Iz A Language Spoken by HeartNaveen GuptaNoch keine Bewertungen

- Form - Details of Ta Duty: (To Be Filled by PHD Students)Dokument1 SeiteForm - Details of Ta Duty: (To Be Filled by PHD Students)Naveen GuptaNoch keine Bewertungen

- Capacity Under Water CommunicationDokument10 SeitenCapacity Under Water CommunicationNaveen GuptaNoch keine Bewertungen

- Notified Mtech List II Sem NitwDokument2 SeitenNotified Mtech List II Sem NitwNaveen GuptaNoch keine Bewertungen

- IIITD Brochure 2012Dokument24 SeitenIIITD Brochure 2012Naveen GuptaNoch keine Bewertungen

- Resignation FormatDokument1 SeiteResignation FormatNaveen GuptaNoch keine Bewertungen

- Seminar M.tech. (ACS) IIIrd SemDokument2 SeitenSeminar M.tech. (ACS) IIIrd SemNaveen GuptaNoch keine Bewertungen

- Small Assignment Small AssignmentDokument1 SeiteSmall Assignment Small AssignmentNaveen GuptaNoch keine Bewertungen

- Shannon Limit For CodesDokument17 SeitenShannon Limit For CodesNaveen GuptaNoch keine Bewertungen

- Certificates Sachin 03Dokument3 SeitenCertificates Sachin 03Naveen GuptaNoch keine Bewertungen

- S Functions in Matlab R2013Dokument594 SeitenS Functions in Matlab R2013Naveen Gupta100% (1)

- An Introduction To The Kalman Filter - Greg Welch and Gary BishopDokument16 SeitenAn Introduction To The Kalman Filter - Greg Welch and Gary BishophemanthNoch keine Bewertungen

- CM8870Dokument9 SeitenCM8870Karthik KalyanaramanNoch keine Bewertungen

- Institute of Technology Mid Term 2013Dokument2 SeitenInstitute of Technology Mid Term 2013Naveen GuptaNoch keine Bewertungen

- Institute of Technology Mid TermDokument2 SeitenInstitute of Technology Mid TermNaveen GuptaNoch keine Bewertungen

- Antenna Based Thesis Mod2Dokument68 SeitenAntenna Based Thesis Mod2Naveen GuptaNoch keine Bewertungen

- Digital Optical Fibre - 2 Transmission & ReceptionDokument47 SeitenDigital Optical Fibre - 2 Transmission & ReceptionNaveen GuptaNoch keine Bewertungen

- Taichi DesignDokument166 SeitenTaichi DesignbulbtommyNoch keine Bewertungen

- Batch File TipsDokument6 SeitenBatch File TipsRashid AlsalamNoch keine Bewertungen

- Debug 1214Dokument5 SeitenDebug 1214Bayu Dibawan C-FamNoch keine Bewertungen

- Supermicro TwinServer 2027PR-HC1R - 8coreDokument1 SeiteSupermicro TwinServer 2027PR-HC1R - 8coreAndreas CimengNoch keine Bewertungen

- Shoregear t1k InstallDokument2 SeitenShoregear t1k InstallJoNoch keine Bewertungen

- LAB 5-PE-LabDokument7 SeitenLAB 5-PE-LabLovely JuttNoch keine Bewertungen

- Cisco MDS 9000 NX-OS Interface Config GuideDokument204 SeitenCisco MDS 9000 NX-OS Interface Config Guidewesmadison23Noch keine Bewertungen

- Jkol2305114715730 4715730Dokument2 SeitenJkol2305114715730 4715730raj VenkateshNoch keine Bewertungen

- Design and Development of A CubeSat Hardware Architecture With COTS MPSoC Using Radiation Mitigation TechniquesDokument71 SeitenDesign and Development of A CubeSat Hardware Architecture With COTS MPSoC Using Radiation Mitigation Techniqueslly1112002Noch keine Bewertungen

- Apphwid 1Dokument11 SeitenApphwid 1Briina S.Noch keine Bewertungen

- Tor Protocol Specification2Dokument5 SeitenTor Protocol Specification2AZERTYUIOPNoch keine Bewertungen

- Powerp 6.2 Release NotesDokument27 SeitenPowerp 6.2 Release Notesmnashish1979Noch keine Bewertungen

- ELM339 Infrared Remote Control: Description FeaturesDokument4 SeitenELM339 Infrared Remote Control: Description FeaturesYacine MARICHENoch keine Bewertungen

- 23200-Show Ver Output On Both FirewallsDokument2 Seiten23200-Show Ver Output On Both Firewallsjatinder bawaNoch keine Bewertungen

- Ujjawal Khare SDEDokument2 SeitenUjjawal Khare SDEUjjawal KhareNoch keine Bewertungen

- Python Classes and ObjectsDokument58 SeitenPython Classes and ObjectsVitor Matheus100% (1)

- BYW77P/PI-200: High Efficiency Fast Recovery Rectifier DiodesDokument6 SeitenBYW77P/PI-200: High Efficiency Fast Recovery Rectifier DiodesGianmarco CastilloNoch keine Bewertungen

- Computer ScienceDokument130 SeitenComputer ScienceMallesh GujjarNoch keine Bewertungen

- Catalogue RFDokument313 SeitenCatalogue RFJojonNoch keine Bewertungen

- Quiz SystemDokument28 SeitenQuiz Systemmervinjones33% (6)

- Switches PDFDokument144 SeitenSwitches PDFtomy_223825000Noch keine Bewertungen

- VOCATIONAL TRAINING ON Flight Reservation APPLICATION PROGRAMMINGDokument71 SeitenVOCATIONAL TRAINING ON Flight Reservation APPLICATION PROGRAMMINGDashmesh SinghNoch keine Bewertungen

- Global Line Series - Santak C1-3KVADokument3 SeitenGlobal Line Series - Santak C1-3KVAJiNoch keine Bewertungen

- Dfs I Fusion v3 I Sep '22Dokument8 SeitenDfs I Fusion v3 I Sep '22Achref MmaNoch keine Bewertungen

- InterM 2010 AUDIO CatalogueDokument111 SeitenInterM 2010 AUDIO CatalogueRadio PartsNoch keine Bewertungen

- Python Training TutorialsDokument40 SeitenPython Training TutorialsSyedNoch keine Bewertungen

- ENSA v7 Module & Final Exam Design DocumentsDokument4 SeitenENSA v7 Module & Final Exam Design DocumentsCCNA 200-301Noch keine Bewertungen

- Junglepax Evolution Module Brochure en 33159 202012Dokument2 SeitenJunglepax Evolution Module Brochure en 33159 202012Roni Pardamean SijabatNoch keine Bewertungen

- Oop Midterm - AnswersDokument4 SeitenOop Midterm - AnswersNur KalkanNoch keine Bewertungen