Beruflich Dokumente

Kultur Dokumente

Fan 7316

Hochgeladen von

sontuyet82Originalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Fan 7316

Hochgeladen von

sontuyet82Copyright:

Verfügbare Formate

April 2011

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

FAN7316

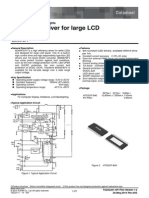

LCD Backlight Inverter Drive IC

Features

High-Efficiency Single-Stage Power Conversion

Wide Input Voltage Range: 4.5V to 24V

Backlight Lamp Ballast and Soft Dimming

Reduces Required External Components

Precision Voltage Reference Trimmed to 2%

N-N Half-Bridge Topology

PWM Control at Fixed Frequency

Analog and Burst Dimming Function

Selectable Burst Dimming Polarity by ADIM Voltage

Striking Frequency Depending on Normal Frequency

Open-Lamp Protection

Open-Lamp Regulation

Short-Circuit Protection

20-Pin SOIC

Applications

LCD TV

LCD Monitor

Description

The FAN7316 is a LCD backlight inverter drive IC that

controls N-N half-bridge topology. The FAN7316 can also

drive push-pull topology.

The FAN7316 provides a low-cost solution by integrating

the external open-lamp protection circuit. The operating

voltage of the FAN7316 is wide, so the FAN7316 doesnt

need an external regulator to supply the voltage to the IC.

The FAN7316 has the internal bootstrap driver, so the

external fast recovery diode can be avoided.

The FAN7316 provides various protections, such as

open-lamp regulation, arc protection, open-lamp

protection, short-circuit protection, and CMP-high

protection to increase the system reliability. The

FAN7316 provides analog dimming, burst dimming, and

burst dimming polarity selection functions.

The FAN7316 is available in a 20-SOIC package.

Ordering Information

Part Number Package Operating Temperature Packing Method

FAN7316MX 20-SOIC -25 to +85C TAPE & REEL

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 2

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

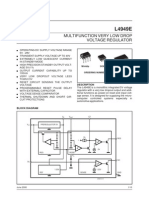

Block Diagram

Figure 1. Internal Block Diagram

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 3

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Pin Assignments

F : Fairchild logo

P : Assembly site code

XY : Year & weekly code

TT : Die run code

FAN7316 : Device name

F PXYTT

FAN7316

1 2 3 4 5 6 7 8

20 19 18 17 16 15 14 13

V

R

E

F

B

D

I

M

O

L

P

1

O

U

T

H

V

B

B

C

T

/

F

T

O

L

P

4

R

T

C

M

P

E

N

A

F

B

O

L

P

2

G

N

D

9 10

12 11

A

D

I

M

V

I

N

O

L

R

O

L

P

3

O

U

T

L

S

C

P

V

S

Figure 2. Package Diagram

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 4

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Pin Definitions

Pin # Name Description

1 OLP1 This pin is for open-lamp protection. If OLP is lower than 1.5V at initial operation, the IC

operates at striking mode for BCT 450 cycles. If OLP is lower than 1.5V in normal mode, the

IC is shut down after a delay of three BCT cycles. 2 OLP2

3 CMP

Error amplifier output. A compensation capacitor should be connected between this pin and

ground.

4 FB Error amplifier inverting input. This pin voltage is regulated at 2V or ADIM voltage.

5 BDIM

This pin is for burst dimming input. The voltage range of 0.5 to 2V at this pin controls burst

mode duty cycle from 0% to 100%.

6 ADIM

This pin is for positive analog dimming input. This voltage to 2V at this pin controls the

amplitude of the lamp current.

7 ENA This pin is for turning on/off the IC.

8 GND Ground.

9 OUTL

Low-side driver output. The output stage can deliver about 500mA source and sink current,

typically.

10 VREF 6V reference voltage.

11 VIN IC supply voltage.

12 VB

High-side floating supply. The bootstrap capacitor should be connected between this pin and

VS pin, which can be fed by an internal bootstrap MOSFET.

13 OUTH

High-side driver output. The output stage can deliver about 500mA source and sink current,

typically.

14 VS

High-side floating supply return. Layout care should be taken to avoid below-ground spikes

on this pin.

15 SCP

This pin is for short-circuit protection. If SCP is higher than 2V, IC enters shutdown mode

after a delay of 32 BCT cycles.

16 RT

This pin programs the switching frequency. The resistor should be connected between this

pin and ground.

17 BCT/FT

This pin programs the burst dimming frequency. A capacitor should be connected between

this pin and ground. The waveform of this pin is the triangular waveform whose amplitude is

from 0.5V to 2V. This pin voltage goes up to 4V when the IC enters shutdown mode.

18 OLR

This pin is for open-lamp regulation. If the voltage at OLR reaches 2V, the IC makes this pin

voltage be controlled not to exceed 2V. If OLR voltage is higher than 1.75V, the IC enters

shutdown mode after delays of 451 BCT cycles in striking mode and three BCT cycles in

normal mode, respectively. If this pin voltage is higher than 3V, the IC enters shutdown mode

without delay.

19 OLP4 This pin is for open lamp protection. If OLP is lower than 1.5V at initial operation, the IC

operates at striking mode for BCT 450 cycles. If OLP is lower than 1.5V in normal mode, the

IC is shut down after a delay of three BCT cycles. 20 OLP3

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 5

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In

addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The

absolute maximum ratings are stress ratings only.

Symbol Parameter Min. Max. Unit

V

IN

IC Supply Voltage 4.5 24 V

V

B

High-Side Floating Supply -0.3 33 V

V

S

High-Side Floating Supply Return -2

(3)

V

B

-7 V

T

J

Operating Junction Temperature -40 +150 C

T

STG

Storage Temperature Range -65 +150 C

JA

Thermal Resistance Junction-Air

(1,2)

90 C /W

P

D

Power Dissipation 1.4 W

Notes:

1. Thermal resistance test board. Size: 76.2mm x 114.3mm x 1.6mm (1S0P); JEDEC standard: JESD51-2, JESD51-3.

2. Assume no ambient airflow.

Recommended Operating Ratings

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to absolute maximum ratings.

Symbol Parameter Min. Max. Unit

V

IN

IC Supply Voltage 4.5 22.0 V

V

B

High-Side Floating Supply V

S

-0.3 V

S

+6.5 V

V

S

High-Side Floating Supply Return

(3)

25 V

T

A

Operating Ambient Temperature -25 +85 C

Notes:

3. The V

S

is tolerant to short negative transient spikes.

Pin Breakdown Voltage

Pin # Name Value Unit Pin # Name Value Unit

1 OLP1 7

V

11 VIN 24

V

2 OLP2 7 12 VB 33

3 CMP 7 13 OUTH 7

4 FB 7 14 VS 33

5 BDIM 7 15 SCP 7

6 ADIM 7 16 RT 7

7 ENA 7 17 BCT/FT 7

8 GND 18 OLR 7

9 OUTL 7 19 OLP4 7

10 VREF 7 20 OLP3 7

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 6

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Electrical Characteristics

For typical values, T

A

=25C, V

IN

=18V, and -25C s T

A

s 85C, unless otherwise specified. Specifications to -25C ~

85C are guaranteed by design based on final characterization results.

Symbol Parameter Test Condition Min. Typ. Max. Unit

V

REF

Section (Recommend X7R Capacitor)

V

6

6V Regulation Voltage CMP=0V 5.76 6.00 6.24 V

V

6line

6V Line Regulation V

IN

=7V, 18V 25 mV

V

6load

6V Load Regulation 10As16s5mA 60 mV

Oscillator Section (Main)

V

fbth

FB Threshold Voltage ADIM=1, OLP=0V 0.45 V

V

cth

CT High Voltage

(4)

2.0 V

V

ctl

CT Low Voltage

(4)

0.5 V

Oscillator Section (Burst)

f

oscb

Oscillation Frequency

T

A

=25C, BCT=10nF 288 300 312 Hz

BCT=10nF 282 300 318 Hz

V

bcth

BCT High Voltage BCT=10nF 2 V

V

bctl

BCT Low Voltage BCT=10nF 0.5 V

V

bctft

BCT Fault Voltage SCP=2.5V 4 V

Error Amplifier Section

G

m1

Error Amplifier Trans-conductance CMP=1, ADIM=1V 100 360 600 umho

A

V

Error Amplifier Open-loop Gain

(4)

50 dB

V2 2V Regulation Voltage

T

A

=25C, ADIM=2.5V 1.97 2.00 2.03 V

260 ppm/C

l

sin

CMP Sink Current ADIM=1V, FB=2.5V 66 100 134 A

l

sur1

CMP Source Current 1 CMP=1V, FB=0V -134 -100 -66 A

I

sur2

CMP Source Current 2 1.75V<OLR<2V

1.6 A

I

sur3

CMP Source Current 3

(4)

OLR>2V 0 A

Under-Voltage Lockout Section (UVLO)

V

th

Start Threshold Voltage ENA=2.5V 3.9 4.2 4.5 V

V

thhys

Start Threshold Voltage Hysteresis ENA=2.5V 0.2 0.4 0.6 V

I

st

Start-up Current V

IN

=V

th

-0.2 20 60 150 A

I

op

Operating Supply Current Not switching 1.5 2.0 mA

ENA Section

V

ena

Enable State Input Voltage 2 5 V

V

dis

Disable Stage Input Voltage 0.7 V

I

sb

Stand-by Current ENA=0 100 150 A

Note:

4. These parameters, although guaranteed, are not 100% tested in production.

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 7

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Electrical Characteristics (Continued)

For typical values, T

A

=25C, V

IN

=18V, and -25C s T

A

s 85C, unless otherwise specified. Specifications to -25C ~

85C are guaranteed by design based on final characterization results.

Symbol Parameter Test Condition Min. Typ. Max. Unit

Protection Section

V

scp

Short-Circuit Protection Voltage 1.9 2.0 2.1 V

V

cmpr

CMP Protection Voltage 2.8 3.0 3.2 V

V

olp

Open-Lamp Protection Voltage 1.4 1.5 1.6 V

V

ovp

Over-Voltage Protection 2.85 3.00 3.15 V

V

olr1

Open-Lamp Regulation Voltage 1 1.60 1.75 1.90 V

V

olr2

Open-Lamp Regulation Voltage 2 1.9 2.0 2.1 V

V

olrhy

Open-Lamp Regulation Hysteresis

(5)

250 mV

t

scp

Short-Circuit Protection Delay

(5)

Striking, f

oscb

=300Hz 1.4 1.5 1.6 s

Normal, f

oscb

=300Hz 80 100 120 ms

t

cmp

CMP Protection Delay

(5)

Striking, f

oscb

=300Hz 1.4 1.5 1.6 s

Normal, f

oscb

=300Hz 80 100 120 ms

t

olp

Open-Lamp Protection Delay

(5)

Striking, f

oscb

=300Hz 1.4 1.5 1.6 s

Normal, f

oscb

=300Hz 6 10 ms

t

olr

Open-Lamp Regulation Delay

(5)

Striking, f

oscb

=300Hz 1.4 1.5 1.6 s

Normal, f

oscb

=300Hz 80 100 120 ms

TSD Thermal Shutdown

(5)

150 C

Output Section

f

nrmo

Output Normal Frequency

T

A

=25C, R

T

=27kO 47.4 49.0 50.6

kHz

R

T

=27kO 47 49 51

f

str

Output Striking Frequency

T

A

=25C, R

T

=27kO 61.5 64.0 66.4

kHz

R

T

=27kO 61 64 67

V

ouvh

OUTH Voltage Before Start-up V

IN

=V

th

-0.6 -0.45 0 0.45 V

V

ouvl

OUTL Voltage Before Start-up V

IN

=V

th

-0.6 -0.45 0 0.45 V

V

osth

High-Side Output Voltage at V

ENA

=0V V

IN

=18V -0.45 0 0.45 V

V

ost

Low-Side Output Voltage at V

ENA

=0V V

IN

=18V -0.45 0 0.45 V

V

ohh

High-Side Output Voltage V

IN

=18V 5.5 6.0 6.5 V

V

ohl

Low-Side Output Voltage V

IN

=18V 5.5 6.0 6.5 V

I

dsurh

High-Side Output Drive Source Current

(5)

V

IN

=18V 500 mA

I

dsinh

High-Side Output Drive Sink Current

(5)

V

IN

=18V 500 mA

I

dsurl

Low-Side Output Drive Source Current

(5)

V

IN

=18V 500 mA

I

dsinl

Low-Side Output Drive Sink Current

(5)

V

IN

=18V 500 mA

t

dead

Dead Time

(5)

500 ns

Note:

5. These parameters, although guaranteed, are not 100% tested in production.

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 8

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Typical Performance Characteristics

Figure 3. Start Threshold Voltage vs. Temp. Figure 4. Start Threshold Voltage Hys. vs. Temp.

Figure 5. Start-up Current vs. Temp. Figure 6. Standby Current vs. Temp.

Figure 7. Operating Frequency vs. Temp. Figure 8. Striking Frequency vs. Temp.

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 9

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Typical Performance Characteristics (Continued)

Figure 9. Burst Dimming Frequency vs. Temp. Figure 10. V

REF

Voltage vs. Temp.

Figure 11. V

REF

Line Regulation Voltage vs. Temp. Figure 12. V

REF

Load Regulation Voltage vs. Temp.

Figure 13. CMP Sink Current vs. Temp. Figure 14. CMP Source Current 1 vs. Temp.

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 10

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Typical Performance Characteristics (Continued)

Figure 15. CMP Source Current 2 vs. Temp. Figure 16. Operating Current vs. Temp.

Figure 17. Error Amplifier 2V Voltage vs. Temp. Figure 18. Open-Lamp Protection Voltage vs. Temp.

Figure 19. Open-Lamp Regulation Voltage 2 vs. Temp. Figure 20. Over-Voltage Protection vs. Temp.

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 11

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Typical Performance Characteristics (Continued)

Figure 21. Short-Circuit Protection Voltage vs. Temp. Figure 22. High-Side Output Voltage vs. Temp.

Figure 23. Low-Side Output Voltage vs. Temp.

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 12

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Functional Description

UVLO: The under-voltage lockout (UVLO) circuit

guarantees the stable operation of the ICs control circuit

by stopping and starting it as a function of the V

IN

value.

The UVLO circuit turns on the control circuit when V

IN

exceeds 4.5V. When V

IN

is lower than 3.9V, the ICs start-

up current is less than 150A.

ENA: Applying voltage higher than 2V to the ENA pin

enables the IC. Applying voltage lower than 0.7V to the

ENA pin disables the IC.

Internal Main Oscillator: The internal timing capacitor

(CT), 20pF, is charged by the reference current source,

which is formed by the timing resistor (RT). The RT

voltage is regulated at 1.728V. The sawtooth waveform

charges up to 2V. Once CT voltage is reached, the CT

begins discharging down to 0.5V. Next, the CT starts

charging again and a new switching cycle begins, as

shown in Figure 24. The main frequency is programmed

by adjusting the R

T

value. The main frequency is

calculated as:

] KHz [

] K [ R

2736

f

T

OSC

O

~ (1)

2V

0.5V

+

-

Ich

+

-

Idch

tch

tdch

20pF

1.728V

S

R

Q

Q

IRT

+

-

IRT/20

IRT

RT

Figure 24. Main Oscillator Circuit

The striking frequency is 1.3 times as high as the main

frequency.

Burst Dimming Oscillator: The burst capacitor timing

(BCT) is charged by the internal reference current

source. The triangular waveform charges up to 2V. Once

the BCT voltage is reached, the capacitor begins

discharging down to 0.5V. Next, the BCT starts charging

again and a new switching cycle begins, as shown in

Figure 25. The burst dimming frequency is programmed

by adjusting BCT value. The burst dimming frequency is

calculated as:

] Hz [

] nF [ BCT

10 3

f

3

OSCB

-

~ (2)

To avoid visible flicker, the burst dimming frequency

should be greater than 120Hz.

2V

0.5V

+

-

I

ch

+

-

Idch

S

R

Q

Q

9A

18A

BCT

t ch tdch

Figure 25. Burst Dimming Oscillator Circuit

Analog Dimming: There are two kinds of analog

dimming polarity: positive analog dimming and negative

analog dimming.

For positive analog dimming, the lamp intensity is

controlled with the ADIM signal. The lamp intensity is

proportional to ADIM signal; as ADIM voltage increases,

the lamp intensity increases. Figure 26 shows how to

implement negative analog dimming circuit and Figure 27

shows the lamp current waveform vs. DIM in positive

analog dimming mode.

Figure 26. Positive Analog Implementation Circuit

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 13

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Figure 27. Positive Analog Dimming Waveform

For negative analog dimming, the lamp intensity is

controlled with the external DIM signal and the resistors.

The lamp intensity is inversely proportional to DIM

voltage. As DIM voltage increases, the lamp intensity

decreases. Figure 28 shows how to implement a negative

analog dimming circuit and Figure 29 shows the lamp

current waveform vs. DIM in negative analog dimming

mode.

Figure 28. Negative Analog Implementation Circuit

Figure 29. Negative Analog Dimming Waveform

Burst Dimming Polarity Selection: FAN7316 provides

the function to select burst dimming polarity by ADIM pin

voltages. If ADIM pin voltage is lower than 3V, positive

burst dimming is chosen. Refer to Figure 30.

OUTL

Lamp

current

BCT

OUTH

2V

0.5V

0V

6V

6V

BDIM

Positive dimming polarity

ADIM

3.0V

Figure 30. Positive Burst Dimming Chosen

If the ADIM pin voltage is higher than 3.5V, negative

dimming polarity is chosen. Refer to Figure 31.

Figure 31. Negative Burst Dimming Chosen

Burst Dimming: There are also two kinds of burst

dimming polarity: positive analog dimming and negative

analog dimming. The lamp intensity is controlled with the

BDIM voltage. By comparing the BDIM voltage with the

0.5~2V triangular waveform of burst dimming oscillator

(BCT), the PWM pulse is generated. The PWM pulse

controls the CMP voltage by discharging and charging

the CMP capacitor.

For positive burst dimming, when BDIM voltage is higher

than BCT voltage, the lamp current is turned on. So, 2V

on BDIM commands full brightness. The duty cycle of the

PWM pulse determines the lamp brightness. The lamp

intensity is proportional to BDIM voltage. As BDIM

voltage increases, the lamp intensity also increases.

Figure 32 shows the lamp current waveform vs. DIM in

positive analog dimming mode.

Figure 32. Positive Burst Dimming Operation

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 14

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

For negative burst dimming, when BDIM voltage is lower

than BCT voltage, the lamp current is turned on. So, 0V

on BDIM commands full brightness. The duty cycle of the

PWM pulse determines the lamp brightness. The lamp

intensity is inversely proportional to BDIM voltage. As

BDIM voltage increases, the lamp intensity decreases.

Figure 32 shows the lamp current waveform vs. DIM in

negative analog dimming mode.

Figure 33. Positive Burst Dimming Operation

Burst dimming can be implemented by not only DC

voltage, also PWM pulse as BDIM signal. Figure 34

shows how to implement burst dimming by using PWM

pulse as BDIM signal.

+

-

Burst Si gnal

to Error Ampl i fi er

External

Pul se Si gnal

Comparator

2V

0.5V

+

-

Ich

+

-

I

dch

S

R

Q

Q

9A

18A

BCT

t ch tdch

BDIM

Figure 34. Burst Dimming Using an External Pulse

During striking mode, burst dimming operation is disabled

to guarantee the continuous striking time. Figure 35

shows that burst dimming is disabled during striking

mode.

OUTL

OLP

BCT

OUTH

2V

0.5V

1.5V

6V

6V

Lamp isn t ignited

BDIM

Burst dimming disable Burst dimming enable

Negative dimming polarity

Lamp is ignited

Figure 35. Burst Dimming During Striking Mode

Output Drives: FAN7316 is designed to drive high-side

and low-side MOSFETs with symmetrical duty cycle. A

fixed dead time of 500ns is introduced between two

outputs at maximum duty cycle, as shown Figure 36.

CT

CLOCK

OUTH

OUTL

CMP

T

Fixed dead time

500 ns

Fixed dead time

500 ns

Figure 36. MOSFETs Gate Drive Signal

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 15

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Bootstrap Operation: To choose the proper C

BS

value,

the external MOSFET can be seen as an equivalent

capacitor. This capacitor, C

IN

, is related to the MOSFET

total gate charge as:

GATE

GATE

IN

V

Q

C = (3)

The ratio between capacitors C

IN

and C

BS

is proportional

to the cyclical voltage loss:

IN BS

C C >> (4)

For example: if Q

GATE

is 24nC and V

GATE

is 10V, C

IN

is

2.4nF. With C

BS

=100nF, the drop is 240mV.

The bootstrap driver introduces a voltage drop due to

MOSFET R

DSON

(typical value: 100O). The following

equation is useful to compute the voltage drop on the

bootstrap MOSFET:

DSON

CHARGE

GATE

DROP DSON CHARGE DROP

R

T

Q

V R I V - = - = (5)

where Q

GATE

is the gate charge of the external MOSFET,

R

DSON

is the on resistance of the bootstrap MOSFET, and

T

CHARGE

is the charging time of the bootstrap capacitor.

For example: If Q

GATE

is 24nC and T

CHARGE

is 10s, the

drop on the bootstrap MOSFET is about 0.24V.

V 24 . 0 100

s 10

nC 24

V

DROP

= O - = (6)

Protections: The FAN7316 has several protections:

Open-Lamp Regulation (OLR), Arc Protection, Open-

Lamp Protection (OLP), Short-Circuit Protection (SCP),

CMP-High Protection, and Thermal Shutdown (TSD). All

protections are latch-mode protections. The latch is reset

when V

IN

falls to the UVLO voltage or ENA is pulled down

to GND.

Open-Lamp Regulation: When a voltage higher than 2V

is applied to the OLR pin, the IC enters regulation mode

and controls CMP voltage. The IC limits the lamp voltage

by decreasing CMP source current. If the OLR voltage is

higher than 1.75V, CMP source current decreases from

100A to 1.6A. If the OLR voltage reaches at 2V, CMP

source current decreases to 0A, so CMP voltage

remains constant and the lamp voltage also remains

constant, as shown in Figure 37. At the same time, the

counter based on BCT time starts counting 450 cycles

and 32 cycles at striking mode and normal mode,

respectively, then the IC enters shutdown, as shown in

Figure 38 and Figure 39.

Figure 37. Open-Lamp Regulation in Striking Mode

Figure 38. Open-Lamp Regulation in Striking Mode

Figure 39. Open-Lamp Regulation in Normal Mode

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 16

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Arc Protection: If OLR voltage is higher than 3V, the IC

enters shutdown mode after a delay of two CT cycles, as

shown in Figure 40.

OUTL

CT

OUTH

2V

0.5V

2 cycles

6V

6V

OLR 3V

Shutdown

Figure 40. Arc Protection

Open-Lamp Protection: If OLP is lower than 1.5V at

initial operation, the IC operates at striking mode for BCT

450 cycles, as shown in Figure 41. If OLP is lower than

1.5V at normal mode, the IC is shut down after a delay of

three BCT cycles, as shown in Figure 42.

OUTL

OLP

BCT

OUTH

4V

2V

0.5V

1.5V

450 cycles

6V

6V

BCT=300Hz Striking time=1.5s

Lamp isnt ignited

Open lamp @ striking mode

Shutdown

Figure 41. Open-Lamp Protection in Striking Mode

OUTL

OLP

BCT

OUTH

4V

2V

0.5V

1.5V

3 cycles

6V

6V

OLP time=6.67~10ms

@ BCT=300Hz

Lamp open

Shutdown

Figure 42. Open-Lamp Protection in Normal Mode

Short-Circuit Protection: If SCP is higher than 2V, the

counter based on BCT time starts counting 450 cycles

and 32 cycles at striking mode and normal mode,

respectively, then the IC enters shutdown, as shown in

Figure 43 and Figure 44.

OUTL

OLP

BCT

OUTH

4V

2V

0.5V

1.5V

450 cycles

6V

6V

Striking time=1.5s @ BCT=300Hz

Lamp isnt ignited

SCP

2V

Shutdown

Figure 43. Short-Circuit Protection in Striking Mode

OLP

1.5V

32 cycles

6V

6V

Lamp is ignited

SCP

2V

Shutdown

BCT

4V

2V

0.5V

Protection Delay 100ms @ BCT=300Hz

Figure 44. Short-Circuit Protection in Normal Mode

CMP-High Protection: If CMP is higher than 3V, the

counter based on BCT time starts counting 450 cycles

and 32 cycles at striking mode and normal mode,

respectively, then the IC enters shutdown, as shown in

Figure 45 and Figure 46.

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 17

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

CMP-High Protection: If CMP is higher than 3V, the

counter based on BCT time starts counting 450 cycles

and 32 cycles at striking mode and normal mode,

respectively, then the IC enters shutdown, as shown in

Figure 45 and Figure 46.

OUTL

OLP

BCT

OUTH

4V

2V

0.5V

1.5V

450 cycles

6V

6V

Striking time=1.5s @ BCT=300Hz

Lamp isnt ignited

CMP

3V

Shutdown

Figure 45. CMP-High Protection in Striking Mode

Figure 46. CMP-High Protection in Normal Mode

Thermal Shutdown: The IC provides the function to

detect the abnormal over-temperature. If the IC

temperature exceeds approximately 150C, the thermal

shutdown triggers.

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 18

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

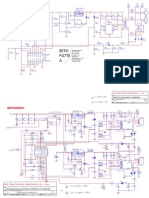

Typical Application Circuit (LCD Backlight Inverter)

Application Device Input Voltage Range Number of Lamps

19-Inch LCD Monitor FAN7316 14.510% 4

1. Features

High-Efficiency Single-Stage Power Conversion

N-N Half-Bridge Topology

Reduces Required External Components

Enhanced System Reliability through Protection Functions

OLP4

R6

680

D4

BAV70

R7

680

0

SN1

GN1

DN1

DN1

GN2

SN2 DN2

DN2

M1

AOP800

0

C9

3p

0

C11

2.7n

0

0

TX1

C14

0.1u

0

C7 10u

C6

1u

C2

1u

0

C17

10n

R30

10R

R29

0

1

1

2

2

CN2

35001WR-02A

1

1

2

2

CN1

35001WR-02A

1

1

2

2

CN3

35001WR-02A

1

1

2

2

CN4

35001WR-02A

C1

330u

OLR

R31

10R

O

L

P

1

O

L

P

2

C

M

P

F

B

B

D

I

M

A

D

I

M

E

N

A

G

N

D

O

U

T

L

V

R

E

F

V

I

N

V

B

O

U

T

H

V

S

S

C

P

R

T

B

C

T

O

L

R

O

L

P

4

O

L

P

3

FAN7316

IC1

REF

0

R18

100k

0

R28

20k

D3

BAV70

D5

BAV70

OLP1 OLP2

OLP3 OLP4

R14

10k

R15

10k

R4

10k

R5

10k

0 0

0 0

F1

FUSE

C4 10u

1

2

3

4

5

6

7

8

9

10

CN5

12505WR-10

R20

10k

R21

20k

C8

3p

C10

2.7n

C15

3p

C18

2.7n

R2

100k

R3

100k

0

0

R9

100k

R8

100k R25

N.C.

R13

100k

C13

1u

C12

33n

0

0

R24

0R

C19

2.7n

C3

1u

0

0

R17

680

0

TX2

0

C16

3p

0

OLP2 OLP1

R16

680

R22

0R

OLR

15V

R23

N.C.

R19

10k

0

LTM190EX

C23

N.C.

ON/OFF

DIM(0~3.3V)

C20

1n

0

C21

4.7n

0

R27

10k

0

0

0

0

R12

75k

R11

9.1k

R10

12k

C5

10n

R1

30k

0

0 0 0

D2

BAV70

OLP3

0

Figure 47. Typical Application Circuit

2. Transformer Schematic Diagram

Figure 48. Transformer Schematic Diagram

3. Core & Bobbin

Core: EFD2126

Material: PL7

Bobbin: EFD2126

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 19

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

4. Winding Specification

Pin No. Wire Turns Inductance Leakage Inductance Remarks

5 2 1 UEW 0.45| 12 94H 9.1H 1kHz, 1V

7 9 1 UEW 0.04| 2560(=0+3607) 3.88H 420mH 1kHz, 1V

5. BOM of the Application Circuit

Part Ref. Value Description Part Ref. Value Description

Fuse C5 10nF 50V 1608 K

F1 24V 3A FUSE C6 1F 50V 2012 K

Resistor (SMD) C7 10F 16V 3216

R1 30k 1608 F C10 2.7nF 50V 1608 K

R2 100k 1608 J C11 2.7nF 50V 1608 K

R3 100k 1608 J C12 33nF 50V 1608 K

R4 10k 1608 F C13 1F 50V 3216 K

R5 10k 1608 F C14 10nF 50V 1608 K

R6 680 1608 F C17 10nF 50V 1608 K

R7 680 1608 F C18 2.7nF 50V 1608 K

R8 100k 1608 J C19 2.7nF 50V 1608 K

R9 100k 1608 J C20 1nF 50V 1608 K

R10 12k 1608 F C21 4.7nF 50V 1608 K

R11 9.1k 1608 F C23 NC

R12 75k 1608 F Capacitor (DIP)

R13 100k 1608 J C8 3p 3KV

R14 10k 1608 F C9 3p 3KV

R15 10k 1608 F C15 3p 3KV

R16 680 1608 F C16 3p 3KV

R17 680 1608 F Diode (SMD)

R18 100k 1608 F D2 BAV70 Fairchild Semiconductor

R19 10k 1608 F D3 BAV70 Fairchild Semiconductor

R20 10k 1608 J D4 BAV70 Fairchild Semiconductor

R21 20k 1608 F D5 BAV70 Fairchild Semiconductor

R22 0 Electrolytic capacitor

R23 NC C1 330 25V

R24 0 MOSFET (SMD)

R25 NC M1 AOP800 Alpha & Omega

R27 10k 1608 F Wafer (SMD)

R28 20k 1608 F CN1 35001WR-02A

R29 0 CN2 35001WR-02A

R30 10 1608 J CN3 35001WR-02A

R31 10 1608 J CN4 35001WR-02A

Capacitor (SMD) CN5 12505WR-10

C2 1F 50V 3216 K Transformer (DIP)

C3 1F 50V 3216 K TX1 EFD2126

C4 10F 16V 3216 TX2 EFD2126

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 20

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Physical Dimensions

0.10 C

C

A

SEE DETAIL A

NOTES: UNLESS OTHERWISE SPECIFIED

A) THIS PACKAGE CONFORMS TO JEDEC

MS-013, VARIATION AC, ISSUE E

B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS DO NOT INCLUDE MOLD

FLASH OR BURRS.

E) LANDPATTERN STANDARD: SOIC127P1030X265-20L

PIN ONE

INDICATOR

0.25

1 10

B C A M

20 11

B

X 45

8

0

SEATING PLANE

GAGE PLANE

DETAIL A

SCALE: 2:1

SEATING PLANE

LAND PATTERN RECOMMENDATION

F) DRAWING FILENAME: MKT-M20BREV3

0.65

1.27

2.25

9.50

13.00

12.60

11.43

7.60

7.40

10.65

10.00

0.51

0.35

1.27

2.65 MAX

0.30

0.10

0.33

0.20

0.75

0.25

(R0.10)

(R0.10)

1.27

0.40

(1.40)

0.25

D) CONFORMS TO ASME Y14.5M-1994

Figure 49. 20-SOIC Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchilds worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductors online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7316 1.0.2 21

F

A

N

7

3

1

6

L

C

D

B

a

c

k

l

i

g

h

t

I

n

v

e

r

t

e

r

D

r

i

v

e

I

C

Das könnte Ihnen auch gefallen

- Apl 5336Dokument20 SeitenApl 5336FlavianoSilvaNoch keine Bewertungen

- FAN7602B Green Current-Mode PWM Controller: Features DescriptionDokument17 SeitenFAN7602B Green Current-Mode PWM Controller: Features DescriptionNichole RollinsNoch keine Bewertungen

- Fan 7317Dokument23 SeitenFan 7317Graciela Judith Dacto ChNoch keine Bewertungen

- EN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated InductorDokument16 SeitenEN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated Inductorcatsoithahuong84Noch keine Bewertungen

- Fan 7313Dokument11 SeitenFan 7313KathafiNoch keine Bewertungen

- LM25005 42V, 2.5A Step-Down Switching Regulator: Literature Number: SNVS411BDokument24 SeitenLM25005 42V, 2.5A Step-Down Switching Regulator: Literature Number: SNVS411BPravin MevadaNoch keine Bewertungen

- Fan 7314Dokument14 SeitenFan 7314Kamal NonekNoch keine Bewertungen

- IC 3842 para FonteDokument8 SeitenIC 3842 para FonteTomNedscNoch keine Bewertungen

- CCFL Inverter IC OZ960Dokument12 SeitenCCFL Inverter IC OZ960davesworkshopNoch keine Bewertungen

- FAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorDokument17 SeitenFAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorVijay MistryNoch keine Bewertungen

- 3842 Ic DatasheetDokument13 Seiten3842 Ic DatasheetEngr Khalid IqbalNoch keine Bewertungen

- Fan 7530Dokument20 SeitenFan 7530aldo_suviNoch keine Bewertungen

- Intelligent CCFL Inverter Controller: FeaturesDokument12 SeitenIntelligent CCFL Inverter Controller: FeaturesMirosław DżumakNoch keine Bewertungen

- LV47002PDokument9 SeitenLV47002PchichedemorenoNoch keine Bewertungen

- L6565Dokument18 SeitenL6565Sergio Daniel BarretoNoch keine Bewertungen

- Green Mode PWM Controller Ap384XgDokument13 SeitenGreen Mode PWM Controller Ap384XgbaphometabaddonNoch keine Bewertungen

- Datasheet PDFDokument11 SeitenDatasheet PDFIdelbrando RochaNoch keine Bewertungen

- L4949Dokument11 SeitenL4949Николай КръстевNoch keine Bewertungen

- Datasheet AP1513Dokument7 SeitenDatasheet AP1513timigoNoch keine Bewertungen

- Data SheetDokument7 SeitenData Sheetitamar_123Noch keine Bewertungen

- LM2852 Synchronous BuckDokument14 SeitenLM2852 Synchronous BuckAndrew CavanaughNoch keine Bewertungen

- PS223Dokument11 SeitenPS223seyyedali2006Noch keine Bewertungen

- PD Derated at 8.5mW/ For Temperature Above Ta 25 (When Mounted On A PCB 70.0mm×70.0mm×1.6mm)Dokument5 SeitenPD Derated at 8.5mW/ For Temperature Above Ta 25 (When Mounted On A PCB 70.0mm×70.0mm×1.6mm)Osama YaseenNoch keine Bewertungen

- IC-ON-LINE - CN dm0365r 44840Dokument20 SeitenIC-ON-LINE - CN dm0365r 44840MoscandoNoch keine Bewertungen

- La 42205Dokument7 SeitenLa 42205ban4444Noch keine Bewertungen

- Viper 100Dokument8 SeitenViper 100SeanNoch keine Bewertungen

- Imprimir Datasheet 1Dokument14 SeitenImprimir Datasheet 1Randy Siancas VelezNoch keine Bewertungen

- IC-ON-LINE - CN dm0465r 44841Dokument20 SeitenIC-ON-LINE - CN dm0465r 44841ubhagavanNoch keine Bewertungen

- La 42102Dokument8 SeitenLa 42102buyadiNoch keine Bewertungen

- Feature General Description: HT7A6005 Low Power, Wide Temperature Range General Purpose Current Mode PWM ControllerDokument11 SeitenFeature General Description: HT7A6005 Low Power, Wide Temperature Range General Purpose Current Mode PWM ControllerEnéas BaroneNoch keine Bewertungen

- Bd9397efv e PDFDokument30 SeitenBd9397efv e PDFshafiuddin7326Noch keine Bewertungen

- Uc 3845Dokument23 SeitenUc 3845Bahram RN100% (1)

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDokument10 SeitenNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNoch keine Bewertungen

- Fan7340 Slc1012c PWM Backlight Samsung 32Dokument16 SeitenFan7340 Slc1012c PWM Backlight Samsung 32Andres Alegria50% (4)

- Datasheet LM3429Dokument34 SeitenDatasheet LM3429Bagus KrisviandikNoch keine Bewertungen

- Fan 6961Dokument13 SeitenFan 6961Ariel NavarreteNoch keine Bewertungen

- Thb7128 InstructionsDokument9 SeitenThb7128 InstructionsanhxcoNoch keine Bewertungen

- DM0265Dokument19 SeitenDM0265liberthNoch keine Bewertungen

- A3953 DatasheetDokument12 SeitenA3953 DatasheetMohan RajNoch keine Bewertungen

- 74LS73Dokument5 Seiten74LS73Cristin BarnesNoch keine Bewertungen

- Up7706 DatasheetDokument12 SeitenUp7706 DatasheetFernando DupuyNoch keine Bewertungen

- XR-215 PLLDokument32 SeitenXR-215 PLLJ Jesús Villanueva GarcíaNoch keine Bewertungen

- FPAB20BH60B PFC SPM 3 Series For Single-Phase Boost PFC: Features General DescriptionDokument11 SeitenFPAB20BH60B PFC SPM 3 Series For Single-Phase Boost PFC: Features General DescriptionWelington GarciaNoch keine Bewertungen

- SG6105 Datasheet, Pinout, Application Circuits Power Supply Supervisor Regulator PWMDokument13 SeitenSG6105 Datasheet, Pinout, Application Circuits Power Supply Supervisor Regulator PWMBeatrizEstevesNoch keine Bewertungen

- Datasheet sg6105dDokument13 SeitenDatasheet sg6105dCartman SantosNoch keine Bewertungen

- LF 351Dokument14 SeitenLF 351Ivan PetrovicNoch keine Bewertungen

- ISL6565A, ISL6565B: Multi-Phase PWM Controller With Precision R or DCR Current Sensing For VR10.X Application FeaturesDokument28 SeitenISL6565A, ISL6565B: Multi-Phase PWM Controller With Precision R or DCR Current Sensing For VR10.X Application FeaturesFranciscoGomezNoch keine Bewertungen

- FAN7930BDokument22 SeitenFAN7930Bpagy snv100% (1)

- LD7750-DS Fuente TCL GermanDokument20 SeitenLD7750-DS Fuente TCL GermanAndres Alegria100% (1)

- SM72441 Programmable Maximum Power Point Tracking Controller For Photovoltaic Solar PanelsDokument10 SeitenSM72441 Programmable Maximum Power Point Tracking Controller For Photovoltaic Solar PanelsShahid SiddiqueNoch keine Bewertungen

- Lm2853 3A 550 KHZ Synchronous Simple Switcher® Buck RegulatorDokument18 SeitenLm2853 3A 550 KHZ Synchronous Simple Switcher® Buck RegulatormanirajNoch keine Bewertungen

- 20 W 2-Channel BTL AF Power Amplifier For Car Stereos: SANYO Electric Co.,Ltd. Semiconductor Bussiness HeadquartersDokument9 Seiten20 W 2-Channel BTL AF Power Amplifier For Car Stereos: SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquartersfernandes66Noch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorVon Everand110 Waveform Generator Projects for the Home ConstructorBewertung: 4 von 5 Sternen4/5 (1)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsVon EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsBewertung: 3.5 von 5 Sternen3.5/5 (6)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Von EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Bewertung: 4.5 von 5 Sternen4.5/5 (3)

- Deflection YokeDokument2 SeitenDeflection Yokesontuyet82Noch keine Bewertungen

- 239716035Dokument25 Seiten239716035sontuyet82Noch keine Bewertungen

- Mitsubishi Special Price Spares List 161111Dokument8 SeitenMitsubishi Special Price Spares List 161111sontuyet82Noch keine Bewertungen

- Technical Data & Service Manual: Indoor Unit: As52AlDokument31 SeitenTechnical Data & Service Manual: Indoor Unit: As52Alsontuyet82Noch keine Bewertungen

- C781 - Ser - MSG-18HRDN1-QC2 - B - V1Dokument38 SeitenC781 - Ser - MSG-18HRDN1-QC2 - B - V1sontuyet82Noch keine Bewertungen

- NN Se992s NN Sd982s NN St962s Panasonic 1680Dokument38 SeitenNN Se992s NN Sd982s NN St962s Panasonic 1680sontuyet82Noch keine Bewertungen

- Proson RV 2040 Service ManualDokument22 SeitenProson RV 2040 Service Manualsontuyet82Noch keine Bewertungen

- IM 1222 SC Supplement Canary WharfDokument14 SeitenIM 1222 SC Supplement Canary Wharfsontuyet82Noch keine Bewertungen

- Karaoke Circuit Building InstructionsDokument10 SeitenKaraoke Circuit Building Instructionssontuyet82Noch keine Bewertungen

- Public Media 2013920820520.005400 S07AHPDokument41 SeitenPublic Media 2013920820520.005400 S07AHPsontuyet82Noch keine Bewertungen

- Speaker Protection CircuitDokument3 SeitenSpeaker Protection Circuitsontuyet820% (2)

- STM Green Model SMPS Solution For High Power SLIM AdaptorDokument35 SeitenSTM Green Model SMPS Solution For High Power SLIM Adaptorsontuyet82Noch keine Bewertungen

- Clevo tn120rDokument90 SeitenClevo tn120rsontuyet82Noch keine Bewertungen

- MPEG-4 HD Single Chip iDTV IC: Emma3TlDokument2 SeitenMPEG-4 HD Single Chip iDTV IC: Emma3Tlsontuyet82Noch keine Bewertungen

- LH-C6230P C6231PDokument114 SeitenLH-C6230P C6231Psontuyet82Noch keine Bewertungen

- MC1723 PDFDokument9 SeitenMC1723 PDFOsman KoçakNoch keine Bewertungen

- AOC Inverter SCHDokument4 SeitenAOC Inverter SCHMarincus AdrianNoch keine Bewertungen

- FSFR1800Dokument17 SeitenFSFR1800sontuyet82Noch keine Bewertungen

- LED Flashing Specification at The Time of The Error: LC-40/46/52LE820E (1st Edition)Dokument4 SeitenLED Flashing Specification at The Time of The Error: LC-40/46/52LE820E (1st Edition)sontuyet82Noch keine Bewertungen

- ICX618ALA: Diagonal 4.5mm (Type 1/4) Progressive Scan CCD Image Sensor With Square Pixel For B/W CamerasDokument20 SeitenICX618ALA: Diagonal 4.5mm (Type 1/4) Progressive Scan CCD Image Sensor With Square Pixel For B/W Camerassontuyet82Noch keine Bewertungen

- 4 1 Alternating Current PDFDokument24 Seiten4 1 Alternating Current PDFmarizg piolNoch keine Bewertungen

- 177 Modern Transistor Circuits ForbeginnersDokument43 Seiten177 Modern Transistor Circuits ForbeginnersIliuta JohnNoch keine Bewertungen

- 7.4 Main Spindle Control With Analog Interface 6SN1121-0BA1!-0AA!Dokument7 Seiten7.4 Main Spindle Control With Analog Interface 6SN1121-0BA1!-0AA!Edinson ZamoraNoch keine Bewertungen

- Railway Axle Power GenerationDokument6 SeitenRailway Axle Power GenerationPooja BanNoch keine Bewertungen

- (Bill) Comparison of Low Frequency Resistance and Lightning Impulse Impedance On Transmission Towers PDFDokument6 Seiten(Bill) Comparison of Low Frequency Resistance and Lightning Impulse Impedance On Transmission Towers PDFalexanderlimaNoch keine Bewertungen

- A Transistor Ladder Voltage-Controlled Filter Implemented On A Field Programmable Analog ArrayDokument8 SeitenA Transistor Ladder Voltage-Controlled Filter Implemented On A Field Programmable Analog Arrayfidel.certucheNoch keine Bewertungen

- Electrical Power Graphic SymbolsDokument10 SeitenElectrical Power Graphic SymbolsPutra JawaNoch keine Bewertungen

- Low Voltage Fixed and Automatic Power Factor Correction SystemsDokument6 SeitenLow Voltage Fixed and Automatic Power Factor Correction Systemszabiruddin786Noch keine Bewertungen

- IMPAQ Charger Operations ManualDokument41 SeitenIMPAQ Charger Operations ManualBrayan NohNoch keine Bewertungen

- Alternating Current 24Dokument31 SeitenAlternating Current 24sri kanthNoch keine Bewertungen

- 2N4123, 2N4124 General Purpose Transistors: NPN SiliconDokument6 Seiten2N4123, 2N4124 General Purpose Transistors: NPN SiliconjosecarlosvjNoch keine Bewertungen

- Service Manual: Model: HT-2199 (Europe)Dokument48 SeitenService Manual: Model: HT-2199 (Europe)Eze KielNoch keine Bewertungen

- Electric Pressure Cookers Training ManualDokument25 SeitenElectric Pressure Cookers Training ManualLa perrritaaaNoch keine Bewertungen

- Open Ended LabDokument8 SeitenOpen Ended LabIHZAM ZIANoch keine Bewertungen

- Esm-4450 Man Env11Dokument125 SeitenEsm-4450 Man Env11Cristian SerbanoiuNoch keine Bewertungen

- ComponentsDokument28 SeitenComponentsGyan Swaroop TripathiNoch keine Bewertungen

- R Van Schalkwyk Curriculum VitaeDokument4 SeitenR Van Schalkwyk Curriculum VitaerubenkannieNoch keine Bewertungen

- Xgard Manual Issue 7Dokument64 SeitenXgard Manual Issue 7Sergei KurpishNoch keine Bewertungen

- Glofa Master-K: User 'S ManualDokument71 SeitenGlofa Master-K: User 'S Manualhass100% (1)

- Operator's Manual: Slit Lamp Microscope HS-5000 5XDokument46 SeitenOperator's Manual: Slit Lamp Microscope HS-5000 5XAli TayyabNoch keine Bewertungen

- Computer Aided Design 2 (E3004)Dokument14 SeitenComputer Aided Design 2 (E3004)Nurul AnisNoch keine Bewertungen

- Physical Chemistry 2 - Kinetics of Electrochemical ProcessesDokument44 SeitenPhysical Chemistry 2 - Kinetics of Electrochemical ProcessesNguyễn Thu HàNoch keine Bewertungen

- Properties of Electric Field LinesDokument1 SeiteProperties of Electric Field LinescbNoch keine Bewertungen

- RBS 6601 HW Installation PDFDokument37 SeitenRBS 6601 HW Installation PDFSang Du Minh100% (2)

- Marconi S 200kW Transatlant..Dokument6 SeitenMarconi S 200kW Transatlant..geraldino250Noch keine Bewertungen

- Test-Summary Formation FactorDokument15 SeitenTest-Summary Formation FactorWanucy Barroso RodriguesNoch keine Bewertungen

- 2 V Amp 2nd e Manual ADokument232 Seiten2 V Amp 2nd e Manual Aroymathew2003Noch keine Bewertungen

- Institute Engineering Department Academic Unit-1: Discover - . EmpowerDokument34 SeitenInstitute Engineering Department Academic Unit-1: Discover - . EmpowerAYUSHNoch keine Bewertungen

- Phase Shift Provided by One Phase Shift Network in RC Phase Shift Oscillator in 3 Stage IsDokument5 SeitenPhase Shift Provided by One Phase Shift Network in RC Phase Shift Oscillator in 3 Stage IsJoyce GeorgeNoch keine Bewertungen

- Densification Handbook: Hub Location Ericsson Nokia Node LocationDokument25 SeitenDensification Handbook: Hub Location Ericsson Nokia Node LocationromoNoch keine Bewertungen