Beruflich Dokumente

Kultur Dokumente

1544

Hochgeladen von

Dan EsentherCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

1544

Hochgeladen von

Dan EsentherCopyright:

Verfügbare Formate

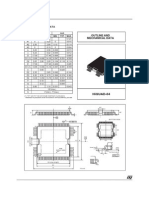

L4938E/ED L4938EPD

ADVANCED VOLTAGE REGULATOR

ENABLE AND SENSE INPUTS (EN, SI) PROTECTED AGAINST NEGATIVE TRANSIENTS DOWN TO -5V RESET THRESHOLD ADJUSTABLE FROM 3.8 TO 4.7V EXTREMELY LOW QUIESCENT CURRENT, 65A (LESS THAN 90A) IN STANDBY MODE OPERATING DC SUPPLY VOLTAGE RANGE 5V - 28V OPERATING TRANSIENT SUPPLY VOLTAGE UP TO 40V HIGH PRECISION STANDBY OUTPUT VOLTAGE 5V 1% WITH 100mA CURRENT CAPABILITY OUTPUT 2 VOLTAGE 5V 2% WITH 400mA CURRENT CAPABILITY (ADJ WIRED TO VOUT2) OUTPUT 2 VOLTAGE ADJUSTABLE BY EXTERNAL VOLTAGE DIVIDER OUTPUT 2 DISABLE FUNCTION FOR STANDBY MODE PIN CONNECTIONS

DIP (12+2+2)

SO20 (12+4+4)

PowerSO20

ORDERING NUMBERS: L4938E (DIP) L4938ED (SO) L4938EPD (PSO)

DESCRIPTION The L4938E/ED/EPD is a monolithic integrated dual voltage regulator with two very low dropout outputs and additional functions as power-on reset and input voltage sense. It is designed for supplying the microcomputer controlled systems especially in automotive applications.

PR

1 2 3 4 5 6 7 8 9 10

D94AT076A

20 19 18 17 16 15 14 13 12 11

SI VS1 VS2 GND GND GND GND N.C. OUT2 ADJ

PR CT EN GND GND RES SO OUT1

1 2 3 4 5 6 7 8

D94AT075A

16 15 14 13 12 11 10 9

SI VS1 VS2 GND GND N.C. OUT2 ADJ

GND N.C. VS2 VS1 SI PR CT EN N.C. GND

1 2 3 4 5 6 7 8 9 10

L4938EPD

20 19 18 17 16 15 14 13 12 11

GND N.C. OUT2 ADJ OUT1 SO RESET N.C. N.C. GND

CT EN GND GND GND GND RES SO OUT1

DIP (12+2+2)

SO (12+4+4)

PowerSO20

February 1999

1/12

L4938E - L4938ED - L4938EPD

ABSOLUTE MAXIMUM RATINGS

Symbol VINDC VINTR IO VSI ISI VEN IEN VRES , VSO IRES , ISO PO Tstg Tj TJSD Parameter DC Operating Supply Voltage Transient Operating Supply Voltage (T < 400ms) Output Current Sense Input Voltage (Voltage Forced) (note 2) Sense Input Current (Current Forced) (note 2) Enable Input Voltage (Voltage Forced) (note 2) Sense Input Current (Current Forced) (note 2) Output Voltages Output Currents (Output Low) Power Dissipation at Tamb = 80C (note 3) Powerdip 12+2+2 Storage Temperature Operating Junction Temperature Thermal shutdown junction temperature Output 2 will shut-down typically at Tj 10K lower than output 1 Value 28 -14 to 40 internally limited -20 to 20 1 -20 to 20 1 -0.3 to 20 5 875 -65 to 150 -40 to 150 165 Unit V V V mA V mA V mA mW C C C

Note 1: The circuit is ESD protected according to MIL-STD-883C Note 2: Current forced means voltage unlimited but current limited to the specified value Voltage forced means voltage limited to the specified valueswhile the current is not limited Note 3: Typical value soldered on a PC board with 8cm 2 copper ground plane (35mm thick).

BLOCK DIAGRAM

VS1

OUT1

1.23V REG1 VS2

REFERENCE

OUT2 ADJ

EN REG2

1.23V

1.23V

CT RES

PR RESET

1.4V

SI 1.23V SENSE

D94AT074A

SO

GND

2/12

L4938E - L4938ED - L4938EPD

THERMAL DATA

Symbol Rth j-amb Rth j-case Parameter Thermal Resistance Junction to ambient Thermal Resistance Junction to case

2

DIP 12+2+2 SO 12+4+4 PowerSO20 40 50 <2

Unit C/W C/W

Note 3: Typical value soldered on a PC board with 8cm copper ground plane (35mm thick).

PIN FUNCTIONS

PIN (DIP 12+2+2) 14 15 16 1 2 3 4, 5, 12, 13 6 7 8 9 10 11 PIN (SO 12+4+4) 18 19 20 1 2 3 4, 5, 6, 7, 14, 15, 16, 17 8 9 10 11 12 13 PIN PowerSO20 3 4 5 6 7 8 1,10,11,20 14 15 16 17 18 2,9,19 Name VS2 VS1 S1 PR CT EN GND RES SO OUT 1 ADJ OUT 2 NC Function Supply Voltage (400mA Regulator) Supply Voltage (100mA Regulator, Reset, Sense) Sense Input Reset Theresold Programming Reset Delay Capacitor Enable (low will activate the 400mA regulator) Ground Reset Output Sense Output 100mA Regulator Output Feedback of 400mA Regulator 400mA Regulator Output Not Connected

ELECTRICAL CHARACTERISTICS (VS = 14V; Tj = -40 to 150C unless otherwise specified.)

Symbol Parameter Supply Output Voltage Test Condition VS = 6 to 28V; IO1 = 400A to 100mA Tj 125C; IO1 = 50 to 400A IOUT1 = 10mA IOUT1 = 100mA; VS = 4.8V IOUT1 = 1 to 100mA (after regulation setting) VOUT1 = 0.8 to 4.5V IEN 2.4V (output 2 disabled) IO1 = 0.1mA; VSI > 1.3V TJ < 85C; RPR = 0 Enable = LOW; VS = 6 to 28V; I02 = 5 to 400mA IOUT2 = 100mA IOUT2 = 400mA; VS = 4.8V IOUT1 = 5 to 400mA (after regulation setting) V02 = 0.8 to 4.5V IOUT1 = 100mA; IOUT2 = 400mA VS = 6 to 28V; IO1 = 1mA, IO2 = 5mA, (after regulation setting) Min. 4.9 4.8 Typ. 5 5 0.1 0.2 Max. 5.1 5.2 0.2 0.4 25 400 90 Unit V V V V mV mA A A 5.1 0.2 0.3 0.3 0.6 50 150 1300 20 20 V V V mV mA mA mA mV

OUT 1

VO1

VDP1 VOL01 VLIM1 IQSB

Dropoutput Voltage 1 Load Regulation 1 Current Limit 1 Quiescent Current in Standby Mode

100

200 65 75

OUT 2

VO2 VDP2 VOL02 RADJ ILIM2 IQ VOLi 1,2 Output Voltage 2 ADJ connected to OUT 2 Dropoutput Voltage 2 Load Regulation 2 Adjust Input Resistance Current Limit 2 Quiescent Current Line Regulation 4.9

60 450

100 650

OUT1, OUT 2

3/12

L4938E - L4938ED - L4938EPD

ELECTRICAL CHARACTERISTICS (Continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

ENABLE INPUT

VENL VENH VENhyst IEN LOW IEN HIGH Enable Input Low Voltage (Output 2 Active) Enable Input High Voltage Enable Hysteresis Enable Input Current Low Enable Input Current High VEN = 0 VEN = 1.1 to 7V; T J < 130C; VEN = 1.1 to 7V; TJ = 130 to 150C; -20 1.4 20 -20 -1 -10 30 -8 0 0 1 20 60 -3 1 10 V V mV A A A

RESET CIRCUIT

VRT VRTH tRD min tRD nom tRR ICT ICT VRESL VRESH Reset Theresold Voltage (note4) Reset Theresold Hysteresis Reset Pulse Delay Reset Pulse Delay Reset Reaction Time Pull Down Capability of the Discharge circuit Charge Current Reset Output Low Voltage Reset Output High Leakage current RPR = RPR = 0 RPR = CRES = 47nF; t r 30s; (note 5) CRES = 47nF; (note 6) CRES = 47nF VOUT1 < VRT VOUT1 > VRT R RES = 10K to VOUT1 VOUT1 1.5V VRES = 5V 4.5 3.65 30 40 60 10 3 -1.3 VO1-0.3 VO1-0.2 3.8 60 60 100 50 6 -1 3.95 120 100 140 150 15 0.7 0.4 1 V V mV ms ms s mA A V A

SENSE COMPARATOR

VSI VSIT VSITH VSOL ISOH ISI HIGH ISI LOW Functional Range Sense Threshold Voltage Sense Threshold Hysteresis Sense Output Low Voltage Sense Output Leakage Sense Input Current High Sense Input Current Low Falling Edge; TJ <130C Falling Edge; TJ <130 to 150C V SI 1.05V; RSO =10K connected to 5V; VS 5V VSO = 5V; VSI 1.5V VSI = 1.1 to 7V; TJ <130C VSI = 1.1 to 7V; TJ <130 to 150C VSI = 0V -1 -10 -20 0 0 -8 -20 1.08 1.05 10 1.16 1.16 30 20 1.24 1.29 60 0.4 1 1 10 -3 V V V mV V A A A A

Note : 4) The reset threshold can be programmed continuously from typ 3.8V to 4.7V by changing a value of an external resistor from pin PR to GN 5) This is a minimum reset time according to the hysteresis of the comparator. Delay time starts with VOUT1 exceeding VRT 6) This is the nominal reset time depending on the discharging limit of CT (saturation voltage) and theupper threshold of the timer comparator. Delay time starts with VOUT1 exceeding VRT 7) The leakage of CT must be less than 0.5mA (2V). If an external resistor between CT and VOUT1 is applied, the leakage current may be increased. The external resistor should have more than 30K. for stability: Cs 1F, C01 10F, C02 10F, ESR 5 (designed target) For details see application note. 8) For transients exceeding 20V or -20V external protection is required at the Pins SI and EN as shown at Pin EN. The protection proposed will provide proper function for transients in the range of 200V. If the zener diode is omitted the external resistor should be raised to 200K to limit the current to 1mA. Without the zener diode, the function 20V or -20V can not be guaranteed.

4/12

L4938E - L4938ED - L4938EPD

Figure 1. Application Diagram.

VS1 CS 1.23V REG1 (Note 8) 100K 15V EN REG2 1.23V REFERENCE

OUT1 CO1

OUT2 VS2 ADJ CO2

for example BZX97C15 PR

1.23V

CT

CT (Note 7)

RES VOUT1 RESET SI 1.4V SO RSO

1.23V SENSE

D94AT079A

GND

FUNCTIONAL DESCRIPTION The L4938E/ED/EPD is a monolithic integrated dual voltage regulator, based on the STM modulator voltage regulator approach. Several outstanding features and auxiliary functions are implemented to meet the requirements of supplying microprocessor systems in automotive applications. Nevertheless, it is suitable also in other applications where two stabilized voltages are required. The modular approach of this device allows to get easly also other features and functions when required. Standby Regulator The standby regulator uses an Isolated collector Vertical PNP transistor as a regulating element. With this structure very low dropout volotage at currents up to 100mA is obtained. The dropout operation of the standby regulator is maintained down to 3V input supply voltage. The output voltage is regulated up to the transient input supply voltage of 40V. With this feature no functional interruption due to overvoltage pulses is generated. In the standby mode when the output 2 is disabled, the current consumption of the device (quiescent current) is less than 90A (14V supply voltage).

To reduce the quiescent current peak in the undervoltage region and to improve the transient response in this region, the dropout voltage is controlled. A second regulation path will keep the output voltage without load below 5.5V even at high temperatures. Output 2 Voltage The output 2 regulator uses the same output structure as the standby regulator but rated for the output current of 400mA. The output voltage is internally fixed to 5V if ADJ is connected to VOUT2. The output 2 regulator can be switches OFF via the enable input. Figure 2.

OUT2 R1E R2E RADJ R2i total 100K typical

D94AT080

ADJ R1i + 1.23V

5/12

L4938E - L4938ED - L4938EPD

Connecting a resistor divider R1E, R2E to the ADJ, OUT2 pin the output voltage 2 can be programmed to the value of R1E(R2E + RADJ) VOUT2 = VOUT1 1 + R2E RADJ with RADJ = 60K to 150K and VOUT1 = 4.95 to 5.05V. For an exact calculation the temperature coefficient (Tc -2000pprm) of the internal resistor (RADJ) must be taken into account. Pin ADJ in this mode should not have a capacitive burden because this would reduce the phase margin of the regulator loop. Reset circuit The reset circuit supervises the standby output voltage. The reset output (RES) is defined from VOUT 1V. Even if VS is lacking, the reset generator is supplied by the output voltage VOUT1. The reset threshold of 4.7V is defined with the internal reference voltage (note 9) and standby output divider, when pin PR is left open. The reset threshold voltage can be programmed in the range from 3.8V to 4.7V by connecting an external resistor from pin PR to GND. The value of the programming resistor RPR can be calculated with: RPR = 22K 92.9K, 3.8V VRT 4.7V 4.7K 1 VRT than approximately 50s. The minimum rset time is generated if reset condition only occures for a short time triggering a reset pulse but not completely discharging CT. The reset can be related to output2 on request. If higher charge currents for the reset capacitor are required a resistors from Pin CT to OUT1, may be used to increase the current. We recommended the use of 10K to 5V as an output pull up. Sense Comparator The sense comparator compares an input signal with an internal voltage reference of typical 1.23V. The use of an external voltage divider makes this comparator very flexible in the application. It can be used to supervise the input voltage either before or after the protection diode and to give additional information to the microprocessor like low voltage warnings. We recommended the use of 10K to 5V as an output pull up.

Note 9: The reference is alternatively supplied from VS or VOUT1. If one supply is present, the reference is operating.

The reset pulse delay time tRD, is defined with the charge time of an external capacitor CT: CT 0.6V tRDmin = (note 5) 1A tRDnom = CT 1.4V (note 6) 1A

Thermal Protection Both outputs are provided with an overtemperature shut down regulation power dissipation down to uncritical values. Output 2 will shut down approximately 10K before output 1. Under normal conditions shut down of output 2 will allow the chip to cool down again. Thus output 1 will be unaffected. The thermal shut down reduces the output voltages until power dissipation and the flow of thermal energy out of the chip balance. Transient Sensitivity In proper operation (VOUT > 4.5V) the reference is supplied by VOUT1 thus reducing sensitivity to input transients. Precise Data will be issued as soon as samples are available.

The reaction time of the reset circuit originates from the noise immunity. Standby output voltage drops below the reset threshold only a bit longer than the reaction time results in a shorter reset delay time. The nominal reset delay time will be generated for standby output voltage drops longer

6/12

L4938E - L4938ED - L4938EPD

Figure 3. Reset Generator

OUT1 REF 1.23V 17K 74K PR VOUT1 REG + Low threshold VBE at 1A=0.5V at 25C High threshold CT CT

D94AT081

1A RES

10...100K

=1.4

Figure 4:

7/12

L4938E - L4938ED - L4938EPD

INPUT PROTECTION The Inputs Enable (EN) and sense in(SI) are proFigure 5. tected against negative transients. Figure 5 is showing the simplified schematic

Input Characteristics of SI, EN:

8/12

L4938E - L4938ED - L4938EPD

DIM. MIN. a1 B b b1 D E e e3 F I L Z 0.38 0.51 0.85

mm TYP. MAX. MIN. 0.020 1.40 0.50 0.50 20.0 8.80 2.54 17.78 7.10 5.10 3.30 1.27 0.015 0.033

inch TYP. MAX.

OUTLINE AND MECHANICAL DATA

0.055 0.020 0.020 0.787 0.346 0.100 0.700 0.280 0.201 0.130

Powerdip 16

0.050

9/12

L4938E - L4938ED - L4938EPD

mm DIM. MIN. A A1 B C D E e H h L K 10 0.25 0.4 2.35 0.1 0.33 0.23 12.6 7.4 1.27 10.65 0.75 1.27 0.394 0.010 0.016 TYP. MAX. 2.65 0.3 0.51 0.32 13 7.6 MIN. 0.093 0.004 0.013 0.009 0.496 0.291

inch TYP. MAX. 0.104 0.012 0.020 0.013 0.512 0.299 0.050 0.419 0.030 0.050

OUTLINE AND MECHANICAL DATA

SO20

0 (min.)8 (max.)

h x 45

A B e K H D A1 C

20

11 E

0 1

SO20MEC

10/12

L4938E - L4938ED - L4938EPD

mm TYP. inch TYP.

DIM. A a1 a2 a3 b c D (1) D1 E e e3 E1 (1) E2 E3 G H h L N S T

MIN. 0.1 0 0.4 0.23 15.8 9.4 13.9

MAX. 3.6 0.3 3.3 0.1 0.53 0.32 16 9.8 14.5

MIN. 0.004 0.000 0.016 0.009 0.622 0.370 0.547

MAX. 0.142 0.012 0.130 0.004 0.021 0.013 0.630 0.386 0.570

OUTLINE AND MECHANICAL DATA

1.27 11.43 10.9 5.8 0 15.5 0.8 11.1 0.429 2.9 6.2 0.228 0.1 0.000 15.9 0.610 1.1 1.1 0.031 10 (max.) 8 (max.) 10

0.050 0.450 0.437 0.114 0.244 0.004 0.626 0.043 0.043

JEDEC MO-166

0.394

(1) "D and F" do not include mold flash or protrusions. - Mold flash or protrusions shall not exceed 0.15 mm (0.006"). - Critical dimensions: "E", "G" and "a3"

PowerSO20

N a2 b e A

c DETAIL B a1 E DETAIL A

DETAIL A e3 H

lead

D a3 DETAIL B

20 11

Gage Plane 0.35

slug

-C-

S E2 T E1 BOTTOM VIEW

SEATING PLANE G C

(COPLANARITY)

E3

1 10

h x 45

PSO20MEC

D1

11/12

L4938E - L4938ED - L4938EPD

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. The ST logo is a registered trademark of STMicroelectronics 1999 STMicroelectronics Printed in Italy All Rights Reserved STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A. http://www.st.com

12/12

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- PSSO-12 Mechanical Data: Dim. Mm. Min. TYP MaxDokument1 SeitePSSO-12 Mechanical Data: Dim. Mm. Min. TYP MaxDan EsentherNoch keine Bewertungen

- Powerso16: Outline and Mechanical DataDokument1 SeitePowerso16: Outline and Mechanical DataDan EsentherNoch keine Bewertungen

- Powerso-20 Mechanical Data: Dim. Mm. Inch Min. TYP Max. Min. Typ. MaxDokument1 SeitePowerso-20 Mechanical Data: Dim. Mm. Inch Min. TYP Max. Min. Typ. MaxDan EsentherNoch keine Bewertungen

- Ppak Mechanical Data: Dim. Min. TYP MaxDokument1 SeitePpak Mechanical Data: Dim. Min. TYP MaxDan EsentherNoch keine Bewertungen

- Powersso-24 Mechanical Data: Dim. Mm. Min. Typ MaxDokument1 SeitePowersso-24 Mechanical Data: Dim. Mm. Min. Typ MaxDan EsentherNoch keine Bewertungen

- L9929Dokument3 SeitenL9929Dan EsentherNoch keine Bewertungen

- Multipowerso-30 Mechanical Data: Dim. Mm. Min. Typ MaxDokument1 SeiteMultipowerso-30 Mechanical Data: Dim. Mm. Min. Typ MaxDan EsentherNoch keine Bewertungen

- Pso 36Dokument1 SeitePso 36Dan EsentherNoch keine Bewertungen

- Fully Integrated H-Bridge Motor Driver: VNH3SP30Dokument26 SeitenFully Integrated H-Bridge Motor Driver: VNH3SP30Dan EsentherNoch keine Bewertungen

- Hiquad 64Dokument1 SeiteHiquad 64Dan EsentherNoch keine Bewertungen

- 10832Dokument26 Seiten10832Dan EsentherNoch keine Bewertungen

- 10302Dokument4 Seiten10302Dan EsentherNoch keine Bewertungen

- 10833Dokument18 Seiten10833Dan EsentherNoch keine Bewertungen

- Powerso-10 Mechanical Data: Dim. Mm. Inch Min. Typ Max. Min. Typ. MaxDokument1 SeitePowerso-10 Mechanical Data: Dim. Mm. Inch Min. Typ Max. Min. Typ. MaxDan EsentherNoch keine Bewertungen

- VNQ830A-E: Quad Channel High Side DriverDokument17 SeitenVNQ830A-E: Quad Channel High Side DriverDan EsentherNoch keine Bewertungen

- VND830PEP-E: Double Channel High Side DriverDokument13 SeitenVND830PEP-E: Double Channel High Side DriverDan EsentherNoch keine Bewertungen

- 10831Dokument21 Seiten10831Dan EsentherNoch keine Bewertungen

- Uh 30Dokument10 SeitenUh 30Dan EsentherNoch keine Bewertungen

- 10683Dokument19 Seiten10683Dan EsentherNoch keine Bewertungen

- 10311Dokument23 Seiten10311Dan Esenther100% (1)

- 10261Dokument10 Seiten10261Dan EsentherNoch keine Bewertungen

- 10303Dokument5 Seiten10303Dan EsentherNoch keine Bewertungen

- 10640Dokument22 Seiten10640Dan EsentherNoch keine Bewertungen

- 10830Dokument21 Seiten10830Dan EsentherNoch keine Bewertungen

- 10022Dokument262 Seiten10022Dan EsentherNoch keine Bewertungen

- 9927Dokument11 Seiten9927Dan EsentherNoch keine Bewertungen

- 9792Dokument21 Seiten9792Dan EsentherNoch keine Bewertungen

- 9934Dokument11 Seiten9934Dan EsentherNoch keine Bewertungen

- 9696Dokument17 Seiten9696Dan EsentherNoch keine Bewertungen

- 9933Dokument11 Seiten9933Dan EsentherNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- M-PRO2 DatasheetDokument17 SeitenM-PRO2 DatasheetcdpangoNoch keine Bewertungen

- 2010-2011 CatalogDokument378 Seiten2010-2011 CatalogHouston Community College91% (43)

- Brickwork and Stonework SupportDokument20 SeitenBrickwork and Stonework SupportSanel GrabovicaNoch keine Bewertungen

- Slant +/- 45° Dual Polarized PanelDokument1 SeiteSlant +/- 45° Dual Polarized PaneljorgeNoch keine Bewertungen

- B. B. ALE Department of Mechanical EngineeringDokument36 SeitenB. B. ALE Department of Mechanical EngineeringRam Krishna SinghNoch keine Bewertungen

- VESDADokument4 SeitenVESDAamijetomar08Noch keine Bewertungen

- John Deere Tractor Service Manual 4040 Tractor 4240 TractorDokument12 SeitenJohn Deere Tractor Service Manual 4040 Tractor 4240 Tractormymisel0% (1)

- ICT On YP Final ReportDokument29 SeitenICT On YP Final Reportquang140788Noch keine Bewertungen

- THE FLIGHT CONTROLS - PresentationDokument14 SeitenTHE FLIGHT CONTROLS - PresentationGiannisNoch keine Bewertungen

- Staad Design CodesDokument7 SeitenStaad Design CodespanjumuttaiNoch keine Bewertungen

- Iseet Iit Jee Main 2013Dokument64 SeitenIseet Iit Jee Main 2013Omkar SawantNoch keine Bewertungen

- Sultan Saed Al - Zahrani Est ProfileDokument60 SeitenSultan Saed Al - Zahrani Est ProfileaayasirNoch keine Bewertungen

- PI734EDokument8 SeitenPI734E3efooNoch keine Bewertungen

- How to Make $1,729 Daily with a Simple One Page WebsiteDokument45 SeitenHow to Make $1,729 Daily with a Simple One Page WebsiteNoriel Morales JaritoNoch keine Bewertungen

- MAO To CMS Encounter Reporting GA Scenarios - 02172012Dokument145 SeitenMAO To CMS Encounter Reporting GA Scenarios - 02172012Marinu24Noch keine Bewertungen

- DGEG EsquemaDokument15 SeitenDGEG EsquemaAlexander James ThorntonNoch keine Bewertungen

- Cma B6521 PDFDokument1 SeiteCma B6521 PDFSurya MantaNoch keine Bewertungen

- FCD-exploded Drawing and Parts Number (English) - 20230522Dokument10 SeitenFCD-exploded Drawing and Parts Number (English) - 20230522Rene GuerreroNoch keine Bewertungen

- Destiny 2: Destiny 2 Is An Online-Only Multiplayer First-Person Shooter Video GameDokument22 SeitenDestiny 2: Destiny 2 Is An Online-Only Multiplayer First-Person Shooter Video GameDoktormin106Noch keine Bewertungen

- Maquina de Anestesia Pelon Prima - sp2 - Service - ManualDokument110 SeitenMaquina de Anestesia Pelon Prima - sp2 - Service - Manualperla_canto_1Noch keine Bewertungen

- Handbook em Final EngDokument56 SeitenHandbook em Final Engigor_239934024Noch keine Bewertungen

- STUP Consultants P. LTD.: IN MonthsDokument11 SeitenSTUP Consultants P. LTD.: IN Monthsjitu487Noch keine Bewertungen

- Bacth ADokument1 SeiteBacth AAditya SurveNoch keine Bewertungen

- Compiler Design Question Bank: PART-A QuestionsDokument23 SeitenCompiler Design Question Bank: PART-A QuestionsBalaram Rath0% (1)

- Rain Alarm Project by Samar SirohiDokument19 SeitenRain Alarm Project by Samar SirohisamNoch keine Bewertungen

- Audi RS4 Avant quattro technical documentationDokument62 SeitenAudi RS4 Avant quattro technical documentationJustin Sandifer100% (1)

- Qt Competency Center Agenda OverviewDokument21 SeitenQt Competency Center Agenda OverviewDharani Kumar K BNoch keine Bewertungen

- Keller SME 12e PPT CH02Dokument22 SeitenKeller SME 12e PPT CH02NAM SƠN VÕ TRẦNNoch keine Bewertungen

- Integrated Voice Evacuation System VM-3000 Series: Operating InstructionsDokument144 SeitenIntegrated Voice Evacuation System VM-3000 Series: Operating InstructionsAbraham GamaNoch keine Bewertungen

- The Communication ProcessDokument7 SeitenThe Communication ProcessInzi GardeziNoch keine Bewertungen