Beruflich Dokumente

Kultur Dokumente

8086 Architecture

Hochgeladen von

Dhiraj KapilaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

8086 Architecture

Hochgeladen von

Dhiraj KapilaCopyright:

Verfügbare Formate

8086 Architecture

Dr. Mohammad Najim Abdullah 1. Hardware Organization

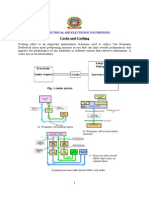

On the structural scheme of the i8086 processor we can see two separate asynchronous processing units. The execution unit (EU) executes instructions; the us interface unit (!"U) fetches instructions# rea$s operan$s# an$ writes results. The two units can operate almost in$epen$ently of one another an$ are a le# un$er most circumstances# to extensi%ely o%erlap instruction fetch with execution. The result is that# in most cases# the time normally re&uire$ to fetch instructions '$isappears' ecause the EU executes instructions that ha%e alrea$y een fetche$ y !"U. Of course nothing special# ut remem er the time when i8086 was $esigne$.

( Dr. Mohammad Najim Abdullah

Execution Unit The execution unit consists of general registers# uffer registers# control unit# arithmetic)logic unit# an$ flag register. The *+U maintains the ,-U status an$ control flags an$ manipulates the general registers an$ instruction operan$s. The EU is not connecte$ to the system us. "t o tains instructions from a &ueue maintaine$ y the !"U. +i.ewise# when an instruction re&uires access to memory or to a peripheral $e%ice# the EU re&uests the !"U to o tain or store the $ata. The EU manipulates only with (6/ it a$$resses (effecti%e a$$resses). *n a$$ress relocation that ena les the EU access to the full mega yte is performe$ y !"U. Bus Interface Unit The us interface unit performs all us operations for the EU. 0ata is transferre$ etween the ,-U an$ memory or ")O $e%ices upon $eman$ from the EU. 0uring perio$s when the EU is usy executing instructions# the !"U fetches more instructions from memory. The instructions are store$ in an internal 1*2 array calle$ the instruction stream &ueue. The 8086 &ueue can store up to six instruction ytes. This allows the !"U to .eep the EU supplie$ with prefetche$ instructions un$er most con$itions. The !"U of 8086 $oes not initiate a fetch until there are two empty ytes in its &ueue. The !"U normally o tains two instruction ytes per fetch# ut if a program transfer forces fetching from an o$$ a$$ress# the 8086 !"U automatically rea$s one yte from the o$$ a$$ress an$ then resumes fetching two/ yte wor$s from the su se&uent e%en a$$resses. Un$er most circumstances the &ueue contains at least one yte of the instruction stream an$ the EU $oes not ha%e to wait for instructions to e fetche$. The instructions in the &ueue are the next logical instructions so long as execution procee$s serially. "f the EU executes an instruction that transfers control to another location# the !"U resets the &ueue# fetches the instruction from the new a$$ress# passes it imme$iately to the EU# an$ then egins refilling the &ueue from the new location. "n a$$ition# the !"U suspen$s instruction fetching whene%er the EU re&uests a memory or ")O rea$ or write (except that a fetch alrea$y in progress is complete$ efore executing the EU3s us re&uest).

The Detail o! the Architecture

Registers The general registers of the 8086 are $i%i$e$ into two sets of four (6/ it registers each. The $ata registers an$ the pointer an$ in$ex registers. The $ata registers3 upper an$ lower hal%es are separately a$$ressa le. "n other wor$s# each $ata register can e use$ interchangea ly as a (6/ it register or as two 8/ it registers. The $ata registers can e use$ without constraint in most arithmetic an$ logic operations. 4ome instructions use certain registers implicitly thus allowing compact yet powerful enco$ing. The pointer an$ in$ex registers can e use$ only as (6/ it registers. They can also participate in most arithmetic an$ logic operations. "n fact all eight general registers fit the $efinition of 'accumulator' as

5 Dr. Mohammad Najim Abdullah

use$ in first an$ secon$ generation microprocessors. The pointer an$ in$ex registers (except !-) are also use$ implicitly in some instructions. The segment registers contain the ase a$$resses of logical segments in the 8086 memory space. The ,-U has $irect access to four segments at a time. The ,4 register points to the current co$e segment; instructions are fetche$ from this segment. The 44 points to the current stac. segment; stac. operations are performe$ on locations in this segment. The 04 register points to the current $ata segment; it generally contains program %aria les. The E4 points to the current extra segment; which also is typically use$ for $ata storage. The "- (instruction pointer) is up$ate$ y the !"U so that it contains the offset of the next instruction from the eginning of the current co$e segment. 0uring normal execution "- contains the offset of the next instruction to e fetched y the !"U; whene%er "- is sa%e$ on the stac.# howe%er# it is first automatically a$6uste$ to point to the next instruction to e executed. -rograms $o not ha%e $irect access to the "-. There are eight (6/ it general registers. The $ata registers7 AX ( AH and AL) BX ( BH and BL) CX ( CH and CL ) DX ( DH and DL ) The pointer an$ in$ex registers7 BP, SP, SI, DI The upper an$ lower hal%es of the $ata registers are separately a$$ressa le. 2emory space is $i%i$e$ into logical segments up to 68. ytes each. The ,-U has $irect access to four segments at a time; their ase a$$resses are containe$ in the segment registers CS, DS, SS, ES CS 9 co$e segment; DS 9 $ata segment; SS 9 stac. segment; ES 9 extra segment :lags are maintaine$ in the flag register $epen$ing on the result of the arithmetic or logic operation. * group of instructions is a%aila le that allows a program to alter its execution $epen$ing on the state of the flags# that is# on the result of a prior operation. There are 7

; Dr. Mohammad Najim Abdullah

A! (the auxiliary carry flag) use$ y $ecimal arithmetic instructions. "n$icates carry out from the low ni le of the 8/ it &uantity to the high ni le# or orrow from the high ni le into the low ni le. C! (the carry flag) in$icates that there has een carry out of # or a orrow into# the high/or$er it of the result. "! (the o%erflow flag) in$icates that an arithmetic o%erflow has occurre$. S! (the sign flag) in$icates the sign of the result (high/or$er it is set# the result is negati%e). P! (the parity flag) in$icates that the result has an e%en parity# an e%en num er of (/ its. #! (the <ero flag) in$icates that the result of the operation is 0. Three a$$itional control flags can e set an$ cleare$ y programs to alter processor operations7 D! (the $irection flag) causes string instructions to auto/$ecrement if it is set an$ to auto/increment if it is cleare$. I! (the interrupt ena le flag) allows the ,-U to recogni<e external interrupts. $! (the trap flag) puts the processor into single/step mo$e for $e ugging.

%e&or' "rgani(ation The 8086 can accommo$ate up to (#088#=>6 ytes of memory. :rom the storage point of %iew# the memory space is organi<e$ as array of 8/ it ytes. "nstructions# yte $ata an$ wor$ $ata may e freely store$ at any yte a$$ress without regar$ for alignment. The "ntel con%ention is that the most/significant yte of wor$ $ata is store$ in the higher memory location. * special class of $ata (pointers) is store$ as $ou le wor$s. The lower/ a$$resse$ wor$ of a pointer contains an offset %alue# an$ the higher/a$$resse$ wor$ contains a segment ase a$$ress. Each wor$ is store$ following the a o%e con%ention. The i8086 programs '%iew' the mega yte of memory space as a group of segments that are $efine$ y the application. * segment is a logical unit of memory that may e up to 68. ytes long. Each segment is ma$e up of contiguous memory locations an$ is an in$epen$ent separately a$$ressa le unit. The software must assign to e%ery segment a ase a$$ress# which is its starting location in the memory space. *ll segments egin on (6/ yte memory oun$aries calle$ paragraphs. The segment registers point to the four currently a$$ressa le segments. To o tain co$e an$ $ata from other segments# program must change the content of segment registers to point to the $esire$ segments. E%ery memory location has its physical a$$ress an$ its logical a$$ress. * physical a$$ress is the 50/ it %alue that uni&uely i$entifies each yte location in the memory space.

8 Dr. Mohammad Najim Abdullah

-hysical a$$resses may range from 0? to :::::?. *ll exchanges etween the ,-U an$ memory components use physical a$$resses. ?owe%er# programs $eal with logical rather than physical a$$resses. * logical a$$ress consists of a segment ase an$ offset %alue. The logical to physical a$$ress translation is $one y !"U whene%er it accesses memory. The !"U shifts segment ase y 8 to the left an$ a$$s the offset to this %alue. Thus we o tain 50/ it physical a$$ress an$ get the explanation for (6/ yte memory oun$aries for the segment ase eginning. The offset of the memory %aria le is calculate$ y the EU $epen$ing on the a$$ressing mo$es an$ is calle$ the operan$3s effecti%e a$$ress (E*). 4tac. is implemente$ in memory an$ is locate$ y the stac. segment register an$ the stac. pointer register. *n item is pushe$ onto the stac. y decrementing 4- y 5 an$ writing the item at the new top of stac. (TO4). *n item is poppe$ off the stac. y copying it from TO4 an$ then incrementing 4- y 5. The memory locations 0? through >:? are $e$icate$ for interrupt %ector ta le# an$ locations ::::0? through :::::? are $e$icate$ for system reset. In)ut*"ut)ut The 8086 ")O space can accommo$ate up to 68. 8/ it ports or up to ;5. (6/ it ports. The "@ an$ OUT instructions transfer $ata etween the accumulator an$ ports locate$ in ")O space. The ")O space is not segmente$; to access a port# the !"U simply places the port a$$ress on the lower (6 lines of the a$$ress us. ")O $e%ices may also e place$ in the 8086 memory space. *s long as the $e%ices respon$ li.e the memory components# the ,-U $oes not .now the $ifference. This a$$s programming flexi ility# an$ is pai$ y longer execution of memory oriente$ instructions. Processor Contro+ and %onitoring The interrupt system of the 8086 is ase$ on the interrupt %ector ta le which is locate$ from 0? through >:? ($e$icate$) an$ from 80? through ;::? (user a%aila le). E%ery interrupt is assigne$ a type co$e that i$entifies it to the ,-U. !y multiplying (type A 8)# the ,-U calculates the location of the correct entry for a gi%en interrupt. E%ery ta le entry is 8 ytes long an$ contains the offset an$ the segment ase (pointer) of the correspon$ing interrupt proce$ure that shoul$ e execute$. *fter system reset all segments are initiali<e$ to 0? except ,4 which is initiali<e$ to ::::?. 4ince# the processor executes the first instruction from a solute memory location ::::0?. This location normally contains an intersegment $irect B2- instruction whose target is the actual eginning of the system program.

"o!tware Organization

Instruction Set The 8086 instruction set from programmer3s point of %iew contains a out (00 instructions. ?owe%er the num er of machine instructions is more then ;800. :or example

= Dr. Mohammad Najim Abdullah

2OC instruction has 58 $ifferent machine forms. On the functional le%el we can $i%i$e the instruction set on 7 (. 0ata transfer instructions (2OC# D,?E# +E*# ...)# 5. *rithmetic instructions (*00# 4U!# "@,# 0E,# ...)# ;. !it manipulation instructions (*@0# 4?1# 1O1# ...)# 8. 4tring instructions (2OC4# +O04# 1E-# ...)# =. -rogram transfer instructions (,*++# B2-# BF# 1ET# ...)# 6. "nterrupt instructions ("@T# "@TO# "1ET)# >. -rocessor control instructions (,+,# 4T0# ?+T# ...). Addressing &odes, The 8086 has the following a$$ressing mo$es a%aila le7 (. 1egister a$$ressing ( 2OC *D#!D )# 5. "mme$iate a$$ressing ( 2OC *D#5:? )# ;. 0irect a$$ressing ( 2OC *D#*+-?*)# 8. 1egister in$irect a$$ressing ( 2OC *D#G!DH )# =. !ase$ a$$ressing ( 2OC *D#G!DI5H )# 6. "n$exe$ a$$ressing ( 2OC *D#!ET*G4"H )# >. !ase$ in$exe$ a$$ressing ( 2OC *D#G!DH.E*22*G4"H )#

6 Dr. Mohammad Najim Abdullah

Das könnte Ihnen auch gefallen

- Cs2257 Operating Systems Lab ManualDokument43 SeitenCs2257 Operating Systems Lab ManualmanjulakinnalNoch keine Bewertungen

- SQL Advanced Topics 1Dokument6 SeitenSQL Advanced Topics 1dannyzarNoch keine Bewertungen

- Computer For CompetetionDokument15 SeitenComputer For CompetetionRaj Kumar SinghNoch keine Bewertungen

- Shell Scripting PresentationDokument91 SeitenShell Scripting PresentationNiranjan DasNoch keine Bewertungen

- Unit I - The 8086 Processor - Software AspectsDokument7 SeitenUnit I - The 8086 Processor - Software Aspectsanand_duraiswamyNoch keine Bewertungen

- Resolving Common Oracle Wait Events Using The Wait InterfaceDokument11 SeitenResolving Common Oracle Wait Events Using The Wait Interfacealok_mishra4533Noch keine Bewertungen

- BeagleBoneBlack TutorialsDokument24 SeitenBeagleBoneBlack Tutorialstuyen1989100% (1)

- CPP HowToProgramDokument51 SeitenCPP HowToProgramDotrung KienNoch keine Bewertungen

- Subroutines: Subroutines The Stack RecursionDokument44 SeitenSubroutines: Subroutines The Stack RecursionElad TalicNoch keine Bewertungen

- Multi2sim-M2s Simulation FrameworkDokument36 SeitenMulti2sim-M2s Simulation FrameworkNeha JainNoch keine Bewertungen

- UNIT-1 Introduction To Embedded Systems Two Mark Questions and AnswersDokument30 SeitenUNIT-1 Introduction To Embedded Systems Two Mark Questions and AnswersBharath RamanNoch keine Bewertungen

- Department of Information TechnologyDokument25 SeitenDepartment of Information Technologymyilvahanan85Noch keine Bewertungen

- AbInitio FAQsDokument14 SeitenAbInitio FAQssarvesh_mishraNoch keine Bewertungen

- Reverse EngineeringDokument85 SeitenReverse Engineeringhughpearse88% (8)

- CSE420/598 Computer Architecture I (FALL 2008) Programming Assignment 4 (100 + 50 Points) Pipelining SimulatorDokument5 SeitenCSE420/598 Computer Architecture I (FALL 2008) Programming Assignment 4 (100 + 50 Points) Pipelining SimulatorJimmy BroncoNoch keine Bewertungen

- The 80c196 ArchitectureDokument27 SeitenThe 80c196 ArchitectureSai Sreekar100% (1)

- Basic Tutorial For Beginners On R: Start - All Programs - Teaching - Math - R 2.7.0Dokument6 SeitenBasic Tutorial For Beginners On R: Start - All Programs - Teaching - Math - R 2.7.0Nikher VermaNoch keine Bewertungen

- Cse230 s14 h05Dokument3 SeitenCse230 s14 h05Heather MarshallNoch keine Bewertungen

- Labsheet 5Dokument15 SeitenLabsheet 5aghgghjjhjhjNoch keine Bewertungen

- 1000 SAP ABAP Interview QuesDASDions and AnswersDokument19 Seiten1000 SAP ABAP Interview QuesDASDions and AnswersSreenith SathianNoch keine Bewertungen

- Unit 6: Intel 8051 MicrcontrollerDokument16 SeitenUnit 6: Intel 8051 Micrcontrollerachuu1987Noch keine Bewertungen

- Core Java NotesDokument56 SeitenCore Java Notesraviteja_357Noch keine Bewertungen

- 1 What Are The Major Differences Between ESX 3.5 and Vsphere?Dokument8 Seiten1 What Are The Major Differences Between ESX 3.5 and Vsphere?ramesh2440Noch keine Bewertungen

- 8051 Tutorial: Types of MemoryDokument6 Seiten8051 Tutorial: Types of Memorynishant205kumarNoch keine Bewertungen

- C - Dynamic Memory Allocation: Prev NextDokument13 SeitenC - Dynamic Memory Allocation: Prev NextsharadacgNoch keine Bewertungen

- Architectural Support For High Level LanguagesDokument33 SeitenArchitectural Support For High Level LanguagesUday KumarNoch keine Bewertungen

- Operating Systems Lecture Notes OS Potpourri: Martin C. RinardDokument4 SeitenOperating Systems Lecture Notes OS Potpourri: Martin C. RinardKurumeti Naga Surya Lakshmana KumarNoch keine Bewertungen

- OratopDokument16 SeitenOratopjonytapiaNoch keine Bewertungen

- Sap Pre Installation Checklist FinalDokument14 SeitenSap Pre Installation Checklist Finalzandruk40Noch keine Bewertungen

- BC0050 - Oracle & Distributed Databases - 4 Credits (Book ID: B0894)Dokument11 SeitenBC0050 - Oracle & Distributed Databases - 4 Credits (Book ID: B0894)deep4youNoch keine Bewertungen

- QuestionDokument5 SeitenQuestionArnab1386Noch keine Bewertungen

- Space Invaders TutorialDokument38 SeitenSpace Invaders TutorialcitisoloNoch keine Bewertungen

- Cache and Caching: Electrical and Electronic EngineeringDokument15 SeitenCache and Caching: Electrical and Electronic EngineeringEnock OmariNoch keine Bewertungen

- System Unit & Input/ Output Devices & Secondary StorageDokument20 SeitenSystem Unit & Input/ Output Devices & Secondary StorageSaya Munir100% (1)

- Designing An ALU: 2.1 Operations of Our ALUDokument8 SeitenDesigning An ALU: 2.1 Operations of Our ALUdarklord338Noch keine Bewertungen

- Buy Quest Products Buy Guy'S Book Buy Quest Products: Top Tips For Oracle SQL TuningDokument41 SeitenBuy Quest Products Buy Guy'S Book Buy Quest Products: Top Tips For Oracle SQL TuningLuis A. Alvarez AngelesNoch keine Bewertungen

- SAP Memory Management DocumentDokument16 SeitenSAP Memory Management DocumentSurya NandaNoch keine Bewertungen

- Funda - IIDokument33 SeitenFunda - IIalok_mishra4533Noch keine Bewertungen

- OS Viva Expected QuestionsDokument7 SeitenOS Viva Expected Questionsaamer_shahbaazNoch keine Bewertungen

- Memory and Operating System: ObjectivesDokument9 SeitenMemory and Operating System: ObjectivessignalcontrolspjNoch keine Bewertungen

- Linux 033Dokument40 SeitenLinux 033Narender GudaNoch keine Bewertungen

- Tetramax Lab 1: Automatic Test Pattern Generation (ATPG) : Computer-Aided VLSI System DesignDokument4 SeitenTetramax Lab 1: Automatic Test Pattern Generation (ATPG) : Computer-Aided VLSI System DesignJeevith PaulNoch keine Bewertungen

- Basic Stuff InterviewDokument19 SeitenBasic Stuff InterviewVamsi BonamNoch keine Bewertungen

- Memory Hir and Io SystemDokument26 SeitenMemory Hir and Io SystemArjun M BetageriNoch keine Bewertungen

- Intel 8086 MicroprocessorDokument3 SeitenIntel 8086 MicroprocessorEnock OmariNoch keine Bewertungen

- Sms 32 V 50Dokument107 SeitenSms 32 V 50Mihret SaracNoch keine Bewertungen

- Enhancements in Powercenter 8 6 To 8 5Dokument14 SeitenEnhancements in Powercenter 8 6 To 8 5saprsa1Noch keine Bewertungen

- 03 ModularizationDokument5 Seiten03 ModularizationMohamed SamirNoch keine Bewertungen

- Solution Manual Barry B BreyDokument31 SeitenSolution Manual Barry B BreyEdward Octaviano IIINoch keine Bewertungen

- Context of ProcessDokument5 SeitenContext of ProcessShivani GujralNoch keine Bewertungen

- Operating System Concepts: GovindarajanDokument55 SeitenOperating System Concepts: GovindarajanShashidhar Narayana KrishnamurthyNoch keine Bewertungen

- SQL, PL/SQL Faq About Triggers:: Insert Update DeleteDokument25 SeitenSQL, PL/SQL Faq About Triggers:: Insert Update DeleteSunil ReddyNoch keine Bewertungen

- Advanced Microprocessor NotesDokument25 SeitenAdvanced Microprocessor NotesPrashant AngirasNoch keine Bewertungen

- Memory Management - What and Where Are The Stack and Heap - Stack OverflowDokument12 SeitenMemory Management - What and Where Are The Stack and Heap - Stack OverflowtousifahmedkhanNoch keine Bewertungen

- Unix Shell Programming Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesVon EverandUnix Shell Programming Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesNoch keine Bewertungen

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationVon EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNoch keine Bewertungen

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Von EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Noch keine Bewertungen

- List of Youtube Videos Created and Shared On LPU Live APPDokument1 SeiteList of Youtube Videos Created and Shared On LPU Live APPDhiraj KapilaNoch keine Bewertungen

- General GuidelinesDokument12 SeitenGeneral GuidelinesDhiraj KapilaNoch keine Bewertungen

- Lavenstein DistanceDokument5 SeitenLavenstein DistanceDhiraj KapilaNoch keine Bewertungen

- Resume: Professional & Educational DetailsDokument3 SeitenResume: Professional & Educational DetailsDhiraj KapilaNoch keine Bewertungen

- 5 Pipelined Processor: Temporal Overlapping of Processing, Assembly LineDokument51 Seiten5 Pipelined Processor: Temporal Overlapping of Processing, Assembly LineDhiraj KapilaNoch keine Bewertungen

- Vliw ArchitectureDokument30 SeitenVliw ArchitectureDhiraj KapilaNoch keine Bewertungen

- CSE313Dokument5 SeitenCSE313Dhiraj KapilaNoch keine Bewertungen

- Prolog Lab ManualDokument160 SeitenProlog Lab Manualelfrich67% (3)

- The MESI ProtocolDokument4 SeitenThe MESI ProtocoldhirajkapilaNoch keine Bewertungen

- CS-501 Advance Software EngineeringDokument1 SeiteCS-501 Advance Software EngineeringDhiraj KapilaNoch keine Bewertungen

- General Machine StructuresDokument22 SeitenGeneral Machine StructuresDhiraj KapilaNoch keine Bewertungen

- Entrepreneurship N Innovation - G1Dokument15 SeitenEntrepreneurship N Innovation - G1Dhiraj KapilaNoch keine Bewertungen

- Knowledge Representation TechniqueDokument30 SeitenKnowledge Representation TechniqueDhiraj KapilaNoch keine Bewertungen

- Knowledge Representation and Rule Based SystemsDokument17 SeitenKnowledge Representation and Rule Based SystemsDhiraj KapilaNoch keine Bewertungen

- List of All Institute Nov. 05.11.2011Dokument10 SeitenList of All Institute Nov. 05.11.2011Dhiraj KapilaNoch keine Bewertungen