Beruflich Dokumente

Kultur Dokumente

Vlsi Lab Exercise Programs I

Hochgeladen von

Vishnu PriyaOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Vlsi Lab Exercise Programs I

Hochgeladen von

Vishnu PriyaCopyright:

Verfügbare Formate

VLSI LAB PROGRAMS

S.No List of Main Programs Exercise Programs to be done 1. Realize Half adder using Two input NAND Gates in structural model 2. Realize Half adder using Two input NOR Gates in structural Model . Realize Half su!tractor using Two input NAND Gates in structural model ". Realize Half su!tractor using Two input NOR Gates in structural model #. Design Half adder using wit$..select and %$en..else wit$ &ropagation dela's. (. Design Half su!tractor using wit$..select and %$en..else wit$ &ropagation dela's. ). Design Half su!tractor using case..w$en and Half adder using if .. t$en statements 1. Realize *ull adder using Two input NAND Gates in structural model 2. Realize *ull adder using Two input NOR Gates in structural model . Realize *ull adder using Two Half adders in structural model ". Design *ull adder using w$en..else statement wit$ a Transport dela' of "++ ns. #. Design *ull adder using if,t$en statement 1. Design *ull su!tractor using Two input NAND gates in structural model 2. Design *ull su!tractor using Two input NOR gates in structural model . Design *ull su!tractor using wit$,select statement wit$ a propagation dela' of ++ ns ". Design *ull su!tractor using case..w$en statement #. Design t$e circuit in page No. #- of .a! manual in structural model (. Design t$e circuit in page No. (+ of .a! manual in structural model 1. Design 1 !it comparator using NAND gates in structural model 2. Design 1 !it comparator using NOR gates in structural model . Design 1 !it comparator using wit$..select statement ". Design 1 !it comparator using nested if statement #. Design " !it comparator using structural model (. Design " !it comparator using for,generate statement in structural model

1.

a!f Adder " S#btractor

$.

%#!! Adder

&.

%#!! S#btractor

'.

(om)arator

*.

M#!ti)!exer

+.

,ecoder

-.

N. Bit adder

/.

Priorit0 encoder

). Design " !it comparator using if,generate statement in structural model 1. Design " /1 Mu0 using case..w$en and w$en..else statements 2. Design 1/1 Mu0 using wit$,select and nested if statements. . Design "/1 Mu0 wit$ logic gates using structural model ". Design Half adder using two 2/1 Mu0es in structural model #. Design Half su!tractor using two 2 / 1 Mu0es in structural model (. Design *ull adder wit$ two " / 1 Mu0es in structural model ). Design *ull su!tractor wit$ two " / 1 Mu0es in structural model 1. Design t$e following 2O& e0pression using 1 / 1 Mu0 *3A45464D7 8 9 324 4#4)4-41141 41#7 -. Design 1(/1 Mu0 wit$ two 1/1 Mu0es 1. Design /1 Decoder using nested if and w$en..else statements 2. Design "/1( Decoder wit$ /1 decoders using structural model . Design 2/" decoder using case..w$en statement ". :mplement "/1( decoder using 2/" decoders in structural model #. Design 2/" decoder and "/1( decoder using .;T approac$ (. Design "/1( decoder wit$ logic gates using structural model ). Design t$e following 2O& e0pression using /1 decoder *3A45464D7 8 9 31424 4#4(7 1. Design #/ 2 decoder using /1 decoders 1. Design " !it adder using *ull adders in structural model 2. Design " !it adder using for..generate in structural model . Design " !it adder using if..generate in structural model ". Design 1 !it adder using " !it adders in structural model #. Design 2 !it adder wit$ " !it adders using for,generate in structural model (. Design " !it adder< 2u!tractor using structural model 1. Design "/2 encoder using case..w$en and w$en..else statements. :nputs Output D+ D1 D2 D =1 =+ 1 + + + + + > 1 + + + 1 > > 1 + 1 + > > > 1 1 1 2. Design a 1/ encoder using logic gates wit$ structural model . Design a 1/ priorit' encoder wit$ following trut$ ta!le ;sing structural model as well as using if.. statements

1.

%!i).%!o)s

12.

S3ift registers

:nputs Output D+ D1 D2 D D" D# D( D) > = ? 1 + + + + + + + + + + > 1 + + + + + + + + 1 > > 1 + + + + + + 1 + > > > 1 + + + + + 1 1 > > > > 1 + + + 1 + + > > > > > 1 + + 1 + 1 > > > > > > 1 + 1 1 + > > > > > > > 1 1 1 1 1. Design @AB *<*4 2AR *<*4 T *<* and D *<* using nested if statements 2. Design @AB *lip flop using NAND gates and 2R flip flop using NOR gates in structural model . %rite a CHD. coding for realizing clocDed @B flip flop using NAND gates along wit$ preset and clear action. ". Design D flip flop and T *lip flops using if statement #. Design master slaEe D flip flop and Eerif' t$e result. Design Master slaEe @AB *<* using structural model 1. Design a " !it 2:&O and &:2O s$ift registers using D *<*s in structural model 2. Design " !it 2:&O42:2O4&:2O and &:&O using nested if statements . Design 1 !it 2:&O and &:2O s$ift registers using D flip flops in structural model ". Design !arrel s$ifter using structural model #. Design a "!it uniEersal s$ift register. 1.Design "!it ripple counter using D *lip flop using structural model and Eerif' t$e result. 2. Design "!it up<down counter using T flip flop wit$ structural model and Eerif' t$e result. . Design # !it up<down counter t$at counts from +++++ to 1+111 and t$en decrements to +++++ using nested if statement. ". Generate a clocD signal wit$ freFuenc' (+BHz and dut' c'cle 2#<)#. Assume t$e input clocD c'cle period as 2#ns. 1.%rite a CHD. coding for a " !it !inar' arra' Multiplier using structural model and Eerif' t$e result. 2. %rite a CHD. coding for "!it 0 !it !inar' Multiplier using structural model and Eerif' t$e result. .%rite a CHD. coding for " !it 5aug$ %oole' Multiplier using structural model and Eerif' t$e result.

11.

(o#nters

1$.

M#!ti)!ier

". %rite a CHD. coding for "!it 5raun Multiplier using structural model and Eerif' t$e result.

Das könnte Ihnen auch gefallen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5795)

- Mudatkaratha MothagamDokument2 SeitenMudatkaratha MothagamVishnu PriyaNoch keine Bewertungen

- Omics: Vamue Rapep Gornts Ginpty " "Dokument1 SeiteOmics: Vamue Rapep Gornts Ginpty " "Vishnu PriyaNoch keine Bewertungen

- Hotel Management System - od-revHEAD - svn001.TmpDokument1 SeiteHotel Management System - od-revHEAD - svn001.TmpVishnu PriyaNoch keine Bewertungen

- Neural Sec B ConsolidatedDokument4 SeitenNeural Sec B ConsolidatedVishnu PriyaNoch keine Bewertungen

- III&IV Unit Two MarksDokument8 SeitenIII&IV Unit Two MarksVishnu PriyaNoch keine Bewertungen

- IM Set2Dokument2 SeitenIM Set2Vishnu PriyaNoch keine Bewertungen

- Employee and DepartmentDokument2 SeitenEmployee and DepartmentVishnu PriyaNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Large List of Intel Interview QuestionsDokument4 SeitenLarge List of Intel Interview QuestionsvaghelamiralNoch keine Bewertungen

- Irs 2453 DDokument18 SeitenIrs 2453 DMallickarjunaNoch keine Bewertungen

- Course Handout: Amity University RajasthanDokument5 SeitenCourse Handout: Amity University RajasthanKaran MaanNoch keine Bewertungen

- Latches and Flipflops: Presented By: Pankaj Pratim Hazarika Etc 5 SemesterDokument11 SeitenLatches and Flipflops: Presented By: Pankaj Pratim Hazarika Etc 5 SemesterPankaj Pratim HazarikaNoch keine Bewertungen

- High Speed Vlsi DesignDokument93 SeitenHigh Speed Vlsi DesignDr Narayana Swamy RamaiahNoch keine Bewertungen

- Embeded PU ComputerDokument188 SeitenEmbeded PU ComputerLoknath RegmiNoch keine Bewertungen

- Lec Verilog TrafficLight SynthesisDokument32 SeitenLec Verilog TrafficLight SynthesisKartikey ManchandaNoch keine Bewertungen

- FPGA Architecture SulochanaDokument38 SeitenFPGA Architecture SulochanaGagandeep Singh DhingraNoch keine Bewertungen

- Harolds Discrete Math Flip Flops Cheat Sheet 2020Dokument6 SeitenHarolds Discrete Math Flip Flops Cheat Sheet 2020Nandini JayakumarNoch keine Bewertungen

- Microprocessor and Microcomputer TechnologyDokument11 SeitenMicroprocessor and Microcomputer TechnologyGabrielBravoNoch keine Bewertungen

- SNUG Design Tips PaperDokument46 SeitenSNUG Design Tips PapersujaataNoch keine Bewertungen

- A Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode SimulationDokument30 SeitenA Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode Simulationiarcad9403Noch keine Bewertungen

- Datasheet Eprom ST 95080 95160 95320 95640Dokument20 SeitenDatasheet Eprom ST 95080 95160 95320 95640Patrick Roncato BritoNoch keine Bewertungen

- 8086 Microprocessor Interfacing: Dr.P.Yogesh, Senior Lecturer, DCSE, CEG Campus, Anna University, Chennai-25Dokument40 Seiten8086 Microprocessor Interfacing: Dr.P.Yogesh, Senior Lecturer, DCSE, CEG Campus, Anna University, Chennai-25Janu100% (2)

- PLC Instructions IIT-DelhiDokument40 SeitenPLC Instructions IIT-DelhiVikashKeshavNoch keine Bewertungen

- 1.define Placement in Physical Design?Dokument7 Seiten1.define Placement in Physical Design?srajeceNoch keine Bewertungen

- Assignment#1Dokument4 SeitenAssignment#1huzaifaalisiddiqui2700% (1)

- Physics Project FileDokument14 SeitenPhysics Project FileSrutanik BhaduriNoch keine Bewertungen

- AT89C55Dokument5 SeitenAT89C55Vani PavuluruNoch keine Bewertungen

- Spartan 6 FPGA Configurable Logic BlockDokument58 SeitenSpartan 6 FPGA Configurable Logic BlockG30nyNoch keine Bewertungen

- HAT552 HAT553 enDokument35 SeitenHAT552 HAT553 enLinh Ngo NhatNoch keine Bewertungen

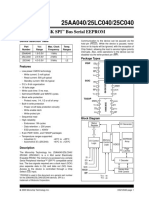

- 25AA040/25LC040/25C040: 4K Spi Bus Serial EEPROMDokument22 Seiten25AA040/25LC040/25C040: 4K Spi Bus Serial EEPROMAgustin AndrokaitesNoch keine Bewertungen

- PMA TB40 1 TemperatureLimiter Manual English 9499 040 93411Dokument32 SeitenPMA TB40 1 TemperatureLimiter Manual English 9499 040 93411Angelito_HBKNoch keine Bewertungen

- Daf Trener TavDokument8 SeitenDaf Trener Tavtri saksonoNoch keine Bewertungen

- + GRAFCET Translate From - Fr.en PDFDokument41 Seiten+ GRAFCET Translate From - Fr.en PDFHamdam NazarovNoch keine Bewertungen

- PDFDokument38 SeitenPDFप्रमोद म्हसेNoch keine Bewertungen

- Habit Manual Chase Bliss PedalDokument28 SeitenHabit Manual Chase Bliss PedalAdam AshforthNoch keine Bewertungen

- A Fully Analog 5Gb/s Clock-and-Data Recovery Circuit in 90nm CMOSDokument19 SeitenA Fully Analog 5Gb/s Clock-and-Data Recovery Circuit in 90nm CMOSJan SenNoch keine Bewertungen

- Comparison of UCA 2Dokument6 SeitenComparison of UCA 2gjd2008Noch keine Bewertungen

- Vlsi Rec 7th Sem VtuDokument50 SeitenVlsi Rec 7th Sem VtuSagar S Poojary100% (1)