Beruflich Dokumente

Kultur Dokumente

Vlsi Design ECE5014

Hochgeladen von

SriramOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Vlsi Design ECE5014

Hochgeladen von

SriramCopyright:

Verfügbare Formate

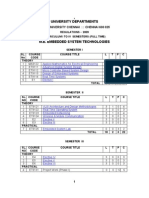

KALASALINGAM UNIVERSITY

(KALASALINGAM ACADEMY OF RESEARCH AND EDUCATION) DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

COURSE PLAN

Academic Year Course Code Course Name Year/Semester/Branch

: : : :

2010-2011 ECE5014 VLSI Design IV/VII/ECE 3-0-0 3 Sriram Sundar.S Sriram Sundar.S

Lecture-Tutorial-Practical : Credits Course coordinator Course instructor : : :

1.

Pre-requisite:

Students are expected to have knowledge in Digital logic & MOS transistor theory.

2.

1. 2. 3. 4.

Objectives:

Objective of the course is To teach the students about the issues involved in the custom design of digital circuits. To review CMOS processes and teach the students about static & dynamic logic. To teach the students about low-power design at both the system and unit level. To give the student experience doing a significant design using mask-level layout tools and from written specifications.

3.

Learning outcome and end use:

At the end of the course the student must be able to 1. Create models of moderately sized CMOS circuits that realize specified digital functions. 2. Apply CMOS technology-specific layout rules in the placement and routing of transistors and interconnect, and to verify the functionality, timing, power, and parasitic effects.

4.

Sl. No. T1

Text Books:

Author Names Neil H E Weste, Kamran Eshranghian Books Title Principles of CMOS VLSI Design : A System Perspective Publisher Name Addison Wesley Edition 2nd edition, 2002

5.

Sl. No. R1 R2 R3 R4

Reference Books:

Authors Douglas A Pucknell, Kamran Eshranghian Wayne Wolf Amar Mukerjee Caver Mead, Lynn Conway Books Title Basic VLSI Design Modern VLSI Design Introduction to NMOS and CMOS VLSI System Design, Introduction to VLSI Systems Publisher PHI Pearson Education PHI Addison Wesley Edition 3rd Edition, 2004 1997 1986 1980

6.

Sl. No. W1

Web resources:

Topic Name wafer processing, CMOS Technology Web Resource

W2

1. http://www.me.gatech.edu/jonathan.colton/me4210/waferproc.pdf 2. http://www.aw-bc.com/info/weste/assets/downloads/ch1.pdf 3. http://www.rose-hulman.edu/~simoni/Classes/EC551/MOSFab /invfab3d.pdf 1. http://bwrc.eecs.berkeley.edu/Classes/icdesign/ee141_s02/notes.html CMOS Design 2. http://www.eee.metu.edu.tr/~askar/EE618/CMOS%20Design%20Rules. rules pdf 3. http://www3.hmc.edu/~harris/cmosvlsi/4e/index.html

Sl. No. W3 W4 W5 W6

Topic Name

Web Resource 1. http://people.bu.edu/rknepper/sc571/chapter1_files/index.html

Threshold voltage VLSI Course materials ppt nptel

1. http://people.bu.edu/rknepper/sc571/chapter2_files/lecture2_A_file s/v3_document.htm http://inst.eecs.berkeley.edu/~cs250/fa09/lectures/ 1. http://nptel.iitm.ac.in/video.php?courseId=1004&p=1 2. http://nptel.iitm.ac.in/courses/Webcourse-contents/IIT-%20Guwahati /ic_tech/index.html

7.

Topic No.

Lesson Plan:

Topic Name Unit- I Overview Text Books Number of Periods Cumulative Periods

1 2 3 4 5 6 7 8 9 10 11 12 13

VLSI Design Process Architectural Design Logical Design Physical Design Layout Styles, Full Custom Semi Custom approaches Overview of wafer fabrication wafer processing Silicon gate NMOS process CMOS process N well P well Twin Tub Silicon On Insulator NMOS and PMOS enhancement transistors Threshold voltage MOS device equations Basic DC equations Second order effect Small signal AC characteristics NMOS and CMOS inverter Inverter delay Pass Transistor Transmission gate Need for design rules Mead Conway design rules for the Silicon gate NMOS process CMOS N well / P well design rules Sheet resistance Area Capacitance Wiring Capacitance

T1 T1 T1 T1 T1 T1 T1 T1 T1 T1 T1 T1 T1

1 1 2 1 1 1 1 1 2 1 1 1 1

1 2 4 5 6 7 8 9 11 12 13 14 15

Unit- II Basic Electrical Properties of MOS And CMOS Circuits

Unit- III Layout Design Rules 14 15 16 17 T1, R4 T1, R4 T1, R4 T1, R4 2 2 2 1 17 19 21 22

Topic No. 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33

Topic Name Unit- IV Logic Design Switch logic- Gate Logic Inverter Two input NAND and NOR gate- Other forms of CMOS logic Dynamic CMOS logic Clocked CMOS logic Pre-charged domino CMOS logic Structure Design Simple combinational logic design examples Parity generator Multiplexer Clocked sequential circuits 2 Phase clocking Charge storage Dynamic Register Element NMOS and CMOS dynamic shift register. Design of a 4 bit shifter 4 bit arithmetic processor ALU Subsystem Implementing ALU functions with an Adder Carry look ahead adders Multipliers Serial/ Parallel Multipliers Pipelined multiplier array Modified booths algorithm high density memory FSM PLA Control Implementation.

Text Books T1 T1 T1 T1 T1 T1 T1 T1 T1 T1 T1 T1 T1 T1 T1 T1

Number of Periods 2 1 1 1 1 1 1 1 1 1 1 1 2 2 1 1

Cumulative Periods 24 25 26 27 28 29 30 31 32 33 34 35 37 39 40 41

Unit- V Sub System Design Process

8.

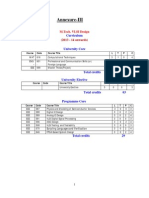

Portions for sessional examination I, II:

Sessional Examination I Sessional Examination II Title I, II Title III, IV

9.

i. ii. iii.

Related Magazines / Journals:

IEEE Transactions on Very Large Scale Integration Systems. IEEE Journal of Solid-State Circuits. Integration, the VLSI Journal (Elsevier).

10. Industries that can be visited / In-plant training:

i. ii. iii. Cadence Design Systems, Bangalore. SITAR (Society for Integrated Circuit Technology and Applied Research), Bangalore. Texas Instruments IC design center in Bangalore.

11. Related Experiments / projects:

i. ii. Designing a CMOS 16-Bit Parallel Adder Layout design of CMOS 4-Bit Ripple Counter

12. Evaluation Plan:

Sessional Examination I Sessional Examination II End Semester Examination Assignments / Quizzes / Tutorials 20% 20% 50% 10%

Prepared by

Verified by

Sriram Sundar.S

HoD/E.C.E (Dr.S.Durairaj)

Das könnte Ihnen auch gefallen

- OutlineDokument1 SeiteOutlineVarg VikernesNoch keine Bewertungen

- The System Designer's Guide to VHDL-AMS: Analog, Mixed-Signal, and Mixed-Technology ModelingVon EverandThe System Designer's Guide to VHDL-AMS: Analog, Mixed-Signal, and Mixed-Technology ModelingBewertung: 5 von 5 Sternen5/5 (1)

- SyllabusDokument44 SeitenSyllabusRekha ThomasNoch keine Bewertungen

- Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015Dokument2 SeitenEce5015 Digital-Ic-Design Eth 1.0 40 Ece5015Sivanantham SadhasivamNoch keine Bewertungen

- Networks-on-Chip: From Implementations to Programming ParadigmsVon EverandNetworks-on-Chip: From Implementations to Programming ParadigmsNoch keine Bewertungen

- Mtech Electronics Syllabus VTUDokument48 SeitenMtech Electronics Syllabus VTUmuqeetmmaNoch keine Bewertungen

- Modern Component Families and Circuit Block DesignVon EverandModern Component Families and Circuit Block DesignBewertung: 5 von 5 Sternen5/5 (1)

- Syllabus MecveDokument44 SeitenSyllabus MecveronpeterpNoch keine Bewertungen

- Embedded Systems: Analysis and Modeling with SysML, UML and AADLVon EverandEmbedded Systems: Analysis and Modeling with SysML, UML and AADLFabrice KordonNoch keine Bewertungen

- EEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Dokument2 SeitenEEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Harsha DuttaNoch keine Bewertungen

- Handbook of Fiber Optic Data Communication: A Practical Guide to Optical NetworkingVon EverandHandbook of Fiber Optic Data Communication: A Practical Guide to Optical NetworkingBewertung: 1 von 5 Sternen1/5 (1)

- DEE6113 Course Outline Jun2016Dokument4 SeitenDEE6113 Course Outline Jun2016FonzBahariNoch keine Bewertungen

- Ece MT SylDokument79 SeitenEce MT Sylpermiable permissionNoch keine Bewertungen

- Top-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsVon EverandTop-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsNoch keine Bewertungen

- ME VLSI & EmdDokument58 SeitenME VLSI & EmdAnil V. WalkeNoch keine Bewertungen

- Petri Nets: Fundamental Models, Verification and ApplicationsVon EverandPetri Nets: Fundamental Models, Verification and ApplicationsNoch keine Bewertungen

- Handout of EEE F 313 (Analog Digital VLSI Design)Dokument3 SeitenHandout of EEE F 313 (Analog Digital VLSI Design)bits_who_am_iNoch keine Bewertungen

- Embedded System Design and IC Technology Course DetailsDokument24 SeitenEmbedded System Design and IC Technology Course DetailsHannan SatopayNoch keine Bewertungen

- M E EmbeddedSystemTechnologiesDokument31 SeitenM E EmbeddedSystemTechnologiesRohini BabuNoch keine Bewertungen

- M.E. Computer Science and Engineering Curriculum and SyllabusDokument58 SeitenM.E. Computer Science and Engineering Curriculum and SyllabuspajadhavNoch keine Bewertungen

- Sri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsDokument122 SeitenSri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsRAAJ KISHOR R HNoch keine Bewertungen

- 18-M.Tech (VLSI Design and Embedded System) PDFDokument31 Seiten18-M.Tech (VLSI Design and Embedded System) PDFAhilan AppathuraiNoch keine Bewertungen

- Me Gtu CurriculumDokument47 SeitenMe Gtu CurriculumAnupam DevaniNoch keine Bewertungen

- M.Tech 2nd SemesterDokument14 SeitenM.Tech 2nd SemesterSivaramsharma RupavathamNoch keine Bewertungen

- BECE303LDokument3 SeitenBECE303LKAVIYA DIASNoch keine Bewertungen

- UntitledDokument12 SeitenUntitledSathiyaraj MurugarajNoch keine Bewertungen

- NIT 1 4 7040 Lecture 1 VLSI EC601Dokument26 SeitenNIT 1 4 7040 Lecture 1 VLSI EC601SANDIP PODDARNoch keine Bewertungen

- Vlsi NotesDokument5 SeitenVlsi NotesDiwakar TiwaryNoch keine Bewertungen

- MicroelectronicsDokument39 SeitenMicroelectronicsArun Av0% (1)

- VLSI M.Tech SyllabusDokument14 SeitenVLSI M.Tech SyllabusdannycbsNoch keine Bewertungen

- Anna University Chennai Affiliated Institutions Regulations 2013 ME VLSI Design I-IV Semesters Curriculum and SyllabusDokument33 SeitenAnna University Chennai Affiliated Institutions Regulations 2013 ME VLSI Design I-IV Semesters Curriculum and Syllabusprinceram123Noch keine Bewertungen

- r19 Mtech Emb Full-10-19Dokument10 Seitenr19 Mtech Emb Full-10-19saikanna427Noch keine Bewertungen

- M.E. (Embedded System Technologies)Dokument37 SeitenM.E. (Embedded System Technologies)Priya DarshiniNoch keine Bewertungen

- Signature of The Chairman BOS M.E (AE) : KCT-M.E (AE) - I To IV Semester Curriculum and Syllabus R - 2009Dokument48 SeitenSignature of The Chairman BOS M.E (AE) : KCT-M.E (AE) - I To IV Semester Curriculum and Syllabus R - 2009vickyskarthikNoch keine Bewertungen

- UntitledDokument2 SeitenUntitledDr. M Kiran KumarNoch keine Bewertungen

- Training Project of VLSIDokument52 SeitenTraining Project of VLSISYED MOHAMMAD FAIZNoch keine Bewertungen

- Teaching VLSI Design Using Industry ToolsDokument11 SeitenTeaching VLSI Design Using Industry ToolsaswinjohnNoch keine Bewertungen

- Vlsi DesignDokument2 SeitenVlsi DesignShribala NagulNoch keine Bewertungen

- VLSI Design Important Questions and AnswersDokument134 SeitenVLSI Design Important Questions and AnswersDelphin ShibinNoch keine Bewertungen

- Me Eee Es R13Dokument42 SeitenMe Eee Es R13Revathy VijayanNoch keine Bewertungen

- Embedded System Lession PlanDokument4 SeitenEmbedded System Lession PlanMATHANKUMAR.SNoch keine Bewertungen

- VLSI Design Course OutlineDokument3 SeitenVLSI Design Course OutlineSoftware EngineerNoch keine Bewertungen

- Vit Ece 5th Year SyllabusDokument16 SeitenVit Ece 5th Year Syllabuspranavateja12399Noch keine Bewertungen

- r19 Mtech Emb Full-30-39Dokument10 Seitenr19 Mtech Emb Full-30-39saikanna427Noch keine Bewertungen

- Vlsi DesignDokument3 SeitenVlsi DesignGokulNoch keine Bewertungen

- Be Cse SyllabusDokument32 SeitenBe Cse SyllabusMayuresh MagarNoch keine Bewertungen

- Vlsi 1Dokument24 SeitenVlsi 1hrrameshhrNoch keine Bewertungen

- VLSI Syllabus 2013-14Dokument43 SeitenVLSI Syllabus 2013-14Eric DharanNoch keine Bewertungen

- VLSI SyllabusDokument57 SeitenVLSI SyllabusAkshay DeshpandeNoch keine Bewertungen

- Embedded System TechnologiesDokument37 SeitenEmbedded System TechnologiesjayaprahasNoch keine Bewertungen

- Design CMOS Logic Gate LayoutDokument4 SeitenDesign CMOS Logic Gate LayoutHieu Nguyen TriNoch keine Bewertungen

- Analog VLSI Design: Technology TrendsDokument25 SeitenAnalog VLSI Design: Technology TrendsSathyaNarasimmanTiagarajNoch keine Bewertungen

- CMOS VLSI and Aspect of ASIC DesignDokument3 SeitenCMOS VLSI and Aspect of ASIC DesignBittU BhagatNoch keine Bewertungen

- Be Cse 201617Dokument33 SeitenBe Cse 201617Shubham JagdaleNoch keine Bewertungen

- Subjects & Syllabus 2014-2015 M.techDokument9 SeitenSubjects & Syllabus 2014-2015 M.techvinjamurisivaNoch keine Bewertungen

- Low Cost Vlsi Design: A Paper Presentation OnDokument16 SeitenLow Cost Vlsi Design: A Paper Presentation OnSrinivas HeroNoch keine Bewertungen

- M.E. Vlsi Design: Anna University of Technology Madurai MADURAI - 625002 Regulations 2010 Curriculam & SyllabiDokument34 SeitenM.E. Vlsi Design: Anna University of Technology Madurai MADURAI - 625002 Regulations 2010 Curriculam & SyllabikumaranrajNoch keine Bewertungen

- Circuit Theory 2014 - Apr MayDokument6 SeitenCircuit Theory 2014 - Apr MaySriramNoch keine Bewertungen

- Wireless Communication - EC 2401 - I - Answer KeyDokument9 SeitenWireless Communication - EC 2401 - I - Answer KeySriramNoch keine Bewertungen

- EC8661 VLSI Design LaboratoryDokument53 SeitenEC8661 VLSI Design LaboratorySriram100% (4)

- MeasurementsDokument12 SeitenMeasurementsSriramNoch keine Bewertungen

- Ec6512 Communication Systems Laboratory ManuslDokument86 SeitenEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- What Determines The Color of An LED?: SemiconductingDokument1 SeiteWhat Determines The Color of An LED?: SemiconductingSriramNoch keine Bewertungen

- EC6612 - VLSI Design Laboratory ManualDokument39 SeitenEC6612 - VLSI Design Laboratory ManualSriramNoch keine Bewertungen

- 2014 - Apr May PDFDokument4 Seiten2014 - Apr May PDFSriramNoch keine Bewertungen

- VLSI Design Lab EC-6612-nDokument58 SeitenVLSI Design Lab EC-6612-nSriramNoch keine Bewertungen

- EC6702Dokument2 SeitenEC6702SriramNoch keine Bewertungen

- Design Entry and Simulation of Sequential CircuitsDokument7 SeitenDesign Entry and Simulation of Sequential CircuitsSriramNoch keine Bewertungen

- Ec6512 Communication Systems Laboratory ManuslDokument86 SeitenEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- Data Path Circuits - EC6601Dokument10 SeitenData Path Circuits - EC6601SriramNoch keine Bewertungen

- Principles of Management: Lesson PlanDokument23 SeitenPrinciples of Management: Lesson PlanSriram100% (1)

- Sensors: SL - N o Application Sensor Example PriceDokument6 SeitenSensors: SL - N o Application Sensor Example PriceSriramNoch keine Bewertungen

- Ec 6501Dokument1 SeiteEc 6501SriramNoch keine Bewertungen

- EC2354 - VLSI DesignDokument2 SeitenEC2354 - VLSI DesignSriramNoch keine Bewertungen

- DSP WorkshopDokument2 SeitenDSP WorkshopSriramNoch keine Bewertungen

- SEMESTER Requirements Lab EquipmentDokument29 SeitenSEMESTER Requirements Lab EquipmentSriramNoch keine Bewertungen

- Ec2357 - Vlsi Design LaboratoryDokument45 SeitenEc2357 - Vlsi Design LaboratorySriramNoch keine Bewertungen

- Concept MapDokument18 SeitenConcept MapSriramNoch keine Bewertungen

- ECE Department Course DetailsDokument151 SeitenECE Department Course DetailsSriramNoch keine Bewertungen

- Verilog Course ManualDokument60 SeitenVerilog Course ManualSriramNoch keine Bewertungen

- Ece 2013Dokument14 SeitenEce 2013SriramNoch keine Bewertungen

- VerilogDokument12 SeitenVerilogSriramNoch keine Bewertungen

- Ece 2008Dokument27 SeitenEce 2008SriramNoch keine Bewertungen

- Analog DesignDokument4 SeitenAnalog DesignSriramNoch keine Bewertungen

- Verilog Lab ProgramsDokument25 SeitenVerilog Lab ProgramsSriramNoch keine Bewertungen

- Kalasalingam University ECE302 Analog Communication Question BankDokument6 SeitenKalasalingam University ECE302 Analog Communication Question BankSriramNoch keine Bewertungen

- VerilogDokument12 SeitenVerilogSriramNoch keine Bewertungen

- Teaching Vocabulary 1. Decisions About Content What Vocabulary To Teach: Criteria For SelectionDokument9 SeitenTeaching Vocabulary 1. Decisions About Content What Vocabulary To Teach: Criteria For SelectionIoana AlexandraNoch keine Bewertungen

- Linking Religion Spirituality With Well BeingDokument17 SeitenLinking Religion Spirituality With Well BeingLou BwoyNoch keine Bewertungen

- Sufism: Philosophy and Practices: 'Tasawwuf, QuranDokument21 SeitenSufism: Philosophy and Practices: 'Tasawwuf, QuranAbdoul Hakim BeyNoch keine Bewertungen

- Merit of The Mass (Fr. Ripperger, F.S.S.P.)Dokument12 SeitenMerit of The Mass (Fr. Ripperger, F.S.S.P.)Richard Aroza100% (5)

- The Wild Boy of AveyronDokument9 SeitenThe Wild Boy of AveyronVIA BAWINGANNoch keine Bewertungen

- Understanding The Self Lesson 1-7Dokument19 SeitenUnderstanding The Self Lesson 1-7Gaille Go100% (1)

- 2006 James Ruse 4 UnitDokument24 Seiten2006 James Ruse 4 UnitGeovanny GandyNoch keine Bewertungen

- ManidweepamDokument177 SeitenManidweepamBrandon Stephens100% (1)

- 12 Concepts 2Dokument2 Seiten12 Concepts 2api-27959641Noch keine Bewertungen

- Excel How To SumDokument3 SeitenExcel How To SumcarlosnestorNoch keine Bewertungen

- Zechariah: The Nations Will Worship The LordDokument15 SeitenZechariah: The Nations Will Worship The LordLola Richey0% (1)

- Any WayDokument23 SeitenAny WaymariaagaNoch keine Bewertungen

- The Protean Quality of Sub Cultural ConsumptionDokument21 SeitenThe Protean Quality of Sub Cultural ConsumptionNick BrettNoch keine Bewertungen

- PWT Chords (English-Tagalog) EDIT Dec-16 PDFDokument79 SeitenPWT Chords (English-Tagalog) EDIT Dec-16 PDFChristine Joy Manguerra RabiNoch keine Bewertungen

- Database Management Systems: Dont Do Research On Any TopicDokument38 SeitenDatabase Management Systems: Dont Do Research On Any Topicmaruthi631Noch keine Bewertungen

- Release Technique Newletter Aug 2015Dokument58 SeitenRelease Technique Newletter Aug 2015hanako1192100% (1)

- Hailu Worku - LuluDokument112 SeitenHailu Worku - Luluhailu123Noch keine Bewertungen

- Role of Parents in The Development of PwIDDsDokument18 SeitenRole of Parents in The Development of PwIDDsBild Andhra PradeshNoch keine Bewertungen

- IUB EMBA Letter of Recommendation for Rahad AhmedDokument6 SeitenIUB EMBA Letter of Recommendation for Rahad Ahmedzainul_abdin_1Noch keine Bewertungen

- 5076 5077 5078 - 2014Dokument49 Seiten5076 5077 5078 - 2014Lin Emancipation0% (1)

- Uranian Astrology For Beginners Lesson 1Dokument5 SeitenUranian Astrology For Beginners Lesson 1Valentin BadeaNoch keine Bewertungen

- Historical Periods in Film StudiesDokument2 SeitenHistorical Periods in Film StudiesFLAKUBELANoch keine Bewertungen

- Montesquieu's Influence on the Doctrine of Separation of PowersDokument24 SeitenMontesquieu's Influence on the Doctrine of Separation of PowersRewant MehraNoch keine Bewertungen

- Let's Check! ULO - ADokument4 SeitenLet's Check! ULO - AMelrose LopezNoch keine Bewertungen

- X Icse Physics Note-4 Work, Energy & PowerDokument3 SeitenX Icse Physics Note-4 Work, Energy & PowerPeggy BellNoch keine Bewertungen

- A Dynamic Theory of Organizational Knowledge Creation: Ikujiro NonakaDokument25 SeitenA Dynamic Theory of Organizational Knowledge Creation: Ikujiro NonakaDenton ColeNoch keine Bewertungen

- Sense Relations Between WordsDokument53 SeitenSense Relations Between WordsLe Tuyet NhiNoch keine Bewertungen

- BSCE Term Paper on Improving English SkillsDokument2 SeitenBSCE Term Paper on Improving English Skillsjanz13Noch keine Bewertungen

- Lesson Plan Poem MicroteachingDokument7 SeitenLesson Plan Poem MicroteachingSolehah Rodze100% (1)

- IGNOU BSHF Question Paper December 2015Dokument6 SeitenIGNOU BSHF Question Paper December 2015Telika RamuNoch keine Bewertungen