Beruflich Dokumente

Kultur Dokumente

VHDL Code

Hochgeladen von

SriramOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

VHDL Code

Hochgeladen von

SriramCopyright:

Verfügbare Formate

Coding for to detect the sequence 110111 using VHDL: library ieee; use ieee.std_logic_1164.

all; entity seq_detector is port (x,clk,clr : in std_logic; z: out std_logic); end seq_detector; architecture detector of seq_detector is component my_dffbehavior port (d,clk,clr : in std_logic; q,qbar : inout std_logic); end component; signal d: std_logic_vector (1 to 3); signal y,yb: std_logic_vector (1 to 3); begin -- Excitation Input values for the flip-flops d(1) <= ( (y(2) and (not y(1)) and (not x)) or ((not y(2)) and (not y(1)) and x) ); d(2)<= ( (y(2) and (not y(1))) or (y(3) and y(1)) or ((not y(2)) and y(1) and x)); d(3) <= ( (y(2) and y(1) and x) or (y(3) and (not y(1)) and x)); -- Output of the flip-flops a1 : my_dffbehavior port map (d(1),clk,clr,y(1),yb(1)); a2 : my_dffbehavior port map (d(2),clk,clr,y(2),yb(2)); a3 : my_dffbehavior port map (d(3),clk,clr,y(3),yb(3)); -- Output function for the sequence detection z <= (y(3) and y(1) and x) after 1 ns; -- after 1 ns represents the delay to produce the output end detector;

Coding for the D Flip-Flop: library ieee; use ieee.std_logic_1164.all; entity my_dffbehavior is port (d,clk,clr : in std_logic; q,qbar : inout std_logic); end my_dffbehavior; architecture my_dffbehaviorarch of my_dffbehavior is begin process (d,clk,clr) begin if (clr = '1') then if (rising_edge (clk)) then q <= d; qbar <= not (d);

end if; else q <= '0'; qbar <= '1'; end if; end process; end my_dffbehaviorarch;

Coding for to detect the sequence 110111 using Verilog: module seq_detector (z,x,clk,reset); output z; input x,clk,reset; wire [1:8] t; -- To represent the minterms present in the flip-flop inputs wire [1:3] d; -- To represent the flip-flop excitation inputs wire [1:3]y; -- To represent the flip-flop true outputs wire [1:3]yb; -- To represent the flip-flop complement outputs wire xb; not g1(yb[1],y[1]); not g2(yb[2],y[2]); not g3(yb[3],y[3]); not g4(xb,x); and g5(t[1],y[2],yb[1],xb); and g6(t[2],yb[2],yb[1],x); and g7(t[3],y[3],y[1],xb); and g8(t[4],y[2],yb[1]); and g9(t[5],y[3],y[1]); and g10(t[6],yb[2],y[1],x); and g11(t[7],y[2],y[1],x); and g12(t[8],y[3],yb[1],x); or (d[1],t[1],t[2],t[3]); or (d[2],t[4],t[5],t[6]); or (d[3],t[7],t[8]); my_dffbehaviorvlog ff1 (y[1],yb[1],d[1],clk,reset); -- D1 flip-flop output my_dffbehaviorvlog ff2 (y[2],yb[2],d[2],clk,reset); -- D2 flip-flop output my_dffbehaviorvlog ff3 (y[3],yb[3],d[3],clk,reset); -- D3 flip-flop output and #10 (z,y[3],y[1],x); // delay '50'ns; -- Sequence Detector output endmodule -- t[1] to t[3] for D1 flip-flop minterms -- t[4] to t[6] for D2 flip-flop minterms -- t[7] to t[8] for D3 flip-flop minterms

-- Coding for the D Flip-Flop: module my_dffbehaviorvlog(q,qbar,d,clk,clr); output q,qbar;

input d,clk,clr; reg q,qbar; always @ (clr or negedge clk) begin if (~clr) begin q = 1'b0; qbar = 1'b1; end else begin q = d; assign qbar = ~q; end end endmodule

Das könnte Ihnen auch gefallen

- The Spectral Theory of Toeplitz Operators. (AM-99), Volume 99Von EverandThe Spectral Theory of Toeplitz Operators. (AM-99), Volume 99Noch keine Bewertungen

- 3 Bit Asynchronous Counter Using JK Flip Flop: Program VHDLDokument4 Seiten3 Bit Asynchronous Counter Using JK Flip Flop: Program VHDLsanthiniNoch keine Bewertungen

- Combinatorial Algorithms: For Computers and CalculatorsVon EverandCombinatorial Algorithms: For Computers and CalculatorsBewertung: 4 von 5 Sternen4/5 (2)

- Digital Lab Cs 6211 VHDL ProgramsDokument13 SeitenDigital Lab Cs 6211 VHDL ProgramsMurugan GNoch keine Bewertungen

- Kow Lpic Da 2Dokument10 SeitenKow Lpic Da 2varshasrinithiNoch keine Bewertungen

- Tables of Coulomb Wave Functions: Whittaker FunctionsVon EverandTables of Coulomb Wave Functions: Whittaker FunctionsNoch keine Bewertungen

- N-Bit Shift Register PDFDokument232 SeitenN-Bit Shift Register PDFAnuradha KhalkhoNoch keine Bewertungen

- Scattering Theory for Automorphic Functions. (AM-87), Volume 87Von EverandScattering Theory for Automorphic Functions. (AM-87), Volume 87Noch keine Bewertungen

- Bharathidasan Engineering College: Department of Electronics & Communication EngineeringDokument71 SeitenBharathidasan Engineering College: Department of Electronics & Communication EngineeringnarasimhanNoch keine Bewertungen

- VHDL Code For D FF Using Behavior ModelDokument20 SeitenVHDL Code For D FF Using Behavior ModelAdithya ChakilamNoch keine Bewertungen

- Matlab OverlapSaveMethodDokument96 SeitenMatlab OverlapSaveMethodJulian HoxhaNoch keine Bewertungen

- Lab - 2 SolDokument18 SeitenLab - 2 SolOnnu RanduNoch keine Bewertungen

- VHDL Code (Including The RegisterFile-RAM Based Model) For SimpleProcessor of BrownVranesic Chapter 7Dokument14 SeitenVHDL Code (Including The RegisterFile-RAM Based Model) For SimpleProcessor of BrownVranesic Chapter 7Shubham ShuklaNoch keine Bewertungen

- Basic Gates ProgramDokument34 SeitenBasic Gates ProgramJoychandra LoukrakpamNoch keine Bewertungen

- Verification of DFT PropertiesDokument5 SeitenVerification of DFT Properties4NM19EC157 SHARANYA R SHETTYNoch keine Bewertungen

- Lab p6Dokument5 SeitenLab p64NM19EC157 SHARANYA R SHETTYNoch keine Bewertungen

- DSP LAB 1to 6Dokument12 SeitenDSP LAB 1to 6daddyplays25Noch keine Bewertungen

- Lab Tasks 10Dokument2 SeitenLab Tasks 10Afaq KhaliqNoch keine Bewertungen

- CLC Clear Close X (0 0 Ones (1,50) ) y - Ics (1 1) H Recur - Diff (X, y - Ics) Plot (H) Grid Title Xlabel YlabelDokument11 SeitenCLC Clear Close X (0 0 Ones (1,50) ) y - Ics (1 1) H Recur - Diff (X, y - Ics) Plot (H) Grid Title Xlabel YlabelMuzammil AhmedNoch keine Bewertungen

- ADSP Lab ManualDokument33 SeitenADSP Lab ManualsunithrNoch keine Bewertungen

- Asynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterDokument20 SeitenAsynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterKalagadda BikshaluNoch keine Bewertungen

- DSP Lab Programs Word-2Dokument39 SeitenDSP Lab Programs Word-2Sai Jaswanth SinghNoch keine Bewertungen

- VHDL CodesDokument15 SeitenVHDL Codesrksinha25Noch keine Bewertungen

- DC Lab 07Dokument7 SeitenDC Lab 07Affra NazirNoch keine Bewertungen

- E Cad Lab ManualDokument51 SeitenE Cad Lab ManualRajesh DoradlaNoch keine Bewertungen

- Dspmanual MatlabDokument26 SeitenDspmanual MatlabgsnaveenkumarNoch keine Bewertungen

- DSP 72Dokument42 SeitenDSP 72SakethNoch keine Bewertungen

- DSP Lab01 HandoutDokument9 SeitenDSP Lab01 HandoutHina ImtiazNoch keine Bewertungen

- OdsDokument17 SeitenOdshd photosNoch keine Bewertungen

- DTSP Lab Manual 5Dokument260 SeitenDTSP Lab Manual 5GeethakshayaNoch keine Bewertungen

- Digital Signal ProcessingDokument23 SeitenDigital Signal ProcessingSanjay PalNoch keine Bewertungen

- DSP Lab ManualDokument51 SeitenDSP Lab ManualShahin4220Noch keine Bewertungen

- Experiment - 1: Aim: Program For The Generation of Unit Step SequenceDokument18 SeitenExperiment - 1: Aim: Program For The Generation of Unit Step SequenceRahul GuptaNoch keine Bewertungen

- Pulse Code Modulation and DemodulationDokument2 SeitenPulse Code Modulation and DemodulationKushalaPriyaReddyNoch keine Bewertungen

- MatlabDokument66 SeitenMatlabappurono100% (1)

- Dic File - 7 SemDokument22 SeitenDic File - 7 SemShalini SharmaNoch keine Bewertungen

- Generation of Basic Signals: AIM: To Write A MATLAB Program To Generate Various Type of Signals. AlgorithmDokument39 SeitenGeneration of Basic Signals: AIM: To Write A MATLAB Program To Generate Various Type of Signals. AlgorithmMrjayanthiNoch keine Bewertungen

- Tugas8 - 2210191006 - Filosofi Dwibakti - LapsemDokument23 SeitenTugas8 - 2210191006 - Filosofi Dwibakti - LapsemFD SyndromeNoch keine Bewertungen

- Date: 28 September, 2015: VHDL Assighment 2Dokument15 SeitenDate: 28 September, 2015: VHDL Assighment 2Ishan DarwhekarNoch keine Bewertungen

- Digital Signal Processing Lab: Practical RecordDokument30 SeitenDigital Signal Processing Lab: Practical RecordAnveshGopalamNoch keine Bewertungen

- MatlabDokument34 SeitenMatlabMeghanaNoch keine Bewertungen

- Digital Signal Processing LABDokument15 SeitenDigital Signal Processing LABRahul GuptaNoch keine Bewertungen

- DSP NewDokument62 SeitenDSP NewSunitha JosephineNoch keine Bewertungen

- Matlabcode PCM&QPSK 1Dokument4 SeitenMatlabcode PCM&QPSK 1sheethal rokhadeNoch keine Bewertungen

- 005 - K. C. Chang - Digital Systems - 4 A 15Dokument13 Seiten005 - K. C. Chang - Digital Systems - 4 A 15Rooster MXNoch keine Bewertungen

- Advanced Communication Lab (15ECL76)Dokument15 SeitenAdvanced Communication Lab (15ECL76)kimberly100% (1)

- Pulse Code ModulationDokument2 SeitenPulse Code ModulationShishir HalderNoch keine Bewertungen

- DSP Lab ReportDokument26 SeitenDSP Lab ReportPramod SnkrNoch keine Bewertungen

- Digital Integrated Circuits Lab: Practical FILEDokument55 SeitenDigital Integrated Circuits Lab: Practical FILELakshayNoch keine Bewertungen

- VHDL Code For Mac UnitDokument8 SeitenVHDL Code For Mac Unitmeaow88100% (1)

- Lab 1 Pulse Code ModulationDokument5 SeitenLab 1 Pulse Code ModulationAbbaas AlifNoch keine Bewertungen

- VHDL SynthesisDokument91 SeitenVHDL SynthesisFennil KinsperNoch keine Bewertungen

- Half AdderDokument11 SeitenHalf AdderTahsin RahmanNoch keine Bewertungen

- DSP Experiments: Experiment 1Dokument20 SeitenDSP Experiments: Experiment 1Sàçhïñ KúshwàháNoch keine Bewertungen

- VHDL ProgramDokument5 SeitenVHDL ProgramJaswanth TejaNoch keine Bewertungen

- DSP Lab RecordDokument27 SeitenDSP Lab RecordShantul KhandelwalNoch keine Bewertungen

- Matlab Code For Basic DSP Signals MATLAB PROGRAM TO DISPLAY THE PROPERTIES OF DISCRETE FOURIER TRANSFORM (DFT)Dokument16 SeitenMatlab Code For Basic DSP Signals MATLAB PROGRAM TO DISPLAY THE PROPERTIES OF DISCRETE FOURIER TRANSFORM (DFT)Sabithkk2007Noch keine Bewertungen

- VTU DSP Lab Manual 5th Sem E C Matlab Programs and CCS Studio ProgramsDokument35 SeitenVTU DSP Lab Manual 5th Sem E C Matlab Programs and CCS Studio ProgramsSundaram NatarajanNoch keine Bewertungen

- Computer Architecture & Digital Hardware Design (ECD09) : (Practical File)Dokument18 SeitenComputer Architecture & Digital Hardware Design (ECD09) : (Practical File)prem kumarNoch keine Bewertungen

- EC6612 - VLSI Design Laboratory ManualDokument39 SeitenEC6612 - VLSI Design Laboratory ManualSriramNoch keine Bewertungen

- Principles of Management: Lesson PlanDokument23 SeitenPrinciples of Management: Lesson PlanSriram100% (1)

- What Determines The Color of An LED?: SemiconductingDokument1 SeiteWhat Determines The Color of An LED?: SemiconductingSriramNoch keine Bewertungen

- EC8661 VLSI Design LaboratoryDokument53 SeitenEC8661 VLSI Design LaboratorySriram100% (4)

- Sensors: SL - N o Application Sensor Example PriceDokument6 SeitenSensors: SL - N o Application Sensor Example PriceSriramNoch keine Bewertungen

- Wireless Communication - EC 2401 - I - Answer KeyDokument9 SeitenWireless Communication - EC 2401 - I - Answer KeySriramNoch keine Bewertungen

- Ec6512 Communication Systems Laboratory ManuslDokument86 SeitenEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- EC2354 - VLSI DesignDokument2 SeitenEC2354 - VLSI DesignSriramNoch keine Bewertungen

- Verilog Course ManualDokument60 SeitenVerilog Course ManualSriramNoch keine Bewertungen

- Concept MapDokument18 SeitenConcept MapSriramNoch keine Bewertungen

- Anna University Chennai - 600 025Dokument2 SeitenAnna University Chennai - 600 025SriramNoch keine Bewertungen

- Ec6512 Communication Systems Laboratory ManuslDokument86 SeitenEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- Eee 2008Dokument29 SeitenEee 2008SriramNoch keine Bewertungen

- Analog CommunicationDokument6 SeitenAnalog CommunicationSriramNoch keine Bewertungen

- Analog DesignDokument4 SeitenAnalog DesignSriramNoch keine Bewertungen

- WIRELESS COMMUNICATION QUESTION PAPER 2011 November DecemberDokument2 SeitenWIRELESS COMMUNICATION QUESTION PAPER 2011 November DecemberSriram100% (1)

- Anna University Chennai - 600 025Dokument2 SeitenAnna University Chennai - 600 025SriramNoch keine Bewertungen

- Vlsi TestingDokument51 SeitenVlsi TestingSriramNoch keine Bewertungen

- II Year B.SC ElectronicsDokument12 SeitenII Year B.SC ElectronicsSriramNoch keine Bewertungen

- ASIC Interview Question & Answer - PLLDokument3 SeitenASIC Interview Question & Answer - PLLprodip7Noch keine Bewertungen

- ELEC-E8412 PE Exercise#5 SolutionsDokument5 SeitenELEC-E8412 PE Exercise#5 SolutionsHồng Bá ThọNoch keine Bewertungen

- Ec6401-Electronic Circuits IIDokument3 SeitenEc6401-Electronic Circuits IIArun ArjunanNoch keine Bewertungen

- Experiment No:5: Gain, Differential Mode Gain, Gain, Differential Mode Gain, CMRR, Slew Rate Common ModeDokument4 SeitenExperiment No:5: Gain, Differential Mode Gain, Gain, Differential Mode Gain, CMRR, Slew Rate Common ModeAyush SahNoch keine Bewertungen

- Tabela B.4 (Resistores) CFW700Dokument1 SeiteTabela B.4 (Resistores) CFW700Everson SilvaNoch keine Bewertungen

- Feedback AmplifiersDokument21 SeitenFeedback AmplifiersNon Artists100% (1)

- Low-Drop Voltage Regulator TLE 4276: FeaturesDokument19 SeitenLow-Drop Voltage Regulator TLE 4276: FeaturesshtormlNoch keine Bewertungen

- Differentiator ExperimentDokument25 SeitenDifferentiator ExperimentAlyaa Nadzirah Binti Shbini100% (1)

- Chapter 01Dokument15 SeitenChapter 01tmya06Noch keine Bewertungen

- P - Chapter 9Dokument12 SeitenP - Chapter 9usa2017lapNoch keine Bewertungen

- Gate Drive Design For Large Mosfet Apt9302Dokument10 SeitenGate Drive Design For Large Mosfet Apt9302Grzegorz WegnerNoch keine Bewertungen

- Digital Electronics Timing DiagramsDokument11 SeitenDigital Electronics Timing DiagramsJaydaHunteNoch keine Bewertungen

- PLS159ADokument12 SeitenPLS159AFrancisco MauroNoch keine Bewertungen

- Scan Chain Failure PDFDokument6 SeitenScan Chain Failure PDFemail2pr2639100% (1)

- RC CircuitsDokument37 SeitenRC CircuitsNoviNoch keine Bewertungen

- Amplifier Transistors: NPN SiliconDokument6 SeitenAmplifier Transistors: NPN SilicondiegooliveiraEENoch keine Bewertungen

- Inductor SimulatorDokument17 SeitenInductor SimulatorwindfocusNoch keine Bewertungen

- KIA278R15PIDokument7 SeitenKIA278R15PIIdrissa NikiemaNoch keine Bewertungen

- VI Characteristics of Diode Transistors Configurations - Amplifiers. Op AmpsDokument3 SeitenVI Characteristics of Diode Transistors Configurations - Amplifiers. Op AmpsAmritha VNoch keine Bewertungen

- IC4017Dokument11 SeitenIC4017Nikhil BhatiNoch keine Bewertungen

- Ece Lab IpDokument3 SeitenEce Lab IpNikhil AggarwalNoch keine Bewertungen

- Time Domain Response of First Order RL and RC CircuitsDokument21 SeitenTime Domain Response of First Order RL and RC CircuitsMOHSINALI MOMINNoch keine Bewertungen

- Continuous-Time OTA-C Filters: Advantages: OTA-C Filters Have The Advantages of High Frequency or Wide BandwidthDokument12 SeitenContinuous-Time OTA-C Filters: Advantages: OTA-C Filters Have The Advantages of High Frequency or Wide BandwidthAshraf DeenNoch keine Bewertungen

- EEEB273 N07 - Diff Amp ActiveLoad x6Dokument9 SeitenEEEB273 N07 - Diff Amp ActiveLoad x6ramanaidu1Noch keine Bewertungen

- Lab 12 (Construction and Analysis of Multiplexer Circuits.)Dokument6 SeitenLab 12 (Construction and Analysis of Multiplexer Circuits.)Husnain 18Noch keine Bewertungen

- Minimum Sum of Products and Minimum Product of SumsDokument4 SeitenMinimum Sum of Products and Minimum Product of SumsSiva GuruNoch keine Bewertungen

- Programmable Quad Bipolar Operational Amplifier: LM146 LM246 LM346Dokument6 SeitenProgrammable Quad Bipolar Operational Amplifier: LM146 LM246 LM346Alejandro Borrego DominguezNoch keine Bewertungen

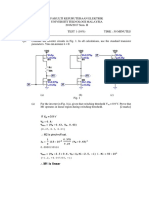

- Fakulti Kejuruteraan Elektrik Universiti Teknologi Malaysia 2016/2017 Sem. II MKEL 1163 TEST 1 (10%) Time: 50 MinutesDokument3 SeitenFakulti Kejuruteraan Elektrik Universiti Teknologi Malaysia 2016/2017 Sem. II MKEL 1163 TEST 1 (10%) Time: 50 MinutesMarie MichelineNoch keine Bewertungen

- CAT 910 Basic CircuiteDokument6 SeitenCAT 910 Basic CircuiteYober Emilio Nato AcostaNoch keine Bewertungen

- Topic 9 MOS Memory and Storage Circuits: ECE 271 Electronic Circuits IDokument98 SeitenTopic 9 MOS Memory and Storage Circuits: ECE 271 Electronic Circuits INiharikaNoch keine Bewertungen

- Mental Math: How to Develop a Mind for Numbers, Rapid Calculations and Creative Math Tricks (Including Special Speed Math for SAT, GMAT and GRE Students)Von EverandMental Math: How to Develop a Mind for Numbers, Rapid Calculations and Creative Math Tricks (Including Special Speed Math for SAT, GMAT and GRE Students)Noch keine Bewertungen

- Quantum Physics: A Beginners Guide to How Quantum Physics Affects Everything around UsVon EverandQuantum Physics: A Beginners Guide to How Quantum Physics Affects Everything around UsBewertung: 4.5 von 5 Sternen4.5/5 (3)

- Limitless Mind: Learn, Lead, and Live Without BarriersVon EverandLimitless Mind: Learn, Lead, and Live Without BarriersBewertung: 4 von 5 Sternen4/5 (6)

- Build a Mathematical Mind - Even If You Think You Can't Have One: Become a Pattern Detective. Boost Your Critical and Logical Thinking Skills.Von EverandBuild a Mathematical Mind - Even If You Think You Can't Have One: Become a Pattern Detective. Boost Your Critical and Logical Thinking Skills.Bewertung: 5 von 5 Sternen5/5 (1)

- Basic Math & Pre-Algebra Workbook For Dummies with Online PracticeVon EverandBasic Math & Pre-Algebra Workbook For Dummies with Online PracticeBewertung: 4 von 5 Sternen4/5 (2)

- Math Workshop, Grade K: A Framework for Guided Math and Independent PracticeVon EverandMath Workshop, Grade K: A Framework for Guided Math and Independent PracticeBewertung: 5 von 5 Sternen5/5 (1)

- Images of Mathematics Viewed Through Number, Algebra, and GeometryVon EverandImages of Mathematics Viewed Through Number, Algebra, and GeometryNoch keine Bewertungen

- Fluent in 3 Months: How Anyone at Any Age Can Learn to Speak Any Language from Anywhere in the WorldVon EverandFluent in 3 Months: How Anyone at Any Age Can Learn to Speak Any Language from Anywhere in the WorldBewertung: 3 von 5 Sternen3/5 (80)

- ParaPro Assessment Preparation 2023-2024: Study Guide with 300 Practice Questions and Answers for the ETS Praxis Test (Paraprofessional Exam Prep)Von EverandParaPro Assessment Preparation 2023-2024: Study Guide with 300 Practice Questions and Answers for the ETS Praxis Test (Paraprofessional Exam Prep)Noch keine Bewertungen

- A Mathematician's Lament: How School Cheats Us Out of Our Most Fascinating and Imaginative Art FormVon EverandA Mathematician's Lament: How School Cheats Us Out of Our Most Fascinating and Imaginative Art FormBewertung: 5 von 5 Sternen5/5 (5)

- Interactive Math Notebook: Geometry WorkbookVon EverandInteractive Math Notebook: Geometry WorkbookBewertung: 5 von 5 Sternen5/5 (5)