Beruflich Dokumente

Kultur Dokumente

Voltage Disturbances Mitigation in Low Voltage Distribution System Using New Configuration of Dynamic Voltage Restorer (DVR)

Hochgeladen von

Mihir HembramOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Voltage Disturbances Mitigation in Low Voltage Distribution System Using New Configuration of Dynamic Voltage Restorer (DVR)

Hochgeladen von

Mihir HembramCopyright:

Verfügbare Formate

World Applied Sciences Journal 10(12): 1480-1489, 2010

ISSN 1818-4952

IDOSI Publications, 2010

Corresponding Author: Rosli Omar, Faculty of Electrical, University Teknikal Malaysia Melaka,

Ayer Keroh, Melaka 75450, Malaysia, E-mail: omarrosli@yahoo.com.

1480

Voltage Disturbances Mitigation in Low Voltage Distribution System Using

New Configuration of Dynamic Voltage Restorer (DVR)

Rosli Omar and N.A. Rahim

1 2

Faculty of Electrical, University Teknikal Malaysia Melaka, Ayer Keroh, Melaka 75450, Malaysia

1

UMPEDAC, Faculty of Engineering, University of Malaya, 50600 Kuala Lumpur, Malaysia

2

Abstract: This paper discusses the design and development of Dynamic Voltage Restorer (DVR) controller for

voltage unbalanced compensation using d-q-o transformation technique. The controller in d-q-o coordinates

has better performance than conventional controllers. The controlled variables in d-q-o coordinates are then

inversely transformed to the original voltages which produced reference voltages to a DVR. The performance

of proposed control algorithm has been simulated by MATLAB/SIMULINK SimPower System Toolbox. A

prototype has been developed in order to validate the effectiveness of the proposed control solution.

Simulation and experimental results are presented for various conditions of disturbances in the network

included unbalance voltage in the supply voltage to show the compensation effectiveness.

Key words: Controller Dynamic voltage restorer Voltage unbalance Matlab/Simulink D-q-o coordinate

Disturbances

INTRODUCTION basic operation principle of the DVR is to inject an

Several methods are available to prevent equipment through an injection transformer when PCC voltage sag is

mal operation due to voltage sags. The two obvious detected. Loads connected downstream are thus

solutions, at first sight, are a reduction of the number of protected from the PCC voltage sag [5-6]. The voltage

faults and improvement of equipment immunity. However, sags as defined by IEEE Standard 1159, IEEE

experience has shown that in many practical cases neither Recommended Practice for Monitoring Electric Power

of these methods is suitable. The most common mitigation Quality, is a decrease in RMS voltage or current at the

method remains the installation of additional equipment power frequency for durations from 0.5 cycles to 1 minute,

between the power system and the equipment, either reported as the remaining voltage. Typical values are

directly with the equipment terminals or at the customer- between 0.1 p.u. and 0.9 p.u. and typical fault clearing

utility interface. The uninterruptable power supply (UPS) times range from three to thirty cycles depending on the

has traditionally been the method of choice for small fault current magnitude and the type of over current

power, single-phase equipment. For large equipment detection and interruption [7].

several methods are in use and under development, one The details of the existing controllers has been

of which is the series voltage controller, also known under applied in DVR can be found in [8-11]. In this paper, the

the name Dynamic Voltage Restorer or DVR [1-4]. improvement of d-q-o technique strategy is applied to the

The Dynamic Voltage Restorer (DVR) is a series control of a three phase DVR. The proposed of the

custom power device intended to protect sensitive loads control strategy has the following advantages compared

from the effects of voltage sags at the point of common to the existing ones. The improvement of the controller is

coupling (PCC).A typical DVR connected system circuit easy to design and does not much depend to circuit

is shown in Figure 1, where the DVR consists of parameters. The dc value of the capacitor and harmonic

essentially a series connected injection transformer, a ripple current due to input power circuit can be reduced.

voltage source inverter (VSI), inverter output filter and an The controller can detect any disturbance in the network

energy storage device connected to the dc-link. The very fast. Once the disturbance is detected, the DVR act

power system upstream to DVR is represented by an very quickly in order to correct it and injecting the exact

equivalent voltage source and source impedance. The amount of energy required.

appropriate voltage quantity in series with the supply

World Appl. Sci. J., 10(12): 1480-1489, 2010

1481

Fig. 1: Typical Existing DVR circuit topology (L ,L ,L , C ,C ,C and R ,R ,R ) are installed on low

Fig. 2: Symmetrical components of unbalanced system of placed in the high voltage side in this case, high order

voltages harmonic currents will penetrates through the injection

The Concept of Voltage Unbalance Using Dynamic the voltage sags/swells at the critical load, DVR produce

Voltage Restorer: Figure 1 shows a distribution system a harmonics distortion fed from series transformer as

which consists of feeder A, feeder B and feeder C. A DVR injection voltage to the critical load. Using the FFT

is connected in series between sensitive loads in order to analyzer Voltage Total Harmonic Distortion (VTHD) of

mitigate unbalanced loads or faults in feeder A or B. The 1.4% of the filtering scheme is shown in Figure 3 is satisfy

possibility of compensation of voltage unbalance can be the IEEE-519 standard harmonic voltage limit.

limited by a number of factors including finite DVR, In DVR the injection transformer must be designed

power rating, different load conditions, background properly according to the voltage required in the

power quality problems and different types of sags secondary side of the transformer. The ratio of the

[12-13]. injection transformer will determines the flow of current in

Figure 2 shows the symmetrical components of an the primary side which may affect the performance of the

unbalanced system of voltages. These are called positive power circuit devices in DVR which consists of Voltage

sequence, negative and zero sequence systems. For a Source Inverter (VSI).

perfect balanced system both negative and zero sequence The transformer in DVR can be configured either in

systems would be absent. Delta-open or Wye open winding. In order to step-up the

Proposed New Configurations Circuit of Dvr distribution system the series injection transformer

Main Circuit of New Configurations: Figure 4 illustrates turn ratio must be calculated. In the proposed

a new configuration model of the proposed DVR system configuration as shown in Figure 4, the maximum injection

and the system consists of a DC voltage source (V ), transformer voltage per phase is set to Vinj 1 is equal to

dc

three single phase injection transformer, a three phase 120 V and single phase voltage line to line of VSL is

voltage source PWM inverter, L-C output filter and about V = 60 V. The comparison of two types of

sensitive loads. In this proposed designed of DVR, transformers can be described as follow;

special attention must be paid on two types of

configuration namely:

Filtering Configuration

Injection transformer winding

Filtering configuration for DVR is very important as

it related with the system dynamic response. The filtering

system of the DVR can be placed either on the high

voltage or the low-voltage side of the injection

transformer and are referred to as line side filter [14-15]

and inverter-side filter [15-18] respectively. In the

proposed filtering system as shown in Figure 3, the

filtering scheme is installed for both on the low and high

voltages. The filter inductor, capacitor and resistor

fa fb fc fa fb fc a b c

voltage side between the series converter and the

transformer and the high voltage side(C ,C and C ), when

1 2 3

it is place in low voltage side, high order harmonics from

the three phase voltage source PWM inverter is by pass

by the filtering scheme and its impact on the injection

current rating can be ignored. The type of this filtering

configuration can also eliminate switching ripples

produced by the converter. As for the filtering scheme is

and it will carry the harmonic voltages. When compensate

VSI output voltage to mitigate 50% of voltage sags in the

rms

VSI L-L

( )

1 120

2

60

inj

Delta open

VSI L L

V

V

a

V V

= = =

( )

( )

( ) 1 1

( ) 1

3

3 120

3.4

60

inj inj

Wye Open

VSI L L VSI L L

V V

a

V V

= = = =

World Appl. Sci. J., 10(12): 1480-1489, 2010

1482

Fig. 3: THD for voltage of the proposed scheme

Fig. 4: New Configuration of DVR

The turn ratio of the injection transformer In Delta If in case the injection transformer is connected in

-Open winding Wye -Open winding

a

b

c

LPF

LPF

LPF

VLa

VLb

VLc

THREE PHASE

PLL

+

+

+

+

d

-

q

-

o

a

b

c

Amplitude

Vsa

Vsb

Vsc

-

+

PI

C

O

N

T

R

O

L

L

E

R

Vs REF

Vs

PWM

Controller

Vsa

Vsb

Vsc

+

-

PI

CONTROLLER

Vdc

VLd

VLq

Vq dc

Vd dc

Vq ref

Vd ref

V

s

a

r

e

f

V

s

b

r

e

f V

s

c

r

e

f

Vdcref

Block 1

Block 2

Block 3

Block5

B

l

o

c

k

6

Unbalanced

Voltage

Detection

Block 4

PWM1 to PWM6 switches

d

-

q

-

o

Vquadrature

La

Lb

Lc

o

V V

V Q V

V

V

(

(

(

(

=

(

(

(

(

1 1

1

2 2

2 3 3

0

3 2 2

1 1 1

2 2 2

(

(

(

(

(

(

(

(

World Appl. Sci. J., 10(12): 1480-1489, 2010

1483

Fig. 5: Block Diagram Control of the proposed Scheme of DVR for Unbalanced Voltage

Based on the calculation the high ratio of the Block 1 is used to convert the three phase load

transformer winding will increase the primary side current, voltages (V , V , V ) into the - -o coordinates as

so in the proposed configuration the wye-open winding in equation (1)

is used.

Control Method of the Proposed Scheme: There are many

control schemes reported in the literature for control of

DVR such as instantaneous reactive power theory, power (1)

balanced theory, synchronous reference frame theory etc

[14]. In this paper a new control method for DVR system

is proposed by using the d-q-o transformation or Parks

transformation for sags/swells detection. The d-q-o Where Q =

method gives the sag depth and phase shift information

with start and end times. The main aspects of the control

system are shown in Figure 5 and include the following

blocks:

La Lb Lc

cos sin

2

sin cos 3

d

q

V V

V V

(

(

( (

(

=

( (

(

( (

(

cos sin

2

sin cos 3

d

q

V V

V V

(

(

( (

(

=

( (

(

( (

(

1 0 1

3

0.5 1

2

3

0.5 1

2

a

b

c

o

V V

V V

V

V

(

(

(

( (

(

( (

=

(

( (

(

( (

(

(

( ) ( ) ( )

2 2 2 2

3

source sa sb sc

V V V V

| |

= + +

|

\ .

World Appl. Sci. J., 10(12): 1480-1489, 2010

1484

Block 1 is used to convert the three phase load Block 6 is the PWM block, this block provides the

voltages (V , V , V ) into the - -o coordinates as

La Lb Lc

in equation (1), the three phase load voltages

reference components V V and Vo can be

-ref, -ref ref

converted to V V (2).

d ref and q ref

(2)

Transformation to dqo to abc

(3)

(4)

Block 2 is considered as a source voltages (V ,

sa

V V ). The amplitude of AC voltage at the sources

sb, sc

(V ) can be calculatedas follow;

source

(5)

Block 3 is a three phase PLL (Phase-locked loop). The

angle of the source voltage can be obtained using

three phase PLL. The information extracted from the

PLL is used for detection and reference voltage

generation.

Block 4 is the detection scheme for the voltage

Unbalanced compensator. From Figure 5 shows that,

the synchronous frame variables, V and V are used

d q

as inputs for low pass filters to generate voltage

references in the synchronous frame.

Block 5 receive the components of the load voltage

vectors V ref and V ref and transforms them to three

d q

phase coordinates using equation (3) and (4) the

generation voltages are used as the voltage

reference. The DC link error in Figure 5 is used to get

optimized controller output signal because the

energy on the DC link will be changed during the

unbalance voltage.

firing for the Inverter switches (PWM1 to PWM6).

The injection voltage is generated according to the

difference between the reference load voltage and the

supply voltage and is applied to the voltage source

converter (VSC).

Simulation Results: The proposed control scheme for the

DVR is validated in this section via MATLAB/SIMULINK

SimPower System toolbox. In this paper, the load is

represented by a series equivalent rated at 200V, 5KVA at

0.9 load power factor. A simulation model has been

developed in MATLAB/SIMULINK as shown in

Figure 4. Simulation and experimental parameters are given

in Table 1. The performance of the DVR for different

supply disturbances is tested under various operating

conditions. Several simulation of the DVR with proposed

controller scheme and new configuration of it have been

made. Figure 6 shows that unbalanced output voltages,

positive sequence, negative and zero sequence. In case of

zero sequence all phases are equal. The distortions occur

for both the negative and zero sequence during

transformation processes from stationary abc reference

frame to d-q-o coordinates. In figure 6 (c) also shows that

the negative sequence disturbances rotates in the

opposite direction.

Experimental Results: In order to validate the

effectiveness of the proposed system a small scale

prototype of DVR was built and tested. The prototype

developed based on schematic in Figure 4, all the system

parameters for the hardware designed as shown in

Table 1. The prototype is rated to protect 5KVA load 40%

voltage sags mitigation and in case of unbalance voltage

at the Point of Common Coupling (PCC) is set at 10%-

20%. Three phase load comprising of 40 and 60mH

inductor.

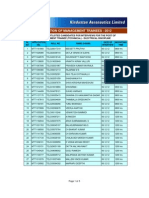

Table 1: System Parameters Proposed

Main Supply Voltage per phase 240V

Line Impedance Ls =0.5mH Rs = 0.1

Series transformer turns ratio 1:1

DC Bus Voltage 120V

Filter Inductance 2mH

Filter capacitance 1uF

Load resistance 40

Load inductance 60mH

Line Frequency 50Hz

Switching Frequency 5kHz

World Appl. Sci. J., 10(12): 1480-1489, 2010

1485

(a) (b)

(c) (d)

Fig. 6: (a) Unbalanced voltage, (b) Positive sequence (c) Negative sequence (d) Zero sequence

The proposed control strategy is implemented The controller has its own ADC converters and PWM

digitally in DSP TMS320F2812. The DSP was selected as pulse outputs. The inputs of a 3-leg Voltage Source

it has a 32-b CPU which operating at 150MHz. The voltage Converter (VSC) are the PWM pulses which are generated

and current sources were sent to the analog digital by the digital controller. The three phase supply voltage

converter of the DSP. The sampling times are governed by is measured continuously and it then compared with the

the DSP timer called a CpuTimer0 which generates reference voltage in order to regulate load voltage

periodic interrupt at each sampling times Ts. The Interrupt response. If there any disturbances occur, different

Service Routine (ISR) will read the sampling value of the between the supply voltage and load voltage, the

voltage and current source from the analog digital different voltage between them will be compensated. The

converter (ADC) The DSP controller offers a display amount of compensated voltage needs to be injected is

function, which monitor the disturbances in the real time. calculated and the results of the supply, load and

The control algorithm which is proposed in section II is compensated voltages will be processed by the DSP and

tested with a control using DSP TMS 320F 2812. injected to the IGBT switching scheme (PWM1 to

( )

( )

( )

2 2

sin sin sin

3 3 2

3 2 2

cos cos cos

3 3

sa

d pos

sb

q pos

sc

V t t t

V

V

V

t t t V

( | | | |

+ (

| | (

(

\ . \ . (

(

= (

(

(

| | | | (

(

+

(

| |

\ . \ .

( )

( )

( )

2 2

sin sin sin

3 3 2

3 2 2

cos cos cos

3 3

sa

d neg

sb

q neg

sc

V t t t

V

V

V

t t t V

( | | | |

+ (

| | (

(

\ . \ . (

(

= (

(

(

| | | | (

(

+

(

| |

\ . \ .

World Appl. Sci. J., 10(12): 1480-1489, 2010

1486

PWM2). Positive and negative sequence can be In the prototype developed the maximum sags time

converted when three voltages are sensed in phase and

quadrature components. The conversion process of

positive and negative sequence can be formulated using

equations (6) - (7).

(6)

(7)

is set to 100 ms as it very fast to detect any disturbances

occur in the network. It should be mentioned that with

the new configuration of the topology and an

improvement of the proposed controller also can detect

voltage swells in the network. Voltage swells can occur

more frequently than other power quality phenomenon

and is known as the most important power quality

problems in the power distribution system. In normal

situation if there is no voltage swells detects in the

network, the dc-link capacitor charging current is almost

zero. Supply current of the network is equal to load

current which is sinusoidal. When the DVR detect the

voltage swells, the DVR starts to inject an appropriate

voltage for the voltage swells; active power is supplied

from the dc-link to the network which causes dc-link

voltage to drop. So the controller will compared with the

reference voltage and inject missing voltage through

injection transformer. The three phase 20% balance

voltage.

(a) (b)

(c) (d)

Fig. 7: (a) Unbalanced voltage, (b) Positive sequence (c) Negative sequence (d) Zero sequence

World Appl. Sci. J., 10(12): 1480-1489, 2010

1487

(a) (b)

(c)

Fig. 8: (a)Three phase Unbalanced Voltages (b) Injected Voltages (c) Restoration load Voltages

(a) (b)

Fig. 9: (a)Total Harmonic Distortion Current (THD) under unstable dc-link (b) Total Harmonic Distortion Current (THD)

I I

under stable dc-link

World Appl. Sci. J., 10(12): 1480-1489, 2010

1488

(a) (b)

(c)

Fig. 10: (a)Three phase 20% balance Voltages Swells (b) Injected Voltages swells (c) Restoration load Voltages

Can be observed in Figure 10(a), the DVR will detect based on the rating of the IGBT. Harmonic current is

voltage swells and injects the missing voltage as shown depending on the DC link voltage. DC side capacitor Cdc1

in Figure 10(b). The fast response to detect voltage swells and Cdc2 should be large enough to absord the ripple

by the controller will causes the load voltage is secured without the distorting the dc bus voltage much. If there is

from distortion and this can be illustrated in Figure 10(c). distortion in the dc voltage the inverter output will get

The performance during 10%-20% voltage unbalance distorted with third harmonic content. With the stability

is illustrated in Figures 7(a). In Figure 7(b), (c) and (d) of the DC bus and the Total Harmonic Distortion for

shows that positive sequence, negative and zero current (THD) for third harmonics current is reduced 7.8

sequence. Next, the performance of DVR for a three % to 2.8% as shown in Figures 9(a) and 9(b).

phases to ground fault is also investigated. Figure 8 (a)

shows that unbalanced three phases fault. Injection CONCLUSION

voltages produced by DVR is shown in Figure 8(b).

Figure 8(c) shows the load voltages restoration using In this research the new configuration of the DVR

DVR. From the results show that the load terminal voltage prototype has been proposed. The proposed topology is

is restored and help to maintain a balanced and constant capable to mitigate various disturbances in the network.

load voltage. A control system based on improvement d-q-o controller

In new configuration of the proposed system, the has been applied to the prototype. The effectiveness of

DC link capacitor acts as an energy storage element of the proposed configuration and improvement of d-q-o

the DVR.The DC link of the DVR prototype is determined controller can be seen from Simulation and experimental

I

World Appl. Sci. J., 10(12): 1480-1489, 2010

1489

results. The implementation of a DSP TMS320F2812 based 9. Madtharad, C., 2002. Premrudeeprceechacharn,

on DVR to extract positive and negative sequence was Active Power Filter for Three-Phase Four-Wire

discussed. The experimental results show that the Electric System Using Neural Networks Electric

performance of the DSP controller is satisfactory in Power Systems Res., 60(1): 179-192.

mitigating disturbances in the network such as voltage 10. Jain, S.K., P. Agrawal and H.O. Gupta, 2002. Fuzzy

sags, swells and unbalance voltage in low voltage Logic Controlled Shunt Active Power Filter for Power

distribution system. Quality Improvement, IEE Procedings-Electric Power

ACKNOWLEDGEMENT 11. Chung, Y.I., D.J. Won, S.Y. Park, S.I. Moon and

The authors wish to thank UM and UTeM for in Dynamic Voltage Restorer System, Electrical

providing grant under grant PS002/2007B for this project. Power and Energy Systems, 25: 525-531.

REFERENCES Ahmed, 2007. Determination of voltage references for

1. IEEE Standards Board, 1995. IEEE Std. 1159-1995, series active power filter based on robust PLL

IEEE Recommended Practice for Monitoring Electric system, in: Conference CD-ROM IEEE International

Power Quality. IEEE Inc. New York. Symposium on Industrial Electronics, ISIE, Spain.

2. Sabin, D., 1996. An assessment of distribution 13. Han, B., B. Bae, H. Kim and S. Baek, 2006. Combined

system power quality, Elect. Power Res. Inst., Palo Operation of Unified Power Quality Conditioner with

Alto, CA, EPRI Final Rep. TR-106294-V2, vol. 2, Distributed Generation, IEEE Trans. On Power

Statisticalbb Summary Report. Delivery, 21(1): 330-338.

3. Fitzer, C., M. Barnes and P. Green, 2004. Voltage Sag 14. Choi, S., B. Li and D. Vilathaguwa, 2002. Design and

Detection Technique for a Dynamic Voltage Restorer, Analysis of the inverter side Filter used in the

IEEE Trans. On Industry Application, 40(1). Dynamic Voltage Restorer (DVR), IEEE Trans. On

4. Vilathgamuwa, M., A.A.D. Ranjith Pcrcra and S.S Power Delivery, 17(6): 1058-1066.

Choi, 2002. Performance improvement of the dynamic 15. Fornani, F., R. Procopio and M.J.H. Bollen,

voltage restorer with closed-loop load voltage and 2005. SSS compensation capability for unbalance

current-mode control, IEEE Transactions on Power voltage sags, IEEE Trans. On Power Delivery,

Electronics, 17(5): 824-834. 20(3): 2030-2037.

5. Elnady, A. and M.M.A. Salama, 2005. Mitigation of 16. Stephen, W., E. Middlekauff and Randolph Collins,

Voltage Disturbances Using Adaptive Perceptron- Jr., 1998. System and Customer Impact: Consideration

Based Control Algorithm, IEEE Transactions on for series Custom Power Devices, IEEE Trans On

Power Delivery, 20(1): 309-318. Power Delivery, 13(1): 278-282.

6. Nielsen, J.G., M. Newman, H. Nielsen and 17. Awad, H., H. Nelsen, F. Blaabjerg and M.J. Newman,

F. Bilabjerg, 2004. Control and Testing of a Dynamic 2005. Operation of static series compensator under

VoltageRestorer(DVR) at medium voltage level, IEEE distorted utility conditions, IEEE Trans. Power

Transactions on Power Electronics, 19(3): 806-813. System, 20(1): 1744-1753.

7. Mekri, F. and B. Mazari, 2006. Machmoum, Control 18. Maria Isabel Milands, Enrique Romero Cadaval and

and optimization of shunt active power filter Fermin Barrero Gonzalez, 2007. Comparison of

parameters by fuzzy logic, Can. J. Electr. Comp. Eng., Control Strategies for shunt Active Power Filters in

31(3): 127-134. Three Phase Four-Wire Systems IEEE Trans. On

8. Vazquez, J.R. and P. Salmeron, 2003. Active Power Power Electronics, 22(1): 229-236.

Filter Control Using Neural Network Technologies,

IEE Procedings -Electric Power Applications,

150(2): 139-145.

Applications, 149(3): 317-328.

J.K. Park, 2003. The DC Link Energy Control Method

12. Mekri, F., M. Machmoum, B. Mazari and N. Ait

Das könnte Ihnen auch gefallen

- Performance Analysis of Closed Loop and Open Loop Control Methods in Dynamic Voltage RestorerDokument4 SeitenPerformance Analysis of Closed Loop and Open Loop Control Methods in Dynamic Voltage RestorerInnovative Research PublicationsNoch keine Bewertungen

- Different Control Techniques of Dynamic VoltageDokument6 SeitenDifferent Control Techniques of Dynamic VoltageSrinivas ReddyNoch keine Bewertungen

- By Dynamic Voltage Restorerfor Power Quality ImprovementDokument6 SeitenBy Dynamic Voltage Restorerfor Power Quality ImprovementSemal TankNoch keine Bewertungen

- Modelling and Analysis of Custom Power Devices For Improve Power QualityDokument6 SeitenModelling and Analysis of Custom Power Devices For Improve Power Qualitytaner56Noch keine Bewertungen

- Multifunctional Dynamic Voltage Restorer Implementation For Emergency Control in Distribution SystemsDokument5 SeitenMultifunctional Dynamic Voltage Restorer Implementation For Emergency Control in Distribution SystemsAbebawBelayNoch keine Bewertungen

- 18 IJTPE Issue12 Vol4 No3 Sep2012 pp126 132Dokument7 Seiten18 IJTPE Issue12 Vol4 No3 Sep2012 pp126 132Mihir HembramNoch keine Bewertungen

- 2 Ijeeerfeb20182Dokument10 Seiten2 Ijeeerfeb20182TJPRC PublicationsNoch keine Bewertungen

- Using Fast Fourier Extraction Method Power Quality Improvement by DVR For Unbalanced Voltage Sag-Swell ControlDokument7 SeitenUsing Fast Fourier Extraction Method Power Quality Improvement by DVR For Unbalanced Voltage Sag-Swell ControlInternational Journal of computational Engineering research (IJCER)Noch keine Bewertungen

- Dynamic Voltage Restorer (DVR) - A Perfect Healer For Power Quality ImprovementDokument5 SeitenDynamic Voltage Restorer (DVR) - A Perfect Healer For Power Quality ImprovementUpender BhatiNoch keine Bewertungen

- Power Quality Improvement Using DVRDokument6 SeitenPower Quality Improvement Using DVRNirav RanaNoch keine Bewertungen

- The Application of Dynamic Voltage Restorers (DVR) On Power Distribution Systems For Mitigation of Voltage Sags / SwellsDokument7 SeitenThe Application of Dynamic Voltage Restorers (DVR) On Power Distribution Systems For Mitigation of Voltage Sags / SwellsIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalNoch keine Bewertungen

- A Novel Dynamic Voltage Restorer Based On Matrix ConvertersDokument7 SeitenA Novel Dynamic Voltage Restorer Based On Matrix ConvertersAbdulwahid Al-safanyNoch keine Bewertungen

- Iaetsd-Minimization of Voltage Sags and Swells Using DVRDokument8 SeitenIaetsd-Minimization of Voltage Sags and Swells Using DVRiaetsdiaetsdNoch keine Bewertungen

- Voltage Sag Swell and Harmonics Are Eliminated by DVR Dstatcom in Power System1Dokument8 SeitenVoltage Sag Swell and Harmonics Are Eliminated by DVR Dstatcom in Power System1Indra SakiNoch keine Bewertungen

- Cascaded 5-Level Inverter Type Dstatcom For Power Quality ImprovementDokument5 SeitenCascaded 5-Level Inverter Type Dstatcom For Power Quality ImprovementSiri SarojaNoch keine Bewertungen

- 1 VRR Puthi 564 Research Article Mar 2012Dokument14 Seiten1 VRR Puthi 564 Research Article Mar 2012taner56Noch keine Bewertungen

- Simulation and Implementation of DVR For Voltage Sag CompensationDokument5 SeitenSimulation and Implementation of DVR For Voltage Sag Compensationjcrodriguez83Noch keine Bewertungen

- 3 6Dokument10 Seiten3 6Mihir HembramNoch keine Bewertungen

- Simulation and Comparison of DVR and DSTATCOM Used For Voltage Sag Mitigation at Distribution Side-359Dokument9 SeitenSimulation and Comparison of DVR and DSTATCOM Used For Voltage Sag Mitigation at Distribution Side-359Nirav RanaNoch keine Bewertungen

- International Journal of Engineering Research and DevelopmentDokument7 SeitenInternational Journal of Engineering Research and DevelopmentIJERDNoch keine Bewertungen

- Improving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshDokument5 SeitenImproving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshsarathNoch keine Bewertungen

- Implementation of Dynamic Voltage Restorer (DVR) and Distribution Static Compensator (D-STATCOM) For Power Quality ImprovementDokument7 SeitenImplementation of Dynamic Voltage Restorer (DVR) and Distribution Static Compensator (D-STATCOM) For Power Quality Improvementtaner56Noch keine Bewertungen

- Design of Electrical Machines: A Report OnDokument11 SeitenDesign of Electrical Machines: A Report Onca6tik01Noch keine Bewertungen

- Implementation of Flux-Charge Control Model To Multifunctional Dynamic Voltage Restorer For Emergency Control in Distribution SystemsDokument6 SeitenImplementation of Flux-Charge Control Model To Multifunctional Dynamic Voltage Restorer For Emergency Control in Distribution SystemsIJMERNoch keine Bewertungen

- Analysis and Control of DSTATCOM For A Line Voltage RegulationDokument6 SeitenAnalysis and Control of DSTATCOM For A Line Voltage RegulationSeema P DiwanNoch keine Bewertungen

- Modeling, Simulation and Control of D-Statcom Using Atp/EmtpDokument4 SeitenModeling, Simulation and Control of D-Statcom Using Atp/EmtpKalyan SrinivasNoch keine Bewertungen

- Voltage Sag Compensation Using Dynamic Voltage Restorer: Mayank Paliwal, Rohit Chandra Verma and Shaurya RastogiDokument10 SeitenVoltage Sag Compensation Using Dynamic Voltage Restorer: Mayank Paliwal, Rohit Chandra Verma and Shaurya RastogiKumar RajanNoch keine Bewertungen

- Multilevel Optimal Predictive Dynamic Voltage RestorerDokument14 SeitenMultilevel Optimal Predictive Dynamic Voltage RestorerChikha SaidNoch keine Bewertungen

- IJETR032528Dokument6 SeitenIJETR032528erpublicationNoch keine Bewertungen

- F 010344049Dokument10 SeitenF 010344049IOSRjournalNoch keine Bewertungen

- Power Quality Improvement Using Dynamic Voltage Restorer (DVR)Dokument4 SeitenPower Quality Improvement Using Dynamic Voltage Restorer (DVR)Timothy AsareNoch keine Bewertungen

- Voltage Harmonics Mitigation Using DVR: Electrical & Electronics EngineeringDokument7 SeitenVoltage Harmonics Mitigation Using DVR: Electrical & Electronics EngineeringUdgam TiwariNoch keine Bewertungen

- Analysis of Power Quality Improvement by Using BFO-Fuzzy Controlled DVRDokument7 SeitenAnalysis of Power Quality Improvement by Using BFO-Fuzzy Controlled DVRInternational Journal of Application or Innovation in Engineering & ManagementNoch keine Bewertungen

- Modeling and Simulation of SRF and P-Q Based Control DstatcomDokument7 SeitenModeling and Simulation of SRF and P-Q Based Control DstatcomIJERDNoch keine Bewertungen

- An Adaptive Hy Steresis-Band Current Control Technique of A Voltage-Fed PWM Inverter For Machine Drive SystemDokument7 SeitenAn Adaptive Hy Steresis-Band Current Control Technique of A Voltage-Fed PWM Inverter For Machine Drive SystemJandfor Tansfg Errott100% (1)

- 34i9-Dynamic Voltage RestorerDokument9 Seiten34i9-Dynamic Voltage RestorerIJAET JournalNoch keine Bewertungen

- Transformer-less DVR Compensates Voltage SagsDokument6 SeitenTransformer-less DVR Compensates Voltage SagsSwathi PrasadNoch keine Bewertungen

- Enhancing Power Quality With Improved Dynamic Voltage RestorerDokument7 SeitenEnhancing Power Quality With Improved Dynamic Voltage RestorerJeffersonGoVaO'NeilNoch keine Bewertungen

- A Dynamic Voltage Restorer For Voltage Sag Mitigation in A Refinery With Induction Motor Loads-EgyptDokument8 SeitenA Dynamic Voltage Restorer For Voltage Sag Mitigation in A Refinery With Induction Motor Loads-EgyptGustavo AguayoNoch keine Bewertungen

- Saha Nguyen IeeeDokument6 SeitenSaha Nguyen IeeeLN ParasuramNoch keine Bewertungen

- Improvement of Power Quality in Distribution System Using D-STATCOM With PI and PID ControllerDokument7 SeitenImprovement of Power Quality in Distribution System Using D-STATCOM With PI and PID ControllerPhani Kumar ChittalaNoch keine Bewertungen

- PWM PHA M Inve Ase Hi Erter High Q Ers Fo Qual or ST Lity P Tand-Powe - Alon Er Ge Ne Sin Enera Ingle Ation E - NDokument6 SeitenPWM PHA M Inve Ase Hi Erter High Q Ers Fo Qual or ST Lity P Tand-Powe - Alon Er Ge Ne Sin Enera Ingle Ation E - Nron1234567890Noch keine Bewertungen

- Modeling and Simulation For Voltage Sags, Swells MitigationDokument62 SeitenModeling and Simulation For Voltage Sags, Swells MitigationSaikumar NemalikantiNoch keine Bewertungen

- Understanding of Dynamic Voltage: Restorers Through MATLAB SimulationDokument6 SeitenUnderstanding of Dynamic Voltage: Restorers Through MATLAB SimulationPhạm Quý ThắngNoch keine Bewertungen

- UPS SystemDokument4 SeitenUPS Systemमृत्युंजय झाNoch keine Bewertungen

- Simple Design Criteria of Injection Transformer For The Dynamic Voltage RestorerDokument4 SeitenSimple Design Criteria of Injection Transformer For The Dynamic Voltage RestorerSyed Wajahat AliNoch keine Bewertungen

- Enhancement of Power Quality in Distribution Systems Using DstatcomDokument7 SeitenEnhancement of Power Quality in Distribution Systems Using Dstatcomvc_pothuNoch keine Bewertungen

- New Approach to Multifunctional DVR for Distribution SystemsDokument75 SeitenNew Approach to Multifunctional DVR for Distribution Systemsrajesh_d84Noch keine Bewertungen

- Design and Analysis of Dynamic Voltage Restorer For Deep Voltage Sag and Harmonic CompensationDokument14 SeitenDesign and Analysis of Dynamic Voltage Restorer For Deep Voltage Sag and Harmonic CompensationJoffie Jacob PulpelNoch keine Bewertungen

- Dynamic Voltage RestorersDokument9 SeitenDynamic Voltage RestorersAsha LekshmiNoch keine Bewertungen

- Enhancement of Power Quality in Distribution System Using D-StatcomDokument31 SeitenEnhancement of Power Quality in Distribution System Using D-StatcomKeyur DesaiNoch keine Bewertungen

- DVR Dstatcom Detailed InformationDokument17 SeitenDVR Dstatcom Detailed InformationSuneel Kumar MauryaNoch keine Bewertungen

- Voltage Control in Power System Using Expert System Based On SCADA SystemDokument5 SeitenVoltage Control in Power System Using Expert System Based On SCADA SystemFABIANCHO2210100% (1)

- Control Strategy for Three-Phase PWM Boost RectifierDokument18 SeitenControl Strategy for Three-Phase PWM Boost RectifierHoàngMạnhTuấnNoch keine Bewertungen

- Voltage Sag and Mitigation Using Dynamic Voltage Restorer (DVR) SystemDokument6 SeitenVoltage Sag and Mitigation Using Dynamic Voltage Restorer (DVR) SystemUzhansEell-neinoNoch keine Bewertungen

- Multi-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LDokument6 SeitenMulti-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LveguruprasadNoch keine Bewertungen

- Application of Dynamic Voltage Restorer in Electrical Distribution System For Voltage Sag CompensationDokument9 SeitenApplication of Dynamic Voltage Restorer in Electrical Distribution System For Voltage Sag CompensationtheijesNoch keine Bewertungen

- Naresh DC Re Injection FinalDokument6 SeitenNaresh DC Re Injection FinalRamu ThommandruNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- <!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01 Transitional//EN" "http://www.w3.org/TR/html4/loose.dtd"> <HTML><HEAD><META HTTP-EQUIV="Content-Type" CONTENT="text/html; charset=iso-8859-1"> <TITLE>ERROR: The requested URL could not be retrieved</TITLE> <STYLE type="text/css"><!--BODY{background-color:#ffffff;font-family:verdana,sans-serif}PRE{font-family:sans-serif}--></STYLE> </HEAD><BODY> <H1>ERROR</H1> <H2>The requested URL could not be retrieved</H2> <HR noshade size="1px"> <P> While trying to process the request: <PRE> TEXT http://www.scribd.com/titlecleaner?title=GA+Theory+and+Application.pdf HTTP/1.1 Host: www.scribd.com Proxy-Connection: keep-alive Accept: */* Origin: http://www.scribd.com X-CSRF-Token: 4b2a6d0ed0819ae0976fcd232108bff2fc91a576 X-Requested-With: XMLHttpRequest User-Agent: Mozilla/5.0 (Windows NT 6.1) AppleWebKit/537.17 (KHTML, like Gecko) Chrome/24.0.1312.57 Safari/537.17 Referer: http://www.scribd.com/upload-document?archive_doc=59380139&meDokument108 Seiten<!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01 Transitional//EN" "http://www.w3.org/TR/html4/loose.dtd"> <HTML><HEAD><META HTTP-EQUIV="Content-Type" CONTENT="text/html; charset=iso-8859-1"> <TITLE>ERROR: The requested URL could not be retrieved</TITLE> <STYLE type="text/css"><!--BODY{background-color:#ffffff;font-family:verdana,sans-serif}PRE{font-family:sans-serif}--></STYLE> </HEAD><BODY> <H1>ERROR</H1> <H2>The requested URL could not be retrieved</H2> <HR noshade size="1px"> <P> While trying to process the request: <PRE> TEXT http://www.scribd.com/titlecleaner?title=GA+Theory+and+Application.pdf HTTP/1.1 Host: www.scribd.com Proxy-Connection: keep-alive Accept: */* Origin: http://www.scribd.com X-CSRF-Token: 4b2a6d0ed0819ae0976fcd232108bff2fc91a576 X-Requested-With: XMLHttpRequest User-Agent: Mozilla/5.0 (Windows NT 6.1) AppleWebKit/537.17 (KHTML, like Gecko) Chrome/24.0.1312.57 Safari/537.17 Referer: http://www.scribd.com/upload-document?archive_doc=59380139&meIshu PathyNoch keine Bewertungen

- A Four-Leg Unified Series-Parallel Active Filter System For PeriodicDokument12 SeitenA Four-Leg Unified Series-Parallel Active Filter System For PeriodicMihir HembramNoch keine Bewertungen

- Effectiveness of DSTATCOM To Compensate The Load Current HarmonicsDokument6 SeitenEffectiveness of DSTATCOM To Compensate The Load Current HarmonicsMihir HembramNoch keine Bewertungen

- FX 2410731080Dokument8 SeitenFX 2410731080Mihir HembramNoch keine Bewertungen

- Energy MetersDokument44 SeitenEnergy Meterssrikrish24Noch keine Bewertungen

- Optimized Restoration of Unbalanced Distribution SystemsDokument7 SeitenOptimized Restoration of Unbalanced Distribution SystemsMihir HembramNoch keine Bewertungen

- 18 IJTPE Issue12 Vol4 No3 Sep2012 pp126 132Dokument7 Seiten18 IJTPE Issue12 Vol4 No3 Sep2012 pp126 132Mihir HembramNoch keine Bewertungen

- 3 6Dokument10 Seiten3 6Mihir HembramNoch keine Bewertungen

- Simplified Control Scheme of Unified Power Quality ConditionerDokument15 SeitenSimplified Control Scheme of Unified Power Quality ConditionerMihir HembramNoch keine Bewertungen

- Simplified Control Scheme of Unified Power Quality ConditionerDokument15 SeitenSimplified Control Scheme of Unified Power Quality ConditionerMihir HembramNoch keine Bewertungen

- Researchpaper Design and Simulation of A Novel Self Supported Dynamic Voltage Restorer DVRDokument6 SeitenResearchpaper Design and Simulation of A Novel Self Supported Dynamic Voltage Restorer DVRMihir HembramNoch keine Bewertungen

- 15 Jpe-10268Dokument7 Seiten15 Jpe-10268Mihir HembramNoch keine Bewertungen

- Upfc Power FlowcontrolDokument5 SeitenUpfc Power FlowcontrolRaghav Tu Jane NaaNoch keine Bewertungen

- Doi - 10.1016 - J.epsr.2004.01.017 - 1-S2.0-S0378779604000628-Main PDFDokument12 SeitenDoi - 10.1016 - J.epsr.2004.01.017 - 1-S2.0-S0378779604000628-Main PDFMihir HembramNoch keine Bewertungen

- Brief TutorialDokument22 SeitenBrief TutorialMario CifuentesNoch keine Bewertungen

- Kondur 1Dokument600 SeitenKondur 1Mihir HembramNoch keine Bewertungen

- PsatDokument29 SeitenPsatkikafhNoch keine Bewertungen

- OPTIMAL UPFC LOCATION FOR INCREASING LOADABILITYDokument6 SeitenOPTIMAL UPFC LOCATION FOR INCREASING LOADABILITYMihir HembramNoch keine Bewertungen

- 5807 Simulink TutorialDokument31 Seiten5807 Simulink TutorialSureshNoch keine Bewertungen

- Electrical PDFDokument5 SeitenElectrical PDFMihir HembramNoch keine Bewertungen

- Thyristor PDFDokument10 SeitenThyristor PDFMihir HembramNoch keine Bewertungen

- Lithography GuideDokument29 SeitenLithography GuidezanibtahiraNoch keine Bewertungen

- P1 Conservation and Dissipation of Energy Student Book AnswersDokument11 SeitenP1 Conservation and Dissipation of Energy Student Book AnswersjoeNoch keine Bewertungen

- Duet CE-3301 Geotechnical Engineering - IDokument37 SeitenDuet CE-3301 Geotechnical Engineering - IShekh Muhsen Uddin AhmedNoch keine Bewertungen

- False Ceiling Construction Details PDFDokument2 SeitenFalse Ceiling Construction Details PDFAlexis17% (6)

- Case Study Cracked Oil Tanks Investigations Web PDFDokument2 SeitenCase Study Cracked Oil Tanks Investigations Web PDFyamakunNoch keine Bewertungen

- Thinking ForthDokument311 SeitenThinking ForthCristianNoch keine Bewertungen

- 3 Phase Induction Motors Objective Questions With AnswersDokument3 Seiten3 Phase Induction Motors Objective Questions With AnswersMohan Raj0% (2)

- G. ACI 360R-06 Brings Slabs On Ground Into The 21st Century - Art McKinney PDFDokument2 SeitenG. ACI 360R-06 Brings Slabs On Ground Into The 21st Century - Art McKinney PDFinitbashNoch keine Bewertungen

- A320 Aircraft CharacteristicsDokument387 SeitenA320 Aircraft CharacteristicsEder LucianoNoch keine Bewertungen

- Product Design Recommended Reading ListDokument3 SeitenProduct Design Recommended Reading ListSai Prasath100% (1)

- Oksd Icwh 1993 RoisumDokument40 SeitenOksd Icwh 1993 RoisumKamalam CloudsoftNoch keine Bewertungen

- 1986 Lobel RobinsonDokument18 Seiten1986 Lobel RobinsonNathallia SalvadorNoch keine Bewertungen

- 83 - Detection of Bearing Fault Using Vibration Analysis and Controlling The VibrationsDokument12 Seiten83 - Detection of Bearing Fault Using Vibration Analysis and Controlling The VibrationsmaulikgadaraNoch keine Bewertungen

- SRDK Cryocooler Service Manual: For Service Personnel OnlyDokument151 SeitenSRDK Cryocooler Service Manual: For Service Personnel OnlyOtávio PagnoncelliNoch keine Bewertungen

- Strength of Pressure Vessels With Ellipsoidal HeadsDokument8 SeitenStrength of Pressure Vessels With Ellipsoidal Headsنصرالدين ادريسNoch keine Bewertungen

- Galvanize Galvanize Business Unit: Trust Us To GalvanizeDokument6 SeitenGalvanize Galvanize Business Unit: Trust Us To GalvanizeAdet WildanNoch keine Bewertungen

- ZXONE Quick Installation Guide - V1.0Dokument56 SeitenZXONE Quick Installation Guide - V1.0kmad100% (2)

- Hit-Re 500 With Hit-V Has RodsDokument3 SeitenHit-Re 500 With Hit-V Has RodsMKNoch keine Bewertungen

- Classification of FluidDokument29 SeitenClassification of FluidAbdur RehmanNoch keine Bewertungen

- 01chapter 5-1Dokument55 Seiten01chapter 5-1AhmNoch keine Bewertungen

- Odv-065r18ejj-G DS 2-0-3Dokument1 SeiteOdv-065r18ejj-G DS 2-0-3Евгений Переверзев0% (1)

- AP Create Accounting - Options & ExplanationDokument2 SeitenAP Create Accounting - Options & ExplanationSaleem JavedNoch keine Bewertungen

- Cs 180 Notes UCLADokument3 SeitenCs 180 Notes UCLAnattaq12345Noch keine Bewertungen

- Fem Question PaperDokument4 SeitenFem Question PaperARSNoch keine Bewertungen

- CUCM Intracluster Port Usage GuideDokument3 SeitenCUCM Intracluster Port Usage GuideAbhinayMylavarapuNoch keine Bewertungen

- A Report On Workability of Fresh Concrete by Slump TestDokument5 SeitenA Report On Workability of Fresh Concrete by Slump TestRishabhJain100% (1)

- Hydraulic Mining Shovel 6040AC: 08. Attachment Functions - FSDokument20 SeitenHydraulic Mining Shovel 6040AC: 08. Attachment Functions - FShector50% (2)

- 25kl SS Tank EstimateDokument1 Seite25kl SS Tank EstimateRaja ManiNoch keine Bewertungen

- Master Opp GaveDokument84 SeitenMaster Opp GaveRizki Al AyyubiNoch keine Bewertungen