Beruflich Dokumente

Kultur Dokumente

DCT Larry

Hochgeladen von

jin11004Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

DCT Larry

Hochgeladen von

jin11004Copyright:

Verfügbare Formate

1

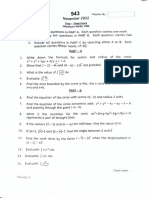

Case Study: DCT

(Larry)

Slides are prepared by Prof. Shao-Yi Chien,

Information Theory and Coding Technique

DSP in VLSI Design Shao-Yi Chien 2

Outline

DCT Algorithm

1-D DCT : Row-Column Method

Direct 2-D Architecture

3

DCT Algorithm

DSP in VLSI Design

Discrete Fourier Transform (DFT)

Shao-Yi Chien 4

DSP in VLSI Design

Discrete Cosine Transform (DCT)

Shao-Yi Chien 5

DSP in VLSI Design

Shao-Yi Chien 6

DSP in VLSI Design

Shao-Yi Chien 7

DSP in VLSI Design Shao-Yi Chien 8

Discrete Cosine Transform

DCT

block size 8 x 8

( ie.N=8 )

DSP in VLSI Design Shao-Yi Chien 9

DCT-Based Coding

Optimal transform is KLT, but

KLT is image dependent

High computing complexity

DCT-based coding,

Image independent, unlike KLT for highly

correlated image data

DCT compaction efficiency is close to KLT

Computations of DCT can be performed with fast

algorithms which can be easily implemented on

parallel architectures.

DSP in VLSI Design Shao-Yi Chien 10

Roles in Video Encoder

DCT Q

IQ

IDCT

Frame(s)

Memory

Motion

Estimation

Entropy

Coding

Rate Control

Compressed

Data T

Motion Vector

Q-Step

Original

Sequence

M

u

l

t

i

p

l

e

x

e

r

Bitstream

Motion

Coding

Compressed

Data M

DSP in VLSI Design Shao-Yi Chien 11

Roles in Video Decoder

IQ IDCT

Frame(s)

Memory

Entropy

Decoding

Compressed

Data T

Motion Vector

Q-Step

D

e

m

u

l

t

i

p

l

e

x

e

r

Bitstream

Motion

Decoding

Reconstructed

Sequence

Compressed

Data M

DSP in VLSI Design Shao-Yi Chien 12

Hardware/Software Trade-Off

For low-end applications, using software

approach is powerful enough

For high-end applications, must use hardware

approach

For middle-end applications, either software or

hardware approach is possible, depending on

the target design platform

DSP in VLSI Design Shao-Yi Chien 13

Basic Transformation Forms

2-D forward transforms

2-D inverse transforms

=

=

=

1

0

1

0

) , , , ( ) , ( ) , (

N

x

N

y

v u y x f y x g v u T

=

=

=

1

0

1

0

) , , , ( ) , ( ) , (

N

u

N

v

v u y x i v u T y x g

DSP in VLSI Design Shao-Yi Chien 14

1-D Discrete Cosine Transform

Forward DCT

Backward DCT

DSP in VLSI Design Shao-Yi Chien 15

1D 8-Point DCT Basis Functions

k = 0

k = 1

k = 5

k = 3

k = 4

k = 7

k = 2

k = 6

DSP in VLSI Design Shao-Yi Chien 16

2-D Discrete Cosine Transform

Forward DCT

Backward DCT

=

=

otherwise , 1

0 , for , 2 / 1

) ( ), ( where

n m

n u m u

Block size = N x N

X(m,n) : DCT coefficients

x(i,j) : image samples in block

DSP in VLSI Design Shao-Yi Chien 17

2-D 8x8 DCT Basis Functions

The DCT represents each block of image

samples as a weighted sum of 2-D cosine

functions (basis functions)

DSP in VLSI Design Shao-Yi Chien 18

DCT Coefficients

dc

Low

frequencies

Medium

frequencies

High

frequencies

dc

Vertical edges

High

frequencies

DSP in VLSI Design Shao-Yi Chien 19

An Example of Energy Compaction

DSP in VLSI Design Shao-Yi Chien 20

An Example of DCT

DC: F(0,0)= (1/8) EE f(m,n)

related to the average value of the block

52 55 61 66 71 61 64 73

63 59 66 90 109 585 69 72

62 59 68 113 144 104 66 73

63 58 71 122 154 106 70 69

67 61 68 104 126 88 68 70

79 65 60 70 77 68 58 75

85 71 64 59 55 61 65 83

87 79 69 58 65 76 78 94

609 -29 -62 25 55 -20 -1 3

7 -21 -62 9 11 -7 -6 6

-46 8 77 -25 -30 10 7 -5

-50 13 35 -15 -9 6 0 3

11 -8 -13 -2 -1 1 -4 1

-10 1 3 -3 -1 0 2 -1

-4 -1 2 -1 2 -3 1 -2

-1 -1 -1 -2 -1 -1 0 -1

DCT IDCT

Pixel Domain

Frequency Domain

DC

AC

DSP in VLSI Design Shao-Yi Chien 21

DCT Algorithm Classification

Direct 2-D Method

The 2-D transforms, DCT and IDCT, to be applied directly on

the N x N input data items

Row-Column Method

The 2-D transform can be carried out with two passes of 1-D

transforms

The separability property of 2-D DCT/IDCT allows the

transform to be applied on one dimension (row) then on the

other (column)

Requires 2N instances of N-point 1-D DCT to implement an

N x N 2-D DCT

DSP in VLSI Design Shao-Yi Chien 22

Row-Column Decomposition

1D DCT

UNIT

1D DCT

UNIT

TRANSPOSE

MEMORY

X

Z

(Y)

Y=AX Z=YA

T

Separable,

row-column decomposition

T

AXA Z =

0 for 1 ) ( and

2

1

) 0 (

1 ,..., 1 , 0 ,

]

4

) 1 2 ( 2

cos[ ) (

2

) , (

= = =

=

+

=

k k c c

N n k

N

k n

k c

N

n k a

t

DSP in VLSI Design Shao-Yi Chien 23

Straightforward Approach

Carry out the computation as full matrix-vector

multiplications

1-D transform requires N*N multiplications and N* (N-1)

additions

2-D transform requires N*N*N*N multiplications and N * N

*(N * N-1) additions

Although requiring the most number of operations, this

method is very regular

Most suitable for vector processors or deeply pipelined

architectures for high PE utilization

1-D fast algorithms => O(N*logN)

2-D fast algorithms => O(N*N*logN)

DSP in VLSI Design Shao-Yi Chien 24

DSP in VLSI Design Shao-Yi Chien 25

DSP in VLSI Design Shao-Yi Chien 26

DSP in VLSI Design Shao-Yi Chien 27

DSP in VLSI Design Shao-Yi Chien 28

DSP in VLSI Design Shao-Yi Chien 29

x(2)

x(2)

DSP in VLSI Design Shao-Yi Chien 30

DSP in VLSI Design Shao-Yi Chien 31

DSP in VLSI Design Shao-Yi Chien 32

DSP in VLSI Design Shao-Yi Chien 33

34

1-D DCT

Row-Column

Method

DSP in VLSI Design Shao-Yi Chien 35

Row-Column Method(1/2)

Basic concept

2-D DCT = 1-D DCT(row) 1-D DCT(column)

1-D DCT 1-D DCT MEMORY

DCT for row DCT for column

Input (X) Output (Z)

(Y)

DSP in VLSI Design Shao-Yi Chien 36

1-D DCT

TRANSPOSE

MEMORY

Row-Column Method(2/2)

Use transpose memory

Input (X) Output

(Y)

(Z)

Z = AXA

T

(A)

37

Row-Column

Method Example

A. Madisetti and A. N. Willson Jr., A 100 MHz 2-D

8x8 DCT/IDCT processor for HDTV applications,

IEEE Transactions on Circuits and Systems for Video

Technology, vol. 5, no. 2, April 1995

DSP in VLSI Design Shao-Yi Chien 38

Matrix Decomposition

Reduce an 8x8 matrix computation to two

4x4 matrix computation

DCT

IDCT

DSP in VLSI Design Shao-Yi Chien 39

Implementation(1/9)

For 8-bit 1D-DCT unit array A:

Y = AX

DSP in VLSI Design Shao-Yi Chien 40

Implementation(2/9)

Use symmetrical property of DCT coefficients:

DCT

IDCT

DSP in VLSI Design Shao-Yi Chien 41

Overall Architecture (1/2)

Architecture:

DSP in VLSI Design Shao-Yi Chien 42

Overall Architecture (2/2)

BDEG MATRIX VECTOR MULTIPLIER

TRANSPOSE

MEMORY

IDRU DRU

ACF MATRIX VECTOR MULTIPLIER

DSP in VLSI Design Shao-Yi Chien 43

X

Y

MUX

MUX

LIFO

Data Reorder Unit (1/3)

DRU architecture

add sub even odd

DCT IDCT

DSP in VLSI Design Shao-Yi Chien 44

Y

7

Y

6

Y

5

Y

4

X

3

X

2

X

1

X

0

Y

3

Y

2

Y

1

Y

0

Y

0

Y

1

Y

2

Y

3

X

3

X

2

X

1

X

0

Y

5

Y

4

X

1

X

0

Y

3

Y

2

Y

1

Y

0

Y

2

Y

3

X

1

X

0

Y

1

Y

0

Y

6

Y

5

Y

4

X

2

X

1

X

0

Y

3

Y

2

Y

1

Y

0

Y

1

Y

2

Y

3

X

2

X

1

X

0

Y

0

Y

0

Y

0

Y

2

Y

1

Y

0

Y

2

Y

1

Y

0

Y

1

Y

0

Y

1

Y

0

Y

3

Y

2

Y

1

Y

0

Y

3

Y

2

Y

1

Y

0

Y

4

X

0

Y

3

Y

2

Y

1

Y

0

Y

3

X

0

Y

2

Y

1

Y

0

X

Y

MUX

MUX LIFO

Data Reorder Unit (2/3)

DRU_1 Data flow:

DSP in VLSI Design Shao-Yi Chien 45

Data Reorder Unit (3/3)

DRU_2 Data flow:

add sub even odd

Y

0

Y

1

Y

2

Y

3

Y

7

Y

6

Y

5

Y

4

Y

0

+ Y

7

Y

1

+ Y

6

Y

2

+ Y

5

Y

3

+ Y

4

Y

0

- Y

7

Y

1

- Y

6

Y

2

- Y

5

Y

3

- Y

4

Y

0

Y

6

Y

2

Y

4

Y

7

Y

1

Y

5

Y

3

DSP in VLSI Design Shao-Yi Chien 46

Matrix multiplier (1/4)

ACF matrix vector multiplier

acc0

DSP in VLSI Design Shao-Yi Chien 47

Matrix multiplier (2/4)

BDEG matrix vector multiplier

acc0

DSP in VLSI Design Shao-Yi Chien 48

Matrix multiplier (3/4)

Hardwired multipliers

Use Sign Digit Code(SDC) number system

DSP in VLSI Design Shao-Yi Chien 49

Matrix multiplier (4/4)

Accumulator

DSP in VLSI Design Shao-Yi Chien 50

Transpose Memory (1/2)

Pin-pong mode

Using RAMs

ADDR

0 1 2 3... 7 8 9 10 11...15 16 17...62 63

0 8 16 24...56 1 9 17 25...57 2 10...55 63

0 1 2 3... 7 8 9 10 11...15 16 17...62 63

.

.

.

TIME

DSP in VLSI Design Shao-Yi Chien 51

Transpose Memory (2/2)

Using registers

(0,7) (0,6) (0,0)

(6,7)

(7,7) (7,6)

(6,6)

(7,0)

(6,0)

IN

. . .

. . .

. . .

.

.

.

.

.

.

.

.

.

MUX

OUT

DSP in VLSI Design Shao-Yi Chien 52

Scheduling

i: block index

R: row

C: column

X

XiR0

XiR7

Y

Y

YiC7 YiC0

Z

ZiC7 ZiC0

YiR0

YiR7

DSP in VLSI Design Shao-Yi Chien 53

Scheduling

DRU

ACF/

BDEG

IDRU

X0R0

X0R0 >

Y0R0

Y0R0

X0R1

X0R1 >

Y0R1

Y0R1

X0R2

X0R2 >

Y0R2

Y0R2

X0R3

X0R3 >

Y0R3

Y0R3

X0R4

X0R4 >

Y0R4

Y0R4

X0R5

X0R5 >

Y0R5

Y0R5

X0R6

X0R6 >

Y0R6

8 cycles

DSP in VLSI Design Shao-Yi Chien 54

Scheduling

DRU

ACF/

BDEG

IDRU

Y0R5

X0R6

X0R6 >

Y0R6

Y0R6

X0R7

X0R7 >

Y0R7

Y0R7

8 cycles

X1R0

X1R0 >

Y1R0

Y1R0

X1R1

X1R1 >

Y1R1

Y1R1

X1R2

X1R2 >

Y1R2

Y1R2

X1R3

X1R3 >

Y1R3

Y1R3

X1R4

X1R4 >

Y1R4

Y0C0

Y0C0 >

Z0C0

Z0C0

Y0C1

Y0C1 >

Z0C1

Z0C1

Y0C2

Y0C2 >

Z0C2

Z0C2

Y0C3

Y0C3 >

Z0C3

Z0C3

Y0C4

100% hardware utilization!

55

Direct 2-D DCT

Architecture

DSP in VLSI Design Shao-Yi Chien 56

Direct 2-D DCT Method

Computing the transform directly from the N x

N input numbers

Derive fast DCT algorithms from the signal flow

graph (like FFT)

Based on 1-D DCT

Larger flow graph

Global routing

More temporal storage

Larger datapath

DSP in VLSI Design Shao-Yi Chien 57

An Example

of 2-D DCT Architecture

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- A Tutorial On HybridDokument56 SeitenA Tutorial On HybridHarissaMariaNoch keine Bewertungen

- A Tutorial On HybridDokument56 SeitenA Tutorial On HybridHarissaMariaNoch keine Bewertungen

- Hybrid Technology AVL CapabilitiesDokument52 SeitenHybrid Technology AVL Capabilitiesgunardi1204Noch keine Bewertungen

- Grade 7 Math Learning Module Q2Dokument81 SeitenGrade 7 Math Learning Module Q2eustoque266879% (29)

- DCT 4Dokument2 SeitenDCT 4jin11004Noch keine Bewertungen

- Converting DCT Coefficients To H.264/AVC: Mitsubishi Electric Research Laboratories, Inc., 2004Dokument11 SeitenConverting DCT Coefficients To H.264/AVC: Mitsubishi Electric Research Laboratories, Inc., 2004jin11004Noch keine Bewertungen

- Automotive Transmissions1Dokument0 SeitenAutomotive Transmissions1jin11004Noch keine Bewertungen

- Dct-Domain Blind Measurement of Blocking Artifacts in Dct-Coded ImagesDokument4 SeitenDct-Domain Blind Measurement of Blocking Artifacts in Dct-Coded Imagesjin11004Noch keine Bewertungen

- Contents.: The M Double-Clutch Transmission With DrivelogicDokument21 SeitenContents.: The M Double-Clutch Transmission With DrivelogicalbeikNoch keine Bewertungen

- Blinn DCTDokument6 SeitenBlinn DCTjin11004Noch keine Bewertungen

- 0010 ItipDokument6 Seiten0010 Itipjin11004Noch keine Bewertungen

- Steganography Technique Based On DCT CoefficientsDokument5 SeitenSteganography Technique Based On DCT Coefficientsjin11004Noch keine Bewertungen

- Converting DCT Coefficients To H.264/AVC: Mitsubishi Electric Research Laboratories, Inc., 2004Dokument11 SeitenConverting DCT Coefficients To H.264/AVC: Mitsubishi Electric Research Laboratories, Inc., 2004jin11004Noch keine Bewertungen

- Dune™ Compact ScalesDokument2 SeitenDune™ Compact Scalesjin11004Noch keine Bewertungen

- 5116.DCT FilterDokument52 Seiten5116.DCT Filterjin11004Noch keine Bewertungen

- Ce 21515521Dokument7 SeitenCe 21515521jin11004Noch keine Bewertungen

- D C T 7 4 8 Series Owner'S ManualDokument84 SeitenD C T 7 4 8 Series Owner'S ManualmarcelodelrockNoch keine Bewertungen

- Paper (4) 35 41Dokument7 SeitenPaper (4) 35 41jin11004Noch keine Bewertungen

- Ijcs 34 2 02Dokument7 SeitenIjcs 34 2 02jin11004Noch keine Bewertungen

- Ijcs 34 2 02Dokument7 SeitenIjcs 34 2 02jin11004Noch keine Bewertungen

- DCTDokument11 SeitenDCTjin11004Noch keine Bewertungen

- L 000000000234135Dokument4 SeitenL 000000000234135jin11004Noch keine Bewertungen

- Converting DCT Coefficients To H.264/AVC: Mitsubishi Electric Research Laboratories, Inc., 2004Dokument11 SeitenConverting DCT Coefficients To H.264/AVC: Mitsubishi Electric Research Laboratories, Inc., 2004jin11004Noch keine Bewertungen

- Dct-Domain Blind Measurement of Blocking Artifacts in Dct-Coded ImagesDokument4 SeitenDct-Domain Blind Measurement of Blocking Artifacts in Dct-Coded Imagesjin11004Noch keine Bewertungen

- VQMDokument10 SeitenVQMjin11004Noch keine Bewertungen

- Miller W04Dokument96 SeitenMiller W04jin11004Noch keine Bewertungen

- Phev Study Final ReportDokument218 SeitenPhev Study Final Reportjin11004Noch keine Bewertungen

- Beamer Technical Vienna Presentation v0425Dokument47 SeitenBeamer Technical Vienna Presentation v0425jin11004Noch keine Bewertungen

- DCT Theory and ApplicationDokument32 SeitenDCT Theory and ApplicationAhmed SoulimanNoch keine Bewertungen

- 1208 3133Dokument5 Seiten1208 3133jin11004Noch keine Bewertungen

- DCT - Strang - Direct Cosine TransformDokument23 SeitenDCT - Strang - Direct Cosine TransformmarcoNoch keine Bewertungen

- A First Course in Discrete Mathematics - I. AndersonDokument200 SeitenA First Course in Discrete Mathematics - I. AndersonB . HassanNoch keine Bewertungen

- Introduction To Fuzzy SetDokument2 SeitenIntroduction To Fuzzy SetTria Putri NoviasariNoch keine Bewertungen

- Mat FinalDokument7 SeitenMat Finalsanathhegde2018Noch keine Bewertungen

- Final Synopsis Neetu GuptaDokument25 SeitenFinal Synopsis Neetu Guptanarendrakum16Noch keine Bewertungen

- Ncert Solutions Class 10 Maths Chapter 10 CirclesDokument24 SeitenNcert Solutions Class 10 Maths Chapter 10 Circleshetv031013Noch keine Bewertungen

- MMW - Problem Set 1 Module 2Dokument5 SeitenMMW - Problem Set 1 Module 2John Rave Manuel GonzalesNoch keine Bewertungen

- (De Gruyer Studies in Mathematical Physics) Anna G. Chunovkina, Leonid A. Mironovsky, Valery A. Slaev-Metrology and Theory of Measurement-De Gruyter (2013)Dokument585 Seiten(De Gruyer Studies in Mathematical Physics) Anna G. Chunovkina, Leonid A. Mironovsky, Valery A. Slaev-Metrology and Theory of Measurement-De Gruyter (2013)Govinda Prasad DhunganaNoch keine Bewertungen

- MFSAS Exam 2014 SolutionsDokument5 SeitenMFSAS Exam 2014 Solutionstasos_rex3139Noch keine Bewertungen

- Maths November 2022 Question PaperDokument6 SeitenMaths November 2022 Question PaperKumar SubramanianNoch keine Bewertungen

- Homotopy PDFDokument9 SeitenHomotopy PDFPllamenowa IvoNoch keine Bewertungen

- Trigonometric Equation: Solved ExampleDokument32 SeitenTrigonometric Equation: Solved Example10x RiderNoch keine Bewertungen

- Ben Green and Progression of Prime NumbersDokument19 SeitenBen Green and Progression of Prime Numbersslavojzizek69Noch keine Bewertungen

- Math 131-Spring 13-Course Outline PDFDokument3 SeitenMath 131-Spring 13-Course Outline PDFvejoshi21699Noch keine Bewertungen

- Math Project Work: Name - Shubhanshu Bhargava CLASS - 10 Section - A Shift-I ShiftDokument20 SeitenMath Project Work: Name - Shubhanshu Bhargava CLASS - 10 Section - A Shift-I ShiftSumit yadavNoch keine Bewertungen

- Course NotesDokument31 SeitenCourse Notestesting543Noch keine Bewertungen

- 007 Examples Constraints and Lagrange EquationsDokument12 Seiten007 Examples Constraints and Lagrange EquationsImran AnjumNoch keine Bewertungen

- MultipleQuestions IntegrationDokument4 SeitenMultipleQuestions IntegrationChashan DeepNoch keine Bewertungen

- CH03 895267Dokument50 SeitenCH03 895267Pablo GomezNoch keine Bewertungen

- Report Shooting MethodDokument7 SeitenReport Shooting MethodahmedNoch keine Bewertungen

- 2.7 - Gauss Divergence TheoremDokument44 Seiten2.7 - Gauss Divergence TheoremindraNoch keine Bewertungen

- Assignment 6 Real Analysis Iit GDokument1 SeiteAssignment 6 Real Analysis Iit GGautam BorahNoch keine Bewertungen

- Teaching of Mathematics in Singapore Secondary SchoolDokument13 SeitenTeaching of Mathematics in Singapore Secondary SchoolLetharic 07Noch keine Bewertungen

- Solving Reynolds Equation Using Pseudospectral MethodDokument19 SeitenSolving Reynolds Equation Using Pseudospectral MethodKiranmayee KolluruNoch keine Bewertungen

- Referensi Pendidikan Matematika (Analisis Kesalahan Belajar KPK Dan FPB)Dokument11 SeitenReferensi Pendidikan Matematika (Analisis Kesalahan Belajar KPK Dan FPB)Dwi Kurniawan 354313Noch keine Bewertungen

- Chapter 3Dokument37 SeitenChapter 3behnamjpNoch keine Bewertungen

- Time Series.Dokument97 SeitenTime Series.Pranav Khanna100% (1)

- Ee101 DGTL 1 PDFDokument144 SeitenEe101 DGTL 1 PDFShubham KhokerNoch keine Bewertungen

- VL2019205005389 Da PDFDokument44 SeitenVL2019205005389 Da PDFsimon jordan1005Noch keine Bewertungen

- Cluster 4Dokument34 SeitenCluster 4Gary SNoch keine Bewertungen