Beruflich Dokumente

Kultur Dokumente

Lica

Hochgeladen von

Manu anandOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lica

Hochgeladen von

Manu anandCopyright:

Verfügbare Formate

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

LIST OF EXPERIMENTS

S.No.

NAME OF EXPERIMENTS

EXPERIMENT NO.

ECE-LICA-EX-01

2.

To study OP-AMP as adder and subtractor

circuits(IC-741).

To Study Op-amp as Differentiator & Integrator

3.

To study clipping circuits using OP-AMP(IC-741).

ECE-LICA-EX-03

4.

To study clamping circuits using OP-AMP(IC-741).

ECE-LICA-EX-04

5.

To study OP-AMP as Schmitt trigger(IC-741).

ECE-LICA-EX-05

6.

ECE-LICA-EX-06

8.

To study Astable multivibrator circuit using timer IC555.

To study monostable multivibrator circuit using timer

IC-555.

To study Frequency divider using IC-555.

9.

To design 2nd order low pass Butterworth filter

ECE-LICA-EX-09

1.

7.

ECE-LICA-EX-02

ECE-LICA-EX-07

ECE-LICA-EX-08

10. To design 2nd order high pass Butterworth filter.

ECE-LICA-EX-10

11. *To study an instrumentation amplifier using OPAMP (IC-741).

12. *To Study Op-amp as Inverting & Non.Inverting

Amplifier

ECE-LICA-EX-11

Prepared by:- Mr.Satpal Singh

ECE-LICA-EX-12

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

EXPERIMENT NO. 1

AIM: To study Operational amplifier as Adder and Subtractor using IC-741.

APPRATUS:-Digital Multimeter, CRO, Power supply, IC-741,R1=1k,R2=1k,RL=10k

CIRCUIT DIAGRAM:OP AMP AS ADDER:-

OP-AMP AS A SUBTRACTOR:-

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

PROCEDURE:OP AMP AS ADDER:Connect the circuit as shown in figure.

Switch on the instrument using on/off toggle switch provided on the front panel.

Apply input voltage at pin number 2 and 3 of IC-741 from both supplies and note

down the output voltages .

Repeat step 3rd for different I/P devices.

Calculate O/P voltage using.

Vout =Vin [RF/R1]+Vin [RF/R2]

OP-AMP AS A SUBTRACTOR:1.Connect the circuit as shown in figure.

2.Switch on the instruction instrument using ON/OFF toggle switch provided on the

front panel.

3.Apply different voltages at pin number 2 and 3 and note down the O/P voltage.

4.Calculate the O/P voltage using.

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Vout =Vin[1+RF/R2]-Vin[RF/R1]

RESULT:- OP-AMP as adder and subtractor is studied .

EXPERIMENT NO. 2

AIM:- To study Operational amplifier as Differentiator and Integrator using IC-741.

APPRATUS:-Digital Multimeter, CRO, function generator Power supply, IC741,Resistances,capacitances

CIRCUIT DIAGRAM:OP AMP AS DIFFERENTIATOR:OP-AMP AS INTEGRATOR:-

PROCEDURE:OP AMP AS DIFFERENTIATOR:Connect the circuit as shown in figure.

Switch on the instrument using on/off toggle switch provided on the front panel.

Apply input voltage at pin number 2 and note down the output voltage .

Calculate O/P voltage using.

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Vo=-RFC1dvin/dt

OP-AMP AS INTEGRATOR:1.Connect the circuit as shown in figure.

2.Switch on the instruction instrument using ON/OFF toggle switch provided on the

front panel.

3.Apply voltage at pin number 2 and note down the O/P voltage.

4.Calculate the O/P voltage using.

Vo=1/R1CFvindt

RESULT: - OP-AMP is studied as Differentiator and Integrator.

EXPERIMENT NO. 3

Aim: To study clipping circuits using OP-AMP(IC-741).

Apparatus required: CRO and frequency counter, patch cord BNC cable,DMM.

Theory:

1.The positive clipper : - A positive clipper is shown. Such clipper remove (clip)

+ve part of input signal applying a bias at output node. At no signal condition D1 is

forward biased since the bias voltage are applied at the inverting terminal. When +ve

half cycle of input signal is amplified the diode D1 is reversed biased at the instant

when input amplitude has magnitude equal to the bias. D1 is now reversed biased and

there is no furthur signal output except a dc voltage. If the polarity of bias is get

reversed as shown in fig 2, the D1 is imidiately cut - off if there is no input signal and

output is equal to bias level. Applying input signal on +ve half cycle there is no output

since D1 is revered biased. On -ve half cycle when the input signal magnitude cross

the bias level, d1 is forward biased and output signal is just a part of -ve half cycle.

2. Negative clipper :- A negitive clipper circuit is shown. Here diode D2 is forward

biased since the inverting terminal of op amp is applied with -ve bias. The input signal

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

is presented at output till its magnitude exceed the bias level cause to get reversed bias

the diode. inverting bias polarity cause to appear a part of +ve half of input signal as

was in positive clipper.

Waveform:-

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Negative clipper:-

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Wave Form:-

Procedure:1. Connect the circuit as shown in fig 1. Keep dc supply control to minimum ( zero).

Adjust function generator for sine wave 3Vpp output signal at 1 Khz frequency.

2. Observe the waveform at the output. Its +ve half is clipped due to D1. Now

increase the dc voltage (0-2Vdc) and observe its effect upon the output waveform.

Adjust dc voltage to +1V and trace the waveform. Bring the dc supply to minimum.

3. Revert the dc supply connections as shown in fig 2. Increse the dc supply and

observe its effect upon output waveform. Fix it at -1V and trace the waveform

PRECAUTION:All the connections should be proper

There should be no voltage fluctuations.

Readings should be taken carefully.

RESULT:- The given signal has been clippped by a value .Vref + Vp in case of +Ve

clippper & by ref. Vref negative in case of ve clipper.

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

EXPERIMENT NO. 4

AIM: To study clamping circuits using OP-AMP(IC-741).

APPARATUS USED:Digital multimeter, CRO , Function generator, IC 741,Power supply, Bread Board,

IC-741,diode, resistance, capacitor, connecting wires.

THEORY:In clamper circuit a predetermined level is added to the output voltage. If the clamped

dc level is positive, the clamper is the positive clamper. On the other hand, if the

clamped dc level is negative the clamper is called as negative clamper . These are also

called dc inserter or restorer.

In the negative half cycle, the diode d , in the circuit becomes the

forward bias and the circuit becomes a closed circuit .Due to this capacitor is charged

up to Vp. In positive half cycle the diode d1 is reversed bias. Due to this , circuit,

dont complete. The output voltage will be Vin(due to I/P voltage) +Vp(due to voltage

at capacitor) +Vref.(due to reference voltage applied at the non-inverting terminal of

the Op-Amp as shown in figure.

In the same way, negative clamper can also be obtained by changing the polarity of

reference voltage and polarity of diode.

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Procedure:1. Connect the circuit as shown in fig 1. Keep dc supply control to minimum ( zero).

Adjust function generator for sine wave 3Vpp output signal at 1 Khz frequency.

2. Observe the waveform at the output. Its +ve half is clipped due to D1. Now

increase the dc voltage (0-2Vdc) and observe its effect upon the output waveform.

Adjust dc voltage to +1V and trace the waveform. Bring the dc supply to minimum.

3. Revert the dc supply connections as shown in fig 2. Increse the dc supply and

observe its effect upon output waveform. Fix it at -1V and trace the waveform

PRECAUTION:All the connections should be proper

There should be no voltage fluctuations.

Readings should be taken carefully.

RESULT:- The given signal has been clamped by a value .Vref + Vp in case of +Ve

clamper & by ref. Vref negative in case of ve clamper.

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

EXPERIMENT NO.5

AIM: To design Schmitt trigger circuits using IC 741.

APPARATUS:

Dual trace oscilloscope ,Audio Signal Generator,2 Variable Power Supply, IC-741,

Resistors of 1k, 2k & 500, 2-Zener diodes (1N4735) of 6.2V, Connecting wires.

THEORY:

The construction of basic Schmitt trigger is shown in fig. Positive feedback is applied

through the resistive network R1 and R2. The input signal Vin is applied at the

negative terminal. A reference voltage Vr is fed into the feedback network through

R2. When V- is less then Vf the output is clamped at + Vo that is the positive

saturation voltage.

The feedback voltage at V+ is then given by:

V+(1)= (R1/R1+R2) Vin +(R2/R1+R2) Vo. (1)

When the input voltage gradually increase the above threshold level, V- become

greater than V+. Now the o/p switches to Vo .The ve saturation voltage as shown in

fig. (b). Accordingly the feedback voltage at the +ve terminal becomes:

V+(2)= (R1/R1+R2) Vin -(R2/R1+R2) Vo. (2)

As long as the negative terminal voltage is greater then the positive terminal

voltage, the circuit makes no transition, but suppose Vin start decreasing .the circuit

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

will switch back to initial condition only when Vin crosses the threshold V+(2) i.e.

Vin =V+(2). Thus, the schmitt trigger circuit has two-threshold voltage. V+(1) called

the upper threshold value (point) and V+(2) called the lower threshold point. This

threshold value is known as Vut & Vlt. Such circuits, where the forward and reverse

direction transition is not same are said to exhibit Hysterises. As shown in fig (b).

This hysterises is measured by

Vh= Vut Vlt.

Where Vut = R1/R1+R2 (+ VSAT) and Vlt = R1/R1+R2(-VSAT)

CIRCUIT DIAGRAM:

SCHMITT TRIGGER

PROCEDURE:

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

1. Connect the ckt. As shown in figure with component values R1 =2k, R2 =1k,

Roff =R2/R1= 680. Roff is the resistance incorporated. To minimum input

offset voltage.

2. Connect the signal generator with the input adjusted to 5V PP Sinewave, 1kHz.

Set the variable reference voltage Vr to 0V.

3. Observe both the input and output waveform on the C.R.O. Draw them on the

semilog graph paper.

4. Now adjust Vr to 1V and repeat 3 step.

5. Replace R2 (1k) to 100 ohms resistor. Repeat step 3.

RESULT: Schmitt trigger has been designed using IC-741.

EXPERIMENT NO.6

AIM: - To study the IC 555 as a monostable multivibrator.

APPARATUS USED:- CRO, , IC 555, Power supply, Bread board, , two resistance

of 2.2k & 3.9k,two capacitor of 0.1uf&. 01uf, triggering ckt,

THEORY: - A Monostable Multivibrator, often called a one-shot Multivibrator, is a

pulse-generating circuit in which the duration of the pulse is determined by the RC

network connected externally to the 555 timer. In a stable or stand by mode the

output of the circuit is approximately Zero or at logic-low level. When an external

trigger pulse is obtained, the output is forced to go high ( VCC). The time for which

the output remains high is determined by the external RC network connected to the

timer. At the end of the timing interval, the output automatically reverts back to its

logic-low stable state. The output stays low until the trigger pulse is again applied.

Then the cycle repeats. The Monostable circuit has only one stable state (output low),

hence the name monostable. Normally the output of the Monostable Multivibrator is

low.

Circuit Diagram

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Procedure:

1. Connect the circuit as shown in fig, selecting C equal to 100 uF and R = 100K.

Switch on the power. Observe the LED status ( in timer off position the LED will not

glow ).

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

2. Momentarily push the pulser key. The LED will change state as soon as IC get

triggered. Note the time from stop watch till IC goes into off position again. Repeat

the step two or three time and note the time. Change the R = 20K and repeat the step.

Calculate the theoratical time and compare the result.

3. Select lower value of C (01 mFD ) in place of previous capacitor. Connect CRO at

the output of ICand connect a function generator ( F.G ) at trigger input as shown in

dashed lines in fig., while remove the LED and pulser key connections.

3. Raise the square wave( 100 HZ ) amplitude till a waveform appears upon the CRO

screen. Trace the waveform appearing upon screen. Connect CRO at input and trace

the waveform.

4. Change the frequency of square wave say 200HZ and trace the input waveform.

Connect CRO back with the output of IC 555. Trace the waveform appearing.

5. Observe the waveforms from the input and the output. It is cleared that the mono

time of ICis constant in both input triggering frequencies.

Waveforms:

Monostable Multivibrator

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Precautions:

1.Check the connections before giving the power supply.

2.Readings should be taken carefully.

3. Connections should be made carefully.

RESULT:

An Monostable Multivibrator on IC-555 has been verified.

EXPERIMENT NO.7

Aim: To study Astable Multivibrator circuit using timer IC-555.

Apparatus required: CRO and frequency counter, patch cord BNC cable.

Theory: An Astable Multivibrator has two stable states and it keeps on switching

between these two states by itself . No external triggering signal is needed. The

astable multivibrator cannot remain indefinitely in any one of the two states.The two

amplifier stages of an astable multivibrator are regenerative across coupled by

capacitors.

When the power supply VCC is connected, the external timing capacitor C charges

towards VCC with a time constant (RA+RB) C. During this time, pin 3 is high (VCC) as

Reset R=0, Set S=1 and this combination makes Q =0 which has unclamped the

timing capacitor C.

Circuit Diagram:

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Astable Multivibrator

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Procedure:

1. Connct the circuit as shown in fig 3 connect CRO across the output, select C = .01

Uf and R 100K. Switch on the power. Observe the trace and copy it upon the paper.

Measure its time period from the calibrated CRO time / div or with a frequency

counter. Note the values of R(s) and C and evaluate the theoratical value.

2. Change the R value to 20 K. Observe the waveform. Is it slightly asymmetric Find

out the period from the trace or by frequency counter.

3. Connect CRO across the C and observe the waveform appearing. Is it exponential

tringular ? Plot all waveform one after one in sequence and conclude the result.

4. Connect the circuit as shown in fig 4. Connect two loose patch cords one with

ground and other with vcc sockets.

5. Switch on the power. Observe LED, if it is glowing ( the IC is set) determine

theICstate either set or reset.

6. If LED glows than momentarily touch loose end of vcc ( +5V) patch cord with the

pin 6 ( TR ). Observe the LED changes its state and goes off. Touch again grounded

lead with pin 2 ( TR ) The LED comes on. Wait for few time. Observe that the LED is

remain lit, which show the IC output remain in this stable state. Touch grounded lead

with pin 2 again and note it does not affect the stable state.

7. Touch momentarily positive connected ( +5V ) with pin 6 ( TH ) input and observe

the effect at the output. Retouch positive connected lead again observe it does not

affect the stable state. Conclude the result from the experiment.

Waveforms:

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Precautions:

1. Connections should be made carefully.

2. Readings should be noted without parallax error.

3.Set the input waveform of correct amplitude and frequency.

4. Connect the CRO to the output terminal.

Result: The output waveform is obtained and observed on the CRO.

EXPERIMENT NO.8

Aim: To study Timer IC 555 voltage controlled Oscillator.

Apparatus required: CRO and frequency counter, patch cord BNC cable,DMM.

Theory:

Timer I.C is designed to generate accurate and stable R - C defined periods, for use as

monostable and astable pulse generators. In fig 1, basic block diagram of 555 is

shown. It contains two voltage comparators, one flip - flop, one inverter and two

transistors as reset and discharge device. the two voltage comparators is provide a

voltage refrence by a resistive chain in such manner that, generates 1/ 3 vcc refrence

voltage to lower comparator non - inverting input and 2/ 3 vcc to inverting input of

upper comparator. The outputs of comparators are coupled with a R - S flip - flop

which set or reset by these voltages. The lower comparator is called as trigger

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

comparator and the upper as threshold comparator. The flip flop output goes low as

soon as the voltage at inverting pin of trigger comparator crosses the 1/ 3 vcc refrence.

The output available from I.C is in inverted form thus it goes high. The output of flip flop remains in this state untill the voltage at non - inverting input of threshold

comparator goes high than 2/ 3 vcc refrence. This reset the flip - flop and its output Q

goes high, whether the available output goes low due to invertion. The discharge

transistor comes into saturation and provide a low ohmic path from pin 7 ( discharge )

to ground. The Q2 work as reset transistor and reset the flip - flop as soon as it is

pulled to ground, ignoring any operation is done by comparators. This simple

artitecture of 555 is very useful for many applications. One application of this device

is to construct a voltage controlled oscillator as shown in fig 2.

The VCO : However, in cases or applications such as FM, tone generators, and

frequency-shift keying (FSK), the frequency is to be controlled by means of an input

voltage, called the control voltage. This can be achieved in a voltage-controlled

oscillator (VCO). A VCO is a circuit that provides an oscillating output signal

(typically of square-wave or triangular waveform) whose frequency can be adjusted

over a range by a dc voltage.The basic action of fig 2, circuit is such that, in each

operating cycle, timing capacitor C (.01uF) alternately charge at a rate (2I),

determined by RT1 (3K9) until the voltage Vc reaches upper threshold level (2/3

Vcc), at which point IC 555 toggles cause to saturate discharge transistor (pin 7). The

charging current (2), is blocked and C now discharge at constant rate (), determined

by RT2 (7K8) until the Vc reaches lower threshold level (1/3 Vcc), where again IC

555 toggles to high state. Since Q2 and Q3 are current sources which conducts

contineously during charge cycle, hence the charge current must be doubled equal to

2. During discharge cycle Q2 is cut off hence C discharge at rate equal to . Q1 acts

as balanced voltage divider.

CIRCUIT DIAGRAM:-

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

PROCEDURE:1. Connect CRO one channel across the timing capacitor C (pin 2 and ground).

Connect 2nd channel with output (pin 3 and ground). Connect DMM (dc range) with

Vin and ground.

2. Keep VR nearly centre. Switch on power.

3. Adjust CRO to obtain 3 or 4 waveforms. Observe the waveshape appear at CRO.

4. Now vary dc voltage by mean of VR and observe the change in waveform time.

5. Now bring the VR to obtain Vin = 2V. If freq counter is available connect it with f

out, otherwise measure time period T from CRO (cal mode) anf calculate freq f = 1/T.

6. Increase voltage in 0.5V steps and note the frequency for each voltage. Tabulate the

readings.

7. From the table plot VCO characteristics between Vin and f out. The straight line

show the linearity of VCO. The slope of curve gives control characteristics in Hz/v.

OBSERVATION TABLE:-

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Control voltage

Vin volts

2.0

2.5

3.0

3.5

4.0

4.5

5.0

5.5

6.0

Frequency

f out Hz

.......

.......

.......

.......

.......

.......

.......

.......

.......

WAVE FORM:-

RESULT: We are successfully output waveform is obtained and observed on the

CRO.

EXPERIMENT NO.9

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

AIM:To design a second order low pass Butterworth filter.

APPRATUS:

Digital Multimeter, CRO, Function generator, Power supply,IC-741, R 1 =27K,

R2=R3 =33K, RF =20K POT, RL=10K, C2=C3=0.0047F, Connecting wires.

OP - AMP LOW - HIGH PASS FILTER

The mean of filter is an electrical circuit which has property to select some

band of frequency

or say it is a frequency selective network. An active filter has some type of

amplification

involved to raise the Q of the filter. It offers more flexibility to adjust the

passband

gain, reduce loading upon the source and economical since it does not has

inductors. The

prime filters are low pass, high pass filters. The filters has some specific

characteristics

which is determined from the cut - off rate or attenuation rate. In brief

introductory low pass

filter is described.

The 1st order low pass filter : A low pass filter has property to pass out low

frequency band

which should below the cut - off frequency fc. There are many type of

electrical circuits to

construct these filter but Butterworth filter is common. In fig 1, basic low pass

filter is shown,

in which R - C has finite cut - off charateristics which can be realized by

expression given

as

Vo = Av{Vin / (1 + j RC)} .1

The above expression is true if the output Vo is terminated in very high

impedance. The

filter cut - off rate wil be -6 dB/ octave since it is a 1st order filter.

Design of filter : When terminated in op - amp (non- inveting input as it has

high impedance),

the transfer function of fig 1 filter is given as

Vo/ Vin = Av/ 1+ (f/fh)2 .2

where Av is voltage gain and fh is highest cut - off frequency.

Av = 1 + (RF / R1) .3

The angular cut - off frequency is

c = 1/RC or fc = 1/ 2RC .4

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Fig 1. A 1st order low pass filter.

Filter characteristics

For 2nd order circuit the cut - off frequency will be

The transfer function of filter is

Vo/Vin = Av / 1 + (f/fh)4

where Av is same as eq 3.

Fig 2. A 2nd order low pass filter.

Filter characteristics

A high pass filter has property to pass out high frequency band which should

above the cut

- off frequency fc. In fig 3, basic high pass filter is shown, in which R - C has

finite cut - off

charateristics which can be realized by expression given as

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Vo = Av[ Vin { ( j RC) / (1 + j RC) } ] .7

The above expression is true if the output Vo is terminated in very high

impedance. The

filter cut - off rate wil be -6 dB/ octave since it is a 1st order filter. The design

of filter is

same as low pass filter, only fh is change to fl (lowest cut - off frequency). The

2nd order

filter is shown in fig 4. The design equations are same as low pass filter.

Fig 3. A 1st order high pass filter.

Filter characteristics

THEORY: Second order filters are important because higher-order filters can be

designed using them. The gain of the second order filter is set by R 1 and RF, while the

high cut off frequency fH is determined by R2, C2, R3, and C3, as follows:

1

fH =

2 R2R3C2 C3

Furthermore, for a second order low-pass Butterworth response, the voltage gain

magnitude equation is

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

vo

AF

vin =

1+(f/fH)4

Where AF = 1+RF/R1= pass band gain of the filter

f = frequency of the input signal (Hz)

1

fH =

= high cutoff frequency (Hz)

2 R2R3C2 C3

PROCEDURE:

(1) Choose a value for the high cutoff frequency fH.

(2) To simply the design calculations, set R2 = R3 =R and C2 =C3=C. then choose a

value of C1F.

(3) Calculate the value of R using equation

R = 1/2fHC

(4) Finally, because of the equal resistor (R2 = R3) and capacitor (C2 = C3) values, the

pass band voltage gain AF =(1 + RF/R1) of the second-order low pass filter has to

be equal to 1.586. That is RF =0.586R: This gain is necessary to guarantee

Butterworth response. Hence choose a value of R1100 k and calculate the

value of RF.

(5) Connect the components according the circuit diagram shown.

(6) Connect the function generator at Vin. Keep the amplitude fixed & vary the

frequency.

(7) Observe the output Vo at CRO.

(8) Find the voltage gain Av. .

(9) Plot curve of gain VS frequency.

OBSERVATION TABLE:

Sr.

No.

FREQUENC

Y f (Hz)

INPUT

VOLTAG

E (in V)

OUTPUT

VOLTAG

E (in V)

GAIN MAGNITUDE=

V0/Vin

OBSERVED

MAGNITUDE (d B)=20

log V0/Vin

1.

2.

3.

PRECAUTIONS:

1. All the connections should be proper

2. There should be no voltage fluctuations.

3. Readings should be taken carefully.

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

RESULT: A 2ND ORDER LPF is designed using IC 741

EXPERIMENT NO.10

AIM:To design a secondorder high pass Butterworth filter .

APPRATUS:

Digital Multimeter, CRO, Function generator, IC 741, Power supply, R 1 =27K,

R2=R3 =33K, RF =20K POT, RL=10K, C2=C3=0.0047F.

CIRCUIT DIAGRAM:

THEORY: Second order filters are important because higher-order filters can be

designed using them. The gain of the second order filter is set by R 1 and RF, while the

lower cut off frequency fL is determined by R2, C2, R3, and C3, as follows:

1

fL =

2 R2R3C2 C3

Furthermore, for a second order high-pass Butterworth response, the voltage gain

magnitude equation is:

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

vo

vin

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

AE

=

1+(fL/f)4

Where AF = 1.586 voltage gain at pass band

fL =low cutoff frequency

PROCEDURE:

1. Choose a value for the lower cutoff frequency fL.

2. To simply the design calculations, set R2 = R3 =R and C2 =C3=C. then choose

a value of C1F.

3. Calculate the value of R using equation

R = 1/2fLC

4. Finally, because of the equal resistor (R2 = R3) and capacitor (C2 = C3) values,

the pass band voltage gain AF =(1 + RF/R1) of the second-order high pass filter

has to be equal to 1.586. That is RF =0.586R: This gain is necessary to

guarantee Butterworth response. Hence choose a value of R 1100 k and

calculate the value of RF.

5. Take the breadboard and put the IC-741 in to it.

6. Connect the different components according to the circuit diagram.

7. Connect function generator at Vin. Keep the amplitude fixed and vary the

frequency.

8. Observe the output Vo at CRO.

9. Find the voltage gain Av .

10. Plot curve of gain VS frequency.

OBSERVATION TABLE:

FREQUENCY RESPONSE DATA

Sr.

No.

FREQUENC

Y f (Hz)

INPUT

VOLTAG

E (in V)

OUTPUT

VOLTAG

E (in V)

GAIN MAGNITUDE=

V0/Vin

OBSERVED

MAGNITUDE (d B)=20

log V0/Vin

1.

2.

3.

PRECAUTIONS:

1. All the connections should be proper

2. There should be no voltage fluctuations.

3. Readings should be taken carefully.

4. IC- pin numbers should be counted from right end.

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

RESULT: The second order high pass Butterworth filter has been designed & its

frequency response been studied

EXPERIMENT NO.11

AIM: To study an instrumentation amplifier using OP-AMP (IC-741).

APPRATUS: Digital Multimeter, CRO,Power supply.

THEORY :

One of the most useful application of an op - amp is differential input dc amplifier

configuration. But in this configuration input impedances are not similar. Thus there

is three op - amp configuration is used which is called as 'Buffered differential input

instrumentation amplifier'.The loading effect of such configuration is negliable while

the voltage gain might be set for very large. However this tends to impair the common

mode rejection ratio (CMRR)and input offset voltage unbalance.

Differential amplifier ( I.A.) with variable gain.

In fig 1, such amplifier circuit is shown employing three op - amps. Here the bridge

balance is does not disturbed by the gain adjust control, thus CMRR is quite constant

at each gain setting. The offset voltage is usually disturbed with alteration in gain, but

it can be adjusted quite well.

Circuit description

The op - amp IC1 and 2, (CA3140), at front end acts as buffer, with voltage gain of G

approximately. The voltage gain G, is set by RF and RG1 as G = { 1 + ( 2RF / RG )}.

The 3rd op - amp 3140 is differential amplifier having unity voltage gain, which

depends upon the loop around it. Since feedback attenuation results in higher gain ,

which is achieved by

varying the RG, (selectable) yeilds to exactly the condition needed to maintain good

balance and high CMRR. The offset adjustment is carried out by summing the dc

voltages at the non - inverting input of

IC3.

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

(Fig:-The instrumentation amplifier connections for input - output

characteristics)

Fig :The instrumentation amplifier connections for common mode.

Experiment procedure:Adjustment of offset voltage.

1. Connect the circuit as shown in fig 2. Keep the dc voltage control to fully counter

clockwise direction.

2. Set the GAIN control to desired position (note that the resistance values are given

for calculation). Connect the DVM (range 20 V ), across the output sockets as shown.

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

3. Adjust the OFFSET control to bring the output voltage at zero volts.

Remember these steps are taken each times whenever a new gain setting is selected.

4. Now adjust DC volts pot slowly to obtain output voltage < 8.00 volts.

5. Connect D.V.M at the input as shown and measure the input dc voltage. Calculate

the voltage gain as Av = output voltage / input voltage. The amplifier gain may varied

between

5 - 101 approximately by RG. Measuring CMRR.

6. Adjust the desired (known) voltage gain, Av. Keep the dc voltage to zero.

7. Now short both inputs as shown in fig 3. Connect the DVM at output. Adjust the

offset voltage if required.

8. Now Increase the dc voltage and measure the output voltage Vo. Measure the input

voltage, Vin. Calculate the gain Acm = Vo/ Vin.

9. Compute the CMRR as Acm / Av ( known from before experiment) and express it

in dB.

AIM: To study inverting and non-inverting amplifiers using op-amps.

APPARATUS:

IC 741, CRO, connecting wires and function generator.

THEORY:

An op-amp exhibits the following characteristics

Positive Vcc

(1) High voltage gain.

(2) High input impedance

(3) Low output impedance

(4) Negligible output offset voltage

Normally an integrated circuit op-amp consists of four stages. The first is a

Inverting

Differential-Amplifier

with a double2ended output,7the second is also a Differentialinput

Amplifier but with a single ended output, the third is an emitter follower and finally

6

this is followed by a D.C. level shifter and output

driver stage.

741

Non inverting

input

Prepared by:- Mr.Satpal Singh

Output Vo

4

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Negative Vcc

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

INVERTING AMPLIFIER:

Referring to the figure below, the very high impedance of the OP-Amps makes it

draw zero current into the negative input terminal. Hence

Is = Vs/Rs = If

The output voltage is given by

Vo = - If Rf = -Is Rf

The voltage gain is

Vo/Vs = -Rf/ Rs

CIRCUIT DIAGRAM:

If

Rf

+15V

Rs

Vs

-Vo

741

Is

+

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

-15V

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

NON-INVERTING AMPLIFIER:

In the circuit shown in figure, we note that the voltage gain of the op-amp is

very large. This means that for any finite output, the input voltage between the V+

and V- terminals is almost zero. Hence V+ = VUsing the voltage divider rule, and also the fact that input current drawn at the

OP-AMP inputs is zero we have

V0 =(Rs/ Rs+Rf)*Vs

The voltage gain can be derived as

Vo/Vs = 1+ Rf/Rs

CIRCUIT DAIGRAM:

If

Rf

+15V

Rs

Vs

Vo

741

Is

-

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

-15V

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

PROCEDURE:

(A) Inverting- Amplifier: 1. Set up the circuit shown in figure, with Rf = 100 and Rs = 1K.

2. Apply an input signal of 1 Vpp and 1KHz to the inverting input. Observe the output

voltage Vo and input signal Vs on the dual channel oscilloscope. Measure the peak

voltages.

3. Repeat the measurements of Vo for Rs = 10 K, and 100K.

4. Calculate the voltage gain as a ratio and in decibels.

(B). Non-Inverting amplifier.

1.Set up the circuit of figure with Rs= 1K, Rf = 10K, and apply a 1 Vpp, 1KHz input

signal.

2. Observe the input and output waveforms on the dual channel oscilloscope note the

polarity and peak value of the output.

3. Repeat the observations and measurements for Rf = 100 K. Repeat observations in

the table.

Observation Table:

a) Non-Inverting Amplifier:

Sr.No.

Vs(in VPP)

Rf (in )

b) Inverting Amplifier:

Sr.No.

Vs(in VPP)

Prepared by:- Mr.Satpal Singh

Rf (in K)

Rs (in K)

Theoretical

Observed Vo

Vo (in (in VPP)

VPP)

=(1+Rf/

Rs)Vs

Rs (in K)

Theoretical Vo Observed

(in VP=(- (in VPP)

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Vo

Maharishi Markendeshwar University, Sadopur

LABORATORY MANUAL

EXPERIMENT NO. : ECE-LICAEX-13

REV. NO. :

DEPTT.

:

ELECTRONICS

&

COMMUNICATION DEPARTMENT

ISSUE NO. :

ISSUE DATE :

REV. DATE : -

PAGE:

LABORATORY :- LINEAR IC LAB ( ECE-317)

SEMESTER : V

Rf/Rs)V

s

PRECAUTIONS:

1. All the connections should be proper

2. There should be no voltage fluctuations.

3. Readings should be taken carefully.

RESULT: The inverting and non-inverting amplifier using op-amp is studied.

Prepared by:- Mr.Satpal Singh

Approved by:- Assoc. Prof. Parveen Bajaj(HOD)

Das könnte Ihnen auch gefallen

- Semiconductor Devices and Circuit Lab ManualDokument46 SeitenSemiconductor Devices and Circuit Lab ManualManu anand100% (1)

- EE LAB ManualDokument48 SeitenEE LAB ManualManu anandNoch keine Bewertungen

- 4 PinchrollerDokument1 Seite4 PinchrollerManu anandNoch keine Bewertungen

- Program 1 - Increment An 8-Bit NumberDokument1 SeiteProgram 1 - Increment An 8-Bit NumberManu anandNoch keine Bewertungen

- Emi Lab ManualDokument94 SeitenEmi Lab ManualManu anand50% (2)

- Load Test of Single Phase TransformerDokument6 SeitenLoad Test of Single Phase TransformerKevin DanyNoch keine Bewertungen

- ONLINE Application For GATE 2011: Page - 1Dokument5 SeitenONLINE Application For GATE 2011: Page - 1Manu anandNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- 1339fas-1271399 lt1339cswDokument21 Seiten1339fas-1271399 lt1339cswMuhammad ShamrezNoch keine Bewertungen

- Acer R3Dokument102 SeitenAcer R3shibilvNoch keine Bewertungen

- GFMDokument2 SeitenGFMadani123Noch keine Bewertungen

- Netstar ManualDokument140 SeitenNetstar Manualapi-3713719Noch keine Bewertungen

- Service Manual: 24 Bit Digital Sound System ProcessorDokument43 SeitenService Manual: 24 Bit Digital Sound System ProcessorzmlopezNoch keine Bewertungen

- Strategy - Apple Inc - Project PPT (Recovered)Dokument16 SeitenStrategy - Apple Inc - Project PPT (Recovered)Jayesh GoswamiNoch keine Bewertungen

- Current Electricity-1 JEE Main and AdvancedDokument8 SeitenCurrent Electricity-1 JEE Main and Advancedbibhas_samantaNoch keine Bewertungen

- MTS APL Source Code ListingDokument90 SeitenMTS APL Source Code ListingWilliam Francis GallantNoch keine Bewertungen

- Design 5 A.C. GeneratorDokument7 SeitenDesign 5 A.C. GeneratorNoykols GRncNoch keine Bewertungen

- SumatraPDF SettingsDokument38 SeitenSumatraPDF SettingsAlex TrinhNoch keine Bewertungen

- The Director in PreproductionDokument19 SeitenThe Director in Preproductionandrei neagNoch keine Bewertungen

- Grounding Rod Catalog Socome PDFDokument3 SeitenGrounding Rod Catalog Socome PDFedy yusufNoch keine Bewertungen

- ESYS50-lab4e-sg Oscilloscope Gerardo SanchezDokument6 SeitenESYS50-lab4e-sg Oscilloscope Gerardo SanchezGerardo SanchezNoch keine Bewertungen

- Audio System: 2004 LEXUS LS 430 (EWD577U)Dokument8 SeitenAudio System: 2004 LEXUS LS 430 (EWD577U)bob loblawNoch keine Bewertungen

- WEG Guia de Instalacao pws5610 Quick Guide English PDFDokument1 SeiteWEG Guia de Instalacao pws5610 Quick Guide English PDFÁgó AttilaNoch keine Bewertungen

- O W N e R S M A N UDokument6 SeitenO W N e R S M A N Uapi-25885158100% (2)

- Abb MCCDokument76 SeitenAbb MCCfridjatNoch keine Bewertungen

- Abs EdgeDokument39 SeitenAbs Edgecorporacion corprosinfro100% (3)

- Digital Communications - Viva Voce QuestionsDokument3 SeitenDigital Communications - Viva Voce QuestionsAllanki Sanyasi Rao100% (1)

- EN VEGACAL 62 4... 20 Ma HART Two WireDokument60 SeitenEN VEGACAL 62 4... 20 Ma HART Two WireVõ HòaNoch keine Bewertungen

- MOSCAPDokument6 SeitenMOSCAPEjder YildizNoch keine Bewertungen

- Flow Control ValvesDokument2 SeitenFlow Control ValvesAnik FaisalNoch keine Bewertungen

- B1641Dokument3 SeitenB1641ViswanathanNoch keine Bewertungen

- Short Answers 2nd Year PDFDokument20 SeitenShort Answers 2nd Year PDFMairan AnjumNoch keine Bewertungen

- كورس حمايه ممتعDokument151 Seitenكورس حمايه ممتعWhite HeartNoch keine Bewertungen

- Installers Manual Sliding Door AutomationDokument55 SeitenInstallers Manual Sliding Door AutomationSidney Moraes AlvesNoch keine Bewertungen

- Ee3015 PDFDokument1 SeiteEe3015 PDFRovick TarifeNoch keine Bewertungen

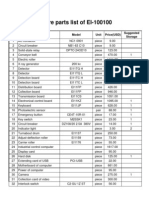

- Ei 100100Dokument2 SeitenEi 100100Tabassum BanuNoch keine Bewertungen

- Frequency Diverse MIMO Techniques For RadarDokument22 SeitenFrequency Diverse MIMO Techniques For RadarNamith DevadigaNoch keine Bewertungen

- TC-P50C2: 50 Inch Class 720p Plasma HDTVDokument95 SeitenTC-P50C2: 50 Inch Class 720p Plasma HDTVRonald CastellarNoch keine Bewertungen