Beruflich Dokumente

Kultur Dokumente

Gate E&C 2011

Hochgeladen von

saketramaOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Gate E&C 2011

Hochgeladen von

saketramaCopyright:

Verfügbare Formate

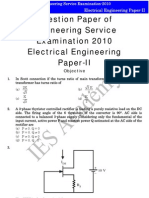

GATE 20 Years

Contents

Chapters Chapter-1 Topics Network Theory

GATE Syllabus for this Chapter Topic Related to Syllabus Previous 20-Years GATE Questions Previous 20-Years GATE Answers

Page No. 1

1 1 2 29

Chapter-2

Control System

GATE Syllabus for this Chapter Topic Related to Syllabus Previous 20-Years GATE Questions Previous 20-Years GATE Answers

51

51 51 52 76

Chapter-3

Electromagnetic Theory

GATE Syllabus for this Chapter Topic Related to Syllabus Previous 20-Years GATE Questions Previous 20-Years GATE Answers

105

105 105 106 121

Chapter-4

Electronic Device and Circuit

GATE Syllabus for this Chapter Topic Related to Syllabus Previous 20-Years GATE Questions Previous 20-Years GATE Answers

137

137 137 138 156

Chapter-5

Analog Circuit

GATE Syllabus for this Chapter Topic Related to Syllabus Previous 20-Years GATE Questions Previous 20-Years GATE Answers

171

171 171 172 203

Indias No. 1

GATE 20 Years Question and Answer

IES Academy

Contents

Chapters Chapter-6

Topics Signals & System

GATE Syllabus for this Chapter Topic Related to Syllabus Previous 20-Years GATE Questions Previous 20-Years GATE Answers

Page No. 225

225 225 226 244

Chapter-7

Communication System

GATE Syllabus for this Chapter Topic Related to Syllabus Previous 20-Years GATE Questions Previous 20-Years GATE Answers

257

257 257 258 276

Chapter-8

Digital Electronics

GATE Syllabus for this Chapter Topic Related to Syllabus Previous 20-Years GATE Questions Previous 20-Years GATE Answers

293

293 293 294 313

Chapter-9

Microprocessor Engineering

Topic Related to Syllabus Previous 20-Years GATE Questions Previous 20-Years GATE Answers

325

325 326 332

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-ii

25, 1st Floor, Jia Sarai, Near IIT Delhi, New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

1.

Network Theory

Gate Syllabus for this Chapter

Networks Theory:

Matrices Associated with Graphs; Incidence, Fundamental Cut-set and Fundamental Circuit Matrices. Solution Methods; Nodal and Mesh analysis. Network Theorems: Superposition, Thevenin and Nortons Maximum Power Transfer, Wye-Delta Transformation. Steady State Sinusoidal Analysis Using Phasors. Linear Constant Coefficient Differential Equations; Timedomain Analysis of Simple RLC Circuits, Solution of Network Equation Using Laplace Transform; Frequency-domain Analysis of RLC Circuits. 2-Port Network Parameters; Drivingpoint and Transfer Functions. State Equations for Networks.

Topics Related to Syllabus

1. 2. 3. 4. 5. Basic Network Analysis and Network Topology Initial Conditions; Time Varying Current and Differential Equation; Laplace Transform Two-port Network Network Theorem Sinusoidal Steady State Analysis; Resonance; Power in AC Circuits; Passive Filters

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-1

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy Previous Years GATE Question

1. Basic Network Analysis and Network Topology

Q1.1. The resonant frequency of the series circuit shown in figure is:

(a) (c) 1 4 2 1 2 10 Hz Hz (b) 1 Hz 4 1 (d) Hz 4 2

[GATE-1990]

Q1.2.

The response of an initially relaxed linear constant parameter network to a unit impulse applied at t = 0 is 4e2t. The response of this network to a unit step function will be: [GATE-1990] (a) 2 [1 e2t] u(t) (b) 4 [e1 e2t] u(t) (c) sin 2t (d) (1 4 e4t) u(t)

Q1.3.

Two resistors R1 and R2 (in ohms) at temperature T1 and T1 K respectively, are connected in series. Their equivalent noise temperature is: [GATE-1991] (a)

T1 R1 + T2 R2 R1

(b)

T1 R1 + T2 R2 R1 + R2

(c)

T1 R1 R1 + R2

(d)

T2 R2 R1 + R2

Q1.4.

For the compensated attenuator of figure, the impulse response under the condition [GATE-1992] R1C1 = R2C2 is:

(a)

1 R2 RC 1 e 1 1 u(t ) R1 + R2

(b)

R2 (t ) R1 + R2 R2

R1 + v1(t) C1 C2 + R2(t) V2(t)

R2 (c) u(t ) R1 + R2

1 RC (d) 1 + e 1 1 u(t ) R1 + R2

- C

Q1.5. Relative to a given fixed tree of a network: (a) Link currents form an independent set (b) Branch voltage form an independent set (c) Link currents form an independent set (d) Branch voltage form an independent set

[GATE-1992]

Q1.6.

The two electrical sub network N1 and N2 are connected through three resistors as shown in figure. The voltage across 5 ohm resistor and 1 ohm resistor are given to be 10V and 5V, respectively. Then voltage across 15 ohm resistors is: [GATE-1993] (a) 105 V (c) 15 V (b) +105 V (d) +15 V

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-2

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

Q1.7.

A network contains linear resistors and ideal voltage sources. If values of all the resistors are doubled, then the voltage across each resistor is: [GATE-1993] (a) Halved (b) Doubled (c) Increases by four times (d) Not changed

Q1.8. The RMS value of a rectangular wave of period T, having a value of +V for a duration, (T1 < T) and V for the duration, T T1 = T2, equals: [GATE-1995] T T T2 V (a) V (b) 1 V (c) (d) 1 V T T 2 2 Q1.9. The number of independent loops for a network with n nodes and b branches is: [GATE-1996] (a) n 1 (b) b n (c) b n + 1 (d) Independent of the number of nodes Q1.10. In the circuit of figure, the current iD through the ideal diode (zero cut in voltage and forward resistance) equals [GATE-1997] (a) (b) (c) (d) 0A 4A 1A None of these

Q1.11. In the circuit of figure, the equivalent impedance seen across terminals a, b is: [GATE-1997]

16 (a) 3 8 (b) 3

(c)

8 3 + 12 j

(d) None of these

Q1.12. The voltage V in figure is: (a) 10 V (b) 15 V (c) 5 V (d) None of these www.iesacademy.com E-mail: iesacademy@yahoo.com

[GATE-1997]

Page-3

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

[GATE-1997]

IES Academy

Q1.13. The voltage V in figure in always equal to: (a) 9 V (b) 5 V (c) 1 V (d) None of these Q1.14. The voltage V in figure is equal to: (a) (b) (c) (d) 3V 3 V 5V None of these

[GATE-1997]

Q1.15. The current i4 in the circuit of figure is equal to: (a) (b) (c) (d) 12 A 12 A 4A None of these

[GATE-1997]

Q1.16. The nodal method of circuit analysis is based on: (a) KVL and Ohms law (b) KCL and Ohms law (c) KCL and KVL (d) KCL, KVL and Ohms law

[GATE-1998]

Q1.17. A network has 7 nodes and 5 independent loops. The number of branches in the network is: [GATE-1998] (a) 13 (b) 12 (c) 11 (d) 10 Q1.18. Identify which of the following is NOT a three of the graph shown in figure: [GATE-1999] (a) (b) (c) (d) begh defg adhg aegh

Q1.19. For the circuit in figure, the voltage v0 is: (a) (b) (c) (d) 2V 1V 1 V None of these

[GATE-2000]

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-4

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

[GATE-2000] 16 V 4V 6 V 16 V

IES Academy

Q1.20. In the circuit of figure, the value of the voltage source E is: (a) (b) (c) (d)

Q1.21. The voltage e0 in figure is: (a) 48 V (b) 24 V (c) 36 V (d) 28 V

[GATE-2001]

Q1.22. The voltage e0 in figure is: (a) 2 V (b)

4 V 3

[GATE-2001]

(c) 4 V (d) 8 V Q1.23. The minimum number of equations required to analyze the circuit shown in figure is [GATE-2003] (a) (b) (c) (d) 3 4 6 7

Q1.24. Consider the network graph shown in figure which one of the following is NOT a tree of this graph? [GATE-2004]

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-5

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

Q1.25. If R1 = R2 = R4 = R and R3 =1. 1R in the bridge circuit shown in figure, then the reading in the ideal voltmeter connected between a and b is: [GATE-2005] (a) 0.238 V (b) 0.138 V (c) 0.238 V (d) 1 V Q1.26. Impedance Z as shown in figure is: (a) j29 (b) j9 (c) j19 (d) j39 Q1.27. In the following graph, the number of trees (P) and number of cut-sets (Q) are: [GATE-2008] (a) P = 2, Q = 2 (b) P = 2, Q = 6 (c) P = 4, Q = 6 (d) P = 4, Q = 10 Q1.28. A fully charged mobile phone with a 12V battery is good for a 10 minutes talk-time. Assume that, during the talk-time, the battery delivers a constant current of 2A and its voltage drops linearly from 12V to 10V as shown in the figure. How much energy does the battery deliver this talk-time? [GATE-2009] [GATE-2005]

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-6

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

v(t) 12 V 10 V 0 10 min t

IES Academy

(a) 220 J (b) 12 kJ (c) 13.2 kJ (d) 14.4 kJ

Q.1.29 In the circuit shown, the power supplied by the voltage source is: (a) (b) (c) (d) 0W 5W 10 W 100 W

[GATE-2010]

2. Initial Conditions, Time-varying Current & Differential Equation, Laplace Transform

Q2.1. The necessary and sufficient condition for a rational function of s. T(s) to be driving point impedance of an RC network is that all poles and zeros should be: (a) Simple and lie on the negative axis in the s-plane [GATE-1991] (b) Complex and lie in the left half of the s-plane (c) Complex and lie in the right half of the s-plane (d) Simple and lie on the positive real axis of the s-plane The voltage across an impedance in a network is V(s) = Z(s) I(s), where V(s), Z(s), I(s) are the Laplace transforms of the corresponding time function v(t), z(t) and i(t). The voltage v(t) is: [GATE-1991] (a) v(t) = z(t) v(t) (c) v(t ) = i( ).z(t + )d

0 t

Q2.2.

(b) v(t ) = i( ) z(t )d

(d) v(t) = z(t) + v(t)

Q2.3.

Condition for valid input impedance is that maximum powers of the number of denominator polynomial may bigger at most by: [GATE-1993] (a) 2 (b) 1 (c) 3 (d) 0

Q2.4. In the circuit shown in figure, assuming initial voltage and capacitors and currents through the inductors to be zero at the time of switching (t = 0), then at any time t > 0: [GATE-1996]

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-7

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

(a) Current increases monotonically with time (b) Current decreases monotonically with time (c) Current remains constant at V/R (d) Current first increases then decreases

Q2.5.

The voltages Vc1, Vc2, and Vc3 across the capacitors in the circuit in figure, under steady state, are respectively [GATE-1996] (a) 80 V, 32 V, 48 V (b) 80 V, 48 V, 32 V (c) 20 V, 8 V, 12 V (d) 20 V, 12 V, 8 V

100V

Vc2 1F Vc1 40K 3F

Vc3

Q2.6.

In the circuit of figure, assume that the diodes are ideal and the meter is an average indicating ammeter. The ammeter will read: [GATE-1996] (a) 0.4 2 A (c) (b) 0.4 A (d)

D1 + D2 10k

0.8

0.4

10k

Q2.7.

In figure, A1, A2 and A3 are ideal ammeters. If A2 and A3 real 3A and 4A respectively, [GATE-1996] then A1 should read: (a) 1 A

A2

L

A1

A3

(b) 5 A (c) 7 A (d) None of these Q2.8. In the circuit of figure, the voltage V(t) is: (a) eat ebt (c) aeat bebt (b) eat + ebt (d) aeat + bebt

R

[GATE-2000]

Q2.9.

In figure the switch was closed for a long time before opening at t = 0. The voltage Vx [GATE-2002] at t = 0+ is E-mail: iesacademy@yahoo.com Page-8

www.iesacademy.com

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

(a) 25 V (b) 50 V (c) 50 V (d) 0 V

Q2.10. I1(s) and I2(s) are the Laplace transform of i1(t) and i2(t) respectively. The equations for the loop currents I1(s) and I2(s) for the circuit shown in figure, after the switch is brought from position 1 to position 2 at t = 0, are: [GATE-2003]

(a)

(b)

(c)

(d)

1 R + Ls + Cs Ls 1 R + Ls + Cs Ls 1 R + Ls + Cs Ls 1 R + Ls + Cs Ls

Ls I 1 1 I R+ 2 Cs Ls I 1 1 I R+ 2 Cs Ls

V ( s) = s ( s) 0 V ( s) s = ( s) 0

I1 ( s) V = s 1 I 2 ( s) 0 RLs + Cs Ls I1 ( s) V = s ( ) I s 1 0 R + Ls + 2 Cs

Q2.11.

At t = 0+, the current i1 is: (a) (c)

[GATE-2003]

V 2R

(b)

V R

V 4R

(d) zero

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-9

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

i1(0)

IES Academy

Q2.12. The circuit shown in figure has initial current = 1A through the inductor and aninitial voltage vc(0) = 1V across the capacitor. For input v(t) = u(t), the Laplace [GATE-2004] transform of the current i(t ) t 0 is:

s s + s +1 s+2 (b) 2 s + s +1 s2 (c) 2 s + s +1 s+2 (d) 2 s + s +1

(a)

2

Q2.13. The equivalent inductance measured between the terminals 1 and 2 for the circuit shown in figure is: [GATE-2004]

(a) L1 + L2 + M (b) L1 + L2 M (c) L1 + L2 + 2M (d) L1 + L1 2M

Q2.14. A square pulse of 3 volts amplitude is applied to CR circuit shown in figure. The capacitor is initially uncharged. The output voltage vo at time t = 2 sec is: [GATE-2005]

(a) 3 V (b) 3 V (c) 4 V (d) 4 V

Q2.15. In the circuit shown below, the switch was concentred to position 1 at t < 0 and at t= 0, it is changed to position 2. Assume that the diode has zero voltage drop and a storage time ts. For t < 1 ts, VR is given by (all in volts): [GATE-2006]

(a) VR = 5 (b) VR = +5 (c) 0 VR = 5 (d) 5 < VR < 0

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-10

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

(a) 8 e0.004t Volts (b) 8 (1 et/0.004) Volts (c) 8 u(t) Volts (d) 8 Volts

Q2.16. In the figure shown below, assume that all the capacitors are initially uncharged. If Vi(t) = 10u(t) volts V0(t) is given by: [GATE-2006]

Q2.17. A 2 mH inductor with some initial current can be represented as shown below, where s is the Laplace transform variable, the value of initial current is: [GATE-2006]

(a) 0.5 A (b) 2.0 A (c) 1.0 A (d) 0.0 A

I(s) 0.002s + 1 mV

Q2.18. In the following circuit, the switch S is closed at t = 0. The rate of change of current di (0+ ) is given by GATE-2008] dt

(a) 0 (b)

RS I S L ( R + RS ) I S L

(c)

(d)

Q2.19. The driving-point impedance of the following 0.2s Z (s) = 2 . The component values are: s + 0.1s + 2 network is given by

[GATE-2008]

R = 0.5 , C = 0.1F (b) L = 0.1H, R = 0.5 , C = 5F

(c) L = 5H,

R = 2 , C = 0.1F

(a) L = 5H,

(d) L = 0.1H, R = 2 ,

C = 5F

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-11

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

20V I I1 + 60V -

IES Academy

+ X

Q2.20. In the interconnection of ideal sources shown in the figure, it is known that the 60 V source is absorbing power. [GATE-2009]

12A

Which of the following can be the value of the current source I? (a) 10 A (b) 13 A (c) 15 A Q2.21. If the transfer function of the following network is load resistance RL is:

(d) 18 A

Vo ( s ) 1 = the value of the Vi ( s) 2 + sCR

[GATE-2009]

(a) R/4 (b) R/2 (c) R (d) 2 R

+

Vi

+

C RL Vo

Q2.22. The switch in the circuit shown was on position a for a long time, and is moved to position b at time t = 0. The current i(t) for t > 0 is given by: [GATE-2009] 125t u(t ) mA (a) 0.2 e a b

(b) 20 e 1250t u(t ) mA (c) 0.2 e 1250t u(t ) mA (d) 20 e

1000t

100V

u(t ) mA

Q2.23.

V di L + Ri = Vo 1 + Be Rt / L sin t u(t). For an initial current of i(0) = o , the R dt

steady state value of the current is given by

The

time-domain

behavior

of

an

RL

circuit

is

represented

by

V (a) i(t ) o R

2Vo (b) i(t ) R

V (c) i(t ) o (1 + B ) R

2Vo (d) i(t ) (1 + B ) R

[GATE-2009]

Q2.24. In the circuit shown, the switch S is open for a long time and is closed at t = 0. The [GATE-2010] current i(t) for t 0+ is:

(a) (b) (c) (d)

i(t) = 0.5 0.125e1000t A i(t) = 1.5 0.125e1000t A i(t) = 0.5 0.5e1000t A i(t) = 0.375e1000t A

E-mail: iesacademy@yahoo.com Page-12

www.iesacademy.com

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy 3. Two-port Network

Q3.1.

The open circuit impedance matrix of the two-port network shown in figure is: [GATE-1990] 2 1 (a) 8 3

2 8 (b) 3 1 0 1 (c) 1 0

2 1 (d) 1 3

Q3.2.

Two two-port networks are connected in cascade. The combination is to represented as a single two-port networks. The parameters of the network are obtained by multiplying the individual: [GATE-1991] (a) z-parameter matrix (b) h-parameter matrix (c) y-parameter matrix (d) ABCD parameter matrix [GATE-1992] (d) AD BC = 0

Q3.3. For a two-port network to be reciprocal (a) Z11 = Z22 (b) y21 = y12 (c) h21 = h21 Q3.4.

The condition that a z-port network is reciprocal, can be expressed in terms of its ABCD parameters as: [GATE-1994] (a) AD BC = 1 (b) AD BC = 0 (c) AD BC > 1 (d) AD BC < 1 The short-circuit admittance matrix of a two-port network is: [GATE-1998]

Q3.5.

0 1 / 2 1 / 2 0

The two-port network is: (a) Non-reciprocal and passive (c) Reciprocal and passive Q3.6.

(b) Non-reciprocal and active (d) Reciprocal and active

A two-port network is shown in figure. The parameter h21 for this network can begiven by: [GATE-1999]

(a) 1/2 (b) +1/2 (c) 3/2 (d) +3/2

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-13

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

[GATE-2001]

Z21 = Z21 = Z21 = Z21 =

IES Academy

Q3.7. The Z parameters Z11 and Z21 for the 2-port network in figure are:

(a) Z11 = (b) Z11 = + (c) Z11 = + (d) Z11 =

6 ; 11 6 ; 11 6 ; 11

16 11 4 11

16 11

4 11

4 ; 11

Q3.8.

The admittance parameter Y12 in the two-port network in figure is:

[GATE-2001]

(a) 0.2 mho (b) 0.1 mho (c) 0.05 mho (d) 0.05 mho

Q3.9.

The impedance parameters Z11 and Z12 of the two-port network in figure are: [GATE-2003]

(a) Z11 = 2.75 and Z12 = 0.25 (b) Z11 = 3 and Z12 = 0.5 (c) Z11 = 3 and Z12 = 0.25 (d) Z11 = 2.25 and Z12 = 0.5

= 2 . The values of the open circuit Q3.10. For the lattice shown in figure, Za = j2 and Zb

z11 impedance parameters Z = z21 1 j 1 + j (a) 1 + j 1 + j 1 j 1 + j (b) 1 + j 1 j 1 + j 1 + j (c) 1 j 1 j 1 + j 1 + j (d) 1 + j 1 + j

z12 are: z22

[GATE-2004]

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-14

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

[GATE-2005]

IES Academy

Q3.11. The h parameters of the circuit in figure are: 0.1 0.1 10 1 (a) (b) 0.1 0.3 1 0.05

30 20 (c) 20 20

10 +1 (d) 1 0.05

n 0 Q3.12. The ABCD parameters of an ideal n : 1 transformer shown in figure are . The 0 X value of X will be: [GATE-2005] (a) n (b) 1/n (c) n2 (d) 1/n2

Q3.13. A two-port network is represented by ABCD parameters given by V1 A B V2 I 1 C D I 2 If two-port is terminated by RL, the input impedance seen at one-port is given by: [GATE-2006] A + BRL ARL + C DRL + A B + ARL (a) (b) (c) (d) BRL + D BRL + C D + CRL C + DRL

Statements for Linked Answers and Questions 3.14 and 3.15:

A two-port network shown below is excited by external DC sources. The voltages and the currents are measured with voltmeters V1, V2 and ammeters A1, A2 (all assumed to be ideal), as indicated. Under following switch condition, the readings obtained are:

(i ) S1 Open, S2 Closed A1 = 0 A, V1 = 4.5 V, V2 = 1.5 V, A2 = 1A (ii ) S1 Closed, S2 Open A1 = 4 A, V1 = 6 V, V2 = 6 V, I 2 = 0 A

Q3.14. The z-parameter matrix for this network is: 1.5 1.5 1.5 (a) (b) 4.5 1.5 1.5 [GATE-2008]

4.5 4.5 1.5 4.5

[GATE-2008]

4.5 1.5 4.5 (d) (c) 1.5 1.5 1.5 Q3.15. The h-parameter matrix for this network is:

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-15

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

3 (b) 3

IES Academy

3 3 (a) 1 0.67

3 (c) 1

1 0.67

3 0.67

1 3 (d) 3 0.67

Q3.16. For the two-port network shown below, the short-circuit admittance parameter matrix is: [GATE-2010] 2 4 (a) S 4 2

(b) (c) (d)

1 0.5 0.5 1 S

1 0.5

0.5 S 1

4 2

2 S 4

4. Network Theorem

Q4.1. A generator of internal impedance ZG deliver maximum power to a load impedance, Zp only if Zp [GATE-1994] (a) Z1 < ZG (b) Z1 > ZG (c) Z p = ZG (d) Z1 = 2ZG Q4.2 A ramp voltage, v(t) = 100t volts, is applied to an RC differencing circuit with R = 5 k and C = 4 F. The maximum output voltage is: [GATE-1994] (a) 0.2 volts (b) 2.0 volts (c) 10.0 volts (d) 50.0 volts

Q4.3. The value of the resistance, R, connected across the terminals A and B, (ref. figure), which will absorb the maximum power is: [GATE-1995]

(a) 4.00 k (b) 4.11 k (c) 8.00 k (d) 9.00 k

Q4.4. Two 2H inductance coils are connected in series and are also magnetically coupled to each other the coefficient of coupling being 0.1. The total inductance of his combination can be: [GATE-1995] (a) 0.4 H (b) 3.2 H (c) 4.0 H (d) 3.8 H Q4.5. Superposition theorem is NOT applicable to networks containing: [GATE-1998] (a) Nonlinear elements (b) Dependent voltage sources (c) Dependent current sources (d) Transformers

Page-16

www.iesacademy.com

E-mail: iesacademy@yahoo.com

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

(a) 1.5, 3 and 9 (b) 3, 9 and 1.5 (c) 9, 3 and 1.5 (d) 3, 1.5 and 9

Q4.6. A delta-connected network with its Wyes-equivalent is shown in figure. The resistances R1, R2, and R3 (in ohms) are respectively. [GATE-1999]

Q4.7.

The value of R (in ohms) required for maximum power transfer in the network shown in figure is: [GATE-1999]

(a) 2 (b) 4 (c) 8 (d) 16

Q4.8. The Theremin equivalent voltage VTH appearing between the terminals A and B of the network shown in figure is given by [GATE-1999]

(a) j16 (3 j4) (b) j16(3 + j4) (c) 16 (3 + j4) (d) 16(3 j4)

Q4.9. Use the data of Fig (a). The current i in the circuit of Fig (b) is: [GATE-2000]

(a) 2 A (b) 2 A (c) 4 A (d) 4 A

Q4.10. If each branch of a delta circuit has impedance equivalent Wye-circuit has impedance

3z , then each branch of the

[GATE-2001]

(a) 3 3 Z (c)

Z

3

(b) 3 Z (d)

Z 3

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-17

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

(a) 16 (b)

40 3

Q4.11. In the network of figure, the maximum power is delivered to RL if its value is: [GATE-2002]

(c) 60 (d) 20

Q4.12. Twelve 1 resistance are used as edges to form a cube. The resistance between two diagonally opposite corners of the cube is: [GATE-2003] 5 6 3 (a) (b) 1 (c) (d) 6 5 2 Q4.13. A source of angular frequency 1 rad/sec has a source impedance consisting of 1 resistance in series with 1H inductance. The load that will obtain the maximum power transfer is: [GATE-2003] (a) 1 resistance (b) 1 resistance in parallel with 1H inductance (c) 1 resistance in series with 1F capacitor (d) 1 resistance in parallel with 1F capacitor Q4.14. For the circuit shown in figure. Thevenins voltage and Thevenins equivalent resistance at terminals a, b is: [GATE-2005]

(a) 5 V and 2 (b) 7.5 V and 2.5 (c) 4 V and 2 (d) 3 V and 2.5

Q4.15. The maximum power that can be transferred to the load resistor RL from the voltage source in figure is [GATE-2005]

(a) 1 W (b) 10 W (c) 0.25 W (d) 0.5 W

Q4.16. An independent voltage source in series with an impedance ZS = RS + jXS delivers a maximum average power to a load impedance ZL when [GATE-2007] (d) ZL = RS jXS (a) ZL = RS + jXS (b) ZL = RS (c) ZL = jXS

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-18

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

(a) 4/3 V, 2 (b) 4V, 2/3 (c) 4/3 V, 2/3 (d) 4 V, 2

Q4.17. For the circuit shown in the figure, the Thevenin voltage and resistance looking into X Y are [GATE-2007]

Q4.18. The Thevenin equivalent impedance Zth between the nodes P and Q in the following circuit is [GATE-2008] 1 (a) 1 (b) 1 + S + S 1 S2 + S + 1 (d) 2 (c) 2 + S + S S + 2s + 1

Q4.19. In the circuit shown, what value of RL maximizes the power delivered to RL? [GATE-2009]

(a) 2.4 (b)

8 3

Vi

VX

VX +

(c) 4 (d) 6

100V

RL

5. Sinusoidal Steady State Analysis, Resonance, Power in AC Circuits, Passive Filters

Q5.1. The transfer function of a simple RC network function as a controller is s + z1 GC ( s ) = . The condition for the RC network to Act as a phase lead controller is: s + p1

(a) p1 < z1 (c) p1 = z1

Q5.2.

(b) p1 = 0 (d) p1 > z1

[GATE-1990]

In a series RLC high Q circuit, the current peaks at a frequency: (a) Equal to the resonant frequency (b) Greater than the resonant frequency (c) Less than the resonant frequency (d) None of these

[GATE-1991]

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-19

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

Q5.3.

Of the four network, N1, N2, N3 and N4 of figure, then network having identical driving-point function are: [GATE-1992]

(a) N1 and N1 (b) N2 and N4 (c) N1 and N3 (d) N1 and N4

Q5.4. For the series RL circuit of Fig. (a), the partical phasor diagram at a certain frequency is shown in Fig. (b). The operating frequency of the circuit is: [GATE-1992]

(a) Equal to the resonance frequency (b) less than the resonance frequency (c) greater than resonance frequency (d) Not zero

Q5.5. In figure and A1, A2 and A3 are ideal ammeters. If A1 reads 5A, A2 reads 12A, then A3 should read: [GATE-1993]

(a) 7 A (b) 12 A (c) 13 A (d) 17 A

Q5.6. The response of an LCR circuit to a step input is over damped. If transfer function has: [GATE-1993] (a) Poles in the negative real axis (b) Poles on imaginary axis (c) Multiple poles on the negative real axis (d) Multiple poles on the positive real axis A series LCR circuit, consisting of

Q5.7.

R = 10 , X L = 20 and XC = 20 ,

is

connected across an AC supply of 200V rms. The rms voltage across the capacitor is: [GATE-1994] (a) 200 < 90 V (b) 200 < +90 V (d) 400 < 90 V (c) 400 < +90 V

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-20

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

Q5.8.

A series RLC circuit has a Q of 100 and an impedance of (100 + j0) at its resonant [GATE-1995] angular frequency of 107 rad/sec. The values of R and L are: (d) 100 , 100 H (a) 100 , 103 H (b) 10 , 102 H (c) 1000 , 10 H The current, i(t), through a 10 resistor in series is equal to 3 + 4sin(100t + 45) + 4sin(300t + 60) amperes. The RMS value of the current and the power dissipated in the circuit are: [GATE-1995]

Q5.9.

(a) 41 A, 410 W, respectively (c) 5 A, 250 W, respectively

(b) 35 A, 410 W, respectively (d) 11 A, 1210 W, respectively

Q5.10. Consider a DC voltage source connected to a series RC circuit. When the steadystate reaches, the ratio of the energy stored in the capacitor to the total energy supplied by the voltage source is equal to: [GATE-1995] (a) 0.362 (b) 0.500 (c) 0.632 (d) 1.000 Q5.11. ADC voltage source is connected across a series RLC circuit. Under steady conditions, the applied DC voltage drops entirely across the: [GATE-1995] (a) R only (d) L only (c) C only (d) R and L Combination Q5.12. A communication channel has first order low pass transfer function. The channel is used to transmit pulses at a symbol rate greater than the half-power frequency of the low pass function. Which of the network shown in figure can be used to equalize the received pulses? [GATE-1997]

Q5.13. In the circuit of figure the energy absorbed by the 4 resistor in the time interval (0,

) is:

[GATE-1997]

(a) 36 Joules (b) 16 Joules (c) 256 Joules (d) None of these

www.iesacademy.com E-mail: iesacademy@yahoo.com Page-21

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

(a) I R < 1mA (b) I R + I L > 1mA (c)

I R + I C < 1mA

Q5.14. The parallel R-L-C circuit shown in figure is in resonance, In this circuit: [GATE-1998]

(d) I R + I C > 5mA

Q5.15. When the angular frequency in figure is varied from 0 to , the locus of the current phasor I2 is given by: [GATE-2001]

Q5.16. If the 3-phase balanced source in figure delivers 1500 W at a leading power factor of 0.844, then the value of ZL (in ohm) is approximately: [GATE-2002]

(a) 9032.44 (b) 8032.44 (c) 80 32.44 (d) 90 32.44

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-22

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

[GATE-2002]

IES Academy

Q5.17. The dependent current source shown in figure is:

(a) Delivers 80 W (b) Absorbs 80 W (c) Delivers 40 W (d) Absorbs 40 W

Q5.18. An input voltage v(t ) = 10 2 cos (t + 10 ) + 10 5 cos (2t + 10 ) V is applied to a series combination of resistance R = 1 and an inductance L = 1H. The resulting steady state current i(t) in ampere is: [GATE-2003] (a) 10 cos (t + 55) + 10 cos (2t + 100 + tan1 2)

3 cos (2t + 55) 2 (c) 10 cos (t 35) + 10 cos (2t + 10 tan1 2)

(b) 10 cos (t + 55) + 10

(d) 10 cos (t 35) + 10

3 cos (2t 35) 2

Q5.19. The current flowing through the resistance R in the circuit in figure has the form P cos 4t, where P is: [GATE-2003]

(a) (0.18 + j0.72) (b) (0.46 + j1.90) (c) (0.18 + j1.90) (d) (0.192 + j0.144)

Q5.20. The differential equation for the current i(t) in the circuit of figure is: [GATE-2003] d 2i di (a) 2 2 + 2 + i(t ) = sin t dt dt d 2i di + 2 + 2i(t ) = cos t (b) dt dt 2 2 di di (c) 2 2 + 2 + i(t ) = cos t dt dt d 2i di + 2 + 2i(t ) = sin t (d) 2 dt dt Q5.21. A series RLC circuit has a resonance frequency of 1 kHz and a quality factor Q = 100. If each of R, L and C is doubled from its original value, the new Q of the circuit is: [GATE-2003] (a) 25 (b) 50 (c) 100 (d) 200

Page-23

www.iesacademy.com

E-mail: iesacademy@yahoo.com

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

Q5.22. Consider the following statements S1 and S2 (S1: At the resonant frequency the impedance of a series RLC circuit is zero; S2: In a parallel GLC circuit, increasing the conductance G results in increase in its Q factor). Which one of the following is correct? [GATE-2004] (a) S1 is FALSE and S2 is TRUE (b) Both S1 and S2 are TRUE (d) Both S1 and S2 are FALSE (c) S1 is TRUE and S2 is FALSE Q5.23. For the circuit shown in figure, the initial conditions are zero. Its transfer function is: [GATE-2004]

(a) (b) (c) (d)

1 s + 106 s + 106

2

106 s + 103 s + 106

2

103 s + 103 s + 106

2

106 s + 106 s + 106

2

Q5.24. The

transfer

function

H (s) =

Vo ( s) Vi (s)

of

an

RLC

circuit

is

given

by

H ( s) =

(a) 25

106 . The Quality factor (Q - factor) of this circuit is: s 2 + 20s + 106 (b) 50 (c) 100 (d) 5000

[GATE-2004]

Q5.25. For the RL circuit shown in figure the input voltage vi(t) = u(t). The current i(t) is: [GATE-2004]

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-24

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

(a) sin (103t 45) (b) sin (103t + 45) (c) sin (103t 53) (d) sin (103t + 53)

Q5.27. The circuit shown in figure with R = 2t. The resulting current i(t) is:

Q5.26. For the circuit shown in figure the time constant RC = 1 ms. The input voltage is vi(t) [GATE-2004] = sin 103 t. The output voltage vo(t) is equal to:

1 1 , L = H, C = 3 F has input voltage v(t) = sin 3 4 [GATE-2004]

(a) 5 sin (2t + 53.1) (b) 5 sin (2t 53.1) (c) 25 sin (2t + 53.1) (d) 25 sin (2t 53.1)

Q5.28. For the circuit in figure, the instantaneous current i1(t) is: 10 3 (a) 90 Amps 2 10 3 90 Amps (b) 2 (c) 560 Amps [GATE-2005]

(d) 5 60 Amps

Q5.29. Which one of the following polar diagrams corresponds to a lag network? [GATE-2005]

Q5.30. In a series RLC circuit R = 2 k , L = 1 H and C = 1/400 F. The resonate frequency is: [GATE-2005] 1 4 4 4 4 (a) 2 10 Hz (b) 10 Hz (c) 10 Hz (d) 2 10 Hz

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-25

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

Q5.31. The condition on R, L and C such that the step response y(t) in figure has no oscillations, is: [GATE-2005] 1 L L (b) R (a) R 2 C C

(c) R 2

L C

(d) R =

L C

Q5.32. A negative resistance Rneg is connected to a passive network N having point [GATE-2006] impedance Z1(s) as shown below. For Z2(s) to be positive real:

(a) (b) (c)

Rneg Re Z1 ( j ),

Rneg Z1 ( j ) , Rneg IMZ1 ( j ) ,

Z2(s)

R neg

N

Z1(s)

(d) Rneg Z1 ( j ) ,

Q5.33. The first and the last critical frequencies (singularities) of a driving-point impedance function of a passive network having two kinds of elements, are a pole and a zero respectively. The above property will be satisfied by: [GATE-2006] (a) RL network only (b) RC network only (c) LC network only (d) RC as well as RL networks Q5.34. In the AC network shown in the figure, the phasor voltage VAB (in volts) is

[GATE-2007]

(a) 0 (b) (c) (d)

530 12.530 1730

Q5.35. In the circuit shown, Vc is 0 volts at t = 0 sec. For t > 0, the capacitor current ic(t) where t is in seconds, is given by: [GATE-2007]

(a) 0.50 exp (25 t) mA (b) 0.25 exp (25 t) mA (c) 0.50 exp (12.5 t) mA (d) 0.25 exp (6.25 t) mA

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-26

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

Q5.36. Two series resonant filters are as shown in the figure. Let the 3-dB bandwidth of B [GATE-2007] Filter 1 be B1 and that of Filter 2 be B2. The value of 1 is B2

(a) 4 (b) 1 1 (c) 2 1 (d) 4

Q5.37. The circuit shown in the figure is used to charge the capacitor C alternately from two current sources as indicated. The switches S1 and S2 are mechanically coupled and connected as follows: [GATE-2008] For 2nT t < (2n + 1) T (n = 0, 1, 2, ...) S1 to P1 and S2 to P 2 For (2n + 1) T t < (2n + 2) T (n = 0, 1, 2, ...) S1 to Q1 and S2 to Q2

Assume that the capacitor has zero initial charge. Given that u(t) is a unit step function, the voltage VC(t) across the capacitor is given by:

(a)

n =0

( 1) tu(t nT )

n n =1

(b) u(t ) + 2 ( 1)n u(t nT )

n =0

(c) tu(t ) + 2 ( 1)n (t nT )u(t nT )

(d)

n =0

0.5 e

( t 2 nT )

+ 0.5e ( t 2nT T )

Common Data for Questions 38 and 39:

The following series RLC circuit with zero initial conditions is excited by a unit impulse function (t).

Q5.38. For t > 0, the output voltage

[GATE-2008]

te

1 + t 2

(a)

t 2 1 2 e e 3

3 t 2

(b)

2 3

(c)

2 3

te

1 t 2

(d)

2 3

1 t 2

3 t sin 2

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-27

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

[GATE-2008]

3t 1 3 t sin cos 2 3 2

1 t 2

IES Academy

Q5.39. For t > 0, the voltage across the resistor is

(a)

1 t 1 23 t 2 e e 3

(b) e

1 t 2

(c)

2 3

1 t 2

3t sin 2

(c)

2 3

3t cos 2

Q5.40. An AC source of RMS voltage 20V with internal impedance ZS = (1 + 2 j) feeds a load of impedance Z L = (7 + 4 j) in the figure below. The reactive power consumed by the load is [GATE-2009]

(a) 8 VAR (b) 16 VAR (c) 28 VAR (d) 32 VAR

Q5.41. For parallel RLC circuit, which one of the following statements is NOT correct? [GATE-2010] (a) The bandwidth of the circuit deceases if R is increased (b) The bandwidth of the circuit remains same if L is increased (c) At resonance, input impedance is a real quantity (d) At resonance, the magnitude of input impedance attains its minimum value Q5.42. The current I in the circuit shown is: [GATE-2010]

+

(a) (b) (c) (d)

j1 A

J1 A

0A 20 A

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-28

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

Answers with Explanation

1.1. Ans.(b) For resonance

Leq = L1 + L2 2 M = 2 + 2 2 1 = 2 H 1 1 1 o 2 = = ; o = 2 22 4 1 f0 = Hz 4

1.2. Ans.(a) Response of linear network = 4 e2t When unit impulse applied h(t ) = 4e 2t If input is unit step then output is y(t)

y ( s ) = H ( s )U ( s ) 4 1 4 1 1 = + S +2 s 2 s s 2 2 t y(t ) = 2 e u t 1 ( ) y( s) =

oC

= o Leq

1.3. Ans.(b)

Teq = T1 R1 + T2 R2 R1 + R2

(Equivalent noise temp) 1.4. Ans.(b) Input is impulse signal = (t ) According standard result V2 (t ) =

R2 V (t ) (for compensated network) R1 + R2 i R2 V2 (t ) = (t ) R1 + R2

1.5. Ans.(a, d) Relative to a given fixed tree of a network Link currents form an independent set Branch voltage form an independent set

1.6. Ans.(a)

www.iesacademy.com E-mail: iesacademy@yahoo.com Page-29

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

Using KCL for cut-set, that means current entering and leaving a cut-set is equal to zero 10 5 I1 + I 2 + I 3 = 0; + I2 + = 0 5 1 I 2 = 7 A Voltage across 15 resistances = 7 15 = 105 V

1.7. Ans.(d) 1.8. Ans.(a)

R.M.S. value of rectangular pulse = 1 T 2 x (t ) dt T 0 T1 +T2 1 T1 2 ( V )2 dt = V dt + T 0 1 T = But, T1 + T2 = T = V

V2 V2 V2 T1 + T1 + T2 T1 = T1 + T2 T T T

1.9. Ans. 1.10. Ans.

(c) (c)

By analysis it is found that diode in feedback and current flow through diode only due to voltage source. Applying KVL in loop (i)

10 V 4( I1 + I 2 ) 4 I 2 = 0 10 V 4 I1 + 8 I 2 = 0 (i )

I I2

I1

2A

I1+2

10V

Applying KVL in loop (ii)

I1 + 2 4 I 2 = 0; 10 4 I1 8( I1 + 2) ; 4 I2 = I1 + 2 4 I1 = (ii ) 6 = 1A 6

10 6 I1 4 = 0

1.11. Ans.(b) It is balanced Wheatstone Bridge.

So, impendence across ab =

84 8 = 12 3

1.12. Ans.(a) V = 10 V (it is parallel to 10 V source) 1.13. Ans.(d) Apply Thenvine theorem across AB

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-30

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

So calculation of VAB is not possible with network information, so (d) option is correct. 1.14. Ans.(a)

A

Note: 5V and 4V source in L.H.S. can be combining and net voltage is l V.

4V

1V 3V

Apply KVL in ABA loop 4V1=0 V=3V

+ V

1.15. Ans.(b)

KCL at node P i1 + i0 + i4 = 0 i4 = i1 + i0 i4 = 5 + 7 i4 = 12 A 1.16. Ans.(b) Nodal method of circuit analysis is based on KCL and ohms law 1.17. Ans.(c) In network number of independent loop = b n + 1 1.18. Ans.(c)

Adhg not a tree because it made a closed loop and in a tree close loop is not possible.

a

1 3

1.19. Ans.(d)

First we find bising of diode for that find voltage across AB Suppose VAB = V By super position theorem VAB = 1 V That means diode in feedback

+

4V

V0

+

B

2V

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-31

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

A

IES Academy

So, Apply KCL at node A VA 4 VA VA + 2 + + =0 2 2 2 2 2 VA = , VA = VO , VO = 3 3

1.20. Ans.(a)

+

4V

2V

Applying KVL 10 5 + E 1 = 0

E = 16

V2

+ 2V

+ 1V

+ -

+ 4V

+ -

5V

v1

10V

1.21. Ans.(d) By super-position theorem Case 1: Only current source is active (voltage source will be short circuit) then find current through 12 resistances. By current source conversion

I=

I1

80V

80 = 5 A; 16

I1 =

6 30 A 5 = 18 18

I1 I

Case 2: By current source suppression only voltage source will be in active mode 16 16 I= ; I1 = 12 24

Total current through 12 resistance =

So, e0 =

30 16 120 + 48 168 + = = 18 24 72 72

168 12 = 28 V 72

1.22. Ans.(c) 1.23. Ans.(b)

Current through 4 = 1 A So, e0 = 4 1 = 4 V Minimum number of equations required for analysis of network Number of equation = b n + 1 Where, n = number of nodes; b = number of branches in the question n = 4; b = 7 So number of equations required = 7 4 + 1 = 4

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-32

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

Tree of network graph will not have any close loop.

IES Academy

1.24. Ans.(b) 1.25. Ans.(c)

R2 R 10 = 10 = 5 V R1 + R2 R+R R3 1.1R 1.1 110 10 = 10 = 10 = Vb = 1.1R + R 2.1 21 R3 + R4 110 = 0.238 V Va Vb = 5 21 1.26. Ans.(b) Total impedance Z = 5j + 2j + 2j + 10j 10j = 9j Va =

1.27. Ans.(c) 1.28. Ans.(c)

Energy delivers during talk time

E=

t = 600 Sec

t =0

V I dt; So, E =

I = 2 A;

V =

t + 12 300

1.29. Ans.(a) 2.1. Ans.(a) 2.2. Ans.(b) 2.3. Ans.(b) 2.4. Ans.(c)

t 2 + 12 dt 300 E = 13.2 kJ By superposition (I is current delivered by 10 V source), I10 = 2.5 A; I1 = 0.5 A; I2 = 2 A;

600

I = OA;

P = OW

Other than (more than one), impedance physically not possible Inductor will be like as short circuit because voltage source is D.C. V So, current through R = , current remains constant at V/R R 2.5. Ans.(b)

100V

Vc2

--

+

Vc1

1F

40K

3F

Vc3

After steady state

I C2=

At steady state I =

100 = 2mA 50k

+Vc 2

+ -

Vc 1

+

40K

Vc3

c3=3f

So, Vc1 = 100 10 2mA 103 = 80 V, but Vc1 = Vc2 + Vc3 (by KVL) 1 We know V C

So voltage across will be higher than C3 By option checking only option B satisfy this condition Vc2 + Vc3 = 80 V and Vc2 > Vc3 2.6. Ans.(d) A1 reads current that flow through this in, half cycle (average value)

2.7. Ans.(b)

Vm 4 0.4 = = 10 10 Current through A1 will be vector sum of current through A2 and A3 I avg

for half cycle

Im

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-33

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

A1 = A22 + A32 = 16 + 9 = 25 = 5 A 1 v(t ) dt L

IES Academy

2.8. Ans.(d)

Voltage across inductor = v(t); Current flowing through inductor = Applying KCL at middle node e at + ebt = Differentiate both side L = 1H;

1 v(t ) dt L v(t ) = ae at + bebt

2.9. Ans.(c)

At t = 0 inductor will like short circuit and 2.5A current flow through inductor at t = 0+

V = 2.5 20 = 50V but Vx = V = 50 V

2.10. Ans.(d)

KVL in loop (i)

V 1 So, I1 ( s ) R + + I1 ( s) + I1 ( s ) I 2 ( s ) sL = 0 s sC 1 V I1 ( s) R + + sL I 2 ( s) sL = sc s

+ R

V S sL

1 SC

I1(s)

I2(s)

R

1 SC

KVL in loop (ii)

1 I 2 ( s) I1 ( s) sL + I 2 ( s)R + I 2 ( s) sc = 0; 1 R + sc + sL sL I1 ( s) V = s 1 ( ) I s sL R + sL + 2 o sc 1 I1 ( s) sL + I 2 ( s) R + sL + = 0 sc

2.11. Ans.(a)

At t 0 + Inductor behaves like open circuit and capacitor as short circuit V So, i1 (t ) = 2R 2.12. Ans.(b)

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-34

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

V (t ) = Ri(t ) + Ldi(t ) 1 + i(t ) dt dt C 0 Take laplace transform in both side I ( s) Vc ( o + ) 1 I ( s) 1 ; = I ( s) + sI ( s) 1 + + + Cs s s s s

IES Academy

V ( s) = RI ( s) + LsI ( s ) LI ( o + ) + I ( s) = s+2 s + s +1

2

2.13. Ans.(d) Equivalent impedance Leq = L1 + L2 2M 2.14. Ans.(b) 2.15. Ans.(a)

Time constant of circuit T = Req.Ceq = 1 103 0.1 10 6 = 1 10 4 sec, but applied pulse duration is 2 sec, so upto 2 sec capacitor will become fully charge Vc = 3V and output voltage Vo = Vc = 3V

Immediate after F.B. to R.B. diode show, same resistance as in F.B. till all storage charge at junction not removed. So, for 0 < t ts, VR will be 5V and after t > ts, VR will be become 0. 2.16. Ans.(b) Method 1: We Know capacitor in unchanged capacitor behaves like short circuit and fully change condition behave like open circuit. So, in V0(t) function if we put t 4 V0(t) will be equal to = 10 = 8 Volt 5 So, by option checking method (b) option satisfy this condition only.

Method 2:

V0 (t ) = V ( ) V ( ) V (0) e

V ( ) = 8 V; Ceq = 4 + 1 = 5 f ; V0 (t ) = 8 (8 0) e

t T V (0) = 0 V;

6

T = Req Ceq ;

3

Req = 4 � 1 = 0.8 k

T = 8 5 10 10 = 4 m sec

t /0.004

= 8(1 e t /0.004 )

2.17. Ans.(a)

Is

0.002s

dI dt Take L transform both side V(s) = sLI(s) LI(o) V =L

1mv

By the initial condition LI(o)=1 mv I(o) = I(o) = 0.5 A So, I(o) = 0.5 A

2.18. Ans.(b) At t = 0 when switch will close, inductor L will behaves like open circuit. Total voltage IS RS will drop across L di(0+ ) di(0+ ) I S RS I S RS = L = dt dt L 2.19. Ans.(d)

Z ( s) =

Circuit is parallel RLC

www.iesacademy.com

0.2s s + 0.1s + 2

2

E-mail: iesacademy@yahoo.com

Page-35

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

2

IES Academy

Y (s) =

1 s 0.1s 2 1 10 1 1 = + + Y ( s ) = 5s + + Y ( s) = Cs + + Z ( s) 0.2s 0.2s 0.2s 2 s R LS C = 5 F, R = 2 , L = 0.1H

2.20. Ans.(a)

20V I I1 + 60V -

Direction of current that flowing through 60 shown in figure Apply KCL at X I + I1 = 12 I = 12 I1 (i ) Only option (a) can be satisfying this condition.

X

2.21. Ans.(c)

V0 (S ) 1 = (i ) Vi (S ) 2 + sCR Given in question RL Vo (S ) 1 + sRLC RL (ii ) = = RL Vi (S ) sRRLC + ( RL + R ) +R 1 + sRLC R = RL

Compare ( i ) and ( ii )

2.22. Ans.(b) When switch on position for long time that means number of current will flow through circuit because capacitance become fully charged.

12A

+ -

Ceq = (0.5 + 0.3) � (0.2) F = 0.16 F Total potential across Ceq = 100 V Now when switch turn to position b equivalent circuit diagram

2.23. Ans.(a) 2.24. Ans.(a)

RCeq = 5 103 0.16 10 6 = 0.8 10 3 i(t ) = V ( o + ) t RC 100 t 8104 e u(t ) = e u(t ) R 5 = 20 e 1250 t u(t ) mA

Take Laplace in both side and put initial conditions, then solve.

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-36

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

L

IES Academy So, i ( 0 ) = 0.75 A

But at t = 0+, switch is closed and iL(0) = iL(0+) = 0.75 A So, value of i(t ) at 1.5 0.75 t=0= = 0.375 A 2

and at t = , value of i(t ) 1.5 will be i(t = ) = = 0.5 A 3 Because 15 mH, inductor will be short circuited. These conditions are full-filled only in option (a).

3.1. Ans.(a)

V1 = Z11 I1 + Z12 I 2 ; V1 = 2 I1 + I 2 ; V2 = 8 I1 + 3 I 2 V1 2 V = 8 2 V2 = Z21 I1 + Z22 I 2 V2 = 2 I 2 6 I1 V1

I1 I2-3I1 I2-2I1 3I1 I2

+

V1

+

V2

1 I1 3 I2

Transmission parameters will be multiplied. 3.2. Ans.(d) 3.3. Ans.(b, c)

Y21 = Y12 ;

3.4. Ans.(a) 3.5. Ans.(b)

0 Y = 1 2 1 2 0

h21 = h12

{Y12

y21 }

So, network is non-reciprocal because Y12 is negative that mean either energy storing or providing device available, so network is active also.

3.6. Ans.(a)

V1 h11 h12 I1 I = h h V ; 2 21 22 2 if V2 = 0; Applying KVL in R.H.S. R( I1 + I 2 ) + I 2 R = 0; RI1 + 2RI 2 = 0; I 2 1 = I1 2

{where, V1 = h11 I1 + h12V2 ,

I2 = h21 I1 (i )

I1 = h21 I1 + h22V2 }

3.7. Ans.(c)

www.iesacademy.com E-mail: iesacademy@yahoo.com Page-37

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

Z11 = E1 i1 at i2 = 0

IES Academy

Apply KVL in loop ( i ) E1 2i1 4i1 + 10E1 = 0; E1 6 = = Z11 i1 11

Z21 = E2 i1

11E1 = 6i1

at i2 = 0

KVL in loop (ii)

E2 4i1 + 10E1 = 0; E2 = 16 i1 ; 11 E1 = 6 60 i1 ; E2 4i1 + i1 = 0 11 11 E2 16 = = Z21 i1 11

3.8. Ans.(c)

It is network y + y3 y3 y11 y12 Y = 1 y y2 + y3 21 y22 y3 1 1 1 z + z z 3 3 = 1 1 1 1 + z z2 z3 3 Y12 = 1 1 = = 0.05 z3 20

I1

I2

3.9. Ans.(a)

By to Y 2 1 2 1 = = R1 = 4 4 2 2 1 2 1 = = R2 = 4 4 2 1 1 1 = R3 = 22 4

R1

R2

R3

z + z3 Z= 1 z3

z3 2.75 = z 2 + z3 0.25

0.25 2.75

Please check above figure

www.iesacademy.com E-mail: iesacademy@yahoo.com Page-38

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

3.10. Ans.(d) Given circuit is lattice network So, Z parameters (according standard result) Z a Zb Z a + Zb 2 1 + j 1 + j 2 = Z= Z a + Zb 1 + j 1 + j Z a Zb 2 2 3.11. Ans.(d)

+

V1

+

V2

+

V1

I1 = I 2 ; V1 = 10 = h11 ; I1

I2 = 1 = h21 ; V1 = 10 I1 I1 h11 = 10; h21 = 1

V1 = h11 I1 + h12V2 ; I 2 = h21 I1 + h22V2 V1 I if V2 = 0; = h11 and 2 = h21 I1 I1

Note: Only option d satisfy this values we can solve for h12 and h22 by making I1 = 0.

3.12. Ans.(b)

I 2 = nI1 V1 = nV2 V1 A B V2 I = C D I2 1 But according the question A B n o C D = o x I 2 V1 n = = ; I1 V2 2 (i )

A = n, B = o, C = o, D = x So, V1 = AV2 ; I1 = DI1 ; I1 1 1 = D = D = = X I2 n n

3.13. Ans.(d)

V1 A B = C D I1 V1 = AV2 BI 2 I1 = CV2 DI 2 V2 I2 (i )

Two-port is terminated by RL

(ii )

V2 = I 2 RL

(iii )

V1 AV2 BI 2 ARL I 2 BI 2 ARL + B = = = = input impedance I1 CV2 DI 2 CRL I 2 DI 2 CRL + D

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-39

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

V2 = Z21 I1 + Z22 I 2 ; Z11 = V1 6 / I =0 = = 1.5; 4 I1 2 Z12 = Z12 V1 4.5 / I1 =0 = = 4.5 1 I2 V 6 = 2 / I1 =0 = = 1.5 4 I1

IES Academy

3.14. Ans.(c)

V1 = Z11 I1 + Z12 I 2 ; Z22 = V2 1.5 / I =0 = = 1.5; 1 I2 1

1.5 4.5 So z parameter matrix = 1.5 1.5

3.15. Ans.(a)

V1 = h11 I1 + h12V2 ; V 4.5 (i ) h12 = 1 / I1 = 0 = = 3; 1.5 V2 V (iii ) h11 = 1 I1 V2 = Z21 I1 + Z22 I 2 = 0; I2 = h21 I1 + h22V2 V 1 (ii ) h22 = 2 / I1 = 0 = = 0.67 1.5 V2

I2 =

Z21 I1 Z22

Z I V Z Z 4.5 1.5 = 3 V1 = Z11 I1 + Z12 21 1 1 = Z11 12 21 = h11 = 1.5 1.5 I1 Z22 Z22 I Z21 1.5 3 3 (iv) h21 = 2 /V2 = 0 = h= = = 1; 1 0.67 1.5 I1 Z22

3.16. Ans.(a)

Y11 =

4.1. Ans.(c) 4.2. Ans.(b)

1 1 + = 4; 0.5 0.5

Y12 = Y21 = 2; Y22 =

1 1 + =4 0.5 0.5

According maximum power transfer theorem Ramp voltage = 100t Output of RC differentiating circuit = RC

dVi (t ) = 5 103 4 10 6 100 dt

= 20 10 1 = 2 volts

4.3. Ans.(a)

Rth across A.B for Rth voltage source become S.C. and circuit will like as R

th

36 44 = + = 2 + 2 = 4 k 9 8

So, value of R should be equal to Rth, according maximum power transfer theorem.

4.4. Ans.(d)

Leq = L1 + L2 K L1 L2 = 2 + 2 0.1 2 2 = 2 + 2 0.2 = 3.8 or 4.2

4.5. Ans.(a)

Super position theorem application only for linear and bidirectional element.

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-40

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

R2 = 5 15 = 1.5 ; 50 R3 = 15 30 = 9 50 R1 = 5 30 = 3 ; 50

IES Academy

4.6. Ans.(d) 4.7. Ans.(c) For maximum power transfer value of R should be conjugate symmetric with impedance of circuit (according maximum power transfer theorem) in circuit only resistance the R should be equal to require of circuit after removing R, for that find Rth across R. Terminal (Voltage source = ss.c and Current source = open circuit)

Rth

5 20 + 4 = 8 25 So, R = 8 Rth =

x A

4.8. Ans.(a) Voltage across xy = 1000 By voltage division rule 4j V th = 1000 = j16(3 4 j ) j4 + 3 4.9. Ans.(c)

j2

y

-j6

j4

VTH

By reciprocity theorem position and value of excitation change and double respectively so current will be double in magnitude, direction of source change so direction of current also will change.

4.10. Ans.(a)

Impedance of each branch of Wye-circuit =

3Z 3Z 3 3Z

Z 3

4.11. Ans.(a) For maximum power delivered to RL calculate Rth across RL terminal connect voltage source V across AB and current provided by V is I then V th =R ; I I1 I

KCL at A

V V I + 0.5 I1 =0 20 40 V V V V ; I1 = I+ = + 40 80 20 40 1 1 1 I =V + 20 40 80 V 80 = = 16 1 I 5

I1 A I

So, RL should be = 16

4.12. Ans.(a)

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-41

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

I

A I 3 I/6 I 6 I 6 I 3 I/6 I/3 I/3

IES Academy

VAB = I I I R+ R+ R 3 6 3 VAB 5 R = 1 ; = I 6

4.13. Ans.(c)

Zs = Z L

Note: Load impedance should be conjugated symmetric with source impedance, for

4.14. Ans.(b)

maximum power transfer.

Apply KCL at node a V th V th 10 + =1 5 5 V th = 7.5 V For Rth calculation make independent current source open, and independent voltage source short circuit, and dependent source will not change.

4.15. Ans.(c)

I1

Rth Rab = 5||5 = 2.5

For maximum power transfer

RL = RS 10 10 V2 V2 = = 0.25 W or 4 RL 4 Rs 4 100 4.16. Ans.(d) For maximum power transfer from the source to the load impedance, load impedance should be complex conjugate of the source impedance. So, if source impedance ZS = RS + jXS, then = RS jXS. 4.17. Ans.(d) P=

Apply KCL at X V th V th V th 2i 2= + + 2 1 1 th V But i = , So V th = 4 volt 1

th

x i

2i 2A

VTh

I sc = 2 A (if we short xy, V = 0) So, Rth = V th 4 = = 2 and V th = 4 volt, I sc 2

{R

th

=2

4.18. Ans.(a)

www.iesacademy.com E-mail: iesacademy@yahoo.com Page-42

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

1 s

IES Academy

Independent voltage source will become short circuit, and independent current source will become open circuit

1 Z th = ( s + 1) � s + = 1 s

Q

4.19. Ans.(c)

RL = Req Apply Thenvin Theorem. Apply KVL in aba 4( I I1 ) + VX VX 4 I1 = 0 I 4 I 4 I1 4 I1 = 0 I1 = 2 Again apply KVL in aba loop I 1 = 4 I1 + 4 I1 = 8 I1 = 8 2 1 = Req = 4 I

For Pmax

5. Sinusoidal Steady State Analysis, Resonance, Power in AC Circuits, Passive Filters

5.1. Ans.(d) 5.2. Ans.(a)

5.3. Ans.(c)

In series RLC high Q circuit, the current peaks at a frequency equal to the resonant frequency because at this condition circuit impedance minimum and current maximum. V1 V I Driving-point function is 1 or 1 ; = driving-point impedance function I1 I1 V1

I1 V = driving-point admittance function by analysis 1 is equal for N1 and N3. V1 I1 5.4. Ans.(b, d) According to phasor diagram current is leading to voltage. So, net behavior of circuit is capacitive. So, operating frequency < Resonant frequency.

5.5. Ans.(c)

A3 =

5.6. Ans.(c)

A1 + A2

For over-damped multiple poles on the negative real axis.

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-43

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

A series LCR circuit R = 10, X L = 20, X C = 20 circuit in resonance. So, current flowing in circuit = 200 = 20 A rms voltage across capacitor = 20 20 = R 400, but voltage is lagging to current. So, voltage across c = 400 90.

IES Academy

5.7. Ans.(d)

5.8. Ans.(a)

A series RLC circuit has

Z = 100 + j0 = R, R = 100 ; Qo =

Q = 100;

o = 107 rad/sec;

5.9. Ans.(c)

o L

R

Qo = 100 =

107 L ; 100

L = 10-3

Current through resistance i(t ) = 3 + 4 sin(100t + 45) + 4 sin(300t + 60) R.M.S. value fo current = i21rms + i 22rms + i 23rms i2 = 4 sin(100t + 45); 4 ; i1rms = 3; i2rms = 2 irms = 9 + 8 + 8 = 5 A where, i1 = 3; i3 = 4 sin(300t + 60) 4 i3rms = 2

Power dissipated in circuit = i 2rms R = 25 10 = 250 W

5.10. Ans.(b) Energy store in C =

1 1 CV 2 = CV 2 total energy provide by source = 2 times 2 2 1 CV 2 1 2 = = 0.5. energy stores in capacitor required ration = 2 2 CV 1 1 = = ; impedance offered by wC o.C

5.11. Ans.(c)

Impedance offered by C =

L = L = o.L = 0. So, DC voltage drop entirely across = C.

5.12. Ans.(b) 5.13. Ans.(b) Applying KVL in closed loop circuit 1 10 = 4 i(t ) + i(t ) dt c Take Laplace in both side

10 1 I ( s) V (0+ ) = 4 I ( s) + + 2 S S s

10 8 8S + 1 6 8S + 1 4 = I ( s) + S I ( s) 2S = S I ( s) = 8S + 1 2 S S i(t ) = e t /8

Energy absorbed by the 4 resistor in (o, ) interval

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-44

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

W =

i (t )R dt =

2t /8

4 dt = 4 e

0

t /8

e t /4 4 dt = 4 = 16[0 1] = 16 jouls 1 4 0

5.14. Ans.(a)

At frequency of resonance the network represent a resistive network, input voltage and current are in phase; input admittance has minimum value so, that input impedance has maximum value current drawn by network from mains has minimum value.

I =V 1 1 ; + C 2 L R

2

1 but C = 0; L

V = IRR

(i )

Current through inductor =

So, I R + I L < 1;

V , because current in lagging with voltage. j L

Similiary I R + I C > 1 and I R < 1

5.15. Ans.(a)

Method 1 : E cos t i2(t ) = m {at = 0} 1 R2 + jC Em =0 i2 (t ) = {at = } In this condition we can find only maximum possible value by case limitation. E i2 (t ) i2(t ) = m ; = 90 at = 0 R2 i2 (t ) =0 at = By option checking only option (a) satisfy both conditions.

Method 2:

i2

L

Em 2R2

Em 2R2

i2 (t ) =

Em cos t 1 R2 + jC Em C 90 tan 1 CR2 2 2 2 1 + C R2 i2 (t ) = 0, i(t ) = 90 i2 (t ) = E i(t ) = 0 R2

at 0; at ;

5.16. Ans.(d)

In star connection total power supplied = 3 VP I P cos or VL I L cos V V 3 L . L cos = 1500 3 3Z L 3VL 2 cos ; VL = 400 V 3 1500 3 1600 0.844 = 90 ZL = 3 1500 Power factor is positive, so load will be capacitive and = ve value ZL =

= cos 1 (0.844) = 32.44 ;

Z L = 90 32.44

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-45

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

20 20 5 I 5 I + =0 I =0 5 V1 20 = = 4 A. 5 5 Applying KVL V V1 5 I 5 I + 1 = 0 V1 = 20 V ; 5

IES Academy

5.17. Ans.(a)

That means current flow in 5 resistor only due to dependent source So, power delivered dependent source = I 2 R = 16 5 = 80 W.

5.18. Ans.(c)

Input voltage V (t ) = 10 2 cos(t + 10) + 10 5 cos(2t + 10) V ; Steady state current i (t ) = ? i(t ) = = Z = R + j 1 = 1 + j 1 = 1 + j

V (t ) 10 2 cos(t + 10) 10 5 cos(2t + 10) 10 2 cos(t + 10) 10 5 cos(2t + 10) = + = + 1 + j 1 + j 1+ j 1 + j2 Z 10 2 cos(t + 10) 245 + 10 5 cos(2t + 10) 5 tan 1 (2) = 10 cos (t 35 ) + 10 cos(2t + 10 tan 1 2)

5.19. Ans.(*) 5.20. Ans.(c)

Incomplete question (value of L1 is not given)

V (t ) = Ri(t ) + Ldi(t ) 1 + i(t ) dt dt C 2di(t ) sin t = 2i(t ) + + 1 i(t ) dt ; dt Q=

cos t = 2

di(t ) 2d 2i(t ) + + i(t ) dt dt 2

5.21. Ans.(b)

f0 1 1 , f0 = B. 2 LC Q = 1 L R C R B = for series (RLC ) L

Q 100 = = 50 2 2 5.22. Ans.(d) (i) At resonant frequency impedance of series RLC circuit is purely resistive If R, L, C all element doubled them Q ' =

(ii) For parallel RLC circuit

Q=

R

C 1 C = L G L

{if G them Q }

5.23. Ans.(d) 5.24. Ans.(b)

VC ( s ) V1( s )

So, S1 and S2 both statements are wrong. 1 1 1 106 SC LC = = 2 = = 2 R 1 1 S LC + SLR + 1 S + 106 S + 106 R + SL + S2 + S + SC L LC

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-46

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

H ( s) = Q=

IES Academy

n 10 � 2 6 2 s + 20s + 10 s + 2 n s + n

6 2 n 2

BW 103 1000 = = 50 Q= 20 20

= 103 and BW = 20

Note: In series circuit of RLC, BW =

R L

5.25. Ans. (c)

L 1 = = 0.5sec. At steady R 2 state, L behaves like short circuit. So, 1 current through R = = 0.5 V . 2

Time constant =

i(t)

.5A .31

1 2

t(sec)

5.26. Ans.(a)

1 j C = By voltage division rule Vo (t ) = V1 (t ) 1 R+ j C = 1 j 10 3 C 2 sin 10 3 t 1 R + j 10 3 C 1 j 10 3 C 2 sin 10 3 t 1 R + j 10 3 C 1 2 sin 10 3 t 3 j10 RC + 1 1 2 45 = sin(10 3 t 45 )

= But RC = 1 10 3 Vo ( t ) = 1 2 sin 10 3 t = j +1

2 sin 10 3 t

5.27. Ans.(a)

Note: = 2 ( sin 2t sin t )

1 1 Circuit is parallel RLC circuit i (t ) = v (t )Y = sin 2t + + jC R jC 1 1 = sin 2t + + jC R jC

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-47

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

1 1 i(t ) = sin 2 t + + j 2 3 13 j 2 1 4

IES Academy

= sin 2 t 3 j2 + j6 = sin 2 t 3 + j4 = 5sin ( 2 t + 53.1 )

5.28. Ans.(a)

By superposition theorem, when 50A source inacrive and remove 1060A (Open), then i1 = 5 0 , when 10 60A in active and remove 5 0 (open) i1 + 1060. So, total current = 10 1 3 3 10 3 + 10 j 5 1 = 10 jA 90 A . 2 2 2 2

5.29. Ans.(d) 5.30. Ans.(b)

If increases, phase shift is decrease for lag network.

In series RLC circuit R = 2 k , L = 1H and C = Resonant frequency = 1 2 1 F 400 1 1 1 1 1 = = 20 103 = 104 Hz LC 2 2 1 1 106 400

5.31. Ans.(c)

Transfer function of the circuit

Y ( s) = U ( s) 1 sc R + sL +

R y(t) C

1 sc

u(t)

+

-

1 2 n LC 2 2 1 R s + 2n s + n s2 + s + L LC 1 1 1 R R 2 n = 2n = 2 = 2 = n = LC L L LC LC R C For no oscillation condition 1; 1. 2 L Y ( s) 1 = = U ( s ) s2 LC + sCR + 1

C R C = 2 L L

5.32. Ans.(a)

For Z2 ( s ) positive real Re Z ( s) Rneg Rneg Re Z1 ( j ) for all .

Z1(s) Z2(s)

Rneg

N

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-48

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

IES Academy

5.33. Ans.(b) If first critical frequency = pole; second critical frequency = 3ero Then, passive network is RC network only 5.34. Ans.(d)

Phasor voltage VAB is = ? VAB = Current impedance = 530 (impedance between A & B ) (5 j3) (5 + j3) = 5 30 (5 j3) � (5 + j3) = 530 5 j3 + 5 + j3 34 25 j15 + j15 + 9) = 530 = 530 10 10

5.35. Ans.(a)

We know I C (t ) = I C ( ) [ I C ( ) I C (0)] e t /T where, I C ( ) = current through capacitor at

Note: We know capacitor behaves like short circuit at t = 0, but open circuit at

t . So, I C ( ) = 0 I C [0 + ] = 10 V = 0.5mA 20 k

T = time constant of charging of capacitor = ReqC

Req = (20 k ) � (20 k ) = 10 k T = 10 103 4 10 6 = 40 10 3 = 40 m sec So, I C (t ) = 0 [0 0.5] e I (t ) = 0.5exp( 25 t )mA

t /40 sec t 1000 40

= 0.5 e

= 0.5 e 25 t mA

5.36. Ans.(d) 3-dB bandwidth of Filter 1 is B1 and 3-dB bandwidth of Filter 2 is B2.

Note: Filter is RLC circuit and band width of series RLC circuit is =

B1 , BW = R L1 B1 L1 L2 1 = = = 4 = R. B2 L1 L1 4 L2 R R for B2 , BW = L1 L2 L1 where, L2 = 4

R . So, for L

5.37. Ans.(c)

Time constant of discharging of capacitor is double than, time constant of charging of capacitor. So waveform of VC is

VC = tu(t ) 2(t T ) u(t 2T ) + 2(t 2T ) u(t 2T ) = tu(t ) + 2 ( 1)n(t nT ) u(t nT )

n =1

) v c(t 1

2T T

-1

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-49

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Indias No 1

Network Theory

Chapter 1

Vi ( s) = 1 2 3

t 2

IES Academy

5.38. Ans.(d)

Voltage across capacitor 1 1 VC ( s) = Vi ( s); 1 s s +1 + s VC (t ) = 1 ; 1 s s +1 + s 1

VC (t ) =

3 t sin 2

5.39. Ans.(b)

Voltage across resistor 1 1 s+ s 2 2 1 = 2 = VR ( s) = 2 2 2 2 1 s + s +1 1 3 1 3 s +1 + s s + 2 + s + 2 + 2 2 3 3 1 sin VR (t ) = e t /2 cos t t 2 3 2 1

5.40. Ans.(c)

20 10 10 3 = = tan 1 = 2 1 + 2j + 7 + 4j 4 + 3j 5 4 3 = tan 1 4 I = 3 Reactive power = VI sin = 20 2 sin tan 1 = 40 sin (37) 24 VAR 4

5.41. Ans.(d)

Bandwidth = 1 1 1 1 1 , . Thus it is maximum at resonance. = + + RC Zi R X L XC

5.42. Ans.(a) 20 mH + 20 j & 50 F 20 j

Now apply KCL V Vx Vx Vx = + 20 j 1 20 j V Vx = (20 j ) Vx Vx V = 20 j.Vx 20 Vx = = 1 with angle 90 20 j V So, I = x = 1 with angle 90 1 So, I = ( 1 j )

www.iesacademy.com

E-mail: iesacademy@yahoo.com

Page-50

25, 1st Floor, Jia Sarai, Near IIT. New Delhi-16 Ph: 011-26537570, 9810958290

Das könnte Ihnen auch gefallen

- CH-1 (Network Theory) PDFDokument44 SeitenCH-1 (Network Theory) PDFshubhang2392Noch keine Bewertungen

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)Von EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)Noch keine Bewertungen

- GATE - EC - Networks PDFDokument39 SeitenGATE - EC - Networks PDFmsreenathreddyNoch keine Bewertungen

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisVon EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisNoch keine Bewertungen

- Electric Circuit and Fields QuestionsDokument38 SeitenElectric Circuit and Fields Questionssamg270% (1)

- Advanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkVon EverandAdvanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkNoch keine Bewertungen

- GATE CLOUD Network Analysis by R K KanodiaDokument126 SeitenGATE CLOUD Network Analysis by R K KanodiaAmit150462% (13)

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesVon EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNoch keine Bewertungen

- EE Mock Test-2 Modes of Heat Transfer 3 Ac Theory Module04 DC Theory Module 58iDokument21 SeitenEE Mock Test-2 Modes of Heat Transfer 3 Ac Theory Module04 DC Theory Module 58iAnonymous 8pCXXsNoch keine Bewertungen

- Advanced Control of AC / DC Power Networks: System of Systems Approach Based on Spatio-temporal ScalesVon EverandAdvanced Control of AC / DC Power Networks: System of Systems Approach Based on Spatio-temporal ScalesNoch keine Bewertungen

- Ee Sample PaperDokument19 SeitenEe Sample Paperjayapriyadarshni12Noch keine Bewertungen

- Vacuum Nanoelectronic Devices: Novel Electron Sources and ApplicationsVon EverandVacuum Nanoelectronic Devices: Novel Electron Sources and ApplicationsNoch keine Bewertungen

- EE 2000 UnsolvedDokument13 SeitenEE 2000 UnsolvedRama Krishna0% (1)

- Electronic Systems: Study Topics in Physics Book 8Von EverandElectronic Systems: Study Topics in Physics Book 8Bewertung: 5 von 5 Sternen5/5 (1)

- Network AnalysisDokument71 SeitenNetwork AnalysisJayNoch keine Bewertungen

- NetworksDokument85 SeitenNetworksMan SanNoch keine Bewertungen

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsVon EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNoch keine Bewertungen

- Electrical Engineering Sem-2 All Question BankDokument2.178 SeitenElectrical Engineering Sem-2 All Question BankGAURAV GUPTANoch keine Bewertungen

- GATEECSP2014Dokument223 SeitenGATEECSP2014nikin149Noch keine Bewertungen

- Power Systems-On-Chip: Practical Aspects of DesignVon EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNoch keine Bewertungen

- Networks Test-3 (Ac Analysis) KL UniversityDokument10 SeitenNetworks Test-3 (Ac Analysis) KL UniversitySURESH KUMAR PITTALANoch keine Bewertungen

- EC Mock Test-3Dokument20 SeitenEC Mock Test-3Arone AsadasNoch keine Bewertungen

- NetworksDokument14 SeitenNetworksjassi7010Noch keine Bewertungen

- Electric Circuit and FieldsDokument24 SeitenElectric Circuit and Fieldssamg27Noch keine Bewertungen

- Gate Ee - 1998Dokument17 SeitenGate Ee - 1998yoursprawinNoch keine Bewertungen

- TCE ComprehensionDokument142 SeitenTCE ComprehensionJaydithya KumarNoch keine Bewertungen

- Compre Queation PaperDokument6 SeitenCompre Queation PaperGanesh DharmireddyNoch keine Bewertungen

- Electrical Engineering 4Dokument17 SeitenElectrical Engineering 4Shubham DeshmukhNoch keine Bewertungen

- Mock Test Ee-EDokument16 SeitenMock Test Ee-Esamg27Noch keine Bewertungen

- Electrical Circuits & FieldsDokument90 SeitenElectrical Circuits & FieldsAkhilesh JindalNoch keine Bewertungen

- Electronic 1st 7 8Dokument22 SeitenElectronic 1st 7 8mohsindalvi87Noch keine Bewertungen

- Soalan Peperiksaan Semester Disember 2008/2009: Fakultikejuruteraan Elektrik UTMDokument442 SeitenSoalan Peperiksaan Semester Disember 2008/2009: Fakultikejuruteraan Elektrik UTMbualkosongNoch keine Bewertungen

- GATE (2012) Question Paper Electronics Electrical 18494Dokument15 SeitenGATE (2012) Question Paper Electronics Electrical 18494Uday KumarNoch keine Bewertungen

- Electrical Circuits - Test 1Dokument5 SeitenElectrical Circuits - Test 1madhubalansNoch keine Bewertungen

- Power Systems QuestionsDokument45 SeitenPower Systems Questionssamg27Noch keine Bewertungen

- MCQ Electrical CircuitsDokument81 SeitenMCQ Electrical CircuitsAnonymous sENwj8nwq50% (2)

- QN CollectionDokument96 SeitenQN Collectionபொறிஞன்Noch keine Bewertungen

- Gates PeeDokument486 SeitenGates Peenishantkumar339Noch keine Bewertungen

- GATE Electrical Engineering Solved 2013Dokument22 SeitenGATE Electrical Engineering Solved 2013RTNoch keine Bewertungen

- Revision Plan-II (DPP # 3) - PhysicsDokument12 SeitenRevision Plan-II (DPP # 3) - PhysicsBhriguKansra100% (1)

- GATE Electrical Engineering 2011Dokument18 SeitenGATE Electrical Engineering 2011naga7389Noch keine Bewertungen

- Electrical Engineering 1Dokument16 SeitenElectrical Engineering 1Tushar GargNoch keine Bewertungen

- Excellent Online Test Series Ee (2017) : Technical Academy Pvt. LTDDokument23 SeitenExcellent Online Test Series Ee (2017) : Technical Academy Pvt. LTDsayedNoch keine Bewertungen

- EE3503 Electrical and Electronic Power Systems May 2013Dokument3 SeitenEE3503 Electrical and Electronic Power Systems May 2013Rajesh PathakNoch keine Bewertungen

- GATE EE 2002 Actual Paper PDFDokument24 SeitenGATE EE 2002 Actual Paper PDFKeilla Romabiles LeopandoNoch keine Bewertungen

- GATE 2016 Electrical Engineering Official Question PaperDokument15 SeitenGATE 2016 Electrical Engineering Official Question PaperAnonymous 5jNzrktNoch keine Bewertungen

- II B.Tech II Semester, Regular Examinations, April - 2012 Electrical Circuit Analysis - IiDokument8 SeitenII B.Tech II Semester, Regular Examinations, April - 2012 Electrical Circuit Analysis - IiViswa ChaitanyaNoch keine Bewertungen

- (WWW - Entrance Exam - Net) EC 1991Dokument13 Seiten(WWW - Entrance Exam - Net) EC 1991Nagmani KumarNoch keine Bewertungen

- Control Systems ElectricalDokument60 SeitenControl Systems Electricalpushplatameena1Noch keine Bewertungen

- Paper2 ObjDokument21 SeitenPaper2 ObjSine SathesNoch keine Bewertungen

- Mock Gate EEEDokument13 SeitenMock Gate EEEnaga01013ee022Noch keine Bewertungen

- GATE Electrical Engineering Solved 2013 PDFDokument22 SeitenGATE Electrical Engineering Solved 2013 PDFPudeti RaghusreenivasNoch keine Bewertungen

- Question PaperDokument7 SeitenQuestion Papernprobo1Noch keine Bewertungen

- GATE - EDC Topic Wise Questions (1996-2011)Dokument27 SeitenGATE - EDC Topic Wise Questions (1996-2011)Waseem AkramNoch keine Bewertungen

- Nodia and Company: Gate Solved Paper Electrical Engineering 2006Dokument45 SeitenNodia and Company: Gate Solved Paper Electrical Engineering 2006VictorHernandezNoch keine Bewertungen

- Ee 2009 Gate PaperDokument16 SeitenEe 2009 Gate Papermass1984Noch keine Bewertungen

- Ec 2010Dokument18 SeitenEc 2010Tiken TakhellambamNoch keine Bewertungen

- JoesDokument1 SeiteJoessaketramaNoch keine Bewertungen

- IftDokument1 SeiteIftsaketramaNoch keine Bewertungen

- ETS Study GuidesDokument170 SeitenETS Study GuidessaketramaNoch keine Bewertungen

- Electrical TSSPDCL QP 2015Dokument14 SeitenElectrical TSSPDCL QP 2015Bada SainathNoch keine Bewertungen

- 100 True Ramtha StoriesDokument245 Seiten100 True Ramtha StoriesAnca-Laura Boteanu100% (2)

- New Microsoft Office Word DocumentDokument16 SeitenNew Microsoft Office Word DocumentsaketramaNoch keine Bewertungen

- II Sem Imp Questions All SubjectsDokument17 SeitenII Sem Imp Questions All SubjectssaketramaNoch keine Bewertungen

- ECET 2014 Electrical and Electronics Engg Question PaperDokument31 SeitenECET 2014 Electrical and Electronics Engg Question Papergayathri88% (16)

- Teach A Lesson To The Manipulators Who Manipulate You, Give Them The Taste of Their Own MedicineDokument1 SeiteTeach A Lesson To The Manipulators Who Manipulate You, Give Them The Taste of Their Own MedicinesaketramaNoch keine Bewertungen

- GoodDokument1 SeiteGoodsaketramaNoch keine Bewertungen

- Read All Books of ScribdDokument1 SeiteRead All Books of ScribdsaketramaNoch keine Bewertungen

- Everything Happens For A ReasonDokument1 SeiteEverything Happens For A ReasonsaketramaNoch keine Bewertungen

- SrikarnDokument1 SeiteSrikarnsaketramaNoch keine Bewertungen

- 2 Sem QuesDokument17 Seiten2 Sem QuessaketramaNoch keine Bewertungen

- 6th Central Pay Commission Salary CalculatorDokument15 Seiten6th Central Pay Commission Salary Calculatorrakhonde100% (436)