Beruflich Dokumente

Kultur Dokumente

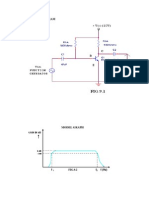

Circuit Diagram: F FIG.9.2 F F (HZ)

Hochgeladen von

ramyaarumugamOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Circuit Diagram: F FIG.9.2 F F (HZ)

Hochgeladen von

ramyaarumugamCopyright:

Verfügbare Formate

18 CIRCUIT DIAGRAM

MODEL GRAPH

f1

FIG.9.2

f2

f (Hz)

TAB.1.1: FREQUENCY RESPONSE OF FIXED BIAS AMPLIFIER Keep the input voltage constant (Vin) = Freque !" #$ H%& Ou'(u' )*+',-e #$ .*+'/& G,$ 0 21 +*- #)* 2 )$ & #$ 3B&

18 1. FIXED BIAS AMPLIFIER CIRCUIT 1.1. AIM: To construct a fixed bias amplifier circuit and to plot the frequency response characteristics 1.2APPARATUS REQUIRED: ! "o 1 ) . 1 6 ( "ame Transistor #esistor #egulated po/er supply !ignal 2enerator  !pread %oard &apacitor #ange %&1'( 1' *+,1'' *+,-8' + ('0.')V ('0.)345 .' 345 1(89 $uantity 1 1,1,1 1 1 1 1 )

1.4. FORMULA: a) R2 2 #R15R2& 0 voltage at /hich &lass :, &lass % or &lass & operation ta*es place

b) hfe = ;<c = ;<b

1.6. THEORY: <n order to operate the transistor in the desired region, /e have to apply an external dc voltage of correct polarity and magnitude to the t/o >unctions of the transistor This is called biasing of the transistor ?hen /e bias a transistor, /e establish a certain current and voltage conditions for the transistor These conditions are called operating conditions or dc operating point or quiescent point This point must be stable for proper operation of transistor :n important and common type of biasing is called 9ixed %iasing The circuit is very simple and uses only fe/ components %ut the circuit does not chec* the collector current /hich increases /ith the rise in temperature

1.7. PROCEDURE 1 &onnections are made as per the circuit diagram

18 ) . 1 6 The /aveforms at the input and output are observed for &lass :, &lass % and &lass & operations by varying the input voltages The biasing resistances needed to locate the $0point are determined !et the input voltage as 1V and by varying the frequency, note the output voltage &alculate gain=)' log (Vo = Vin) : graph is plotted bet/een frequency and gain

1.8. CALCULATIONS: ,& T* 3e'er9$ e ':e .,+ue *; <$,/ re/$/', !e R2 2 #R15 R2& :;e 0= IC2=IB

<&

1.>. RESULT: Thus, the 9ixed bias amplifier /as constructed and the frequency response curve is plotted

18

FIG.7.1

MODEL GRAPH

f1

FIG..2

f2

f (Hz)

TAB 2.1: ?ee( ':e $ (u' .*+',-e !* /', '@ )$ 0 Freque !" #$ H%& Ou'(u' )*+',-e #$ .*+'/& G,$ 0 21 +*-#)*2)$ & #$ 3B&

2. BAT AMPLIFIER USING )OLTAGE DI)IDER BIAS

18

2.1. AIM: To constant a voltage divider bias amplifier and measure input resistance and gain and also to plot the dc collector current as a function of collector resistance 2.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 ( 2.4. FORMULA: "ame Transistor #esistor &apacitor 9unction 2enerator  #egulated po/er supply %read %oard #ange %& 1'( 6-*@,1)*@,) )*@,1('@ ' 189, 1(89 ('0.)345 .'345 ('0.')V $uantity 1 1,1,1,1 ), 1 1 1 1 1

a) #in = A B #e b) 2ain = A B #e=#in

2.6. THEORY: This type of biasing is other/ise called Cmitter %iasing The necessary biasing is provided using . resistorsD #1, #) and #e The resistors #1 and #) act as a potential divider and give a fixed voltage to the base <f the collector current increases due to change in temperature or change in A, the emitter current < e also increases and the voltage drop across #e increases, reducing the voltage difference bet/een the base and the emitter Eue to reduction in Vbe, base current <b and hence collector current <c also reduces This reduction in Vbe, base current <b and hence collector current <c also reduces This reduction in the collector current compensates for the original change in <c The stability factor != (1FA) B ((1= (1FA)) To have better stability, /e must *eep #b=#e as small as possible 4ence the value of #1 #) must be small <f the ratio # b=#e is *ept fixed, ! increases /ith A

2.7. PROCEDURE:

18 1 ) . 1 &onnections are given as per the circuit diagram 3easure the input resistance as #in=Vin=<in (/ith output open) and gain by plotting the frequency response &ompare the theoretical values /ith the practical values Glot the dc collector current as a function of the collector resistance (ie) plot of Vcc and <c for various values of #e

2.8. RESULT: Thus the voltage divider bias amplifier /as constructed and input resistance and gain /ere determined

CIRCUIT DIAGRAM

18

MODEL GRAPH

f1

FIG..2

f2

f (Hz)

TAB 4.1: ?ee( ':e $ (u' .*+',-e !* /', '@ )$ 0

18

Freque !" #$ H%&

Ou'(u' )*+',-e #$ .*+'/&

G,$ 0 21 +*-#)*2)$ & #$ 3B&

4. COMMON COLLECTOR AMPLIFIER

18 4.1 AIM: To construct a common collector amplifier circuit and to plot the frequency response characteristics 4.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 ( 4.4 THEORY: The d c biasing in common collector is provided by #1, #) and #C The load resistance is capacitor coupled to the emitter terminal of the transistor ?hen a signal is applied to the base of the transistor ,V% is increased and decreased as the signal goes positive and negative, respectively &onsidering V%C is constant the variation in the V% appears at the emitter and emitter voltage VC /ill vary same as base voltage V% !ince the emitter is output terminal, it can be noted that the output voltage from a common collector circuit is the same as its input voltage 4ence the common collector circuit is also *no/n as an emitter follo/er 4.7 PROCEDURE: 1 &onnect the circuit as per the circuit diagram ) !et Vi =6' mv, using the signal generator . Keeping the input voltage constant, vary the frequency from ' 45 to 13 45 in regular steps and note do/n the corresponding output voltage 1 Glot the graphH 2ain (d%) vs 9requency(45) "ame Transistor #esistor &apacitor 9unction 2enerator  #egulated po/er supply %read %oard #ange %& 1'( 16*@,1'*@,-8'@,-*@ ' 189, 1(89 ('0.)345 .'345 ('0.')V $uantity 1 1,1,1,1 ), 1 1 1 1 1

RE)IEB QUESTIONS:

18 1 ?hy the common collector amplifier is also called as an emiteer follo/erI

) ?hat is the need for coupling capacitorsI

. ?hat /ill be the input Joutput impedance of common collector amplifierI

1 ?rite some applications of common collector amplifierI

6 ?hat is the current amplification factor of common collector amplifierI

4.8. RESULT: Thus, the &ommon collector amplifier /as constructed and the frequency response curve is plotted

CIRCUIT DIAGRAM

18

MODEL GRAPH

f1

FIG..2

f2

f (Hz)

TAB 6.1:

18 ?ee( ':e $ (u' .*+',-e !* /', '@ )$ 0 Freque !" #$ H%& Ou'(u' )*+',-e #$ .*+'/& G,$ 0 21 +*-#)*2)$ & #$ 3B&

6. DARLINGTON AMPLIFIER USING BAT 6.1 AIM:

18 To construct a Earlington current amplifier circuit and to plot the frequency response characteristics 6.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 ( 1.4 "ame Transistor #esistor &apacitor 9unction 2enerator  #egulated po/er supply %read %oard #ange %& 1'( 16*@,1'*@,-8'@,-*@ ' 189, 1(89 ('0.)345 .'345 ('0.')V $uantity 1 1,1,1,1 ), 1 1 1 1 1

THEORY:

<n Earlington connection of transistors, emitter of the first transistor is directly connected to the base of the second transistor %ecause of direct coupling dc output current of the first stage is (1Fh fe )<b1 <f Earlington connection for n transitor is considered, then due to direct coupling the dc output current foe last stage is (1Fh fe ) n times <b1 Eue to very large amplification factor even t/o stage Earlington connection has large output current and output stage may have to be a po/er stage :s the po/er amplifiers are not used in the amplifier circuits it is not possible to use more than t/o transistors in the Earlington connection <n Earlington transistor connection, the lea*age current of the first transistor is amplified by the second transistor and overall lea*age current may be high, ?hich is not desired 6.6 PROCEDURE: 1 &onnect the circuit as per the circuit diagram ) !et Vi =6' mv, using the signal generator . Keeping the input voltage constant, vary the frequency from ' 45 to 13 45 in regular steps and note do/n the corresponding output voltage 1 Glot the graphH 2ain (d%) vs 9requency(45) 6 &alculate the band/idth from the graph

RE)IEB QUESTIONS: 1 ?hat is meant by darlington pair

18

) 4o/ many transistors are used to construct a darlington amplifier circuitI

. ?hat is the advantage of Earlington amplifier circuitI

1 ?rite some applications of Earlington amplifier I

6.7. RESULT: Thus, the Earlington current amplifier /as constructed and the frequency response curve is plotted

18

FIG.14.1 MODEL GRAPH

f1

f2

f (Hz)

FIG.14.2 TAB.7.1. Keep the input voltage constant (Vin) = Freque !" #$ H%& Ou'(u' )*+',-e #$ .*+'/& G,$ 0 21 +*- #)* 2 )$ & #$ 3B&

18 7. SOURCE FOLLOBER BOOTSTRAPPED GATE RESISTANCE 7.1. AIM: To construct a source follo/er bootstrapped gate resistance amplifier circuit and to plot the frequency response characteristics 7.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 ( 7.4. THEORY: !ource follo/er is similar to the emitter follo/er( the output source voltage follo/ the gate input voltage),the circuit has a voltage gain of less than unity, no phase reversal, high input impedance, lo/ output impedance 4ere the %ootstrapping is used to increase the input resistance by connecting a resistance in bet/een gate and source terminals The resister #: is required to develop the necessary bias for the gate 7.6. PROCEDURE: 1 &onnections are made as per the circuit diagram ) The /aveforms at the input and output are observed for cascode operations by varying the input frequency . The biasing resistances needed to locate the $0point are determined 1 !et the input voltage as 1V and by varying the frequency, note the output voltage 6 &alculate gain=)' log (Vo = Vin ) - : graph is plotted bet/een frequency and gain RESULT: Thus, the !ource follo/er /ith %ootstrapped gate resistance /as constructed and the gain /as determined "ame Transistor #esistor #egulated po/er supply !ignal 2enerator  %read %oard &apacitor #ange %&1'( 1*+,11 *+,13 *+ ('0.')V ('0.)345 .' 345 ' '189 $uantity ) 1,1,1 1 1 1 1 )

18

RE)IEB QUESTIONS: 1 ?hat is meant by source follo/erI

?hat is meant by %ootstrappingI

4o/ the above circuit provide a good impedance matchingI

?hat is the advantage of bootstrapping methodI

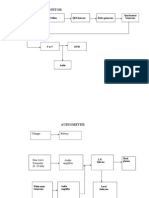

DIFFERENTIAL AMPLIFIER USING BAT CIRCUIT DIAGRAM

18

OBSER)ATION )IN 0)O 0AC 0 )O 2 )IN FORMULA: &ommon mode 2ain (:c) = V7 = V<" Eifferential mode 2ain (:d) = V' = V<" ?here V<" = V1 K V) &ommon 3ode #e>ection #atio (&3##) = :d=:c ?here, :d is the differential mode gain :c is the common mode gain THEORY: The differential amplifier is a basic stage of an integrated operational amplifier <t is used to amplify the difference bet/een ) signals <t has excellent stability, high versatility and immunity to noise <n a practical differential amplifier, the output depends not only upon the difference of the ) signals but also depends upon the common mode signal Transistor $1 and $) have matched characteristics The values of # &1 and #&) are equal #e1 and #e) are also equal and this differential amplifier is called emitter coupled differential amplifier The output is ta*en bet/een the t/o output terminals

18

AIM: To construct a differential amplifier using %LT and to determine the dc collector current of individual transistors and also to calculate the &3## 8.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 "ame Transistor #esistor #egulated po/er supply 9unction 2enerator  %read %oard OBSER)ATION )IN 0 )1 C )2 )1 0 A3 0 )12 )IN 9or the differential mode operation the input is ta*en from t/o different sources and the common mode operation the applied signals are ta*en from the same source #ange %&1'( 1 (*+, 1'*+ ('0.')V ('0.) 345 .' 345 $uantity ) ),1 1 ) 1 1

18 &ommon 3ode #e>ection #atio (&3##) is an important parameter of the differential amplifier &3## is defined as the ratio of the differential mode gain, : d to the common mode gain, :c &3## = :d = :c <n ideal cases, the value of &3## is very high

8.7. PROCEDURE: 1 ) &onnections are given as per the circuit diagram To determine the common mode gain, /e set input signal /ith voltage

Vin=)V

and determine Vo at the collector terminals &alculate common mode gain,

:c=Vo=Vin

. To determine the differential mode gain, /e set input signals /ith voltages V1 and V) &ompute Vin=V10V) and find Vo at the collector terminals &alculate differential mode gain, :d=Vo=Vin &alculate the &3##=:d=:c 3easure the dc collector current for the individual transistors

1 6 RESULT:

Thus, the Eifferential amplifier /as constructed and dc collector current for the individual transistors is determined The &3## is calculated as

18

RE)IEB QUESTIONS 1 ?hat is a differential amplifierI

) ?hat is common mode and differential mode inputs in a differential amplifierI

. Eefine &3##

1 ?hat is common mode signalI

6 8.8.

?rite some applications of Eifferential amplifier

CIRCUIT DIAGRAM

18

TAB 2.1: ?ee( ':e $ (u' .*+',-e !* /', '@ )$ 0 Freque !" #$ H%& Ou'(u' )*+',-e #$ .*+'/& G,$ 0 21 +*-#)*2)$ & #$ 3B&

>. CLASS D A POBER AMPLIFIER >.1. AIM:

18 To construct a &lass : po/er amplifier and observe the /aveform and to compute maximum output po/er and efficiency >.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 ( >.4. FORMULA M,E$9u9 (*Fer 'r, /;er 0P*@9,E0)*22RL E;;e!$e !"@G 0 P*@9,E2P! >.6. THEORY: The po/er amplifier is said to be &lass : amplifier if the $ point and the input signal are selected such that the output signal is obtained for a full input signal cycle 9or all values of input signal, the transistor remains in the active region and never enters into cut0off or saturation region ?hen an a c signal is applied, the collector voltage varies sinusoidally hence the collector current also varies sinusoidally The collector current flo/s for .-'' (full cycle) of the input signal i e the angle of the collector current flo/ is .-'' >.7 PROCEDURE: 1 &onnect the circuit as per the circuit diagram ) !et Vi =6' mv, using the signal generator . Keeping the input voltage constant, vary the frequency from 1' 45 to 13 45 in regular steps and note do/n the corresponding output voltage 1 Glot the graphH 2ain (d%) vs 9requency(45) RESULT: Thus the &lass : po/er amplifier /as constructed The follo/ing parameters /ere calculatedD a) 3aximum output po/er= N Cfficiency= "ame Transistor #esistor &apacitor !ignal 2enerator  #egulated po/er supply %read %oard #ange &M1'', %&668 1(*@,..@,))'+, 1( 89 ('0.)345 .'345 ('0.')V $uantity 1,1 ),1 ) 1 1 1 1

RE)IEB QUESTIONS:

18 1 ?hat is meant by Go/er :mplifier

?hat is the maximum efficiency in class K: amplifier

?hat are the disadvantages of &lass K: amplifier

?rite some applications of Go/er amplifier

6 ?hat si the position of $0point in &lass K: amplifier

B& >.8.

CIRCUIT DIAGRAM

18

PROCEDURE: 1 ) . 1 6 &onnections are given as per the circuit diagram /ithout diodes 7bserve the /aveforms and note the amplitude and time period of the input signal and distorted /aveforms &onnections are made /ith diodes 7bserve the /aveforms and note the amplitude and time period of the input signal and output signal Era/ the /aveforms for the readings &alculate the maximum output po/er and efficiency

4ence the nature of the output signal gets distorted and no longer remains the same as the input This distortion is called cross0over distortion Eue to this distortion, each transistor conducts for less than half cycle rather than the complete half cycle To overcome this distortion, /e add ) diodes to provide a fixed bias and eliminate cross0over distortion H.7. H.8.RESULT: Thus the &lass % complementary symmetry po/er amplifier /as constructed to observe cross0over distortion and the circuit /as modified to avoid the distortion The follo/ing parameters /ere calculatedD c) 3aximum output po/er= Cfficiency H. CLASS B COMPLEMENTARY SYMMETRY POBER AMPLIFIER

18 H.1. AIM: To construct a &lass % complementary symmetry po/er amplifier and observe the /aveforms /ith and /ithout cross0over distortion and to compute maximum output po/er and efficiency H.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 ( 8 H.4. FORMULA: "ame Transistor #esistor &apacitor Eiode !ignal 2enerator  #egulated po/er supply %read %oard #ange &M1'', %&668 1 (*@,16*@ 1''89 <"1''( ('0.)345 .'345 ('0.')V $uantity 1,1 ),1 ) ) 1 1 1 1

<nput po/er, Gin=)Vcc<m=O 7utput po/er, Gout=Vm<m=) Go/er 2ain or efficiency, P=Q=1(Vm=Vcc) 1''

H.6. THEORY: : po/er amplifier is said to be &lass % amplifier if the $0point and the input signal are selected such that the output signal is obtained only for one half cycle for a full input cycle The $0point is selected on the R0axis 4ence, the transistor remains in the active region only for the positive half of the input signal There are t/o types of &lass % po/er amplifiersD Gush Gull amplifier and complementary symmetry amplifier <n the complementary symmetry amplifier, one n0p0n and another p0n0p transistor is used The matched pair of transistor are used in the common collector configuration <n the positive half cycle of the input signal, the n0p0n transistor is driven into active region and starts conducting and in negative half cycle, the p0n0p transistor is driven into conduction 4o/ever there is a period bet/een the crossing of the half cycles of the input signals, for /hich none of the transistor is active and output, is 5ero

CIRCUIT DIAGRAM

18

FIG.8.2 OBSER)ATION OUTPUT SIGNAL AMPLITUDE TIME PERIOD CALCULATION POBER@ PIN OUTPUT POBER@ POUT EFFICIENCY@ G 0 2)CC I92I 0 )9I922 : :

0 # I26&# )92 )CC& E 111

MODEL GRAPH

18

FIG.8.4

CIRCUIT DIAGRAM:

18 BITHOUT FILTER:

FIG.14.1 BITH FILTER:

FIG.14.2

9. HALF BA)E RECTIFIER 9.1. AIM: To construct half /ave rectifier and to dra/ their input and output

18 /aveforms 9.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 "ame Transformer Eiode #esistor &apacitor  %read %oard #ange ).' V = -0'0(0-) <"1''( 1 *+ 1''89 .' 345 $uantity 1 1 1 1 1 1

9.4. FORMULA USED: R$((+e F,!'*r 0 B:ere I9 $/ ':e (e,J !urre ' 9.6. THEORY: H,+; F,.e re!'$;$er: : rectifier is a circuit, /hich uses one or more diodes to convert : & voltage into E & voltage <n this rectifier during the positive half cycle of the : & input voltage, the diode is for/ard biased and conducts for all voltages greater than the offset voltage of the semiconductor material used The voltage produced across the load resistor has same shape as that of the positive input half cycle of : & input voltage Euring the negative half cycle, the diode is reverse biased and it does not conduct !o there is no current flo/ or voltage drop across load resistor The net result is that only the positive half cycle of the input voltage appears at the output 9.7. PROCEDURE: 1 ) . 1 &onnect the circuit as per the circuit diagram :pply a c input using transformer 3easure the amplitude and time period for the input and output /aveforms &alculate ripple factor

MODEL GRAPH:

18

FIG.14.7 TAB.9.1: HALF BA)E RECTIFIER: ?ithout filter <nput signal :mplitude(V) Time period ?ith filter 7utput signal :mplitude(V) Time period

9.8. RESULT: Thus the half /ave rectifier /as constructed and its input and output /aveforms are dra/n The ripple factor of capacitive filter is calculated as #ipple factor=

18 FULLBA)E RECTIFIER

FIG.H.1 FULLBA)E RECTIFIER BITH FILTER

FIG.H.2 11. FULL BA)E RECTIFIER 11.1. AIM: To construct a full /ave rectifier and to measure dc voltage under load and to calculate the ripple factor

18 11.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 "ame Transformer Eiode #esistor &apacitor  %read %oard #ange ).' V = -0'0(0-) <"1''( 1 *+ 1''89 .' 345 $uantity 1 ) 1 1 1 1

11.4. FORMULA R$((+e F,!'*r 0 K L#I92K2& 2 #2MI9 2I&N 2D1 B:ere I9 $/ ':e (e,J !urre ' 11.6. THEORY: The full /ave rectifier conducts for both the positive and negative half cycles of the input ac supply <n order to rectify both the half cycles of the ac input, t/o diodes are used in this circuit The diodes feed a common load #M /ith the help of a centre tapped transformer The ac voltage is applied through a suitable po/er transformer /ith proper turnSs ratio The rectifierSs dc output is obtained across the load The dc load current for the full /ave rectifier is t/ice that of the half /ave rectifier The lo/est ripple factor is t/ice that of the full /ave rectifier The efficiency of full /ave rectification is t/ice that of half /ave rectification The ripple factor also for the full /ave rectifier is less compared to the half /ave rectifier . PROCEDURE: 1 ) . 1 6 &onnections are given as per the circuit diagram /iyhout filter "ote the amplitude and time period of the input signal at the secondary /inding of the transformer and rectified output #epeat the same steps /ith the filter and measure Vdc &alculate the ripple factor Era/ the graph for voltage versus time

MODEL GRAPH

18

RESULT: Thus, the full /ave rectifier /as constructed and the ripple factor /as calculated as #ipple factor =

11.7RE)IEB QUESTIONS:

18 1 ?hat is meant by rectifierI

?rite the operation of t/o diodes during the application of :& input signal

?hich type of transformer used for the rectifier inputI

Eefine ripple factor

?rite the efficiency of this rectifier

11.8.

18

FIG.11.1 MODEL GRAPH

f1

FIG.11.2

f2

f (Hz)

TAB.11.1. FREQUENCY RESPONSE OF CASCODE AMPLIFIER Keep the input voltage constant (Vin) = Freque !" #$ H%& Ou'(u' )*+',-e #$ .*+'/& G,$ 0 21 +*- #)* 2 )$ & #$ 3B&

11. CASCADE AMPLIFIER CIRCUIT

18

11.1. AIM: To construct a cascade amplifier circuit and to plot the frequency response characteristics 11.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 ( "ame Transistor #esistor #egulated po/er supply !ignal 2enerator  !pread %oard &apacitor #ange %&1'( 1'*+,8 *+,6'' +,1''+ ('0.')V ('0.)345 .' 345 ' '189 $uantity 1 1,1,1,1 1 1 1 1 6

11.4. THEORY: : cascade amplifier has many of the same benefits as a cascode : cascade is basically a differential amplifier /ith one input grounded and the side /ith the real input has no load <t can also be seen as a common collector (emitter follo/er) follo/ed by a common base %y cascading a &C stage follo/ed by an emitter0follo/er (&&) stage, a good voltage amplifier results The &C input resistance is high and && output resistance is lo/ The && contributes no increase in voltage gain but provides a near voltage0source (lo/ resistance) output so that the gain is nearly independent of load resistance The high input resistance of the &C stage ma*es the input voltage nearly independent of input0source resistance 3ultiple &C stages can be cascaded and && stages inserted bet/een them to reduce attenuation due to inter0stage loading

RE)IEB QUESTIONS

18 1 ?hat is meant by &ascadingI

) ?hat is the overall gain of the t/o stage cascaded amplifierI

. ?hat methods are used for cascadingI

1 ?hat is the disadvantage of direct coupled cascade amplifierI

6 ?rite some application of cascaded amplifier

11.6. PROCEDURE:

18 1 &onnections are made as per the circuit diagram ) The /aveforms at the input and output are observed for cascade operations by varying the input frequency . The biasing resistances needed to locate the $0point are determined 1 !et the input voltage as 1V and by varying the frequency, note the output voltage 6 &alculate gain=)' log (Vo = Vin ) - : graph is plotted bet/een frequency and gain

11.7. RESULT: Thus, the &ascade amplifier /as constructed and the gain /as determined

18

FIG.12.1 MODEL GRAPH

f1

FIG.12.2

f2

f (Hz)

TAB.12.1. FREQUENCY RESPONSE OF CASCODE AMPLIFIER Keep the input voltage constant (Vin) = Freque !" #$ H%& Ou'(u' )*+',-e #$ .*+'/& G,$ 0 21 +*- #)* 2 )$ & #$ 3B&

12. CASCODE AMPLIFIER CIRCUIT

18 12.1. AIM: To construct a cascode amplifier circuit and to plot the frequency response characteristics 12.2. APPARATUS REQUIRED: ! "o 1 ) . 1 6 ( "ame Transistor #esistor #egulated po/er supply !ignal 2enerator  %read %oard &apacitor #ange %&1'( ))*+,- *+,('' +,1('+ 1- *+,- ) *+,. . *+ 1 1 *+ ('0.')V ('0.)345 .' 345 ' '189 $uantity ) 1,1,1,1, 1,1,1, 1 1 1 1 1 .

12.4. THEORY: : cascode amplifier consists of a common emitter amplifier stage in series /ith a common base amplifier stage <t it one approach to solve the lo/ impedance problem of a common base circuit Transistor $1 and its associated components operate as a common emitter amplifier, /hile the circuit of $) functions as a common base output stage The cascade amplifier gives the high input impedance of a common emitter amplifier, as /ell as the good voltage gain and frequency performance of a common base circuit 12.6. PROCEDURE: 1 &onnections are made as per the circuit diagram ) The /aveforms at the input and output are observed for cascode operations by varying the input frequency . The biasing resistances needed to locate the $0point are determined 1 !et the input voltage as 1V and by varying the frequency, note the output voltage 6 &alculate gain=)' log (Vo = Vin ) - : graph is plotted bet/een frequency and gain

RE)IEB QUESTIONS: 1 ?hat is meant by &ascodingI

18

) ?hat is the overall gain of the t/o stage cascaded amplifierI

. ?hat methods are used for cascadingI

1 ?hat is the disadvantage of direct coupled cascade amplifierI

6 &ompare cascade amplifier /ith cascade amplifier

12.7. RESULT: Thus, the &ascade amplifier /as constructed and the gain /as determined

18

18

Das könnte Ihnen auch gefallen

- EC - I Lab AmnualDokument44 SeitenEC - I Lab AmnualMurali DharanNoch keine Bewertungen

- Vbe Multiplier - Lab5 - AppendixDokument15 SeitenVbe Multiplier - Lab5 - AppendixSidney O. EbotNoch keine Bewertungen

- Lab Experiment 8Dokument8 SeitenLab Experiment 8Meredith Jensen0% (1)

- (Experiment 7) Operational Amplifier - Basic Op-Amp Circuit (Comparator, Summing, Integrators, and Differentiators) PDFDokument13 Seiten(Experiment 7) Operational Amplifier - Basic Op-Amp Circuit (Comparator, Summing, Integrators, and Differentiators) PDFArik JuniarNoch keine Bewertungen

- EDC Lab ManualDokument46 SeitenEDC Lab ManualMOUNIRAGESHNoch keine Bewertungen

- Quaid-E-Awam University of Engg., Sci. & Tech., Nawabshah Department of Telecommunication Engineering Amplifiers & OscillatorsDokument5 SeitenQuaid-E-Awam University of Engg., Sci. & Tech., Nawabshah Department of Telecommunication Engineering Amplifiers & Oscillatorsakjan303Noch keine Bewertungen

- Adc Lab Manual PDFDokument74 SeitenAdc Lab Manual PDFJega Deesan75% (4)

- SCC Lab ManualDokument28 SeitenSCC Lab ManualprashantNoch keine Bewertungen

- Experiment 14 Common Emitter Amplifier Biasing and GainDokument19 SeitenExperiment 14 Common Emitter Amplifier Biasing and GainAdnan Khan0% (1)

- Name of The Simulation:: Pin 1 (Offset Null)Dokument10 SeitenName of The Simulation:: Pin 1 (Offset Null)sabitavabiNoch keine Bewertungen

- Expt. 3 EEE 214 Name of The Experiment: Op-Amp As An Ampliifier ObjectiveDokument3 SeitenExpt. 3 EEE 214 Name of The Experiment: Op-Amp As An Ampliifier ObjectivesabitavabiNoch keine Bewertungen

- Ecgr3155 Experiment 8 Mosfet Amplifiers Configurations and Input Output ImpedancesDokument9 SeitenEcgr3155 Experiment 8 Mosfet Amplifiers Configurations and Input Output ImpedancesdrhammoudaNoch keine Bewertungen

- 01 - Experiment Diode j09Dokument19 Seiten01 - Experiment Diode j09Ahmed Sobhy KhattabNoch keine Bewertungen

- Electronics Sample Lab ReportDokument10 SeitenElectronics Sample Lab ReportLeo Marcelo VillalbaNoch keine Bewertungen

- List of ExperimentsDokument22 SeitenList of ExperimentsloganathanNoch keine Bewertungen

- Circuit Diagram: F FIG.9.2 F F (HZ)Dokument8 SeitenCircuit Diagram: F FIG.9.2 F F (HZ)rediffoooNoch keine Bewertungen

- The Operation Amplifier:: Level TranslatorDokument8 SeitenThe Operation Amplifier:: Level TranslatorPrafull BNoch keine Bewertungen

- Chapter 1: Op-Amps: I. Practical Op-AmpDokument11 SeitenChapter 1: Op-Amps: I. Practical Op-Amprockrockyrocker123Noch keine Bewertungen

- Op-Amps: I. Practical Op-AmpDokument7 SeitenOp-Amps: I. Practical Op-AmpSteven Nelson100% (1)

- Silicon Wafer (Substrate) Preparation 2. Epitaxial Growth 3. Oxidation 4. Photolithography 5. Diffusion 6. Ion Implantation 7. Isolation Techniques 8. MetallizationDokument21 SeitenSilicon Wafer (Substrate) Preparation 2. Epitaxial Growth 3. Oxidation 4. Photolithography 5. Diffusion 6. Ion Implantation 7. Isolation Techniques 8. MetallizationMangaiyarkarasi VengatachalamNoch keine Bewertungen

- Sharmi ECE a-D-Circuits Lab ManualDokument74 SeitenSharmi ECE a-D-Circuits Lab ManualSharmila83Noch keine Bewertungen

- Lab # 5Dokument8 SeitenLab # 5Eunice Caballero IriasNoch keine Bewertungen

- Lab 1-Bjt AmplifierDokument8 SeitenLab 1-Bjt Amplifierhasnain3257100% (1)

- Long Report 7Dokument6 SeitenLong Report 7Ahmad Najmi100% (1)

- Objective: Expt. 5 EEE 214Dokument2 SeitenObjective: Expt. 5 EEE 214sabitavabiNoch keine Bewertungen

- Design of A Discrete BJT Operational AmplifierDokument6 SeitenDesign of A Discrete BJT Operational Amplifierjonesy5000Noch keine Bewertungen

- BJT Amplifiers Frequency ResponseDokument29 SeitenBJT Amplifiers Frequency ResponseKrista JacksonNoch keine Bewertungen

- Unit-3 - Function Generator Using IC 8038Dokument10 SeitenUnit-3 - Function Generator Using IC 8038yp2401553Noch keine Bewertungen

- Op Amps CircuitsDokument11 SeitenOp Amps Circuitslibrian_30005821Noch keine Bewertungen

- Lab Report of Analogue ElectronicDokument13 SeitenLab Report of Analogue ElectronicKing EverestNoch keine Bewertungen

- Inverting and Non-Inverting Amplifiers: Pre-Lab QuestionsDokument13 SeitenInverting and Non-Inverting Amplifiers: Pre-Lab QuestionsBereket TsegayeNoch keine Bewertungen

- Function GeneratorDokument13 SeitenFunction GeneratorDilJalaayNoch keine Bewertungen

- Constant Current BiasDokument36 SeitenConstant Current BiasKRISHNAVINOD100% (6)

- AEC LabManualDokument30 SeitenAEC LabManualPrateek PaliwalNoch keine Bewertungen

- Chet Paynter Introduct 6 Common-Emitter Amplifiers Chapter SummaryDokument5 SeitenChet Paynter Introduct 6 Common-Emitter Amplifiers Chapter SummaryHimanshu Kumar SagarNoch keine Bewertungen

- CBCC Amp 2Dokument5 SeitenCBCC Amp 2sru_1990Noch keine Bewertungen

- 07 - Experiment Dac J09Dokument11 Seiten07 - Experiment Dac J09Beatrice ShokryNoch keine Bewertungen

- IC Applications Lab ManualDokument42 SeitenIC Applications Lab ManualRavikumar ImadabathuniNoch keine Bewertungen

- Iv - Semester, Ece List of ExperimentsDokument117 SeitenIv - Semester, Ece List of ExperimentsvibinmanualNoch keine Bewertungen

- Parameters of Op-Amp: D A C - A - D - 2019Dokument4 SeitenParameters of Op-Amp: D A C - A - D - 2019Rajesh KbNoch keine Bewertungen

- Analog Communications Lab ManualDokument60 SeitenAnalog Communications Lab ManualmailmeasddNoch keine Bewertungen

- Lab 4 - Differentiator & IntegratorDokument14 SeitenLab 4 - Differentiator & IntegratorVickneswaran KalerwananNoch keine Bewertungen

- Name of The Experiment: Study of Cascaded and Feedback Amplifier Circuits Using BJTDokument9 SeitenName of The Experiment: Study of Cascaded and Feedback Amplifier Circuits Using BJTsabitavabiNoch keine Bewertungen

- Common Emitter Amplifier: S.No Name of The Component/ Equipment Specifications QtyDokument0 SeitenCommon Emitter Amplifier: S.No Name of The Component/ Equipment Specifications Qtyagama1188Noch keine Bewertungen

- Expt 6Dokument3 SeitenExpt 6sabitavabiNoch keine Bewertungen

- Term Paper: "Analog Circuits and Linear Ic'S"Dokument17 SeitenTerm Paper: "Analog Circuits and Linear Ic'S"Deep Chand SinglaNoch keine Bewertungen

- Basic Feedback Theory: Integrated CircuitsDokument5 SeitenBasic Feedback Theory: Integrated CircuitsSourik BharNoch keine Bewertungen

- 07 Experiment 7Dokument8 Seiten07 Experiment 7RA F FANoch keine Bewertungen

- Software - Experiment 5. Frequency Response of Common Source Ac Amplifier PDFDokument5 SeitenSoftware - Experiment 5. Frequency Response of Common Source Ac Amplifier PDFSatadru DasNoch keine Bewertungen

- Basic Amplifier Circuits With Bipolar Transistors: ObjectivesDokument6 SeitenBasic Amplifier Circuits With Bipolar Transistors: ObjectivesKhalid W Al-sheakhNoch keine Bewertungen

- Metallization Process Is Used in Interconn DesiredDokument52 SeitenMetallization Process Is Used in Interconn DesiredSanjay KashiNoch keine Bewertungen

- EC Lab ManualDokument27 SeitenEC Lab ManualMohan KumarNoch keine Bewertungen

- Design Differentiator AmplifierDokument10 SeitenDesign Differentiator Amplifierhareesh.makesu0% (1)

- Audio IC Circuits Manual: Newnes Circuits Manual SeriesVon EverandAudio IC Circuits Manual: Newnes Circuits Manual SeriesBewertung: 5 von 5 Sternen5/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- 110 Integrated Circuit Projects for the Home ConstructorVon Everand110 Integrated Circuit Projects for the Home ConstructorBewertung: 4.5 von 5 Sternen4.5/5 (2)

- Ecg Heart Rate Monitor: ECG Amplifier QRS Filter QRS Detector Refra Generator Synchronous GeneratorDokument5 SeitenEcg Heart Rate Monitor: ECG Amplifier QRS Filter QRS Detector Refra Generator Synchronous GeneratorramyaarumugamNoch keine Bewertungen

- List of Experiments: Ee2207 Electronic Devices and Circuits Laboratory (Revised)Dokument55 SeitenList of Experiments: Ee2207 Electronic Devices and Circuits Laboratory (Revised)ramyaarumugamNoch keine Bewertungen

- Towards Realizable, Low-Cost Broadcast Systems For Dynamic EnvironmentsDokument10 SeitenTowards Realizable, Low-Cost Broadcast Systems For Dynamic EnvironmentsramyaarumugamNoch keine Bewertungen

- Anna Univ. Satellite SyllabusDokument1 SeiteAnna Univ. Satellite SyllabusramyaarumugamNoch keine Bewertungen

- Enge Irundhai Aaruyire - Prabha RajaratinamDokument25 SeitenEnge Irundhai Aaruyire - Prabha RajaratinamramyaarumugamNoch keine Bewertungen

- Laboratory Manual Course Code Ece254 Course Title: Unified Electronics Laboratory-IDokument67 SeitenLaboratory Manual Course Code Ece254 Course Title: Unified Electronics Laboratory-IKaran SainiNoch keine Bewertungen

- Analog Electronics Lab ManualDokument49 SeitenAnalog Electronics Lab ManualReddyvari VenugopalNoch keine Bewertungen

- Unit-V Small Signal Low Frequency Transistor Amplifier ModelsDokument40 SeitenUnit-V Small Signal Low Frequency Transistor Amplifier ModelsSivakumar PothirajNoch keine Bewertungen

- Lic QB - 2 Marks Unit I & IiDokument7 SeitenLic QB - 2 Marks Unit I & Iisanthosh sekarNoch keine Bewertungen

- EPC 3rd Sem Lab ManualDokument46 SeitenEPC 3rd Sem Lab ManualHarish G C100% (1)

- Unit 2 QuizDokument18 SeitenUnit 2 QuizkalpanadeviNoch keine Bewertungen

- BJT PDFDokument14 SeitenBJT PDFRaka Satria PradanaNoch keine Bewertungen

- California State University, Long Beach Department of Electrical Engineering EE 430 Analog Electric CircuitsDokument13 SeitenCalifornia State University, Long Beach Department of Electrical Engineering EE 430 Analog Electric CircuitsTuan VoNoch keine Bewertungen

- IES - Electronics Engineering - Analog Electronic CircuitsDokument71 SeitenIES - Electronics Engineering - Analog Electronic CircuitsVishwanath MalakarNoch keine Bewertungen

- 1.1 Ohm's Law: Unit Quantity I.EDokument53 Seiten1.1 Ohm's Law: Unit Quantity I.EMithun MahtoNoch keine Bewertungen

- Transistor Hybrid ModelDokument10 SeitenTransistor Hybrid ModelKetan SolankiNoch keine Bewertungen

- Malvino MCQ in Power AmplifiersDokument7 SeitenMalvino MCQ in Power Amplifiersআশিক পালোয়ানNoch keine Bewertungen

- ANALOG and DIGITAL ELECTRONICSDokument116 SeitenANALOG and DIGITAL ELECTRONICSPavan KumarNoch keine Bewertungen

- References: (1) Electronic Circuit Analysis and Design by Donald A. Neaman, Tata Mcgraw-HillDokument30 SeitenReferences: (1) Electronic Circuit Analysis and Design by Donald A. Neaman, Tata Mcgraw-HillPadirikuppam PavithraNoch keine Bewertungen

- Ot 2Dokument9 SeitenOt 2Eugene MartinNoch keine Bewertungen

- TL 494Dokument37 SeitenTL 494nhatnam06dt1Noch keine Bewertungen

- TransistorDokument23 SeitenTransistorXPTO_COMNoch keine Bewertungen

- ElectronicsLab - Manual March2010Dokument64 SeitenElectronicsLab - Manual March2010pnarendrareddy.mscNoch keine Bewertungen

- Basic Electronics PDFDokument43 SeitenBasic Electronics PDFakkkkNoch keine Bewertungen

- Lab QuizDokument4 SeitenLab Quizvenktesh22Noch keine Bewertungen

- Electronic Fundamentals: B) The Active ElementDokument45 SeitenElectronic Fundamentals: B) The Active ElementZbor ZborNoch keine Bewertungen

- EC-1 (2mark& 16 Mark)Dokument28 SeitenEC-1 (2mark& 16 Mark)anon_59319771Noch keine Bewertungen

- BJT AC Analysis PDFDokument64 SeitenBJT AC Analysis PDFAnonymous 1b3ih8zg9Noch keine Bewertungen

- Electric Guitar Amplifier HandbookDokument16 SeitenElectric Guitar Amplifier Handbookmaeleeisadf50% (2)

- BOYLESTAD 103pagesDokument103 SeitenBOYLESTAD 103pagesIan AmadorNoch keine Bewertungen

- q.16) Operation of Positive and Negative ClippersDokument15 Seitenq.16) Operation of Positive and Negative Clippersdharshini ravichandranNoch keine Bewertungen

- That Pair'S Darlington: Link For Animated ElectricalsDokument28 SeitenThat Pair'S Darlington: Link For Animated ElectricalsAshok KumarNoch keine Bewertungen

- Boyle StadDokument50 SeitenBoyle StadRodel MarananNoch keine Bewertungen

- Compilations of Problems in MalvinoDokument4 SeitenCompilations of Problems in MalvinosampogitoNoch keine Bewertungen

- CH-1 - BJT ModelingDokument28 SeitenCH-1 - BJT Modelingyossf 123Noch keine Bewertungen