Beruflich Dokumente

Kultur Dokumente

Ee101 DGTL 3

Hochgeladen von

PECMURUGANOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ee101 DGTL 3

Hochgeladen von

PECMURUGANCopyright:

Verfügbare Formate

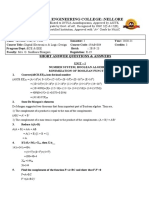

EE101: Digital circuits (Part 3)

M. B. Patil

mbpatil@ee.iitb.ac.in Department of Electrical Engineering Indian Institute of Technology Bombay

M. B. Patil, IIT Bombay

Binary numbers

Decimal (base 10) system 3 1 7 = 3 102 + 1 101 + 7 100 102 101 100

Binary numbers

Decimal (base 10) system 3 1 7 = 3 102 + 1 101 + 7 100 102 101 100

* Digits: 0,1,2,..,9 * example: 4 1 5 3

most signicant digit

least signicant digit

Binary numbers

Decimal (base 10) system 3 1 7 = 3 102 + 1 101 + 7 100 102 101 100 24

Binary (base 2) system 1 0 1 1 1 = 1 24 + 0 23 + 1 22 + 1 21 + 1 20 = 23 (in decimal) 23 22 21 20

* Digits: 0,1,2,..,9 * example: 4 1 5 3

most signicant digit

least signicant digit

Binary numbers

Decimal (base 10) system 3 1 7 = 3 102 + 1 101 + 7 100 102 101 100 24

Binary (base 2) system 1 0 1 1 1 = 1 24 + 0 23 + 1 22 + 1 21 + 1 20 = 23 (in decimal) 23 22 21 20

* Digits: 0,1,2,..,9 * Bits: 0,1 * example: 4 1 5 3 * example: 1 0 0 1 1 0 least signicant digit most signicant bit (MSB) least signicant bit (LSB)

most signicant digit

M. B. Patil, IIT Bombay

Addition of binary numbers

Decimal (base 10) system 104 103 102 101 100 weight

3 8 1 1 1 1 1 0 7 1 1 9 4 9 5 first number second number carry sum

Addition of binary numbers

Decimal (base 10) system 104 103 102 101 100 weight

3 8 1 1 1 1 1 0 7 1 1 9 4 9 5 first number second number carry sum

Binary (base 2) system 24 23

1 1 1 1 1 1

22

0 1 1 0

21

1 1

20 weight

1 0 first number (dec. 11) second number (dec. 14) carry

sum (dec. 25)

Addition of binary numbers

Decimal (base 10) system 104 103 102 101 100 weight

3 8 1 1 1 1 1 0 7 1 1 9 4 9 5 first number second number carry sum

Binary (base 2) system 24 23

1 1 1 1 1 1

22

0 1 1 0

21

1 1

20 weight

1 0 first number (dec. 11) second number (dec. 14) carry

sum (dec. 25)

* 0 + 1 = 1 + 0 = 1 S = 1, C = 0

Addition of binary numbers

Decimal (base 10) system 104 103 102 101 100 weight

3 8 1 1 1 1 1 0 7 1 1 9 4 9 5 first number second number carry sum

Binary (base 2) system 24 23

1 1 1 1 1 1

22

0 1 1 0

21

1 1

20 weight

1 0 first number (dec. 11) second number (dec. 14) carry

sum (dec. 25)

* 0 + 1 = 1 + 0 = 1 S = 1, C = 0 * 1 + 1 = 10 (dec. 2) S = 0, C = 1

Addition of binary numbers

Decimal (base 10) system 104 103 102 101 100 weight

3 8 1 1 1 1 1 0 7 1 1 9 4 9 5 first number second number carry sum

Binary (base 2) system 24 23

1 1 1 1 1 1

22

0 1 1 0

21

1 1

20 weight

1 0 first number (dec. 11) second number (dec. 14) carry

sum (dec. 25)

* 0 + 1 = 1 + 0 = 1 S = 1, C = 0 * 1 + 1 = 10 (dec. 2) S = 0, C = 1 * 1 + 1 + 1 = 11 (dec. 3) S = 1, C = 1

M. B. Patil, IIT Bombay

Addition of binary numbers

example

24

23

1 1

22

0 1 1 0

21

1 1

20 weight

1 0 first number second number carry

1 1

1 1

sum

Addition of binary numbers

example general procedure

24

23

1 1

22

0 1 1 0

21

1 1

20 weight

1 0 first number second number carry

2N AN BN

22 A2 B2 C1 S2

21 A1 B1 C0 S1

20 A0 B0

weight first number second number carry

1 1

1 1

CN CN1 SN

sum

S0

sum

Addition of binary numbers

example general procedure

24

23

1 1

22

0 1 1 0

21

1 1

20 weight

1 0 first number second number carry

2N AN BN

22 A2 B2 C1 S2

21 A1 B1 C0 S1

20 A0 B0

weight first number second number carry

1 1

1 1

CN CN1 SN

sum

S0

sum

A N BN

A FA B A FA B

A2 B2

A FA B

A1 B1

A HA B

A0 B0

CN

Co S Ci

CN1

Co S Ci

C1

Co S Ci

C0

Co S

SN

S2

S1

S0

Addition of binary numbers

example general procedure

24

23

1 1

22

0 1 1 0

21

1 1

20 weight

1 0 first number second number carry

2N AN BN

22 A2 B2 C1 S2

21 A1 B1 C0 S1

20 A0 B0

weight first number second number carry

1 1

1 1

CN CN1 SN

sum

S0

sum

A N BN

A FA B A FA B

A2 B2

A FA B

A1 B1

A HA B

A0 B0

CN

Co S Ci

CN1

Co S Ci

C1

Co S Ci

C0

Co S

SN

S2

S1

S0

* The rightmost block (corresponding to the LSB) adds two bits A0 and B0 ; there is no input carry. This block is called a half adder.

Addition of binary numbers

example general procedure

24

23

1 1

22

0 1 1 0

21

1 1

20 weight

1 0 first number second number carry

2N AN BN

22 A2 B2 C1 S2

21 A1 B1 C0 S1

20 A0 B0

weight first number second number carry

1 1

1 1

CN CN1 SN

sum

S0

sum

A N BN

A FA B A FA B

A2 B2

A FA B

A1 B1

A HA B

A0 B0

CN

Co S Ci

CN1

Co S Ci

C1

Co S Ci

C0

Co S

SN

S2

S1

S0

* The rightmost block (corresponding to the LSB) adds two bits A0 and B0 ; there is no input carry. This block is called a half adder. * Each of the subsequent blocks adds three bits (Ai , Bi , Ci 1 ) and is called a full adder.

M. B. Patil, IIT Bombay

Half adder implementation

A HA B

A0 B0

A 0 0 1

B 0 1 0 1

S 0 1 1 0

Co 0 0 0 1

C0

Co S

S0

Half adder implementation

A HA B

A0 B0

A 0 0 1

B 0 1 0 1

S 0 1 1 0

Co 0 0 0 1 Co = A B S = AB + AB = A B

C0

Co S

S0

Half adder implementation

A HA B

A0 B0

A 0 0 1

B 0 1 0 1

S 0 1 1 0

Co 0 0 0 1 Co = A B S = AB + AB = A B

C0

Co S

S0

Implementation 1

A B

AB S AB A B Co

Half adder implementation

A HA B

A0 B0

A 0 0 1

B 0 1 0 1

S 0 1 1 0

Co 0 0 0 1 Co = A B S = AB + AB = A B

C0

Co S

S0

Implementation 1

Implementation 2

A B

AB A S AB AB A B Co B S Co A+B

M. B. Patil, IIT Bombay

Full adder implementation

A FA B

Co S Ci

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

Ci 0 1 0 1 0 1 0 1

S 0 1 1 0 1 0 0 1

Co 0 0 0 1 0 1 1 1

Full adder implementation

A FA B AB Ci S: 00 01 11 10

Co S Ci

0 1

0 1

1 0

0 1

1 0

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

Ci 0 1 0 1 0 1 0 1

S 0 1 1 0 1 0 0 1

Co 0 0 0 1 0 1 1 1

S = A B Ci + A B Ci + A B Ci + A B Ci

Full adder implementation

A FA B AB Ci S: 00 01 11 10

Co S Ci

0 1

0 1

1 0

0 1

1 0

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

Ci 0 1 0 1 0 1 0 1

S 0 1 1 0 1 0 0 1

Co 0 0 0 1 0 1 1 1

S = A B Ci + A B Ci + A B Ci + A B Ci

AB Ci Co : 00 01 11 10

0 1

0 0

0 1

1 1

0 1

Co = A B + B Ci + A Ci

M. B. Patil, IIT Bombay

Implementation of functions with only NAND gates

The NOT, AND, OR operations can be realised by using only NAND gates:

Implementation of functions with only NAND gates

The NOT, AND, OR operations can be realised by using only NAND gates:

NOT

A= AA

Implementation of functions with only NAND gates

The NOT, AND, OR operations can be realised by using only NAND gates:

NOT

AND

A= AA

AB= AB

A B

AB

Implementation of functions with only NAND gates

The NOT, AND, OR operations can be realised by using only NAND gates:

NOT

AND

OR

A= AA

AB= AB

A+B =AB

A A A A B AB B A+B

M. B. Patil, IIT Bombay

Implementation of functions with only NAND gates

Implement Y = A B + B C D + A D using only NAND gates.

Implementation of functions with only NAND gates

Implement Y = A B + B C D + A D using only NAND gates.

A= AA AB =AB A+B= AB

Implementation of functions with only NAND gates

Implement Y = A B + B C D + A D using only NAND gates. Y = AB BCD AD A= AA AB =AB A+B= AB

Implementation of functions with only NAND gates

Implement Y = A B + B C D + A D using only NAND gates. Y = AB BCD AD AB A= AA AB =AB Y BCD A+B= AB

AD

Implementation of functions with only NAND gates

Implement Y = A B + B C D + A D using only NAND gates. Y = AB BCD AD AB A= AA AB =AB Y BCD A+B= AB

A B

AD

Implementation of functions with only NAND gates

Implement Y = A B + B C D + A D using only NAND gates. Y = AB BCD AD AB A= AA AB =AB Y BCD A+B= AB

A B B C D

AD

Implementation of functions with only NAND gates

Implement Y = A B + B C D + A D using only NAND gates. Y = AB BCD AD AB A= AA AB =AB Y BCD A D AD A+B= AB

A B B C D

M. B. Patil, IIT Bombay

Implementation of functions with only NAND gates

Implement Y = A + B + C using only 2-input NAND gates.

Implementation of functions with only NAND gates

Implement Y = A + B + C using only 2-input NAND gates.

A=AA AB =AB A+B =AB

Implementation of functions with only NAND gates

Implement Y = A + B + C using only 2-input NAND gates. Y = (A + B) + C = (A + B ) C

A=AA AB =AB A+B =AB

Implementation of functions with only NAND gates

Implement Y = A + B + C using only 2-input NAND gates. Y = (A + B) + C = (A + B ) C

A=AA AB =AB A+B Y C A+B =AB

Implementation of functions with only NAND gates

Implement Y = A + B + C using only 2-input NAND gates. Y = (A + B) + C = (A + B ) C

A=AA AB =AB A+B Y C C A+B =AB

Implementation of functions with only NAND gates

Implement Y = A + B + C using only 2-input NAND gates. Y = (A + B) + C = (A + B ) C = ABC A=AA AB =AB A+B Y C C A+B =AB

Implementation of functions with only NAND gates

Implement Y = A + B + C using only 2-input NAND gates. Y = (A + B) + C = (A + B ) C = ABC A=AA AB =AB A+B A+B Y C C A+B =AB

Implementation of functions with only NAND gates

Implement Y = A + B + C using only 2-input NAND gates. Y = (A + B) + C = (A + B ) C = ABC A=AA A A A+B B B A+B Y C C AB =AB A+B =AB

M. B. Patil, IIT Bombay

Implementation of functions with only NOR gates

The NOT, AND, OR operations can be realised by using only NOR gates:

Implementation of functions with only NOR gates

The NOT, AND, OR operations can be realised by using only NOR gates:

NOT

A= A+A

Implementation of functions with only NOR gates

The NOT, AND, OR operations can be realised by using only NOR gates:

NOT

AND

A= A+A

AB= A+B

A A A B AB

Implementation of functions with only NOR gates

The NOT, AND, OR operations can be realised by using only NOR gates:

NOT

AND

OR

A= A+A

AB= A+B

A+B =A+B

A A A B AB A B A+B

Implementation of functions with only NOR gates

The NOT, AND, OR operations can be realised by using only NOR gates:

NOT

AND

OR

A= A+A

AB= A+B

A+B =A+B

A A A B AB A B A+B

Implementation of functions with only NOR (or only NAND) gates is more than a theoretical curiosity. There are chips which provide a sea of gates (say, NOR gates) which can be congured by the user (through programming) to implement functions.

M. B. Patil, IIT Bombay

Implementation of functions with only NOR gates

Implement Y = A B + B C D + A D using only NOR gates.

Implementation of functions with only NOR gates

Implement Y = A B + B C D + A D using only NOR gates.

A= A+A A+B= A+B AB =A+B

Implementation of functions with only NOR gates

Implement Y = A B + B C D + A D using only NOR gates. Y = AB + BCD + AD

A= A+A A+B= A+B AB =A+B

Implementation of functions with only NOR gates

Implement Y = A B + B C D + A D using only NOR gates. Y = AB + BCD + AD

A= A+A AB A+B= A+B AB =A+B Y BCD

AD

Implementation of functions with only NOR gates

Implement Y = A B + B C D + A D using only NOR gates. Y = AB + BCD + AD = (A + B) + (B + C + D) + (A + D)

A= A+A AB A+B= A+B AB =A+B Y BCD

AD

Implementation of functions with only NOR gates

Implement Y = A B + B C D + A D using only NOR gates. Y = AB + BCD + AD = (A + B) + (B + C + D) + (A + D)

A B

A A= A+A AB A+B= A+B B AB =A+B Y BCD

AD

Implementation of functions with only NOR gates

Implement Y = A B + B C D + A D using only NOR gates. Y = AB + BCD + AD = (A + B) + (B + C + D) + (A + D)

A B

A A= A+A AB A+B= A+B B AB =A+B C BCD D

AD

Implementation of functions with only NOR gates

Implement Y = A B + B C D + A D using only NOR gates. Y = AB + BCD + AD = (A + B) + (B + C + D) + (A + D)

A B

A A= A+A AB A+B= A+B B AB =A+B C BCD D A

AD

M. B. Patil, IIT Bombay

Multiplexers

S1

I0 I1 I2 I3 S1 S0 Z

S0 0 1 0 1

Z I0 I1 I2 I3

0 0 1 1

Multiplexers

S1

I0 I1 I2 I3 S1 S0 Z

S0 0 1 0 1

Z I0 I1 I2 I3

0 0 1 1

* A multiplexer or data selector (MUX in short) selects one of the 2N input lines, i.e., it makes the ouput Z equal to one of the input lines. In other words, a MUX routes one of the input lines to the output.

Multiplexers

S1

I0 I1 I2 I3 S1 S0 Z

S0 0 1 0 1

Z I0 I1 I2 I3

I0 I1 I2 I3

SW0 SW1 SW2 SW3

0 0 1 1

S1 S0

* A multiplexer or data selector (MUX in short) selects one of the 2N input lines, i.e., it makes the ouput Z equal to one of the input lines. In other words, a MUX routes one of the input lines to the output.

Multiplexers

S1

I0 I1 I2 I3 S1 S0 Z

S0 0 1 0 1

Z I0 I1 I2 I3

I0 I1 I2 I3

SW0 SW1 SW2 SW3

0 0 1 1

S1 S0

* A multiplexer or data selector (MUX in short) selects one of the 2N input lines, i.e., it makes the ouput Z equal to one of the input lines. In other words, a MUX routes one of the input lines to the output. * Conceptually, a MUX may be thought of as 2N switches. For a given combination of the select inputs, only one of the switches closes (makes contact), and the others are open.

M. B. Patil, IIT Bombay

Multiplexers

I0

S1

I0 I1 I2 I3 S1 S0 Z

S0 0 1 0 1

Z

I1

0 0 1 1

I0 I1

I2 Z

I2 I3

I3

S1 S0

M. B. Patil, IIT Bombay

Multiplexers

I0

S1

I0 I1 I2 I3 S1 S0 Z

S0 0 1 0 1

Z

I1

0 0 1 1

I0 I1

I2 Z

I2 I3

I3

S1 S0

* A 4-to-1 MUX can be implemented as, Z = I0 S 1 S 0 + I1 S 1 S 0 + I2 S 1 S 0 + I3 S 1 S 0 . For a given combination of S1 and S0 , only one of the terms survives (the others being 0). For example, with S1 = 0, S0 = 1, we have Z = I1 .

M. B. Patil, IIT Bombay

Multiplexers

I0

S1

I0 I1 I2 I3 S1 S0 Z

S0 0 1 0 1

Z

I1

0 0 1 1

I0 I1

I2 Z

I2 I3

I3

S1 S0

* A 4-to-1 MUX can be implemented as, Z = I0 S 1 S 0 + I1 S 1 S 0 + I2 S 1 S 0 + I3 S 1 S 0 . For a given combination of S1 and S0 , only one of the terms survives (the others being 0). For example, with S1 = 0, S0 = 1, we have Z = I1 . * Multiplexers are available as ICs, e.g., 74151 is an 8-to-1 MUX.

M. B. Patil, IIT Bombay

Multiplexers

I0

S1

I0 I1 I2 I3 S1 S0 Z

S0 0 1 0 1

Z

I1

0 0 1 1

I0 I1

I2 Z

I2 I3

I3

S1 S0

* A 4-to-1 MUX can be implemented as, Z = I0 S 1 S 0 + I1 S 1 S 0 + I2 S 1 S 0 + I3 S 1 S 0 . For a given combination of S1 and S0 , only one of the terms survives (the others being 0). For example, with S1 = 0, S0 = 1, we have Z = I1 . * Multiplexers are available as ICs, e.g., 74151 is an 8-to-1 MUX. * ICs with arrays of multiplexers (and other digital blocks) are also available. These blocks can be congured (wired) by the user in a programmable manner to realise the functionality of interest.

M. B. Patil, IIT Bombay

Active high and active low inputs/outputs

S1

I0 I1 I2 I3 Z

S0 0 1 0 1

Z I0 I1 I2 I3

0 0 1 1

S1 S0

Select inputs are active high.

Active high and active low inputs/outputs

S1

I0 I1 I2 I3 Z

S0 0 1 0 1

Z I0 I1 I2 I3

0 0 1 1

S1 S0

Select inputs are active high.

S1

I0 I1 I2 I3 Z

S0 1 0 1 0

Z I0 I1 I2 I3

1 1 0 0

S1 S0

Select inputs are active low.

M. B. Patil, IIT Bombay

Enable (E) pin

inputs

outputs

inputs

outputs

E Active high enable pin.

E Active low enable pin.

M. B. Patil, IIT Bombay

Enable (E) pin

inputs

outputs

inputs

outputs

E Active high enable pin.

E Active low enable pin.

* Many digital ICs have an Enable (E) pin. If the Enable pin is active, the IC functions as desired; else, it is disabled, i.e., the outputs are set to some default values.

M. B. Patil, IIT Bombay

Enable (E) pin

inputs

outputs

inputs

outputs

E Active high enable pin.

E Active low enable pin.

* Many digital ICs have an Enable (E) pin. If the Enable pin is active, the IC functions as desired; else, it is disabled, i.e., the outputs are set to some default values. * The Enable pin can be active high or active low.

M. B. Patil, IIT Bombay

Enable (E) pin

inputs

outputs

inputs

outputs

E Active high enable pin.

E Active low enable pin.

* Many digital ICs have an Enable (E) pin. If the Enable pin is active, the IC functions as desired; else, it is disabled, i.e., the outputs are set to some default values. * The Enable pin can be active high or active low. * If the Enable pin is active low, it is denoted by Enable or E. When E = 0, the IC functions normally; else, it is disabled.

M. B. Patil, IIT Bombay

Using two 8-to-1 MUXs to make a 16-to-1 MUX

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

I0 I1 I2 I3 I4 I5 I6 I7

S3 0

74151 Z X1

S2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

S1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

S0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

0 0 0

S2 S1 S0 E X

0 0 0 0

I0 I1 I2 I3 I4 I5 I6 I7

1 1 1

74151 Z X2

1 1

S2 S1 S0 E

1 1 1

S3 S2 S1 S0

M. B. Patil, IIT Bombay

Using two 8-to-1 MUXs to make a 16-to-1 MUX

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

I0 I1 I2 I3 I4 I5 I6 I7

S3 0

74151 Z X1

S2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

S1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

S0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

0 0 0

S2 S1 S0 E X

0 0 0 0

I0 I1 I2 I3 I4 I5 I6 I7

1 1 1

74151 Z X2

1 1

S2 S1 S0 E

1 1 1

S3 S2 S1 S0

* When S 3 is 0, the upper MUX is enabled, and the lower MUX is disabled (i.e., X 2 = 0).

M. B. Patil, IIT Bombay

Using two 8-to-1 MUXs to make a 16-to-1 MUX

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

I0 I1 I2 I3 I4 I5 I6 I7

S3 0

74151 Z X1

S2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

S1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

S0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

0 0 0

S2 S1 S0 E X

0 0 0 0

I0 I1 I2 I3 I4 I5 I6 I7

1 1 1

74151 Z X2

1 1

S2 S1 S0 E

1 1 1

S3 S2 S1 S0

* When S 3 is 0, the upper MUX is enabled, and the lower MUX is disabled (i.e., X 2 = 0). * When S 3 is 1, the lower MUX is enabled, and the upper MUX is disabled (i.e., X 1 = 0).

M. B. Patil, IIT Bombay

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using a 16-to-1 MUX.

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using a 16-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0

I0 I1 I2 I3 I4 I5 I6 I7 MUX Z I8 I9 I10 I11 I12 I13 I14 I15 S3 S2 S1 S0 A B C D

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using a 16-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0

I0 I1 I2 I3 I4 I5 I6 I7 MUX Z I8 I9 I10 I11 I12 I13 I14 I15 S3 S2 S1 S0 A B C D

* When A B C D = 1, we want X = 1. A B C D = 1 A = 1, B = 0, C = 0, D = 1, i.e., the input line corresponding to 1001 (I9) gets selected. Make I9 = 1.

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using a 16-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0

1 I0 I1 I2 I3 I4 I5 I6 I7 MUX Z I8 I9 I10 I11 I12 I13 I14 I15 S3 S2 S1 S0 A B C D

* When A B C D = 1, we want X = 1. A B C D = 1 A = 1, B = 0, C = 0, D = 1, i.e., the input line corresponding to 1001 (I9) gets selected. Make I9 = 1.

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using a 16-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0

1 I0 I1 I2 I3 I4 I5 I6 I7 MUX Z I8 I9 I10 I11 I12 I13 I14 I15 S3 S2 S1 S0 A B C D

* When A B C D = 1, we want X = 1. A B C D = 1 A = 1, B = 0, C = 0, D = 1, i.e., the input line corresponding to 1001 (I9) gets selected. Make I9 = 1. * Similarly, when A B C D = 1, we want X = 1. Make I4 = 1.

X

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using a 16-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0

1 1 I0 I1 I2 I3 I4 I5 I6 I7 MUX Z I8 I9 I10 I11 I12 I13 I14 I15 S3 S2 S1 S0 A B C D

* When A B C D = 1, we want X = 1. A B C D = 1 A = 1, B = 0, C = 0, D = 1, i.e., the input line corresponding to 1001 (I9) gets selected. Make I9 = 1. * Similarly, when A B C D = 1, we want X = 1. Make I4 = 1.

X

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using a 16-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0

1 1 I0 I1 I2 I3 I4 I5 I6 I7 MUX Z I8 I9 I10 I11 I12 I13 I14 I15 S3 S2 S1 S0 A B C D

* When A B C D = 1, we want X = 1. A B C D = 1 A = 1, B = 0, C = 0, D = 1, i.e., the input line corresponding to 1001 (I9) gets selected. Make I9 = 1. * Similarly, when A B C D = 1, we want X = 1. Make I4 = 1.

X

* In all other cases, X should be 0. connect all other pins to 0.

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using a 16-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0

0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 I0 I1 I2 I3 I4 I5 I6 I7 MUX Z I8 I9 I10 I11 I12 I13 I14 I15 S3 S2 S1 S0 A B C D

* When A B C D = 1, we want X = 1. A B C D = 1 A = 1, B = 0, C = 0, D = 1, i.e., the input line corresponding to 1001 (I9) gets selected. Make I9 = 1. * Similarly, when A B C D = 1, we want X = 1. Make I4 = 1.

X

* In all other cases, X should be 0. connect all other pins to 0.

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using a 16-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

X 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0

0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 I0 I1 I2 I3 I4 I5 I6 I7 MUX Z I8 I9 I10 I11 I12 I13 I14 I15 S3 S2 S1 S0 A B C D

* When A B C D = 1, we want X = 1. A B C D = 1 A = 1, B = 0, C = 0, D = 1, i.e., the input line corresponding to 1001 (I9) gets selected. Make I9 = 1. * Similarly, when A B C D = 1, we want X = 1. Make I4 = 1.

X

* In all other cases, X should be 0. connect all other pins to 0. * In this example, since the truth table is organized in terms of ABCD , with A as the MSB and D as the LSB (the same order in which A, B , C , D are connected to the select pins), the design is simple: The expected output for 0000, 0001, 0010, etc. is applied to pins I0, I1, I2, etc., respectively.

M. B. Patil, IIT Bombay

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using an 8-to-1 MUX.

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using an 8-to-1 MUX.

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 0 0

D I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

0

D

MUX

0 0 0

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using an 8-to-1 MUX.

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 0 0

D I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

0

D

MUX

0 0 0

* When A B C = 1, i.e., A = 1, B = 0, C = 0, we have X = D . connect the input line corresponding to 100 (I4) to D .

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using an 8-to-1 MUX.

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 0 0

D I0 I1 I2 I3 D I4 I5 I6 I7 S2 S1 S0 A B C

0

D

MUX

0 0 0

* When A B C = 1, i.e., A = 1, B = 0, C = 0, we have X = D . connect the input line corresponding to 100 (I4) to D .

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using an 8-to-1 MUX.

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 0 0

D I0 I1 I2 I3 D I4 I5 I6 I7 S2 S1 S0 A B C

0

D

MUX

0 0 0

* When A B C = 1, i.e., A = 1, B = 0, C = 0, we have X = D . connect the input line corresponding to 100 (I4) to D . * When A B C = 1, i.e., A = 0, B = 1, C = 0, we have X = D . connect the input line corresponding to 010 (I2) to D .

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using an 8-to-1 MUX.

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 0 0

D D I0 I1 I2 I3 D I4 I5 I6 I7 S2 S1 S0 A B C

0

D

MUX

0 0 0

* When A B C = 1, i.e., A = 1, B = 0, C = 0, we have X = D . connect the input line corresponding to 100 (I4) to D . * When A B C = 1, i.e., A = 0, B = 1, C = 0, we have X = D . connect the input line corresponding to 010 (I2) to D .

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using an 8-to-1 MUX.

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 0 0

D D I0 I1 I2 I3 D I4 I5 I6 I7 S2 S1 S0 A B C

0

D

MUX

0 0 0

* When A B C = 1, i.e., A = 1, B = 0, C = 0, we have X = D . connect the input line corresponding to 100 (I4) to D . * When A B C = 1, i.e., A = 0, B = 1, C = 0, we have X = D . connect the input line corresponding to 010 (I2) to D . * In all other cases, X should be 0. connect all other pins to 0.

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using an 8-to-1 MUX.

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 0 0

D 0 0 D 0 D 0 0 0 I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

0

D

MUX

0 0 0

* When A B C = 1, i.e., A = 1, B = 0, C = 0, we have X = D . connect the input line corresponding to 100 (I4) to D . * When A B C = 1, i.e., A = 0, B = 1, C = 0, we have X = D . connect the input line corresponding to 010 (I2) to D . * In all other cases, X should be 0. connect all other pins to 0.

Using MUXs to implement logical functions

Implement X = A B C D + A B C D using an 8-to-1 MUX.

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 0 0

D 0 0 D 0 D 0 0 0 I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

0

D

MUX

0 0 0

* When A B C = 1, i.e., A = 1, B = 0, C = 0, we have X = D . connect the input line corresponding to 100 (I4) to D . * When A B C = 1, i.e., A = 0, B = 1, C = 0, we have X = D . connect the input line corresponding to 010 (I2) to D . * In all other cases, X should be 0. connect all other pins to 0. * Home work: Implement the same function (X ) with S 2 = B , S 1 = C , S 0 = D .

M. B. Patil, IIT Bombay

Using MUXs to implement logical functions

Implement the function X with the following truth table using an 8-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 0

Using MUXs to implement logical functions

Implement the function X with the following truth table using an 8-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 0

I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

MUX

Using MUXs to implement logical functions

Implement the function X with the following truth table using an 8-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 0

I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

MUX

Using MUXs to implement logical functions

Implement the function X with the following truth table using an 8-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 0

I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

MUX

* When ABC = 000, X = D I0 = D .

Using MUXs to implement logical functions

Implement the function X with the following truth table using an 8-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 0

D I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

MUX

* When ABC = 000, X = D I0 = D .

Using MUXs to implement logical functions

Implement the function X with the following truth table using an 8-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 1 0 1 1 1 1 0 0 0 1 1 0 1 1 0 0 0 0

D I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

MUX

* When ABC = 000, X = D I0 = D .

Using MUXs to implement logical functions

Implement the function X with the following truth table using an 8-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 1 0 1 1 1 1 0 0 0 1 1 0 1 1 0 0 0 0

D I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

MUX

* When ABC = 000, X = D I0 = D . * When ABC = 001, X = 1 I1 = 1, and so on.

Using MUXs to implement logical functions

Implement the function X with the following truth table using an 8-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 1 0 1 1 1 1 0 0 0 1 1 0 1 1 0 0 0 0

D 1 I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

MUX

* When ABC = 000, X = D I0 = D . * When ABC = 001, X = 1 I1 = 1, and so on.

Using MUXs to implement logical functions

Implement the function X with the following truth table using an 8-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 1 0 1 1 1 1 0 0 0 1

D D 1 0 D I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

MUX

1 0 1 1 0 0 0 0

1 0 0

* When ABC = 000, X = D I0 = D . * When ABC = 001, X = 1 I1 = 1, and so on.

Using MUXs to implement logical functions

Implement the function X with the following truth table using an 8-to-1 MUX.

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 1 0 1 1 1 1 0 0 0 1

D D 1 0 D I0 I1 I2 I3 I4 I5 I6 I7 S2 S1 S0 A B C

MUX

1 0 1 1 0 0 0 0

1 0 0

* When ABC = 000, X = D I0 = D . * When ABC = 001, X = 1 I1 = 1, and so on. * Home work: repeat with S2 = B , S1 = C , S0 = D .

M. B. Patil, IIT Bombay

Demultiplexers

S2 0 0 0 0 1 1 1 1

S1 0 0 1 1 0 0 1 1

S0 0 1 0 1 0 1 0 1

O0 I 0 0 0 0 0 0 0

O1 0 I 0 0 0 0 0 0

O2 0 0 I 0 0 0 0 0

O3 0 0 0 I 0 0 0 0

O4 0 0 0 0 I 0 0 0

O5 0 0 0 0 0 I 0 0

O6 0 0 0 0 0 0 I 0

O7 0 0 0 0 0 0 0 I

S2 S1 S0 I O0 O1 O2 O3 O4 O5 O6 S2 S1 S0 O7 O0 O1 O2 O3 I O4 O5 O6 O7

DEMUX

M. B. Patil, IIT Bombay

Demultiplexers

S2 0 0 0 0 1 1 1 1

S1 0 0 1 1 0 0 1 1

S0 0 1 0 1 0 1 0 1

O0 I 0 0 0 0 0 0 0

O1 0 I 0 0 0 0 0 0

O2 0 0 I 0 0 0 0 0

O3 0 0 0 I 0 0 0 0

O4 0 0 0 0 I 0 0 0

O5 0 0 0 0 0 I 0 0

O6 0 0 0 0 0 0 I 0

O7 0 0 0 0 0 0 0 I

S2 S1 S0 I O0 O1 O2 O3 O4 O5 O6 S2 S1 S0 O7 O0 O1 O2 O3 I O4 O5 O6 O7

DEMUX

* A demultiplexer takes a single input (I) and routes it to one of the output lines (O0, O1, ).

M. B. Patil, IIT Bombay

Demultiplexers

S2 0 0 0 0 1 1 1 1

S1 0 0 1 1 0 0 1 1

S0 0 1 0 1 0 1 0 1

O0 I 0 0 0 0 0 0 0

O1 0 I 0 0 0 0 0 0

O2 0 0 I 0 0 0 0 0

O3 0 0 0 I 0 0 0 0

O4 0 0 0 0 I 0 0 0

O5 0 0 0 0 0 I 0 0

O6 0 0 0 0 0 0 I 0

O7 0 0 0 0 0 0 0 I

S2 S1 S0 I O0 O1 O2 O3 O4 O5 O6 S2 S1 S0 O7 O0 O1 O2 O3 I O4 O5 O6 O7

DEMUX

* A demultiplexer takes a single input (I) and routes it to one of the output lines (O0, O1, ). * For N Select inputs (S0, S1, ), the number of output lines is 2N .

M. B. Patil, IIT Bombay

Demultiplexers

S2 0 0 0 0 1 1 1 1

S1 0 0 1 1 0 0 1 1

S0 0 1 0 1 0 1 0 1

O0 I 0 0 0 0 0 0 0

O1 0 I 0 0 0 0 0 0

O2 0 0 I 0 0 0 0 0

O3 0 0 0 I 0 0 0 0

O4 0 0 0 0 I 0 0 0

O5 0 0 0 0 0 I 0 0

O6 0 0 0 0 0 0 I 0

O7 0 0 0 0 0 0 0 I

S2 S1 S0 I O0 O1 O2 O3 O4 O5 O6 S2 S1 S0 O7 O0 O1 O2 O3 I O4 O5 O6 O7

DEMUX

* A demultiplexer takes a single input (I) and routes it to one of the output lines (O0, O1, ). * For N Select inputs (S0, S1, ), the number of output lines is 2N . * Conceptually, a DEMUX can be thought of as 2N switches. For a given combination of the Select inputs, only one of the switches is closed, all others being open.

M. B. Patil, IIT Bombay

Demultiplexer: gate-level diagram

O0

O1

O0 O1 O2 I

O2

O3

DEMUX

O3 O4 O5 O6 O5 O4

S2 S1 S0 O7 O6

O7

S2 S1 S0

M. B. Patil, IIT Bombay

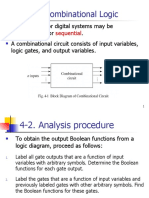

Decoders

A0 A1

N inputs

O0 O1

Decoder

M outputs

AN-1

OM-1

M. B. Patil, IIT Bombay

Decoders

A0 A1

N inputs

O0 O1

Decoder

M outputs

AN-1

OM-1

* For each input combination, only one output line is active (which means 0 or 1, depending on whether the outputs are active low or active high).

M. B. Patil, IIT Bombay

Decoders

A0 A1

N inputs

O0 O1

Decoder

M outputs

AN-1

OM-1

* For each input combination, only one output line is active (which means 0 or 1, depending on whether the outputs are active low or active high). * Since there are 2N input combinations, there could be 2N output lines, i.e., M = 2N . However, there are decoders with M < 2N as well.

M. B. Patil, IIT Bombay

3-to-8 decoder (1-of-8 decoder)

A2

O0 O1 A0 A1 Decoder A2 O2 O3 O4 O5 O6 O7

A1 0 0 1 1 0 0 1 1

A0 0 1 0 1 0 1 0 1

O0 1 0 0 0 0 0 0 0

O1 0 1 0 0 0 0 0 0

O2 0 0 1 0 0 0 0 0

O3 0 0 0 1 0 0 0 0

O4 0 0 0 0 1 0 0 0

O5 0 0 0 0 0 1 0 0

O6 0 0 0 0 0 0 1 0

O7 0 0 0 0 0 0 0 1

0 0 0 0 1 1 1 1

M. B. Patil, IIT Bombay

BCD-to-decimal decoder

A3 0 0 0 O0 O1 A0 A1 A2 A3

7442

A2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

A1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

A0 Active output 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 O0 O1 O2 O3 O4 O5 O6 O7 O8 O9

none none none none none none

0 0 0 0 0 1 1 1 1 1 1 1 1

O2 O3 O4 O5 O6 O7 O8 O9

M. B. Patil, IIT Bombay

BCD-to-decimal decoder

A3 0 0 0 O0 O1 A0 A1 A2 A3

7442

A2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

A1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

A0 Active output 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 O0 O1 O2 O3 O4 O5 O6 O7 O8 O9

none none none none none none

0 0 0 0 0 1 1 1 1 1 1 1 1

O2 O3 O4 O5 O6 O7 O8 O9

* Note that the combinations A3 A2 A1 A0 = 1010 onwards are dont care conditions since a BCD (binary coded decimal) number is expected to be less than 1010 (i.e., decimal 10).

M. B. Patil, IIT Bombay

BCD-to-7 segment decoder

VCC

a

a

MSB D C 7446 B A LSB

common anode

b c d e f g

e g c f b

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

M. B. Patil, IIT Bombay

BCD-to-7 segment decoder

VCC

a

a

MSB D C 7446 B A LSB

common anode

b c d e f g

e g c f b

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

* The resistors serve to limit the diode current. For VCC = 5 V , VD = 2 V , and ID = 10 mA, R = 300 .

M. B. Patil, IIT Bombay

BCD-to-7 segment decoder

VCC

a

a

MSB D C 7446 B A LSB

common anode

b c d e f g

e g c f b

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

* The resistors serve to limit the diode current. For VCC = 5 V , VD = 2 V , and ID = 10 mA, R = 300 . * Home work: Write the truth table for c (in terms of D , C , B , A). Obtain a minimized expression for c using a K map.

M. B. Patil, IIT Bombay

Encoders

A0 A1

M inputs

O0 O1

Encoder

N outputs

AM-1

ON-1

M. B. Patil, IIT Bombay

Encoders

A0 A1

M inputs

O0 O1

Encoder

N outputs

AM-1

ON-1

* Only one input line is assumed to be active. The (unique) binary number corresponding to the active input line appears at the output pins.

M. B. Patil, IIT Bombay

Encoders

A0 A1

M inputs

O0 O1

Encoder

N outputs

AM-1

ON-1

* Only one input line is assumed to be active. The (unique) binary number corresponding to the active input line appears at the output pins. * The N output lines can represent 2N binary numbers, each corresponding to one of the M input lines, i.e., we can have M = 2N . Some encoders have M < 2N .

M. B. Patil, IIT Bombay

Encoders

A0 A1

M inputs

O0 O1

Encoder

N outputs

AM-1

ON-1

* Only one input line is assumed to be active. The (unique) binary number corresponding to the active input line appears at the output pins. * The N output lines can represent 2N binary numbers, each corresponding to one of the M input lines, i.e., we can have M = 2N . Some encoders have M < 2N . * As an example, for N = 3, we can have a maximum of 23 = 8 input lines.

M. B. Patil, IIT Bombay

Encoders

8to3 encoder example

A0 A1 A2 A3 A4 A5 A6 A7

A0 1 0 0

O0

A1 0 1 0 0 0 0 0 0

A2 0 0 1 0 0 0 0 0

A3 0 0 0 1 0 0 0 0

A4 0 0 0 0 1 0 0 0

A5 0 0 0 0 0 1 0 0

A6 0 0 0 0 0 0 1 0

A7 0 0 0 0 0 0 0 1

O2 0 0 0 0 1 1 1 1

O1 0 0 1 1 0 0 1 1

O0 0 1 0 1 0 1 0 1

Encoder

O1 O2

0 0 0 0 0

M. B. Patil, IIT Bombay

Encoders

8to3 encoder example

A0 A1 A2 A3 A4 A5 A6 A7

A0 1 0 0

O0

A1 0 1 0 0 0 0 0 0

A2 0 0 1 0 0 0 0 0

A3 0 0 0 1 0 0 0 0

A4 0 0 0 0 1 0 0 0

A5 0 0 0 0 0 1 0 0

A6 0 0 0 0 0 0 1 0

A7 0 0 0 0 0 0 0 1

O2 0 0 0 0 1 1 1 1

O1 0 0 1 1 0 0 1 1

O0 0 1 0 1 0 1 0 1

Encoder

O1 O2

0 0 0 0 0

* Note that only one of the input lines is assumed to be active.

M. B. Patil, IIT Bombay

Encoders

8to3 encoder example

A0 A1 A2 A3 A4 A5 A6 A7

A0 1 0 0

O0

A1 0 1 0 0 0 0 0 0

A2 0 0 1 0 0 0 0 0

A3 0 0 0 1 0 0 0 0

A4 0 0 0 0 1 0 0 0

A5 0 0 0 0 0 1 0 0

A6 0 0 0 0 0 0 1 0

A7 0 0 0 0 0 0 0 1

O2 0 0 0 0 1 1 1 1

O1 0 0 1 1 0 0 1 1

O0 0 1 0 1 0 1 0 1

Encoder

O1 O2

0 0 0 0 0

* Note that only one of the input lines is assumed to be active. * What if two input lines become simultaneously active? There are priority encoders which assign a priority to each of the input lines.

M. B. Patil, IIT Bombay

74147 decimal-to-BCD priority encoder

A1 1 A1 A2 A3 A4 A5 A6 A7 A8 A9

74147

A2 1 X X X X X X X 0 1

A3 1 X X X X X X 0 1 1

A4 1 X X X X X 0 1 1 1

A5 1 X X X X 0 1 1 1 1

A6 1 X X X 0 1 1 1 1 1

A7 1 X X 0 1 1 1 1 1 1

A8 1 X 0 1 1 1 1 1 1 1

A9 1 0 1 1 1 1 1 1 1 1

O3 1 0 0 1 1 1 1 1 1 1

O2 1 1 1 0 0 0 0 1 1 1

O1 1 1 1 0 0 1 1 0 0 1

O0 1 0 1 0 1 0 1 0 1 0

X X O0 O1 O2 O3 X X X X X X 0

M. B. Patil, IIT Bombay

74147 decimal-to-BCD priority encoder

A1 1 A1 A2 A3 A4 A5 A6 A7 A8 A9

74147

A2 1 X X X X X X X 0 1

A3 1 X X X X X X 0 1 1

A4 1 X X X X X 0 1 1 1

A5 1 X X X X 0 1 1 1 1

A6 1 X X X 0 1 1 1 1 1

A7 1 X X 0 1 1 1 1 1 1

A8 1 X 0 1 1 1 1 1 1 1

A9 1 0 1 1 1 1 1 1 1 1

O3 1 0 0 1 1 1 1 1 1 1

O2 1 1 1 0 0 0 0 1 1 1

O1 1 1 1 0 0 1 1 0 0 1

O0 1 0 1 0 1 0 1 0 1 0

X X O0 O1 O2 O3 X X X X X X 0

* Note that the higher input lines get priority over the lower ones. For example, A7 gets priority over A1 , A2 , A3 , A4 , A5 , A6 . If A7 is active (low), the binary output is 1000 (i.e., 0111 inverted bit-by-bit) which corresponds to decimal 7, irrespective of A1 , A2 , A3 , A4 , A5 , A6 .

M. B. Patil, IIT Bombay

74147 decimal-to-BCD priority encoder

A1 1 A1 A2 A3 A4 A5 A6 A7 A8 A9

74147

A2 1 X X X X X X X 0 1

A3 1 X X X X X X 0 1 1

A4 1 X X X X X 0 1 1 1

A5 1 X X X X 0 1 1 1 1

A6 1 X X X 0 1 1 1 1 1

A7 1 X X 0 1 1 1 1 1 1

A8 1 X 0 1 1 1 1 1 1 1

A9 1 0 1 1 1 1 1 1 1 1

O3 1 0 0 1 1 1 1 1 1 1

O2 1 1 1 0 0 0 0 1 1 1

O1 1 1 1 0 0 1 1 0 0 1

O0 1 0 1 0 1 0 1 0 1 0

X X O0 O1 O2 O3 X X X X X X 0

* Note that the higher input lines get priority over the lower ones. For example, A7 gets priority over A1 , A2 , A3 , A4 , A5 , A6 . If A7 is active (low), the binary output is 1000 (i.e., 0111 inverted bit-by-bit) which corresponds to decimal 7, irrespective of A1 , A2 , A3 , A4 , A5 , A6 . * The lower input lines are therefore shown as dont care (X) conditions.

M. B. Patil, IIT Bombay

Das könnte Ihnen auch gefallen

- Digital Electronics For Engineering and Diploma CoursesVon EverandDigital Electronics For Engineering and Diploma CoursesNoch keine Bewertungen

- Ee101 DGTL 3Dokument123 SeitenEe101 DGTL 3Shubham MittalNoch keine Bewertungen

- Arth CirDokument105 SeitenArth Cirnoor_dcetNoch keine Bewertungen

- Chapter 04Dokument33 SeitenChapter 04Iqbal Ashfaq Joiya100% (1)

- Computer ArithmaticDokument21 SeitenComputer Arithmaticmanishbhardwaj8131Noch keine Bewertungen

- l2 Combi LogicDokument27 Seitenl2 Combi LogicPECMURUGANNoch keine Bewertungen

- Comb CircDokument63 SeitenComb Circm.sangeethjaNoch keine Bewertungen

- Lect2 ExerciseDokument12 SeitenLect2 ExerciserasromeoNoch keine Bewertungen

- C++ Bitwise OperatorsDokument19 SeitenC++ Bitwise OperatorsÄbûýé SêñdèkúNoch keine Bewertungen

- Tutorial 7 SolutionsDokument6 SeitenTutorial 7 Solutionssama abd elgelilNoch keine Bewertungen

- Courses in Electrical Engineering: Digital Electronics Chapter Three: Boolean AlgebraDokument14 SeitenCourses in Electrical Engineering: Digital Electronics Chapter Three: Boolean AlgebraNGOUNENoch keine Bewertungen

- Number Arithmetic p2Dokument8 SeitenNumber Arithmetic p2manishbhardwaj8131Noch keine Bewertungen

- Badass Tutorial Unit 6 Adders SubtractorsDokument23 SeitenBadass Tutorial Unit 6 Adders SubtractorsdjpsychoscientzNoch keine Bewertungen

- Unit 2Dokument38 SeitenUnit 2toshgangwarNoch keine Bewertungen

- Digital Electronics: Answer: D Explanation: The Expression For Associative Property Is Given by A+ (B+C) (A+B) +C &Dokument51 SeitenDigital Electronics: Answer: D Explanation: The Expression For Associative Property Is Given by A+ (B+C) (A+B) +C &Rajesh KumarNoch keine Bewertungen

- Cominational and Sequential CircuitsDokument28 SeitenCominational and Sequential CircuitsKennedy MutaiNoch keine Bewertungen

- Computer Architecture 3rd Edition by Moris ManoCh 10Dokument21 SeitenComputer Architecture 3rd Edition by Moris ManoCh 10Sadaf RasheedNoch keine Bewertungen

- Simplification of Boolean Functions: Example 1Dokument15 SeitenSimplification of Boolean Functions: Example 1Sudharsanam BollineniNoch keine Bewertungen

- PLCDokument25 SeitenPLCsrgroups118Noch keine Bewertungen

- 1 - Bit ALUDokument13 Seiten1 - Bit ALUSouvik BasuNoch keine Bewertungen

- 02 SubtractorsDokument21 Seiten02 SubtractorsSarita AninditaNoch keine Bewertungen

- Exam 1 Study Questions: Chapters 1-7, 9 of Nelson's TextDokument6 SeitenExam 1 Study Questions: Chapters 1-7, 9 of Nelson's TextNUrul Aqilah MusNoch keine Bewertungen

- DELD - Short Answer Questions and AnswersDokument23 SeitenDELD - Short Answer Questions and AnswersPasupuleti Venkata RamanaNoch keine Bewertungen

- CT 02 Syllabus and Assignment OneDokument2 SeitenCT 02 Syllabus and Assignment OneImran EmuNoch keine Bewertungen

- 17-CAT-II Key G2 Slot-26-Aug-2019Material - I - 26-Aug-2019 - CAT2-G2 - AK - 2019 - LIJDokument4 Seiten17-CAT-II Key G2 Slot-26-Aug-2019Material - I - 26-Aug-2019 - CAT2-G2 - AK - 2019 - LIJAhmed Shmels MuheNoch keine Bewertungen

- DE LAB MANUAL Finalised PDFDokument55 SeitenDE LAB MANUAL Finalised PDFOmkar MutalikNoch keine Bewertungen

- Unit2 CADokument34 SeitenUnit2 CAIT HOD Nandha College of TechnologyNoch keine Bewertungen

- Courses in Electrical Engineering: Digital Electronics Chapter Six: Combinatory LogicDokument29 SeitenCourses in Electrical Engineering: Digital Electronics Chapter Six: Combinatory LogicNGOUNENoch keine Bewertungen

- Unit 04 English Sentence To Boolean EquationsDokument30 SeitenUnit 04 English Sentence To Boolean EquationsJhill-Jhill Jimenez Dela PeñaNoch keine Bewertungen

- Practice Problems - 1: Department of Electrical EngineeringDokument2 SeitenPractice Problems - 1: Department of Electrical EngineeringMalay Kumar MohantaNoch keine Bewertungen

- 05-The Processor (To Be Updated) Final TermDokument54 Seiten05-The Processor (To Be Updated) Final TermAnsar HasasNoch keine Bewertungen

- Bcd-Adder 1Dokument21 SeitenBcd-Adder 1PriyankaNoch keine Bewertungen

- Combinational Logic Circuits - PPTDokument36 SeitenCombinational Logic Circuits - PPTAllanki Sanyasi RaoNoch keine Bewertungen

- SRM University: Department of CseDokument47 SeitenSRM University: Department of CseShreyas NagareNoch keine Bewertungen

- 04 Gates BooleanDokument10 Seiten04 Gates BooleansaranNoch keine Bewertungen

- Combinational CircuitsDokument68 SeitenCombinational Circuitsavita207Noch keine Bewertungen

- QuestionsDokument9 SeitenQuestionsCristian MihaiNoch keine Bewertungen

- Rajagiri School of Engineering and Technology: Rajagiri Valley, Kakkanad. Third SemesterDokument37 SeitenRajagiri School of Engineering and Technology: Rajagiri Valley, Kakkanad. Third SemesterAmrita VenkitaramaniNoch keine Bewertungen

- Ee101 DGTL 1Dokument152 SeitenEe101 DGTL 1PECMURUGANNoch keine Bewertungen

- Convert Gray Code 101011 Into Its Binary Equivalent. Gray Code: 1 0 1 0 1 1 Binary Code: 1 1 0 0 1 0Dokument23 SeitenConvert Gray Code 101011 Into Its Binary Equivalent. Gray Code: 1 0 1 0 1 1 Binary Code: 1 1 0 0 1 0khadarbasha.n nNoch keine Bewertungen

- Topic 12 AddersDokument18 SeitenTopic 12 AddersTalal KhaliqNoch keine Bewertungen

- (CSM51A / EE16 S10) Solutions For Midterm: Problem Points Score 1 15 2 10 3 20 4 20 5 15 6 20 Total 100Dokument10 Seiten(CSM51A / EE16 S10) Solutions For Midterm: Problem Points Score 1 15 2 10 3 20 4 20 5 15 6 20 Total 100krazykrnxboyNoch keine Bewertungen

- Cs6211 - Digital Lab ManualDokument105 SeitenCs6211 - Digital Lab Manualvcetkathir100% (2)

- CEA201 CH11-DigitalLogicDokument24 SeitenCEA201 CH11-DigitalLogicTTNoch keine Bewertungen

- Dayalbagh Educational Institute: Experiment 1-To Implement Half Adder by Using Basic and UniversalDokument41 SeitenDayalbagh Educational Institute: Experiment 1-To Implement Half Adder by Using Basic and UniversalKhushi GuptaNoch keine Bewertungen

- EE1D11 Instr w4 Quiz1Dokument20 SeitenEE1D11 Instr w4 Quiz1Isa SpolerNoch keine Bewertungen

- B38DB ClassExs2sDokument33 SeitenB38DB ClassExs2sNabil IshamNoch keine Bewertungen

- Question Bank - DSD 2nd SemDokument2 SeitenQuestion Bank - DSD 2nd Semmirajb004Noch keine Bewertungen

- Notes 1Dokument76 SeitenNotes 1rainatkmNoch keine Bewertungen

- ClassXI Hy2021 Comp - Sc.Dokument6 SeitenClassXI Hy2021 Comp - Sc.subhraNoch keine Bewertungen

- BCA T 113 Digital Electronics Question BankDokument9 SeitenBCA T 113 Digital Electronics Question BankAhana MalhotraNoch keine Bewertungen

- Logicenglish Newlast PDFDokument16 SeitenLogicenglish Newlast PDFvinuNoch keine Bewertungen

- Digital TutotrialsDokument29 SeitenDigital Tutotrialsrktiwary256034Noch keine Bewertungen

- Mod 1 2Dokument20 SeitenMod 1 2Naseef RahmanNoch keine Bewertungen

- DPSD Lab ManualDokument108 SeitenDPSD Lab ManualAmudha Palanisamy100% (3)

- Boolean Expression SimplificationDokument8 SeitenBoolean Expression SimplificationOcsicnarf Oredenet OidotsucNoch keine Bewertungen

- Chapt 4Dokument72 SeitenChapt 4jannngirNoch keine Bewertungen

- Developing The Half Adder and Full AdderDokument14 SeitenDeveloping The Half Adder and Full AdderFaisal KhanNoch keine Bewertungen

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxVon EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxBewertung: 4 von 5 Sternen4/5 (2)

- Combinational Circuit Analysis and DesignDokument25 SeitenCombinational Circuit Analysis and DesignPECMURUGANNoch keine Bewertungen

- Digital Signal Processing: b, where (a, b) can be (t t x πDokument5 SeitenDigital Signal Processing: b, where (a, b) can be (t t x πSugan MohanNoch keine Bewertungen

- Syllabus: Department of Computer Science & Engineering Lab Manual Digital Lab Class: 2 Yr, 3 SemDokument104 SeitenSyllabus: Department of Computer Science & Engineering Lab Manual Digital Lab Class: 2 Yr, 3 SemPECMURUGANNoch keine Bewertungen

- PLDsDokument25 SeitenPLDsPECMURUGAN100% (1)

- Combinational Logic Design ProcessDokument21 SeitenCombinational Logic Design ProcessILikeScribd5050Noch keine Bewertungen

- Digital Signal ProcessingDokument271 SeitenDigital Signal ProcessingPECMURUGAN100% (3)

- Combinational Logic1-1Dokument9 SeitenCombinational Logic1-1PECMURUGANNoch keine Bewertungen

- EE101: Digital Circuits (Part 2) : M. B. PatilDokument68 SeitenEE101: Digital Circuits (Part 2) : M. B. PatilSenthil KumarNoch keine Bewertungen

- 2-Mod2 CP Impact 2013Dokument317 Seiten2-Mod2 CP Impact 2013PECMURUGANNoch keine Bewertungen

- 7 Segment LedDokument27 Seiten7 Segment LedNikhil BhatiNoch keine Bewertungen

- CSE 2 2013R Anna UniversityDokument11 SeitenCSE 2 2013R Anna UniversityBaskyNoch keine Bewertungen

- Instructions and RequirementsDokument4 SeitenInstructions and RequirementsPECMURUGANNoch keine Bewertungen

- GE 2151 BEEE Question Paper Nov Dec 2011Dokument3 SeitenGE 2151 BEEE Question Paper Nov Dec 2011PECMURUGANNoch keine Bewertungen

- Lec 03 ZCZCDokument26 SeitenLec 03 ZCZCPECMURUGANNoch keine Bewertungen

- EE101: Digital Circuits (Part 2) : M. B. PatilDokument68 SeitenEE101: Digital Circuits (Part 2) : M. B. PatilSenthil KumarNoch keine Bewertungen

- Chapter 04Dokument40 SeitenChapter 04瘋橋夜泊Noch keine Bewertungen

- Ee101 DGTL 5Dokument150 SeitenEe101 DGTL 5Shreeroop AjaykumarNoch keine Bewertungen

- GE 2151 BEEE Question Paper Nov Dec 2011Dokument3 SeitenGE 2151 BEEE Question Paper Nov Dec 2011PECMURUGANNoch keine Bewertungen

- KmapDokument38 SeitenKmapPECMURUGANNoch keine Bewertungen

- Ee101 DGTL 1Dokument152 SeitenEe101 DGTL 1PECMURUGANNoch keine Bewertungen

- 06668967Dokument10 Seiten06668967PECMURUGANNoch keine Bewertungen

- Ee101 DGTL 4Dokument116 SeitenEe101 DGTL 4PECMURUGANNoch keine Bewertungen

- K MappingDokument28 SeitenK MappingVikrant BhaskarNoch keine Bewertungen

- Unit 8: Precast ConcreteDokument27 SeitenUnit 8: Precast ConcreteRemya R. KumarNoch keine Bewertungen

- Totally Precast Concrete Bridges: ForwardDokument27 SeitenTotally Precast Concrete Bridges: ForwardPECMURUGANNoch keine Bewertungen

- Concreet Tecnologey 7-9-2008Dokument23 SeitenConcreet Tecnologey 7-9-2008PECMURUGANNoch keine Bewertungen

- Aasr 2012 3 5 2837 2846Dokument10 SeitenAasr 2012 3 5 2837 2846PECMURUGANNoch keine Bewertungen

- Precast ConcreteDokument20 SeitenPrecast ConcreteMuhammadTareqRasyadJamallulailNoch keine Bewertungen

- Cambridge English Proficiency Writing Answer Sheet: Test Form SEX Date of Birth Your NameDokument8 SeitenCambridge English Proficiency Writing Answer Sheet: Test Form SEX Date of Birth Your NameΕυάγγελος ΚάσσοςNoch keine Bewertungen

- Exercises695Clus Solution - Doc Exercises695Clus SolutionDokument7 SeitenExercises695Clus Solution - Doc Exercises695Clus SolutionMaster IdNoch keine Bewertungen

- Math+1110 BookaDokument104 SeitenMath+1110 Bookabalvinder singhNoch keine Bewertungen

- Seat Heat Retrofit From Sep98aDokument10 SeitenSeat Heat Retrofit From Sep98aChirica RemusNoch keine Bewertungen

- 6201 OVP Alarm # Ericsson Alarm Script Alarm MeansDokument5 Seiten6201 OVP Alarm # Ericsson Alarm Script Alarm MeansMaicl PuriciNoch keine Bewertungen

- A New Hendecagonal Fuzzy Number For Optimization ProblemsDokument7 SeitenA New Hendecagonal Fuzzy Number For Optimization ProblemsEditor IJTSRDNoch keine Bewertungen

- Civil Guruji EstimationDokument122 SeitenCivil Guruji EstimationEshwar Prasad100% (2)

- Directive Low VoltageDokument137 SeitenDirective Low Voltageximeres0% (1)

- Refraction Assignment - C.R, R.D & A.DDokument4 SeitenRefraction Assignment - C.R, R.D & A.DSanjay SrinivasanNoch keine Bewertungen

- ISO27k ISMS 6.1 SoA 2022Dokument5 SeitenISO27k ISMS 6.1 SoA 2022Natália Gomes KnobNoch keine Bewertungen

- CENTURY Series: REX-C100 REX-C400 REX-C410 REX-C700 REX-C900Dokument4 SeitenCENTURY Series: REX-C100 REX-C400 REX-C410 REX-C700 REX-C900Marco TàiNoch keine Bewertungen

- JIS 8801 - JapanDokument25 SeitenJIS 8801 - JapanannccknarimeNoch keine Bewertungen

- Ioqm 1 23Dokument5 SeitenIoqm 1 23Shakir MommandNoch keine Bewertungen

- Arithmetic Progression Icse Grade 10Dokument73 SeitenArithmetic Progression Icse Grade 10manishi_2005Noch keine Bewertungen

- DWM LAb Manual FinalDokument43 SeitenDWM LAb Manual FinalDevyani PatilNoch keine Bewertungen

- Difference Calculus and Generating Functions. Santos, D. A. 2005Dokument34 SeitenDifference Calculus and Generating Functions. Santos, D. A. 2005José Daniel Rivera Medina100% (1)

- MM200 Instruction Manual - GEK-113400CDokument78 SeitenMM200 Instruction Manual - GEK-113400Cshijub_001Noch keine Bewertungen

- 001 R0 STK Substructure Design AMH To Be SentDokument91 Seiten001 R0 STK Substructure Design AMH To Be SentThulasi Raman KowsiganNoch keine Bewertungen

- Judicial AffidavitDokument224 SeitenJudicial Affidavitclandestine2684Noch keine Bewertungen

- C 1 2013 Engineering GraphicsDokument38 SeitenC 1 2013 Engineering GraphicsIrina GheorgheNoch keine Bewertungen

- Eastern Nigeria Shallow Water Metocean 2.1Dokument320 SeitenEastern Nigeria Shallow Water Metocean 2.1Osas AsemotaNoch keine Bewertungen

- Volume 2. Nomor 2. Juli Volume 2. Nomor 2. Juli - Desember 2014Dokument17 SeitenVolume 2. Nomor 2. Juli Volume 2. Nomor 2. Juli - Desember 2014Christin AgapeNoch keine Bewertungen

- Fluid Flow in An Asymmetric ChannelDokument20 SeitenFluid Flow in An Asymmetric ChannelMuhammad NabeelNoch keine Bewertungen

- MAA 2.8 EXPONENTS SolutionsDokument5 SeitenMAA 2.8 EXPONENTS SolutionsMuborakNoch keine Bewertungen

- Slab Design - OkDokument35 SeitenSlab Design - OkazwanNoch keine Bewertungen

- Programming VHDLDokument39 SeitenProgramming VHDLsscetrajivNoch keine Bewertungen

- Perhitungan DPT 4-7 MDokument38 SeitenPerhitungan DPT 4-7 MD WNoch keine Bewertungen

- (Mai 1.2-1.3) Exponents - Systems of Linear Equations - SolutionsDokument3 Seiten(Mai 1.2-1.3) Exponents - Systems of Linear Equations - SolutionsJuhi KastiyaNoch keine Bewertungen

- AGMA 2015 915-1-A02Dokument108 SeitenAGMA 2015 915-1-A02danielk32100% (1)

- Daftar Shift Kasir 2022Dokument75 SeitenDaftar Shift Kasir 2022orbita kasirNoch keine Bewertungen