Beruflich Dokumente

Kultur Dokumente

DC (Bias) Circuit: Common-Source Amplifier Stage

Hochgeladen von

alokesh1982Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

DC (Bias) Circuit: Common-Source Amplifier Stage

Hochgeladen von

alokesh1982Copyright:

Verfügbare Formate

Common-Source Amplifier

Stage

Two types of common-source amplifiers will

be investigated in lab projects. One is with the source grounded and the other is with

a current-source bias (dual power supply). In Units 5. and 5.! we discuss various

aspects of the common-source stage with grounded source" in Unit 5.# we ta$e up

circuit-linearity considerations" and in Unit 5.% we cover the basics of the dual-power-

supply amplifier. &oth amplifiers are based on the '(O)" as in the projects. *he first

two units are mostly a review of the basic amplifier as presented in previous units" to

reinforce the basic concepts. *he '(O) replaces the +(O) (Units ! and %) in this unit"

to provide familiarity with the opposite polarity in bias considerations and to illustrate

that the linear model applies in the same manner for both transistor types.

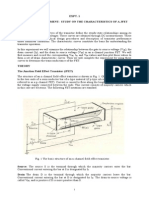

DC (Bias) Circuit

,c circuits for the grounded-source amplifier are shown in -ig. 5. ('(O)). *he circuit

in (a) is based on a single power supply" and the gate bias is obtained with a resistor

voltage-divider networ$. *he circuit in (b) is for a laboratory project

amplifier. &oth .

//

and .

))

are negative" since the source is at ground. *here is

no voltage drop across 0

/

since there is negligible gate current. 0

/

is necessary

only to prevent shorting the input signal" .

i

. *he bias current I

,

for a given

applied .

)/

will respond according to (#.1)" which is

I

,

$

p

(.

)/

.

tpo

)

!

( +

p

.

),

)

.

0

Fig. 5.1 &asic '(O) common- source

amplifiers. )ingle-power- supply

amplifier (a) and laboratory

0

/ !

.

i

.

//

0

/

.

i

amplifier (b) with .

)/

( .

//

) and

.

.

))

controlled by ,23 output

o

o

channels. +ote that either end of

the circuit of (a) can be at ground.

0

/

,

0

,

(a)

.

))

.

))

(b)

*he two circuits are e4uivalent" as

.

//

and 0

/

of -ig. 5..b are the *h5venin

e4uivalent of the bias networ$ of the -ig. 5.(a). In the project on the amplifier" they

are actually a voltage and a resistor. *his is not a bias-stable circuit" as a

slight change in .

)/

or the transistor parameters can result in a significant

change in I

,

. *he dual-power-supply circuit of Unit 5.% is considerably better in this

respect.

Amplifier Voltage Gain

*his dc (bias) circuit becomes an amplifier now simply by adding a signal source at the

gate as in -ig. 5.!. *his re4uires a coupling capacitor" as shown here in the complete

circuit" to prevent disturbing the bias upon connecting the input signal to the circuit.

In the amplifier of 'roject 5" the signal will be superimposed on the bias

voltage at the node of .

//

. *his can be facilitated with 6ab.I78 and the ,23. 2

capacitor" as in an actual amplifier" is therefore not re4uired. *he re4uirement for

having 6ab.I78 control over both .

//

and .

))

" and the limitation of two output

channels" dictates this configuration.

In 'roject 5 we measure the gain as a function of bias current" I

,

. -or a )'I97

comparison" we need an e:pression for the gain. -or the ideal case" which

neglects the output conductance" g

ds

" the output current is related to the input voltage

by (%.)" which is

I

d

g

m

.

gs

g

m

.

i

9

.

.

.

//

Fig. 5.2 2 signal source is connected to the

gate through a coupling capacitor. *he

capacitor is necessary to isolate the dc

circuit from the signal source.

0

/

.

s

+

.

i

g

o

0

,

*he output signal voltage is" in general"

.

))

.

ds

.

o

I

d

0

, (5.)

.

gs

-

+

i

0

/

0

,

.

o

g

m

.

gs

Fig. 5. )ignal-e4uivalent version of the

amplifier stage. ,c nodes are set to ;ero volts

(circuit reference). *he reactance of 9

g

is

assumed to be ;ero.

*he convention used here for subscript order for signal (linear) variables is common to

the +(O) and '(O). *his is consistent with the fact that the linear model does not

distinguish between the two types. *hus" for e:ample" the dc terminal voltage for a

'(O) is .

)/

" but the signal e4uivalent is .

gs

(-ig. 5.#) and the signal input voltage is

positive at the input terminal (common-source" gate input). -or the '(O)" i

,

is defined

as positive out of the drain" but the signal

output current is into the drain (as in the +(O)). 8e note that a positive

( .

gs

.

sg

) corresponds to a decrease in the total gate source voltage"

which is consistent with a decrease of i

,

and positive I

d

.

.

gs

v

)/

"

,

v

.

p

*hus" the negative sign in (5.) is consistent with the flow of current I

d

up

through the resistor (-ig. 5.#) for positive .

i

.

gs

. *he common-source stage is an

inverting amplifier and has an inherent 1<

o

phase shift. -rom (%.) and (5.)" the

gain is

.

o

a

(5.!)

g

m

0

,

i

where both .

i

.

gs

and .

o

.

ds

are with respect to ground or the source terminal for the

common-source stage.

If the output resistance" = g

ds

" cannot be neglected (which is the case for the

project on '(O) amplifiers)" the transistor current" g

m

.

i

" is shared between the output

resistance and 0

,

. *he portion that flows through 0

,

is (-ig. 5.%)

I g .

(5.#)

0

,

m i

+ g

ds

0

,

+ote again that the signal schematic transistor represents a current source with

value g

m

.

i

" as established in connection with -ig. %.. *he additional feature of

the transistor model is included with the addition of =g

ds

. *his resistance is

actually part of the transistor and is between the drain and source of the transistor" but

the circuit as given is e4uivalent" as the source is at ground. )ince

the output voltage is .

o

I

0

0

,

" the new gain result is

a g

0

,

(5.%)

v m

+ g

sd

0

,

+ote that this form evolves from ideal transistor current" g

m

.

gs

" flowing through the

parallel combination of the output resistance and 0

,

.

*o facilitate an intuitive grasp of the magnitude o f the effect of g

ds

" we use the

e:pression for g

ds

(%.#) in (5.%)" to obtain

a g

0

,

(5.5)

v m

+ I

,

0

,

+ote that

I

,

0

,

is the voltage drop across 0

,

. -or e:ample" for a <-. power

supply" we choose I

,

0

,

5 . . 2 measurement of

p

for our devices will show that

.

p

= !< ." which results in

p

I

,

0

,

= %. *hus" the effect of

case is significant.

g

ds

(

p

I

,

) for this

.

i

g

m

.

i

Fig. 5.! 9ommon-source amplifier stage

signal circuit" with all dc nodes set to ;ero

volts. *he transistor model includes

0

/ .

o output resistance =g

ds

" which appears

0

,

= g

ds

directly in parallel with 0

,

with the source

grounded.

-inally" we can get an overall current dependence for a

v

of g

m

" using (%.5) with $

p

$

p

" which results in

with the elimination

a ! $ I

0

,

(5.>)

v p ,

+

p

I

,

0

,

Using an alternative form for g

m

( !I

,

= .

effp

) " also (%.5)" the gain e:pression is

I 0

a !

, ,

(5.?)

v

effp

+

p

I

,

0

,

where

I

,

.

I

,

effp

$

p

( +

p

.

),

) $

p

-or simplicity" appro:imate forms of (%.5) and (%.#) of g

m

and g

ds

are used here"

which are independent of .

),

. -or reference" the @e:actA and appro:imate forms of (%.5)

and (%.#)" respectively" are repeated hereB

g

m

! $

p

( +

p

.

),

)I

,

! $

p

I

,

and

!

gs

g

I

,

ds p

+

p

.

),

p

I

,

*he @e:actA e4uations of g

m

and g

ds

are used in conjunction with the amplifier

projects to compare the computed gain with the measured gain plotted against

I

,

. *his is done in both 6ab.I78 and (athcad. 'arameters $

p

and .

tpo

(to get

.

effp

) will be e:tracted from the measured dc data" and

p will be used as an

adjustable parameter to fit the )'I97 an d measured gain data.

5.# 6inearity of the /ain of the 9ommon-)ource

2mplifier

*he connection between I

d

and .

gs

is linear provided that .

gs

is small enough" as

considered in the following units. Use of the linear relations also assumes that the

output signal remains in the active region (i.e." neither in the linear region nor near

cutoff). *his is discussed below. +(O) subscripts are used. *he results are the same

for the '(O)" with a @ p A subscript substituted for @ n A and the subscript order

reversed for all bias -voltage variables.

5.#. +onlinearity 0eferred to the Input

*he general e4uation again is (#.1)

i

,

$

n

(v

/)

.

tno

)

*hen using

I

d

i

,

I

,

and v

/)

.

/)

+ .

gs

" the e4uation for the incremental drain

current becomes

I $

!

(

.

.

)

. + .

!

1

(5.1)

d n

/) tno gs gs

]

which leads to a nonlinear (variable) transconductance" g

m

" given by

$

(

! . .

+

.

!

)

. _

I

g

d

n effn gs gs

g

(5.C)

m

. .

m

!.

gs gs

effn

,

*herefore" the condition for linearity is that .

gs

<< !.

eff

" with .

effn

.

/)

.

tno

5 Unit 5.# 6inearity of the /ain of the 9ommon -)ource

2mplifier

n

and using g

m

!$ .

effn

.

8ith this condition not satisfied" an output signal is distorted. Dowever" for

the purpose of measuring the amplifier gain" our signal voltmeter will ta$e the

average of the positive and negative pea$s" which is

$ (! . .

+

.

!

)+

$ (! . .

.

!

)

I

davg

eff gs gs n

!

eff gs gs

(5.<)

In the parabolic relationship" the s4uared terms cancel entirely. In general"

though" the output signal contains harmonic content (distortion) when

large compared to .

effn

.

5.#.! +onlinearity 0eferred to the Output

.

gs

is too

*he discussion above of limits imposed on

.

gs

assumes that the transistor

remains in the active mode. *o clarify this point" reference is made to the output

characteristics of -ig. 5.5. *he graph has plots of the output characteristic for

three values of v

/)

in addition to the load line. *he characteristic plot in the

midrange is for no signal. Operating point variables are .

,)

!.5 . and

I

,

%< 2 . 8ith a large" positive .

gs

" the characteristic moves up to the high -level

plot ( i

,hi

) and the opposite occurs for a large but negative .

gs

( i

,lo

). *he high-

level plot is shown for when the transistor is about to move out of the active

region and into the linear region. 2ttempts to force v

,)

to lower values will

create considerable distortion in the output signal voltage. *he lower curve suggests that

the positive output signal is on the verge of being cut off (clipped) for an additional

increase in the negative -input signal voltage.

2ccording to the discussion above" the negative signal output voltage is

limited to

.

dsminus

.

,)

.

effn

(5.)

*echnically"

.

effn

is from the high-current signal state" but for simplicity" a

reasonable estimate can be made from the dc caseE that is" .

effn

.

/)

.

tno

. *he

positive signal limit is

.

dsplus .

,,

.

,)

I

,

0

,

(5.!

,

i

,

(2)

v

effn

i

,hi

i

,lo

I

,

.

,)

v

,)

(.)

Fig. 5.5 9ommon-source amplifier stage output characteristics. Output

characteristics are from top to bottom" large high-current signal swing" i

,hi

" dc

bias" I

,

" low-current signal swing" i

,lo

. 2lso shown is the load line. *he current

voltage circuit solution is always the intersection between a given

characteristic and the load line.

*he actual output-signal limit is dictated by the smaller of the two for a

symmetrical periodic signal such as a sine-wave. In the e:ample shown in -ig.

5.5" .

effn

<.5 ." .

,)

!.5 . " and .

,,

5 .. *he plus and minus signal-voltage

limits are about !.5 . and !.< ." respectively. ,epending on the dc bias" the limit could

be dictated by one or the other. In the amplifier projects" the gain will typically be

measured over a range of dc bias current for a fi:ed resistor. *his means that for the low-

current end of the scan" the signal will be limited by the

magnitude of I

,

0

,

and" by design" the plus and minus swings will be made to be

about e4ual at the highest dc current.

,istortion associated with the nonlinear I

d .

gs

relation and that due to

signal limits at the output may be ta$ing place simultaneously. *his is seen from the gain

e:pression (5.?) (g

ds

<)

.

0

a

v

!

.

effp

where a

v

.

ds

= .

gs

and where the appro:imation is for the case of neglecting the

n

factor. *hus" for a given

.

ds

" .

gs

is

5# Unit 5.% 9urrent-)ource 9ommon-)ource 2mplifierB 9ommon-)ource 2mplifier with a )ource

0esistor

,

. !.

.

gs

.

effp

!.

0

,

.

ds

(5.#)

If" for e:ample"

.

ds

is pushed to the positive output-signal limit" then .

ds

.

0

.

2ccording to (5.#)" .

gs

.

effp

= !" and

.

gs

relation as given in (5.C)"

.

gs

e:ceeds the condition for a linear I

d

g

I

d

.

gs

_

g

gs

m

t

effn

,

5.% 9urrent-)ource 9ommon-)ource 2mplifierB

9ommon-)ource 2mplifier with a )ource 0esistor

*he bias circuit of the current-source bias amplifier" shown in -ig. 5.>" has a dual power

supply. One advantage of this is that the input is at ;ero dc volts such that the signal can

be connected directly without interfering with the bias. *he dc circuit e4uation for setting

up the bias is

.

,,

.

)/

I

,

0

(5.%)

)

where ($

p

$

p

) .

)/

I

,

= $

p

+ .

tp

.

*his circuit is more bias stable than the grounded source amplifier" as slight

changes in .

)/

(due to device parameter variations or temperature) are usually

small compared to .

,,

. +ote that .

tp

is used in lieu of .

tpo

as .

&)

<. *he chip

(9,%<<?) used in the projects is a p-well device (as noted in Unit #)" with the +(O)

transistors in the well. *he well is connected to .

))

" while the body of the chip is

connected" as in -ig. 5.>" to .

,,

. *he pn junction formed by the well and

the bul$ is thus reverse-biased with a voltage .

))

+ .

,,

.

In the amplifier projects" however" we have the latitude to connect the body and

source as there is only one transistor in the circuit and the body can float

along with the source. *hus we can assume that .

tp

.

tpo

. 2s shown in -ig. 5.?"

the signal circuit re4uires the addition of a bypass capacitor"

9

s

. *his places the

source at signal ground provided that the capacitor is large enough. *he criterion

0

for this is discussed in Unit >. *he voltage-gain e4uation is the same as in the

amplifier" with the source actually grounded.

.

,,

Fig. 5." ,c circuit of the dual-power-

supply common-source amplifier. *he gate

is at ground potential" allowing the

signal to be connected directly to

+

.

)/

0

/

0

)

.

,,

the gate. 0

/

is necessary only to prevent

shorting out the input signal.

.

,

0

,

.

))

8ithout the bypass capacitor" 0

)

is in the signal circuit and a fraction of the

applied signal voltage at the gate is dropped across the resistor. *he signal circuit for this

case is shown in -ig. 5.1. *he circuit transconductance of the amplifier

with 0

)

was discussed initially in Unit %. *his is reviewed in the following.

.

,,

Fig. 5.# 2mplifier circuit with a

bypass capacitor attached between the

source and ground to tie the source to

signal ground. )ignal input is attached

directly to the gate. &ody and source are

connected internally in the project chip for

the transistor used in the amplifier.

0

)

9

s

.

i

.

g

+

.

o

/

0

,

.

))

2n applied input signal" .

i

.

g

" divides between the gate source terminals and

the source resistor according to F(%.>)G

.

g

.

gs

+ I

d

0

)

55 Unit 5.5 ,esign of a &asic 9ommo n-)ource 2mplifier

+

m

v

.

g m )

0

)

Fig. 5.$ )ignal circuit for dual-power supply

common-source amplifier. Input signal

voltage" .

i

" is divided between .

gs

" the

control voltage" and the source resistor

according to the ratio B g

m

0

)

.

.

i

.

g

.

gs

-

+

0

/

.

o

0

,

8hen combing this with I

d

g

m

.

gs

" we obtain F(%.?)G

I

.

g

.

gs

+ g

m

.

gs

0

)

(

+ g

m

0

)

)

.

gs

(

+ g

m

0

)

)

d

g

m

*he circuit transconductance" /

m

" is then F(%.1)G

I

d

g

m

/

.

g

+ g

m

0

)

*he gain for this case is thus (neglecting

g

ds

)

.

d

a / 0

g

m

0

,

(5.5)

m ,

+ g 0

In one of the amplifier projects"

capacitor is actually less than unity.

0

)

0

,

" and the gain without the bypass

5.5 ,esign of a &asic 9ommon-)ource 2mplifier

Unli$e in the laboratory environment" an actual practical common-source amplifier

would have a single power supply for the base and collector circuit bias. 2lso" the

circuit design re4uires a tolerance to a wide range of parameter

.

.

/

variation" including that due to temperature change. In this unit" the design process for a

possible common-source amplifier is discussed. 7mphasis is on dc bias stability" that is"

on tolerance to device parameter and circuit component variations.

*he common-source amplifier to be designed is shown in -ig. 5.C. )ource

resistor" 0

)

" is included for bias (and gain) stabili;ation. *he goal is for the circuit

to function properly for any +(O) transistor" which has device parameters $

n

and .

tno

that fall into a wide range of values" as is normally e:pected. *olerance to

component variation" such as resistor values" could also be built into the design.

.

,,

Fig. 5.% +(O) common-source amplifier with

0

)

for bias and gain stabili;ation. /ate bias is

provided by a voltage-divider networ$

consisting of 0

/

and 0

/!

. *he body

i

and source terminals are connected.

0

/

0

,

9

g

o

9

s

0

/ !

0

)

/ate voltage .

/

is provided by the voltage divider" consisting of resistors 0

/

and 0

/!

. )ince there is no gate current" the gate bias voltage is F(.!)G

0

/ !

.

0

/ !

+ 0

/

.

,,

.oltage .

/

is thus relatively stable and can be considered constant. Once .

/

has

been established" the drain current will be dictated by

.

/

.

/)

I

,

0

(5.>)

)

)ince the gate source voltage is given by

$

$

I

.

/)

I

,

+

n

.

tno

(5.?)

the drain current" I

,

" may be e:pressed in terms of the device parameters as

.

/

I

,

I

,

.

n

0

)

tno

(5.1)

*his result reveals the dependence of I

,

on the magnitudes of $

n

and .

tno

.

(2gain" for simplicity" as in the amplifier projects" we will assume that the body and

source are connected such that .

tn

.

tno

.)

&ias current I

,

is assumed to be a given. *he initial design then is conducted

for the +(O) nominal" average values for $

n

and .

tno

. 2ny combination of .

/

and 0

)

that satisfies (5.1) will provide the design I

,

. )pecific values for .

/

and

0

)

will be dictated by stability re4uirements. )uppose that $

n

is e:pected to fall

within $

no

t $

n

and .

tno

within .

tnoo

t .

tno

" where $

no

and .

tnoo

are the nominal

values of the original design. 2ssume that the design bias current associated with $

no

and

.

tnoo

is I

,o

. 2t the e:tremes for the parameters" the low and high currents will be

I

. . t .

/

,

(

tnoo tno

)

I

,lo ",hi

$

no

$

n

0

(5.C)

)

0esistor 0

)

" for the given .

/

and design drain current" is

.

/

.

/)o

0

)

,o

(5.!<)

.

/)o is obtained from (5.?)" using the nominal parameter values. *he low and

high current limits tend to converge on .

/

= 0

)

as .

/

becomes large. *hat is" in the

limit" .

/

dominates the voltages in the numerator of (5.C)" thus rendering the

e:pression insensitive to the minor contributions from changes in $

n

and .

tno

.

2n important design consideration is drain source voltage"

dictates the output signal range. *his is calculated from

.

,)

" as this

0

.

,)

.

,,

I

,

(0

,

+ 0

)

)

(5.!)

In the design of the amplifier" drain resistor 0

,

is normally selected for e4ual positive

and negative pea$-signal ma:imums. *his configuration is illustrated in -ig. 5.<" which

shows the output characteristic of the transistor in the circuit.

*he signal is limited by . . and . . . at the high and low ends

,, 0

)

effno /)o tno

of the voltage range" respectively. *herefore" nominal bias should be set at

.

,)o

.

,,

I

,o

0

)

+.

effno

!

(5.!!)

-or simplicity" it is assumed that v

effn

.

effno

. .

effno

" .

,,o

" and

I

,o

are the bias

values at the nominal parameter values. *he bias drain voltage is .

,)o

drop across 0

)

" that is"

plus the

.

,o

.

,)o

+ I

,o

0

) (5.!#)

Hnowing .

,o

then provides for the calculation of 0

,

from

.

,,

.

,o

0

,

I

(5.!%)

,o

where .

,o

and I

,o

are for the initial design with

$

no

and .

tnoo

.

2n optimi;ation design se4uence plots the limits for a range of .

/

and for

specified .

tno

and $

n

. 2n e:ample is shown in -ig. 5.. *he plot of .

,)o

corresponds to the nominal $

no

and .

tnoo

. *he curve slopes downward as I

,

0

)

increases for increasing .

/

at constant nominal bias current" I

,o

. .

,)hi

is for the

combination of .

tno

and $

n

" which gives the ma:imum positive deviation from

the nominal" and

.

,)lo

is the opposite. *he e:ample of -ig. 5. is for .

,,

< .

and design bias current of I

,o

<< 2

and nominal parameters $

no

!

#<< 2 = .

!

"

.

tnoo

.5 ." .

tno

<. . " and $

n

<< 2 = . . 7:perience with the 9(O) chip of

our amplifier project ('roject ?) indicates that these are representative.

-igure 5.! shows plots of the computed positive and negative signal-pea$

limits. ,ue to the increasing .

)

with increasing .

/

" the signal range decreases" as

shown by the plots. *hus" the signal-pea$ limits have a ma:imum" as is evident

in the graph. *he design of the amplifier uses .

/

at the ma:imum of the lower

0

, )

/

0

0 + 0

curve. *he value of

.

/

is consistent with the ma:imum .

,)lo

in the plot of -ig.

5.. In the e:ample" .

/

# ..

v

effn

i

,

(2)

i

,

i

,sig

I

,

.

,)

i

0 +0

v

,)

(.)

.

,,

I

,

0

)

Fig. 5.1& Output characteristic of the transistor of the amplifier with

bias .

,)

set appro:imately according to (5.!!). *he signal is restricted

within the range

. . and appro:imately v . *he characteristic

,, 0

)

effn

curves are for no signal (solid plot) and for the signal at a ma:imum (dashed

plot)" as limited by the transistor going into the inactive (linear) region. *he

load lines are dc (solid line) and signal (ac" dashed line).

Once .

/

is determined" the selection of 0

/

is made from (.!)" which is

0

/ !

. .

0

/

0

/!

+

,,

/

0

/

.

,,

where 0

/

is the parallel combination

0

/ !

0

/

0

/

/! /

0

/

can be selected somewhat arbitrarily but could be dictated by the coupling

capacitor" 9

g

" re4uirement. 2ssociated with the coupling capacitor is the

fre4uency (>.!)" which is

# - d&

/ no tnoo tno

0

) m

f

#d&

!0

/

9

g

.

,)hi

.

,)o

.

,)lo

.

/

Fig. 5.11 9omputed high and low range of .

,)

as a function of gate-bias

voltage . . *he computation is with $ #<< 2= .

!

" . .5 ." . <. ."

and $

n

<< 2= .

!

.

0

/!

is then calculated from

0

/

0

/

0

/!

/

0

/

*he gain e4uations for the circuit of -ig. 5.C" with and without a bypass capacitor" are

(5.!) and (5.5)" respectively. *hese are

a

v

g

m

0

,

and

g

m

0

,

a

v

+ g 0

In the design procedure outlined in this unit" emphasis is on stability and the gain

falls out. *his would typically be the case for this type of amplifier. 8e note

that due to the characteristically small g

m

of (O)-7*s" the voltage gain is

relatively small. /ain can be improved considerably through the use a current- source

load" as in the amplifier of Unit <.

.

dplus

.

dplus

.

dm in us

.

d min us

.

/

Fig. 5.12 9omputed ma:imums for negative and positive output voltage signal

pea$s as a function of .

/

B .

dplus

" positive ma:imumE .

dminus

" negative

ma:imum.

a

v

g

m

0

,

9ommon-source amplifier-stage voltage gain.

a g

0

,

p , ,

9ommon-source amplifier gain including

output resistance" '(O). ()ame for +(O)

with

n

.)

.

gs

+onlinear transconductance for large input

signals. ()ame for '(O) with .

effp

.)

effn

.

dsminus

.

,)

.

effn

+egative output signal limit" +(O).

.

dsminus

.

),

.

effp

+egative output signal limit" '(O).

.

dsplus

.

,,

.

,)

I

,

0

,

'ositive output signal limit" +(O).

.

dsplus

.

))

.

),

I

,

0

,

'ositive output signal limit" '(O).

a

g

m

0

,

m )

.oltage gain of common-source stage with

source resistor.

/

g

m

m )

9ircuit transresistance of common-source stage

with source resistor.

5.> )ummary of 74uations

v m

+ I 0

g

m

g

m

t

!.

v

+ g 0

m

+ g 0

5.? 7:ercises and 'rojects

'roje c t ( ath c ad - il es 7:ercise<5.mcd - 'roject<5.mcd

'a(orator) *ro+ect 5 '(O) 9ommon-)ource 2mplifier

'5.! '(O) 9ommon-)ource 2mplifier ,9 )etup

'5.# 2mplifier /ain at One &ias 9urrent

'5.% 2mplifier /ain versus &ias 9urrent

Das könnte Ihnen auch gefallen

- STEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10Von EverandSTEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10Noch keine Bewertungen

- Planning For Project Layout ReportDokument11 SeitenPlanning For Project Layout ReportAko C Rence100% (2)

- Triode Emulator by Dimitri DanyukDokument8 SeitenTriode Emulator by Dimitri Danyukt_ca100% (2)

- Analog Communications Lab ManualDokument60 SeitenAnalog Communications Lab ManualmailmeasddNoch keine Bewertungen

- Graphic Symbols According To DIN ISO 1219-1 (Extract) : Symbol MeaningDokument4 SeitenGraphic Symbols According To DIN ISO 1219-1 (Extract) : Symbol MeaningZubin PatelNoch keine Bewertungen

- SHS Core - Earth and Life Science CGDokument13 SeitenSHS Core - Earth and Life Science CGShendy AcostaNoch keine Bewertungen

- Design and Implementation of Multiple Output Switch Mode Power SupplyDokument6 SeitenDesign and Implementation of Multiple Output Switch Mode Power SupplyseventhsensegroupNoch keine Bewertungen

- Manual Partes Torre Iluminacion Chicago CPLT - M10 PDFDokument56 SeitenManual Partes Torre Iluminacion Chicago CPLT - M10 PDFromaldoagurto0% (1)

- Electronics Sample Lab ReportDokument10 SeitenElectronics Sample Lab ReportLeo Marcelo VillalbaNoch keine Bewertungen

- Innovation in ConstructionDokument165 SeitenInnovation in Constructionfoush bashaNoch keine Bewertungen

- Easy(er) Electrical Principles for General Class Ham License (2015-2019)Von EverandEasy(er) Electrical Principles for General Class Ham License (2015-2019)Bewertung: 5 von 5 Sternen5/5 (1)

- Long Report 7Dokument6 SeitenLong Report 7Ahmad Najmi100% (1)

- Presentation GrihaDokument60 SeitenPresentation GrihaTimila Dangol100% (1)

- Heat TransferDokument382 SeitenHeat TransferManish Chouhan100% (1)

- Function GeneratorDokument13 SeitenFunction GeneratorDilJalaayNoch keine Bewertungen

- Name of The Simulation:: Pin 1 (Offset Null)Dokument10 SeitenName of The Simulation:: Pin 1 (Offset Null)sabitavabiNoch keine Bewertungen

- Vbe Multiplier - Lab5 - AppendixDokument15 SeitenVbe Multiplier - Lab5 - AppendixSidney O. EbotNoch keine Bewertungen

- Electronics Engineering Pre-Board 1Dokument12 SeitenElectronics Engineering Pre-Board 1Rennel MallariNoch keine Bewertungen

- 211-5OperationalAmplifiers 05Dokument10 Seiten211-5OperationalAmplifiers 05Kumar ReadarNoch keine Bewertungen

- P07 LabNotesPt2 and Interference LabDokument37 SeitenP07 LabNotesPt2 and Interference Labcliffhanger107Noch keine Bewertungen

- Expt. 3 EEE 214 Name of The Experiment: Op-Amp As An Ampliifier ObjectiveDokument3 SeitenExpt. 3 EEE 214 Name of The Experiment: Op-Amp As An Ampliifier ObjectivesabitavabiNoch keine Bewertungen

- KKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKDokument21 SeitenKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKDeepal PrasankaNoch keine Bewertungen

- 6LABO Ganago Student Lab7Dokument27 Seiten6LABO Ganago Student Lab7Rocio Deidamia Puppi HerreraNoch keine Bewertungen

- Designing A Class A Power Amplifier Using The Load-Pull MethodDokument15 SeitenDesigning A Class A Power Amplifier Using The Load-Pull MethodNguyen Duc TaiNoch keine Bewertungen

- 3.3 FET AmplifierDokument5 Seiten3.3 FET Amplifierlizhi0007100% (1)

- Name of The Experiment: Study of Cascaded and Feedback Amplifier Circuits Using BJTDokument9 SeitenName of The Experiment: Study of Cascaded and Feedback Amplifier Circuits Using BJTsabitavabiNoch keine Bewertungen

- Chapter 5: Diode Circuits: Section 5.5Dokument22 SeitenChapter 5: Diode Circuits: Section 5.5dhwanikaNoch keine Bewertungen

- Simulationof Single Phase Full Bridge Converter Using PSPICEDokument10 SeitenSimulationof Single Phase Full Bridge Converter Using PSPICEDhivya NNoch keine Bewertungen

- Ee240 hw1 Sol 1509Dokument10 SeitenEe240 hw1 Sol 1509AMSA84Noch keine Bewertungen

- 01004017Dokument4 Seiten01004017pepe890305Noch keine Bewertungen

- Circuit Diagram: F FIG.9.2 F F (HZ)Dokument44 SeitenCircuit Diagram: F FIG.9.2 F F (HZ)ramyaarumugamNoch keine Bewertungen

- Electronic Applications Test 7 Page 1 / 17 1.: A. 6 B. 2 C. 4 D. 5 E. 8Dokument17 SeitenElectronic Applications Test 7 Page 1 / 17 1.: A. 6 B. 2 C. 4 D. 5 E. 8YudhaAprilianNoch keine Bewertungen

- Fast Power FlowDokument23 SeitenFast Power FlowKornepati SureshNoch keine Bewertungen

- Experiment 20: Ohm's Law: PurposeDokument4 SeitenExperiment 20: Ohm's Law: PurposeChris AngNoch keine Bewertungen

- Name of The Experiment: Mathematical Operations Using Op-Amp ObjectiveDokument2 SeitenName of The Experiment: Mathematical Operations Using Op-Amp ObjectivesabitavabiNoch keine Bewertungen

- Diodes and Their ApplicationsDokument3 SeitenDiodes and Their ApplicationsAlex Turriza SuárezNoch keine Bewertungen

- Series Lof Oh LinesDokument17 SeitenSeries Lof Oh LinesChristopher StanleyNoch keine Bewertungen

- The Operational Amplifier and Applications.: Chapter IiiaDokument30 SeitenThe Operational Amplifier and Applications.: Chapter IiiavnkrishNoch keine Bewertungen

- Phy3802L: Intermediate Lab: Iel.1 Summing (Inverting) AmplifierDokument4 SeitenPhy3802L: Intermediate Lab: Iel.1 Summing (Inverting) Amplifiernainesh goteNoch keine Bewertungen

- The Two Diode Bipolar Junction Transistor ModelDokument3 SeitenThe Two Diode Bipolar Junction Transistor ModelAlbertoNoch keine Bewertungen

- Lecture 21: Junction Field Effect Transistors. Source Follower AmplifierDokument8 SeitenLecture 21: Junction Field Effect Transistors. Source Follower AmplifiercasprossNoch keine Bewertungen

- Eee214 1Dokument4 SeitenEee214 1sabitavabiNoch keine Bewertungen

- Apostila - Matemática Computacional - Adérito Araújo - Univ. de Coimbra, PortugalDokument29 SeitenApostila - Matemática Computacional - Adérito Araújo - Univ. de Coimbra, PortugalAntonio PortelaNoch keine Bewertungen

- Objective: Design A Practical Integrator Circuit Using Common OP AMP Circuits. TestDokument10 SeitenObjective: Design A Practical Integrator Circuit Using Common OP AMP Circuits. TestVinoth KumarNoch keine Bewertungen

- Classical ModelDokument27 SeitenClassical ModelDrVikas Singh BhadoriaNoch keine Bewertungen

- Bel Paper No 2Dokument21 SeitenBel Paper No 2Gaurav KumarNoch keine Bewertungen

- Fractal Ant1Dokument6 SeitenFractal Ant1atharvawazurkarNoch keine Bewertungen

- A New Approach Transformer Ground Differential: FOR ProtectionDokument15 SeitenA New Approach Transformer Ground Differential: FOR ProtectionproteccionesNoch keine Bewertungen

- Symmetrical Components v2Dokument32 SeitenSymmetrical Components v2Carlos RodriguezNoch keine Bewertungen

- Expt09 - D-C Power SupplyDokument2 SeitenExpt09 - D-C Power Supplypopmop2Noch keine Bewertungen

- HW 12 CDokument6 SeitenHW 12 CaperlahkoNoch keine Bewertungen

- Subject NotesDokument13 SeitenSubject NotesMary HelenNoch keine Bewertungen

- Harmonic Model For The Fluorescent LampDokument7 SeitenHarmonic Model For The Fluorescent Lampwilliamb285Noch keine Bewertungen

- EEE 4308L Electronics I Laboratory Laboratory #1 Operational Amplifier-Based IntegratorsDokument19 SeitenEEE 4308L Electronics I Laboratory Laboratory #1 Operational Amplifier-Based IntegratorsnoneNoch keine Bewertungen

- G6 PDFDokument9 SeitenG6 PDFJagadish KgNoch keine Bewertungen

- chp5 1Dokument6 Seitenchp5 1Harshith GowdaNoch keine Bewertungen

- Industrial ElectronicsDokument22 SeitenIndustrial ElectronicsMark RaboyNoch keine Bewertungen

- Symmetrical ComponentsDokument32 SeitenSymmetrical ComponentsReza SiavoshiNoch keine Bewertungen

- Methodologies To Determine Fhe Fault Current Through An OPGW (Optical Ground Wire)Dokument6 SeitenMethodologies To Determine Fhe Fault Current Through An OPGW (Optical Ground Wire)mrjack1100% (2)

- View A Transformer's Hysteresis Curve With An Ultra-Simple CircuitDokument2 SeitenView A Transformer's Hysteresis Curve With An Ultra-Simple Circuitagmnm1962100% (1)

- ECE 250 Lab 6 Temperature Sensor Subsystem Design: VI.A. Pre-Lab Design and System OperationDokument7 SeitenECE 250 Lab 6 Temperature Sensor Subsystem Design: VI.A. Pre-Lab Design and System OperationHerless FloresNoch keine Bewertungen

- Op-Amp Comparator: Astable (Or Free-Running) Multivibrators Monostable MultivibratorsDokument5 SeitenOp-Amp Comparator: Astable (Or Free-Running) Multivibrators Monostable MultivibratorsYuvaraj ShanNoch keine Bewertungen

- Problems: and LowardDokument5 SeitenProblems: and LowardPedro FilhoNoch keine Bewertungen

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesVon EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNoch keine Bewertungen

- Influence of System Parameters Using Fuse Protection of Regenerative DC DrivesVon EverandInfluence of System Parameters Using Fuse Protection of Regenerative DC DrivesNoch keine Bewertungen

- Quantum DerivesDokument1 SeiteQuantum Derivesalokesh1982Noch keine Bewertungen

- SuperconductorsDokument1 SeiteSuperconductorsalokesh1982Noch keine Bewertungen

- Wave Particle DualityDokument1 SeiteWave Particle Dualityalokesh1982Noch keine Bewertungen

- History of Quantum PhysicsDokument1 SeiteHistory of Quantum Physicsalokesh1982Noch keine Bewertungen

- Frequency: Is Considered The Father of The Quantum TheoryDokument1 SeiteFrequency: Is Considered The Father of The Quantum Theoryalokesh1982Noch keine Bewertungen

- Region of Convergence Example 2: Inverse Z-TransformDokument1 SeiteRegion of Convergence Example 2: Inverse Z-Transformalokesh1982Noch keine Bewertungen

- Quantum Mechanics (QM Also Known As Quantum Physics or Quantum Theory), IncludingDokument1 SeiteQuantum Mechanics (QM Also Known As Quantum Physics or Quantum Theory), Includingalokesh1982Noch keine Bewertungen

- Rabindranath TagoreDokument1 SeiteRabindranath Tagorealokesh1982Noch keine Bewertungen

- History of Z TransformDokument1 SeiteHistory of Z Transformalokesh1982Noch keine Bewertungen

- Passband Modulation: Modulation From Wikipedia, The Free Encyclopedia For Other Uses, SeeDokument3 SeitenPassband Modulation: Modulation From Wikipedia, The Free Encyclopedia For Other Uses, Seealokesh1982Noch keine Bewertungen

- Silicon, (Si) :the Most Common Semiconductor, Atomic Number 14Dokument1 SeiteSilicon, (Si) :the Most Common Semiconductor, Atomic Number 14alokesh1982Noch keine Bewertungen

- OpticalDokument2 SeitenOpticalalokesh1982Noch keine Bewertungen

- Optical Intravalley Scattering: Harrison56Dokument1 SeiteOptical Intravalley Scattering: Harrison56alokesh1982Noch keine Bewertungen

- 3.3.2 Ionized Impurity Scattering: Brooks51Dokument1 Seite3.3.2 Ionized Impurity Scattering: Brooks51alokesh1982Noch keine Bewertungen

- One DimensionalDokument1 SeiteOne Dimensionalalokesh1982Noch keine Bewertungen

- Magnets: Antiferromagnet. Magnetite (FeDokument1 SeiteMagnets: Antiferromagnet. Magnetite (Fealokesh1982Noch keine Bewertungen

- Multi Potential ScatteringDokument1 SeiteMulti Potential Scatteringalokesh1982Noch keine Bewertungen

- Intervalley Phonon Scattering: Harrison56 Conwell67Dokument1 SeiteIntervalley Phonon Scattering: Harrison56 Conwell67alokesh1982Noch keine Bewertungen

- Acoustic Intravalley Scattering at Low TemperaturesDokument1 SeiteAcoustic Intravalley Scattering at Low Temperaturesalokesh1982Noch keine Bewertungen

- STLE July 2018Dokument108 SeitenSTLE July 2018Jorge Cuadros Blas100% (1)

- Petrol Chainsaws: Owner's ManualDokument4 SeitenPetrol Chainsaws: Owner's Manualkatta ngaNoch keine Bewertungen

- WPS, PQR & WQT According To ASME Section IX - 2019Dokument50 SeitenWPS, PQR & WQT According To ASME Section IX - 2019Anon YmousNoch keine Bewertungen

- Corrosion of Carbon Steels in Caustic SodaDokument5 SeitenCorrosion of Carbon Steels in Caustic SodamasilamaniNoch keine Bewertungen

- Pcmflash 71Dokument160 SeitenPcmflash 71helakob197Noch keine Bewertungen

- Pravin ResumeDokument3 SeitenPravin ResumeSatyajeet ReddyNoch keine Bewertungen

- Coulson MethodDokument17 SeitenCoulson MethodSanjeeb SutradharNoch keine Bewertungen

- Question and Answers Electrical MaintenaDokument416 SeitenQuestion and Answers Electrical MaintenaimranNoch keine Bewertungen

- Flexible Disc Couplings: TB Wood's Form-Flex & Torsiflex-IDokument52 SeitenFlexible Disc Couplings: TB Wood's Form-Flex & Torsiflex-Ioscar.pabaNoch keine Bewertungen

- Viteee - 2020 - Physics 1. Laws of Motion & Work, Energy and PowerDokument2 SeitenViteee - 2020 - Physics 1. Laws of Motion & Work, Energy and PowerAaditya KannanNoch keine Bewertungen

- CH 4 - The Properties of MatterDokument21 SeitenCH 4 - The Properties of Matterapi-236666161Noch keine Bewertungen

- SBSBattery VRLA Tubular Gel VRZ Series PDFDokument1 SeiteSBSBattery VRLA Tubular Gel VRZ Series PDFAleiska Victoria Gómez BetancourthNoch keine Bewertungen

- SUNON DC Brushless Fan & Blower (255-E)Dokument214 SeitenSUNON DC Brushless Fan & Blower (255-E)Carlos X.Noch keine Bewertungen

- Hot Bolt Clamp 8pp BrochureDokument8 SeitenHot Bolt Clamp 8pp BrochureAlaxxiNoch keine Bewertungen

- Biogass DigesterDokument9 SeitenBiogass DigesterHasnain AshrafNoch keine Bewertungen

- Report PDFDokument12 SeitenReport PDFShailendra RajputNoch keine Bewertungen

- Lab 2 - Electric FieldDokument5 SeitenLab 2 - Electric FieldAbdoul BinJimNoch keine Bewertungen

- Cu N Kháng MikroDokument4 SeitenCu N Kháng Mikrothienvuong90Noch keine Bewertungen

- Experiment Procedure: Description of The Experiment Components and Measuring EquipmentsDokument14 SeitenExperiment Procedure: Description of The Experiment Components and Measuring EquipmentsMuhammad Ali Khan AwanNoch keine Bewertungen

- Addon Products From GiovenzanaDokument11 SeitenAddon Products From GiovenzanalifttecNoch keine Bewertungen

- LA500DC: Unrivaled Performance, Security and AccessibilityDokument2 SeitenLA500DC: Unrivaled Performance, Security and AccessibilityMisho Felino GarciaNoch keine Bewertungen

- Technical System Catalogue RilineDokument21 SeitenTechnical System Catalogue RilineTomislav ŠeplNoch keine Bewertungen