Beruflich Dokumente

Kultur Dokumente

Preparatorio9 LABORATORIO de Sistemas Digitales

Hochgeladen von

Eduardo CaizatoaOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Preparatorio9 LABORATORIO de Sistemas Digitales

Hochgeladen von

Eduardo CaizatoaCopyright:

Verfügbare Formate

Escuela Politcnica Nacional

Facultad de ingeniera elctrica y electrnica Laboratorio de sistemas digitales Prctica N9

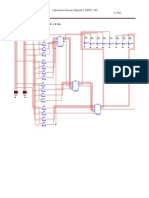

PRCTICA N9 TEMA:Contadores OBJETIVO: Familiarizar al estudiante con el diseo de circuitos contadores TRABAJO PREPARATORIO: 1. Utilizando flip-flops J-K, disee un contador asincrnico descendente modulo 20 que pueda ser visualizado en displays de nodo comn, y el circuito de borrado manual que me permita empezar en 0 en cualquier momento.

1

U4

7 1 2 6 4 5 3

2 7 2 7 2

A B C D BI/RBO RBI LT 7447

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

U1:A

Q 15 9 6 J CLK

U1:B

Q 11 4 1 J CLK

U2:A

Q 15 9 6 J CLK

U2:B

Q 11 4 1 J CLK

U3:A

Q 15

J CLK

4 1 16

8 7 6 5 4 3 2 R R R R R

14

12

10

16

14

12

10

16

14

RP1

3 8 3 8

7476

7476

7476

7476

7476

RESPACK-7

1

U5

7 1 2 6 4 5 3 A B C D BI/RBO RBI LT 7447 3 8 6 5 7432 7432 10 7408 2

8 7 6 5 4 3 2 1

U7:A

1 3 2

0

U7:C

9

U6:A

1

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

U7:B 7432

4

RP2

RESPACK-7

2. Utilizando flip-flops J-K disee un contador asincrnico ascendente modulo 24 que pueda ser visualizado en displays de nodo comn, y el circuito de borrado manual que me permita empezar en 0 en cualquier momento.

U10

1

U3:B

Q 11 4 1

R

U8:A

Q 15 9 6 J CLK

U8:B

Q 11 4 1 J CLK

U9:A

Q 15 9 6 J CLK

U9:B

Q 11 4 1 J CLK

U12:A

Q 15

7 1 2 6 4 5 3

A B C D BI/RBO RBI LT 7447

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

J CLK K

J CLK

6 12

10

16

14

12

10

16

14

12

10

16

14 7 1 2 6 4 5 3

U11

A B C D BI/RBO RBI LT 7447 QA QB QC QD QE QF QG 13 12 11 10 9 15 14

7476

7476

7476

7476

7476

7476

U16:A

1 3 2 7400 1 2 13

U15:A

12

U13:A

1 3 2 7400

8 7 6 5 4 3 2

8 7 6 5 4 3 2

7411

U14:A

1 3 2 7408

RP3

RESPACK-7

RP4

RESPACK-7

Escuela Politcnica Nacional

Facultad de ingeniera elctrica y electrnica Laboratorio de sistemas digitales Prctica N9

3. Disear un contador asincrnico ascendente modulo 68 utilizando el contador 7490 y 7493 que pueda ser visualizado en displays de nodo comn, y el circuito de borrado manual que me permita empezar en 0 en cualquier momento. 7490

U1

14 1 CKA CKB Q0 Q1 Q2 Q3 12 9 8 11 7 1 2 6 4 5 3

U3

A B C D BI/RBO RBI LT 74LS47 QA QB QC QD QE QF QG 13 12 11 10 9 15 14

2 3 6 7

R0(1) R0(2) R9(1) R9(2) 74LS90

U5:B

4 6 5 74LS08 3 1 74LS08

8 7 6 5 4 3 2

U5:A

2

RP2

RESPACK-7

1

U2

14 1 CKA CKB Q0 Q1 Q2 Q3 12 9 8 11 7 1 2 6 4 5 3

U4

A B C D BI/RBO RBI LT 74LS47

8 7 6 5 4 3 2 1

U5:C

9 8 10 74LS08

2 3 6 7

R0(1) R0(2) R9(1) R9(2) 74LS90

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

RP1

RESPACK-7

7493

6

U15:B

7411

U18

3 2 R0(2) R0(1) QD QC QB QA

5 4 3

1

U20

11 8 9 12 7 1 2 6 4 5 3 A B C D BI/RBO RBI LT 7447

8 7 6 5 4 3 2

U26:B

4 6 5 7432

4

1 14

CKB CKA 7493

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

U17:B

7404

3

U26:C

9 8 10 7432 3 2 RESPACK-7

U19

R0(2) R0(1) QD QC QB QA 11 8 9 12 7 1 2 6 4 5 3

U25

A B C D BI/RBO RBI LT 7447

4 5

RP7

QA QB QC QD QE QF QG 13 12 11 10 9 15 14

8 7 6 5 4 3 2 1

1 14

CKB CKA 7493

U6:B

7408

RP8

RESPACK-7

Escuela Politcnica Nacional

Facultad de ingeniera elctrica y electrnica Laboratorio de sistemas digitales Prctica N9

4. Utilizando flip-flops JK disee un contador asincrnico descendente modulo 22 que pueda ser visualizado en displays de nodo comn, y el circuito de borrado manual que me permita empezar en 0 en cualquier momento.

U7:A

1 3 2 5 74LS32 4

U7:B

6

74LS32

1

2 7 2 7 S S S S

J CLK

J CLK

J CLK

J CLK

J CLK

4 1 16

15

9 6

11

4 1

15

9 6

11

4 1

U1:A

U1:B

U2:A

U2:B

U3:A

Q 15

14

12

10

16

14

12

10

16

14

7476

7476

7476

7476

7476 8

U4:C

10 9

74LS08

0

U4:B

4 6 3 2 74LS08 74LS08 5

U4:A

1

U5:B

4 6 5 13 74LS32 12

U4:D

11

?

U5:C

9 8 10 74LS32

74LS08

U6:A

1 3 2 5 74LS08 4

U6:B

6

? ?

U6:C

9 8 10 12 74LS08 11 13 74LS32 11 13 74LS08

74LS08

U5:D

U6:D

12

5. Realice un circuito digital que permita dividir una seal cuadrada de 25 KHz para obtener una seal de 5 KHz.

A

U1

R1(1) 14 1 CKA CKB Q0 Q1 Q2 Q3 12 9 8 11

B C D

R1

330R

2 3 6 7

R0(1) R0(2) R9(1) R9(2) 7490

R2

330R

D1

LED-RED

D2

LED-RED

6. Disear un contador sincrnico ascendente y descendente modulo 08, utilizando flipflop JK que pueda ser visualizado en displays de nodo comn, y el circuito de borrado manual que me permita empezar en 0 en cualquier momento.

Escuela Politcnica Nacional

Facultad de ingeniera elctrica y electrnica Laboratorio de sistemas digitales Prctica N9

U38:A

1 7404 2

1

U38:B

3 7404 4 5

1

U38:C

6 7404

0

(COM)

U37:A

1 3 2 7408 2 3 5 6 11 10 14 13

U39

1A 1B 2A 2B 3A 3B 4A 4B A/B E 74157 1Y 2Y 3Y 4Y 4 7 9 12 U40(LT) 7 1 2 6 4 5 3

U40

A B C D BI/RBO RBI LT 7447 QA QB QC QD QE QF QG 13 12 11 10 9 15 14

U25:B(J)

J CLK

J CLK

4 1

15

J CLK

9 6

11

9 6

U25:B

U36:A

U36:B

Q 11

0

8 R

1 15

7476

U25:B(CLK)

12

10

16

14

12

10

7476

7476

BIBLIOGRAFA http://www.esi.uclm.es/www/isanchez/teco/pr6.doc SISTEMAS DIGITALES, Novillo Carlos. Libro Manual TEXAS INSTRUMENTS, Pocket Data Book. Fast and LS TTL data, manual TTL de MOTOROLA

Das könnte Ihnen auch gefallen

- CONTADORESDokument15 SeitenCONTADORESRudxy M100% (2)

- Monitor de Produccion GiganteDokument12 SeitenMonitor de Produccion GiganteJOSEMARIA RAFAEL ARCE FALLANoch keine Bewertungen

- ELectronica DigitalDokument16 SeitenELectronica DigitalHerman SalasNoch keine Bewertungen

- Copia de Copia de ACER - Codificación PermisosDokument80 SeitenCopia de Copia de ACER - Codificación PermisosBrian ZerboNoch keine Bewertungen

- Circuito Multiplicador Binario 4Dokument1 SeiteCircuito Multiplicador Binario 4Omar GarcíaNoch keine Bewertungen

- Preparatorio # 8Dokument6 SeitenPreparatorio # 8Raisa MarilynNoch keine Bewertungen

- Configuración circuito sumador BCD 7483 7486Dokument9 SeitenConfiguración circuito sumador BCD 7483 7486Alex MolinaNoch keine Bewertungen

- Flip Flop 74ls76Dokument4 SeitenFlip Flop 74ls76Giancarlo Villanueva Oropeza0% (1)

- Entrenador PLLDokument1 SeiteEntrenador PLLCalinhosBaoNoch keine Bewertungen

- Sistema Mínimo de Una Computadora o MicrocontroladorDokument1 SeiteSistema Mínimo de Una Computadora o MicrocontroladorAlfre2AlcazarNoch keine Bewertungen

- Sistemas Digitales Problemas 1Dokument25 SeitenSistemas Digitales Problemas 1Ce ChavezNoch keine Bewertungen

- Sistemas Digitales Problemas 3Dokument39 SeitenSistemas Digitales Problemas 3Christian QCNoch keine Bewertungen

- Imprimir Laboratorios ELT 352Dokument9 SeitenImprimir Laboratorios ELT 352Jose JobsNoch keine Bewertungen

- 1 Tarea N2 - PotenciaDokument16 Seiten1 Tarea N2 - PotenciaEDGAR KANTUTA HNoch keine Bewertungen

- Contadores digitales EPNDokument5 SeitenContadores digitales EPNRob ArrobaNoch keine Bewertungen

- Clase de Micro Control Adores PIC16F877Dokument21 SeitenClase de Micro Control Adores PIC16F877Gustavo ChaconNoch keine Bewertungen

- Lab 7 DigitalesDokument11 SeitenLab 7 DigitalesLuis HinoNoch keine Bewertungen

- UNIVERSIDAD DEL CALLAO FACULTAD DE INGENIERIA ELÉCTRICA Y ELECTRÓNICA ESCUELA PROFECIONAL DE INGENIERIA ELECTRÓNICA ASIGNATURA: MICROCONTROLADORES 01LDokument8 SeitenUNIVERSIDAD DEL CALLAO FACULTAD DE INGENIERIA ELÉCTRICA Y ELECTRÓNICA ESCUELA PROFECIONAL DE INGENIERIA ELECTRÓNICA ASIGNATURA: MICROCONTROLADORES 01LDoming de la CruzNoch keine Bewertungen

- 1Dokument4 Seiten1Leo FloresNoch keine Bewertungen

- Circuito Contador Binario de Personas Entrada y SalidaDokument3 SeitenCircuito Contador Binario de Personas Entrada y SalidaJomagoz CanizaNoch keine Bewertungen

- Teclado MatricialDokument6 SeitenTeclado MatricialNelson CorreaNoch keine Bewertungen

- Mantenimiento maquinaria mina MarisolDokument20 SeitenMantenimiento maquinaria mina MarisolDannyElbisCatuntaHuisaNoch keine Bewertungen

- Electrónico ascensor 8 plantasDokument11 SeitenElectrónico ascensor 8 plantasCarlos Alberto Malo AquinoNoch keine Bewertungen

- SA-AK770 Diagrama de FuenteDokument3 SeitenSA-AK770 Diagrama de FuenteJavier Arias LuceroNoch keine Bewertungen

- Diagrama Con Lv1116nDokument8 SeitenDiagrama Con Lv1116nJuan Carlos GarcíaNoch keine Bewertungen

- Flip flop y contadores digitalesDokument5 SeitenFlip flop y contadores digitalesLC LyonNoch keine Bewertungen

- Suma PORTB+0AhDokument3 SeitenSuma PORTB+0AhGerman A CMeNoch keine Bewertungen

- CTSAADokument24 SeitenCTSAApaulmx13Noch keine Bewertungen

- Sistemas Digitales - Carlos Novillo M - AnexosDokument11 SeitenSistemas Digitales - Carlos Novillo M - AnexosWilson Francisco BritoNoch keine Bewertungen

- Borrador Informe Digitales Simulacion Luces DireccionalesDokument20 SeitenBorrador Informe Digitales Simulacion Luces Direccionalesjmalpica5615Noch keine Bewertungen

- Proyecto Simulación Contador de Personas U ObjetosDokument7 SeitenProyecto Simulación Contador de Personas U ObjetosMassielJasselNoch keine Bewertungen

- Fuente 32XH6BDokument1 SeiteFuente 32XH6BCarlos BaezNoch keine Bewertungen

- Practica 7Dokument5 SeitenPractica 7Carlos BeltránNoch keine Bewertungen

- Contador Ascendente Descendente PDFDokument5 SeitenContador Ascendente Descendente PDFJoshua Nessus Aragonès SalazarNoch keine Bewertungen

- Ejerciciospic PDFDokument40 SeitenEjerciciospic PDFJose Neira CastilloNoch keine Bewertungen

- PRACTICA - 8 - PERIFERICO - DE - ENTRADA - TECLADO - EQ. MICROINF 9h20 - 19-03-2019Dokument5 SeitenPRACTICA - 8 - PERIFERICO - DE - ENTRADA - TECLADO - EQ. MICROINF 9h20 - 19-03-2019Fabrice FeussiNoch keine Bewertungen

- Contador de 0 A 9 Con Display de 7 Segmentos de Ánodo ComúnDokument2 SeitenContador de 0 A 9 Con Display de 7 Segmentos de Ánodo ComúnPedro SánchezNoch keine Bewertungen

- Programación de SemafarosDokument11 SeitenProgramación de SemafarosJulio RamírezNoch keine Bewertungen

- PRACTICA 6 Roberto JimenezDokument10 SeitenPRACTICA 6 Roberto JimenezRoberto Jimenez DiazNoch keine Bewertungen

- Practica SecuencialesDokument23 SeitenPractica SecuencialesJimmy MartinezNoch keine Bewertungen

- Pa3 Ermelinda MezaDokument9 SeitenPa3 Ermelinda MezaHermelinda MezaNoch keine Bewertungen

- Lab 04 - Circuitos Contadores Con Flip FlopsDokument5 SeitenLab 04 - Circuitos Contadores Con Flip FlopshugoNoch keine Bewertungen

- Termometro Digital - PozulDokument14 SeitenTermometro Digital - Pozulrocker17_10Noch keine Bewertungen

- Probador de Flyback de Bob Parker.Dokument7 SeitenProbador de Flyback de Bob Parker.Jesus Alfonso Blanchard Celedon0% (1)

- CNC 3 AxDokument1 SeiteCNC 3 AxMeher BnouniNoch keine Bewertungen

- CIRCUITOSDokument26 SeitenCIRCUITOSEduardo HuancaNoch keine Bewertungen

- Plano Behringer Pmp6000Dokument15 SeitenPlano Behringer Pmp6000Alejandro Munoz0% (1)

- Semana 8 Electronica BasicaDokument6 SeitenSemana 8 Electronica BasicaErik PaucarNoch keine Bewertungen

- Programación de microcontrolador PIC16F628A para visualización en display 7 segmentosDokument18 SeitenProgramación de microcontrolador PIC16F628A para visualización en display 7 segmentosJulio RamírezNoch keine Bewertungen

- Robot seguidor de líneas con PIC16F84ADokument2 SeitenRobot seguidor de líneas con PIC16F84AaxefecNoch keine Bewertungen

- Montaje receptor de bajo coste basado en SI4735Dokument28 SeitenMontaje receptor de bajo coste basado en SI4735Teodor SerbanNoch keine Bewertungen

- Microcontrolador PIC 16f84aDokument26 SeitenMicrocontrolador PIC 16f84aaoh1226Noch keine Bewertungen

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaVon EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaNoch keine Bewertungen

- Simulación de circuitos electrónicos con OrCAD® PSpice®Von EverandSimulación de circuitos electrónicos con OrCAD® PSpice®Noch keine Bewertungen

- Servicios complementarios en sistemas eléctricos de potencia: Análisis y modelamientoVon EverandServicios complementarios en sistemas eléctricos de potencia: Análisis y modelamientoBewertung: 5 von 5 Sternen5/5 (1)

- 100 Circuitos de Shields para MotoresVon Everand100 Circuitos de Shields para MotoresBewertung: 4.5 von 5 Sternen4.5/5 (4)

- Alta Frecuencia 1er BimestreDokument6 SeitenAlta Frecuencia 1er BimestreEduardo CaizatoaNoch keine Bewertungen

- Tips y Trucos de Excel PDFDokument71 SeitenTips y Trucos de Excel PDFNeri CroCroNoch keine Bewertungen

- Lineas de Transmisión Parte1Dokument50 SeitenLineas de Transmisión Parte1Eduardo CaizatoaNoch keine Bewertungen

- PRACTICA No1Dokument9 SeitenPRACTICA No1Eduardo CaizatoaNoch keine Bewertungen

- Preparatorio - Pract 6 - Ampli Oper Parte 1Dokument7 SeitenPreparatorio - Pract 6 - Ampli Oper Parte 1Eduardo CaizatoaNoch keine Bewertungen

- PREPARATORIO No10Dokument9 SeitenPREPARATORIO No10Eduardo CaizatoaNoch keine Bewertungen

- Informe 4.Dokument10 SeitenInforme 4.Eduardo CaizatoaNoch keine Bewertungen

- PRACTICA No1Dokument9 SeitenPRACTICA No1Eduardo CaizatoaNoch keine Bewertungen

- Transformadores de MedidaDokument6 SeitenTransformadores de MedidaEduardo CaizatoaNoch keine Bewertungen

- Sistema Digital y Sistema AnalógicoDokument3 SeitenSistema Digital y Sistema AnalógicoEduardo CaizatoaNoch keine Bewertungen

- Matriz GTC45 SiexpalDokument6 SeitenMatriz GTC45 SiexpalSeinma Seinma100% (1)

- Plan de Emergencia Ambiental PDFDokument65 SeitenPlan de Emergencia Ambiental PDFWillmam VillasmilNoch keine Bewertungen

- Cuento Bajo El AguaDokument3 SeitenCuento Bajo El AguaLuis AntonioNoch keine Bewertungen

- Manual Oficial Del LulowinDokument77 SeitenManual Oficial Del LulowinjfmarcanoNoch keine Bewertungen

- Ondas Transversales y Longitudinales, Reflexión y RefracciónDokument7 SeitenOndas Transversales y Longitudinales, Reflexión y RefracciónDavid MartinezNoch keine Bewertungen

- Cor 60 RPTDokument1 SeiteCor 60 RPTJuandaCabreraCoboNoch keine Bewertungen

- Programas Presupuestarios Con Proyectos de InversiónDokument5 SeitenProgramas Presupuestarios Con Proyectos de InversiónCarlos GarnicaNoch keine Bewertungen

- Materiales para Obra NegraDokument1 SeiteMateriales para Obra NegraHiroshi Alejandro100% (1)

- Marbil Parrilla ValleDokument11 SeitenMarbil Parrilla ValleZarate Mora David EduardoNoch keine Bewertungen

- Ante Proyecto IntegradorDokument10 SeitenAnte Proyecto IntegradorDavid PalaciosNoch keine Bewertungen

- Manual Petzl PDFDokument64 SeitenManual Petzl PDFBomberosVoluntariosAlvear100% (3)

- Manual Combate Contra IncendiosDokument24 SeitenManual Combate Contra IncendiosDiana Laura Bautista MontejoNoch keine Bewertungen

- Produccion Petrolera y Mecanismos de EmpujeDokument15 SeitenProduccion Petrolera y Mecanismos de EmpujeArgus Arley Gustavo ANoch keine Bewertungen

- Diagramas de Fase o EquilibrioDokument5 SeitenDiagramas de Fase o EquilibrioSergio MartinezNoch keine Bewertungen

- Ciudad LegibleDokument53 SeitenCiudad LegibleAna Del GenerNoch keine Bewertungen

- Informe Final 2 Circuitos Electronicos 1Dokument31 SeitenInforme Final 2 Circuitos Electronicos 1Darwin Dario Uscacchi ValenciaNoch keine Bewertungen

- Crea y publica presentación PowerPoint en YouTubeDokument23 SeitenCrea y publica presentación PowerPoint en YouTubesilroggero6746Noch keine Bewertungen

- (Ejercicios) Componentes Internos Del OrdenadorDokument2 Seiten(Ejercicios) Componentes Internos Del OrdenadorBigRattelNoch keine Bewertungen

- Agentes de Control de Espuma para Tensioactivos SiliconadosDokument14 SeitenAgentes de Control de Espuma para Tensioactivos SiliconadosJosefogNoch keine Bewertungen

- Materiales QUIÑONESDokument3 SeitenMateriales QUIÑONESJorg LuisNoch keine Bewertungen

- Aceite de EucaliptoDokument7 SeitenAceite de EucaliptoJasmy JasNoch keine Bewertungen

- Infograma #2 - Yaudy Alvarado MurilloDokument2 SeitenInfograma #2 - Yaudy Alvarado MurilloYaudy AlvaradoNoch keine Bewertungen

- Fichas Geomorfologia CorregidoDokument4 SeitenFichas Geomorfologia CorregidoMaría Emilia TorresNoch keine Bewertungen

- Introducción Integral DefinidaDokument18 SeitenIntroducción Integral Definidaamhinu90100% (1)

- REQUERIMIENTOS ActualizadoDokument10 SeitenREQUERIMIENTOS ActualizadoKheny Lopez100% (1)

- 3 Destilación DiferencialDokument35 Seiten3 Destilación DiferencialMaria Del Mar MedinaNoch keine Bewertungen

- Clases 3 CoordenadasDokument25 SeitenClases 3 CoordenadasGabriel ZentenoNoch keine Bewertungen

- Transporte interno optimizadoDokument8 SeitenTransporte interno optimizadoRuth Flavia Rojas SalasNoch keine Bewertungen

- 2Dokument151 Seiten2Aldony Pari ChaupisNoch keine Bewertungen

- Conservacion Por MicroondasDokument28 SeitenConservacion Por MicroondasGerald Paul Chumpitaz HuanquiNoch keine Bewertungen