Beruflich Dokumente

Kultur Dokumente

8086 & 8088 Microprocessors: Lecture 4: Microprocessors & Computer Architecture 8086/8088 Microprocessors

Hochgeladen von

Awais004Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

8086 & 8088 Microprocessors: Lecture 4: Microprocessors & Computer Architecture 8086/8088 Microprocessors

Hochgeladen von

Awais004Copyright:

Verfügbare Formate

6-Mar-14

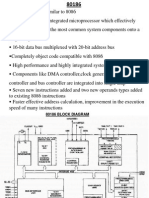

8086 & 8088 Microprocessors

Course Code:EE2323 Microprocessors & Computer Architecture Spring-2014, M.A.J.U Islamabad 8086 Microprocessor (1978) 16-bit microprocessor 20-bit Address Bus 16-bit Data Bus 6-byte instruction queue Separate Data & Segment Registers 8088 Microprocessor (1979) 16-bit microprocessor 20-bit Address Bus 8-bit Data Bus 4-byte instruction queue Separate Data & Segment Registers

1 2

Lecture 4: Microprocessors & Computer Architecture 8086/8088 Microprocessors

8086/8088 Processor Microarchitecture

Micro-architecture is internal architecture of a processor 8086/8088 microprocessors have pipelined micro architecture that employ parallel processing Micro-architecture of 8086/8088 microprocessors consist of two independent processing units

Bus interface Unit (BIU) Execution Unit (EU)

8086/8088 Processor Microarchitecture

BIU & EU make fetch & execution of instructions independent operations Both units execute in parallel and result in efficient use of system bus and higher performance

6-Mar-14

Bus Interface Unit (BIU)

BIU is 8086/8088 interface to the outside world BIU is responsible for performing all external bus operations such as instruction fetching, reading/writing of data to memory and address generation BIU is composed of system bus, segment registers, instruction pointer, address generation unit and instruction queue System bus include bidirectional data bus, 20 bit address bus and control bus Instruction queue is a FIFO queue where program instructions are prefetched in sequential order and fed into the execution unit

5

Execution Unit (EU)

Execution unit is responsible for decoding & execution of program instructions Execution unit is composed of general purpose registers, ALU, control flags & temporary operand registers EU accesses instructions from instruction queue, decodes them, reads operands from registers/memory and performs the operation specified by instruction ALU performs arithmetic, logic, shift operations and may update control flags EU may also request BIU to perform read/write operations on memory or I/O devices If instruction queue is empty, EU waits for the instruction to be fetched

6

Memory Address Space

Memory in an 8086 microprocessor is byte addressable With 20-bit address bus an 8086 P can address 1M ( 220) distinct memory locations Memory space is organized as consecutive byte locations over the address range 00000H to FFFFFH 8086 microprocessor can access data in memory as a byte (8-bits), word (16-bits) and double word (32-bits) 16 bit & 32 bit data occupy multiple byte locations in memory

7

Byte Ordering (Endianness)

Multiple byte data can be stored in memory in two formats Little Endian

Least significant byte goes to low memory location & most significant byte goes to high memory location

Big Endian

Most significant byte goes to low memory location & least significant byte goes to high memory location 8086/8088 based processors memory in little endian format access

8

6-Mar-14

Byte Ordering (Endianness) : Example

Example : Store 16-bit words 1234H and 5678H at Memory Addresses 0x10000H & 0x10002H in Little Endian & Big Endian Format

Byte Ordering (Endianness) : Example

Example : Store 8-bit data 12H, 39H, 85H, 48H at Memory Addresses 0x10000H to 0x10003H in Little Endian & Big Endian Format

Endianness does not matter for 8bit

Big Endian

Little Endian

9

Big Endian

Little Endian

10

Memory Alignment

For storage of multi-byte data elements such as 16-bit, 32-bit , 64-bit data memory address is either aligned or misaligned An aligned address for an n-byte data element is an address that is multiple of n

For 2 byte data, aligned address should be multiple of 2 For 4 byte data, aligned address should be multiple of 4 For 8 byte data, aligned address should be multiple of 8

Memory Alignment : Word Data

Word data is composed of two bytes For word size data an aligned memory address should be a multiple of 2 A word data stored at an even address is said to be aligned word A word data stored at an odd address is said to be a misaligned word

If the address of an n-byte data in memory is not multiple of n it is said to be misaligned/unaligned x86 processors can handle both aligned and misaligned memory addresses

11

12

6-Mar-14

Memory Alignment : Word Data

Memory Alignment Double word Data

Double word data is composed of four bytes

Address

0008H 0007H 0006H 0005H 0004H 0003H 0002H 0001H 0000H

Physical Memory

Byte 8 Byte7

Word 6

Misaligned Words

An aligned double word is stored at a memory address that is a multiple of 4 If a double word is stored at an address that is not a multiple of 4 it is said to be a misaligned double word

Byte 6 Byte 5 Byte 4 Byte 3

Word 2 Word 4 Word 3

Aligned Words

Word 1

Byte 2 Byte 1 Byte 0

Word 0

13

14

Memory Alignment Double word Data

Aligned Double Words Address

0008H 0007H 0006H 0005H 0004H 0003H 0002H 0001H 0000H

Memory Alignment of Data

Physical Memory

Byte 8 Byte7 Byte 6 Byte 5 Byte 4 Byte 3 Byte 2 Byte 1 Byte 0

Double Word 0 Double Word 1 Double Word 4 Double Word 3 Double Word 2 Double Word 5

Not Aligned Double Words

15 16

6-Mar-14

Data Types

Data formats supported by 8086/8088 P are :

Data Types

BCD Data

BCD data is processed either in unpacked or packed form in 8086/8088 microprocessors In unpacked form one BCD digit is stored in 4 least significant bits of a byte while upper 4 bits are set to zero In packed form two BCD digits are stored in a byte

Integer Data

Integer data may exist as :

Byte (8-bits) Word (16-bits) Double Word (32-bits)

Integer data is processed by 8086/8088 as unsigned or signed data Negative numbers are stored and processed in 2s complement form

ASCII Data

Each ASCII character is stored in a byte in 8086/8088 microprocessors

8086/8088 P has specific instructions to handle BCD and ASCII Data

17

18

8086/8088 P Software Model

Software model of a processor explain the internal CPU registers, their types and usage, their limitations, memory and I/O address space, address generation, control and status flags Software model helps software programmer understanding operation of the microprocessor in

8086/8088 P Software Model

8086 Memory Space (1M)

8086 Register File

8086 software model includes an instruction pointer (IP) register, 12 16-bit internal registers, a status/flag register and memory & I/O address spaces Software architecture of 8086 & 8088 microprocessors is same

19

8086 I/O Space (64k)

20

6-Mar-14

8086/8088 Register File

Data Register

7

Accumulator AX Base BX Counter CX Data DX

Segment Register

0 7 AL BL CL DL 0 15

Code Segment CS Data Segment DS Extra Segment ES Stack Segment SS

AH BH CH DH

CS DS ES SS

Pointer Register

Stack Pointer Base Pointer

Flag Register

SP BP 0

Status and control flag

15

Flag H

0 7

Flag L

Index Register

Source Index Destination Index

Instruction Pointer

SI DI 0

Instruction Pointer

15

15

IP

* All 8086 Registers are 16 bits in size. 8086 data registers are further divided into two 8-bit halves

21

Das könnte Ihnen auch gefallen

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Von EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Noch keine Bewertungen

- Arch of 8088 8086Dokument54 SeitenArch of 8088 8086riyasekaranNoch keine Bewertungen

- Chapter 2Dokument20 SeitenChapter 2Saud MustafaNoch keine Bewertungen

- 8086 Third Term TopicsDokument46 Seiten8086 Third Term TopicsgandharvsikriNoch keine Bewertungen

- Unit-1,2,3 MP&MC NotesDokument25 SeitenUnit-1,2,3 MP&MC NotesHyma Prasad GelliNoch keine Bewertungen

- Arche of 8086Dokument9 SeitenArche of 8086MOHAMMED ASLAM CNoch keine Bewertungen

- Software Model of 8086 MicroprocessorDokument30 SeitenSoftware Model of 8086 MicroprocessorNitesh TarbaniNoch keine Bewertungen

- MP-MC R16 - Unit-4Dokument14 SeitenMP-MC R16 - Unit-4satyanarayana12Noch keine Bewertungen

- Microprocessor NotesDokument140 SeitenMicroprocessor NotesSaquibh ShaikhNoch keine Bewertungen

- Amp Module 1Dokument14 SeitenAmp Module 1fasnamditNoch keine Bewertungen

- MP Unit-8 VtuDokument10 SeitenMP Unit-8 VtuBmvpNoch keine Bewertungen

- Unit - Iv: Advanced Microprocessors: Salient Features of 80386Dokument14 SeitenUnit - Iv: Advanced Microprocessors: Salient Features of 80386Swamy NallabelliNoch keine Bewertungen

- 16 Bit Microprocessor 8086Dokument11 Seiten16 Bit Microprocessor 8086Yogesh KuteNoch keine Bewertungen

- Internal Architecture 8086Dokument3 SeitenInternal Architecture 8086firoz83% (6)

- Microprocessor Unit-1 PART ADokument12 SeitenMicroprocessor Unit-1 PART ASasi BhushanNoch keine Bewertungen

- UNIT I 8086 Microprocessor Architecture and Register OrganizationDokument50 SeitenUNIT I 8086 Microprocessor Architecture and Register Organizationsnehaupadhya20Noch keine Bewertungen

- CS18303 Microprocessor and Microcontroller Lecture NotesDokument160 SeitenCS18303 Microprocessor and Microcontroller Lecture NotesDeepak SrinivasNoch keine Bewertungen

- Lecture 5Dokument46 SeitenLecture 5MuhammadSaeedTahirNoch keine Bewertungen

- Chapter 2 - Microprocessor ArchitectureDokument52 SeitenChapter 2 - Microprocessor ArchitectureAhmed QaziNoch keine Bewertungen

- Intel8086microprocessor 140901003952 Phpapp02Dokument9 SeitenIntel8086microprocessor 140901003952 Phpapp02dz15dzNoch keine Bewertungen

- MP - Lec 02 - The Microprocessor and Its ArchitectureDokument40 SeitenMP - Lec 02 - The Microprocessor and Its ArchitectureuabdulgwadNoch keine Bewertungen

- 8086introductionDokument175 Seiten8086introductionSasanka Sekhar SahuNoch keine Bewertungen

- Microprocessor 80286Dokument4 SeitenMicroprocessor 80286xorxorxorNoch keine Bewertungen

- 8086 Microprocessor CheatsheetDokument17 Seiten8086 Microprocessor Cheatsheetdz15dzNoch keine Bewertungen

- Unit 1 - 80386 Architecture and Programmers ModelDokument43 SeitenUnit 1 - 80386 Architecture and Programmers ModelpjNoch keine Bewertungen

- NotesDokument21 SeitenNotesShinisg Vava50% (2)

- Microprocessor LAB IIDokument26 SeitenMicroprocessor LAB IISomnath DeyNoch keine Bewertungen

- MPMC (Unit 02) Part 01Dokument101 SeitenMPMC (Unit 02) Part 01bovas.biju2021Noch keine Bewertungen

- CH-6 8086 Microprocessor InterfacingDokument8 SeitenCH-6 8086 Microprocessor InterfacingAnikhet MulkyNoch keine Bewertungen

- Mpi Unit 1Dokument22 SeitenMpi Unit 1sree ramyaNoch keine Bewertungen

- Micro Processor 8086Dokument27 SeitenMicro Processor 8086tarforgalz7265Noch keine Bewertungen

- Chapter TwoDokument48 SeitenChapter Twolemi bkNoch keine Bewertungen

- Week2-The 8086 Microprocessor ArchitectureDokument48 SeitenWeek2-The 8086 Microprocessor ArchitectureJerone CastilloNoch keine Bewertungen

- and Pentium MicroprocessorsDokument37 Seitenand Pentium Microprocessorsgayathrishiv91100% (1)

- 8086 Memory OrganizationDokument6 Seiten8086 Memory OrganizationRajiv Kumar100% (1)

- 8086 Memory OrganizationDokument6 Seiten8086 Memory OrganizationManohar_3020Noch keine Bewertungen

- 8086 Memory Organization PDFDokument6 Seiten8086 Memory Organization PDFAshok ChakriNoch keine Bewertungen

- Microprocessor QuestionDokument7 SeitenMicroprocessor QuestionANIRUDDHA PAULNoch keine Bewertungen

- Intel: Term Paper On 80486 MicroprocessorDokument8 SeitenIntel: Term Paper On 80486 MicroprocessorLALRAZNoch keine Bewertungen

- Unit 1&3Dokument18 SeitenUnit 1&3Sreekanth PagadapalliNoch keine Bewertungen

- Architecture of 80386Dokument42 SeitenArchitecture of 80386santosh.parsaNoch keine Bewertungen

- The Complete Understanding of Microprocessors and Intro To ARMDokument56 SeitenThe Complete Understanding of Microprocessors and Intro To ARMasimNoch keine Bewertungen

- 8086 Memory OrganizationDokument6 Seiten8086 Memory OrganizationTarun KumarNoch keine Bewertungen

- Advanced Microprocessor Presentation 4Dokument21 SeitenAdvanced Microprocessor Presentation 4Ubaid SaudagarNoch keine Bewertungen

- Microprocessor Helpful NotesDokument234 SeitenMicroprocessor Helpful NotesNevin HardyNoch keine Bewertungen

- 8086 Notes NITW2020Dokument76 Seiten8086 Notes NITW2020ka21ecb0f27Noch keine Bewertungen

- FEATURES OF 80386:: 2) Address 4GB of Memory 2) 16 MB ofDokument39 SeitenFEATURES OF 80386:: 2) Address 4GB of Memory 2) 16 MB ofJ VNoch keine Bewertungen

- Handouts 8086upDokument25 SeitenHandouts 8086upmift ademNoch keine Bewertungen

- Unit2 MP PDFDokument145 SeitenUnit2 MP PDFAASTHA KIETNoch keine Bewertungen

- FEATURES OF 80386:: 3) Address 4GB of Memory 3) 16 MB ofDokument39 SeitenFEATURES OF 80386:: 3) Address 4GB of Memory 3) 16 MB ofSorabh ChhabraNoch keine Bewertungen

- and 80486Dokument28 Seitenand 80486sangeetaranjan0% (1)

- I Am Intel 8086Dokument8 SeitenI Am Intel 8086AB ESPORTSNoch keine Bewertungen

- Chapter - Two of Microprocessor29Dokument45 SeitenChapter - Two of Microprocessor29Sã MïNoch keine Bewertungen

- Unit-I (Architecture of 8086)Dokument23 SeitenUnit-I (Architecture of 8086)Gouse MaahiNoch keine Bewertungen

- Architecture of 8086Dokument17 SeitenArchitecture of 8086sreenimolNoch keine Bewertungen

- Microprocessor 80386Dokument40 SeitenMicroprocessor 80386eshwar_worldNoch keine Bewertungen

- Architecture of 80386Dokument39 SeitenArchitecture of 80386Jaimon JacobNoch keine Bewertungen

- Master System Architecture: Architecture of Consoles: A Practical Analysis, #15Von EverandMaster System Architecture: Architecture of Consoles: A Practical Analysis, #15Noch keine Bewertungen

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationVon EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNoch keine Bewertungen

- "Do We Need A New Marketing Strategy?" A Case of Shaporch Pvt. LTDDokument1 Seite"Do We Need A New Marketing Strategy?" A Case of Shaporch Pvt. LTDAwais004Noch keine Bewertungen

- Final: Mohammad Ali Jinnah University, Islamabad Mid-Term Examination Fall 2014 Electronic Engineering (Morning)Dokument1 SeiteFinal: Mohammad Ali Jinnah University, Islamabad Mid-Term Examination Fall 2014 Electronic Engineering (Morning)Awais004Noch keine Bewertungen

- LeadershipDokument4 SeitenLeadershipAwais004Noch keine Bewertungen

- Slide001 Semiconductor ReviewDokument154 SeitenSlide001 Semiconductor ReviewAwais004Noch keine Bewertungen

- PLC Course Outline - WIADokument3 SeitenPLC Course Outline - WIAAwais004Noch keine Bewertungen

- Synchronous GeneratorDokument17 SeitenSynchronous GeneratorAwais004Noch keine Bewertungen

- Lecture 1 & 2 - 2Dokument37 SeitenLecture 1 & 2 - 2Awais0040% (1)

- Project Report SampleDokument23 SeitenProject Report SampleAwais004Noch keine Bewertungen

- 7 Cs of Effective CommunicationDokument10 Seiten7 Cs of Effective CommunicationHemantkumar JainNoch keine Bewertungen

- Hardware Implementation of A Neural-Network Recognition Module For Visual Servoing in A Mobile RobotDokument7 SeitenHardware Implementation of A Neural-Network Recognition Module For Visual Servoing in A Mobile RobotHarikrishnan Manakara RadhakrishnanNoch keine Bewertungen

- 8086 Instruction Set and Its ClassificationDokument3 Seiten8086 Instruction Set and Its ClassificationMuthu Kumar100% (1)

- Fpga Based 32 Bit Risc Processor DesignDokument18 SeitenFpga Based 32 Bit Risc Processor DesignAchit YadavNoch keine Bewertungen

- Microcontroller ApplicationsDokument115 SeitenMicrocontroller ApplicationsCapuchino HuiNingNoch keine Bewertungen

- Hardware Recommendations For HadoopDokument12 SeitenHardware Recommendations For HadoopTan ArmanNoch keine Bewertungen

- 101 Intro To The MP Post GuideDokument12 Seiten101 Intro To The MP Post Guiderpanther040% (1)

- EEE - 347 HW1 v2 - CBDokument3 SeitenEEE - 347 HW1 v2 - CBEmre OnursoyNoch keine Bewertungen

- LX2160A I NXP' B M: S S Iggest UlticoreDokument5 SeitenLX2160A I NXP' B M: S S Iggest UlticoreRoei ZoharNoch keine Bewertungen

- MCQ For 9th ClassDokument20 SeitenMCQ For 9th ClassSyed Faisal Bashir0% (1)

- 3D Printing Medical Miracles: Diagnostic Device Design Dynamic Response Analysis Hybrid 3D PrintingDokument60 Seiten3D Printing Medical Miracles: Diagnostic Device Design Dynamic Response Analysis Hybrid 3D PrintingOARIASCONoch keine Bewertungen

- N33 Presentation Rev1.1Dokument22 SeitenN33 Presentation Rev1.1José LezcanoNoch keine Bewertungen

- 04 Verilog LabDokument19 Seiten04 Verilog LabEstéfano Gómez100% (1)

- Cash Registers: Maintenance Guide Special Functions Programming (For Technical Personnel) Installation KitDokument81 SeitenCash Registers: Maintenance Guide Special Functions Programming (For Technical Personnel) Installation Kitromarosa_1936888690% (1)

- Embedded System Design IssuesDokument8 SeitenEmbedded System Design Issuesusamadar707Noch keine Bewertungen

- 5 Pen PC Technology Powerpoint PresentationDokument35 Seiten5 Pen PC Technology Powerpoint PresentationMohd JunaidNoch keine Bewertungen

- History of Computers: The Mechanical Era (1623-1945)Dokument4 SeitenHistory of Computers: The Mechanical Era (1623-1945)icih karolin bin stephenNoch keine Bewertungen

- Yoko PLCDokument126 SeitenYoko PLCfebinjohnNoch keine Bewertungen

- 6-SiFive Promotes RISC-V 20190905Dokument29 Seiten6-SiFive Promotes RISC-V 20190905nauman wazirNoch keine Bewertungen

- Question Bank Unit-I Mechatronics, Sensor and Transducers (2 Mark Questions)Dokument11 SeitenQuestion Bank Unit-I Mechatronics, Sensor and Transducers (2 Mark Questions)ChippyVijayanNoch keine Bewertungen

- Advanced Hardware FundamentalsDokument32 SeitenAdvanced Hardware FundamentalsshubhNoch keine Bewertungen

- SCE - EN - 011-100 Unspecific Hardware Configuration S7-1200 - R1709Dokument46 SeitenSCE - EN - 011-100 Unspecific Hardware Configuration S7-1200 - R1709shailesh284Noch keine Bewertungen

- MCQ Quiz 2 MicrocorrectDokument7 SeitenMCQ Quiz 2 MicrocorrectRick AlvientoNoch keine Bewertungen

- A01 THE-x86-MICROPROCESSOR 6821 FM 1 PDFDokument28 SeitenA01 THE-x86-MICROPROCESSOR 6821 FM 1 PDFJKNoch keine Bewertungen

- GCSE Computer Science Final Version PDFDokument72 SeitenGCSE Computer Science Final Version PDFkinhoonNoch keine Bewertungen

- MICROPORCESSOR 8085 Lab ManualDokument53 SeitenMICROPORCESSOR 8085 Lab ManualAjay PatilNoch keine Bewertungen

- William Stallings Computer Organization and Architecture 10 EditionDokument33 SeitenWilliam Stallings Computer Organization and Architecture 10 EditionkrtxbNoch keine Bewertungen

- h16763 Vxrail 14g Spec SheetDokument3 Seitenh16763 Vxrail 14g Spec SheetjimNoch keine Bewertungen

- SDM Module IDokument28 SeitenSDM Module IKiran KrishnanNoch keine Bewertungen

- 486 Sps 103Dokument61 Seiten486 Sps 103Samuel MarquezNoch keine Bewertungen

- Presentation ON: Introduction To MicroprocessorDokument20 SeitenPresentation ON: Introduction To MicroprocessorManish JangidNoch keine Bewertungen