Beruflich Dokumente

Kultur Dokumente

CD 4099

Hochgeladen von

Boris AfskOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

CD 4099

Hochgeladen von

Boris AfskCopyright:

Verfügbare Formate

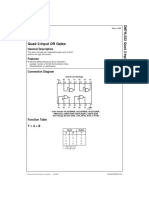

CD4099BC 8-Bit Addressable Latch

October 1987 Revised April 2002

CD4099BC 8-Bit Addressable Latch

General Description

The CD4099BC is an 8-bit addressable latch with three address inputs (A0A2), an active low enable input (E), active high clear input (CL), a data input (D), and eight outputs (Q0Q7). Data is entered into a particular bit in the latch when that bit is addressed by the address inputs and the enable (E) is LOW. Data entry is inhibited when enable (E) is HIGH. When clear (CL) and enable (E) are HIGH, all outputs are LOW. When clear (CL) is HIGH and enable (E) is LOW, the channel demultiplexing occurs. The bit that is addressed has an active output which follows the data input while all unaddressed bits are held LOW. When operating in the addressable latch mode (E = CL = LOW), changing more than one bit of the address could impose a transient wrong address. Therefore, this should only be done while in the memory mode (E = HIGH, CL = LOW).

Features

I Wide supply voltage range: 3.0V to 15V I High noise immunity: 0.45 VDD (typ.) I Low power TTL: fan out of 2 driving 74L compatibility: or 1 driving 74LS I Serial to parallel capability I Storage register capability I Random (addressable) data entry I Active high demultiplexing capability I Common active high clear

Ordering Code:

Order Number CD4099BCN Package Number N16E Package Description 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Connection Diagram

Top View

Truth Table

Mode Selection E CL L H L H L L Addressed Latch Follows Data Unaddressed Latch Holds Previous Data Addressable Latch Reset to 0 Reset to 0 Demultiplexer Clear Mode

Holds Previous Data Holds Previous Data Memory

H Follows Data H Reset to 0

2002 Fairchild Semiconductor Corporation

DS005984

www.fairchildsemi.com

CD4099BC

Logic Diagram

www.fairchildsemi.com

CD4099BC

Absolute Maximum Ratings(Note 1)

(Note 2) DC Supply Voltage (VDD) Input Voltage (VIN) Storage Temperature Range (TS) Power Dissipation (PD) Dual-In-Line Small Outline Lead Temperature (TL) (Soldering, 10 seconds) 260C (Note 2) 700 mW 500 mW

Recommended Operating Conditions (Note 2)

DC Supply Voltage (VDD) Input Voltage (VIN) Operating Temperature Range (TA) 3.0 to 15 VDC 0 to VDD VDC

0.5 to +18 VDC 0.5 to VDD +0.5 VDC 65C to +150C

55C to +125C

Note 1: Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed; they are not meant to imply that the devices should be operated at these limits. The tables of Recommended Operating Conditions and Electrical Characteristics provide conditions for actual device operation. Note 2: VSS = 0V unless otherwise specified.

DC Electrical Characteristics

Symbol IDD Parameter Quiescent Device Current VOL LOW Level Output Voltage

Conditions VDD = 5V, VIN = VDD or VSS VDD = 10V, VIN = VDD or VSS VDD = 15V, VIN = VDD or VSS |IO| 1A VDD = 5V VDD = 10V VDD = 15V

55C Min Max 5.0 10 20 0.05 0.05 0.05 4.95 9.95 14.95 1.5 3.0 4.0 3.5 7.0 11.0 0.64 1.6 4.2 0.64 1.6 4.2 0.1 0.1 3.5 7.0 11.0 0.51 1.3 3.4 0.51 1.3 3.4 4.95 9.95 14.95 Min

+25C Typ 0.02 0.02 0.02 0 0 0 5 10 15 2.25 4.5 6.75 2.75 5.5 8.25 0.88 2.25 8.8 0.88 2.25 8.8 105 105 0.1 0.1 1.5 3.0 4.0 Max 5.0 10 20 0.05 0.05 0.05

+125C Min Max 150 300 600 0.05 0.05 0.05 4.95 9.95 14.95 1.5 3.0 4.0 3.5 7.0 11.0 0.36 0.9 2.4 0.36 0.9 2.4 1.0 1.0

Units

VOH

HIGH Level Output Voltage

|IO| 1 A VDD = 5V VDD = 10V VDD = 15V V

VIL

LOW Level Input Voltage

VDD = 5V, VO = 0.5V or 4.5V VDD = 10V, VO = 1.0V or 9.0V VDD = 15V, VO = 1.5V or 13.5V VDD = 5V, VO = 0.5V or 4.5V VDD = 10V, VO = 1.0V or 9.0V VDD = 15V, VO = 1.5V or 13.5V VDD = 5V, VO = 0.4V VDD = 10V, VO = 0.5V VDD = 15V, VO = 1.5V VDD = 5V, VO = 4.6V VDD = 10V, VO = 9.5V VDD = 15V, VO = 13.5V VDD = 15V, VIN = 0V VDD = 15V, VIN = 15V

VIH

HIGH Level Input Voltage

IOL

LOW Level Output Current (Note 3)

mA

IOH

HIGH Level Output Current (Note 3)

mA

IIN

Input Current

Note 3: IOH and IOL are tested one output at a time.

www.fairchildsemi.com

CD4099BC

AC Electrical Characteristics

Symbol tPHL, tPLH Parameter Propagation Delay Data to Output tPLH, tPHL Propagation Delay Enable to Output tPHL Propagation Delay Clear to Output tTLH, tTHL Propagation Delay Address to Output tTHL, tTLH Transition Time (Any Output) TWH, TWL Minimum Data Pulse Width tWH, tWL Minimum Address Pulse Width tWH Minimum Clear Pulse Width tSU Minimum Set-Up Time Data to E tH Minimum Hold Time Data to E tSU Minimum Set-Up Time Address to E tH Minimum Hold Time Address to E CPD CIN Power Dissipation Capacitance Input Capacitance

(Note 4)

Conditions Min Typ 200 75 50 200 80 60 175 80 65 225 100 75 100 50 40 100 50 40 200 100 65 75 40 25 40 20 15 60 30 25 15 0 0 50 20 15 100 5.0 7.5 Max 400 150 100 400 160 120 350 160 130 450 200 150 200 100 80 200 100 80 400 200 125 150 75 50 80 40 30 120 60 50 50 30 20 15 10 5 pF pF ns ns ns ns ns ns ns ns ns ns ns ns Units

TA = 25C, CL = 50 pF, RL = 200k, Input tr = tf = 20 ns, unless otherwise noted VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V Per Package (Note 5) Any Input

Note 4: AC Parameters are guaranteed by DC correlated testing. Note 5: Dynamic power dissipation (PD) is given by: PD = (CPD + C L) VCC2f + PQ; where CL = load capacitance; f = frequency of operation; for further details, see application note AN-90, 54C/74C Family Characteristics.

www.fairchildsemi.com

CD4099BC

Switching Time Waveforms

www.fairchildsemi.com

CD4099BC 8-Bit Addressable Latch

Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. www.fairchildsemi.com 6 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- ZAP!the Rise and Fall of AtariDokument104 SeitenZAP!the Rise and Fall of AtariMerdas ChamseddineNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- 1973 Fairchild Linear Integrated Circuits Data CatalogDokument548 Seiten1973 Fairchild Linear Integrated Circuits Data Catalogkgrhoads100% (3)

- Replay:The History of Video GamesDokument549 SeitenReplay:The History of Video GamesHarvey AquinoNoch keine Bewertungen

- Fabless Book For SemiWiki Subscribers PDFDokument217 SeitenFabless Book For SemiWiki Subscribers PDFjamesbookNoch keine Bewertungen

- Fabless Book For SemiWiki SubscribersDokument217 SeitenFabless Book For SemiWiki SubscribersJagadeshKumar100% (1)

- Microfabrication: NanotechnologyDokument646 SeitenMicrofabrication: NanotechnologycutiacelNoch keine Bewertungen

- VLSI System DesignDokument767 SeitenVLSI System DesignMr_India100% (4)

- LM494 Pulse Width Modulated Control Circuit: General Description FeaturesDokument9 SeitenLM494 Pulse Width Modulated Control Circuit: General Description FeaturesAndré Frota PaivaNoch keine Bewertungen

- DSDokument23 SeitenDSGuillermo JiménezNoch keine Bewertungen

- CM8870Dokument9 SeitenCM8870Karthik KalyanaramanNoch keine Bewertungen

- 4046Dokument14 Seiten4046dayvidmedeirosNoch keine Bewertungen

- 34063A Fuente SwuitchingDokument7 Seiten34063A Fuente SwuitchingBoris AfskNoch keine Bewertungen

- Diodo 1N4148Dokument7 SeitenDiodo 1N4148Jean Pool Quispe EspinozaNoch keine Bewertungen

- ThesisDokument242 SeitenThesisali.umrani4538Noch keine Bewertungen

- The Intel 4004 Microprocessor: What Constituted Invention?: William AsprayDokument12 SeitenThe Intel 4004 Microprocessor: What Constituted Invention?: William AsprayKokipro KokiproNoch keine Bewertungen

- Philippine Economic Zone Authority: List of Operating Registered Enterprises - Cebu AS OF 30 JUNE 2009Dokument86 SeitenPhilippine Economic Zone Authority: List of Operating Registered Enterprises - Cebu AS OF 30 JUNE 2009Leyte Cebu HomesNoch keine Bewertungen

- Case Study on Strategy Development at Intel from Memory Chips to MicroprocessorsDokument6 SeitenCase Study on Strategy Development at Intel from Memory Chips to MicroprocessorsKyaw KyawNoch keine Bewertungen

- A History of The Invention of The Transistor and Where It Will Lead UsDokument9 SeitenA History of The Invention of The Transistor and Where It Will Lead UstthenryNoch keine Bewertungen

- FQPF8N80CDokument11 SeitenFQPF8N80CWsad WsadNoch keine Bewertungen

- MB6S DatasheetDokument3 SeitenMB6S Datasheetnonyabizness2003Noch keine Bewertungen

- EE105 - Fall 2015 Microelectronic Devices and Circuits: Prof. Ming C. Wu Wu@eecs - Berkeley.edu 511 Sutardja Dai Hall (SDH)Dokument14 SeitenEE105 - Fall 2015 Microelectronic Devices and Circuits: Prof. Ming C. Wu Wu@eecs - Berkeley.edu 511 Sutardja Dai Hall (SDH)Kulanthaivelu RamaswamyNoch keine Bewertungen

- Fairchild Channel F Instructions PDFDokument2 SeitenFairchild Channel F Instructions PDFDanNoch keine Bewertungen

- LM336-5.0/LM336B-5.0: Programmable Shunt RegulatorDokument6 SeitenLM336-5.0/LM336B-5.0: Programmable Shunt RegulatorLiver Haro OrellanesNoch keine Bewertungen

- M3054MDokument1 SeiteM3054MMuhammad MajidNoch keine Bewertungen

- Lista de Precios Yim S.A.C. 21-12-20 (20+4)Dokument27 SeitenLista de Precios Yim S.A.C. 21-12-20 (20+4)ivelha publicidadNoch keine Bewertungen

- EC501 - 1 - Intro - History (Compatibility Mode)Dokument20 SeitenEC501 - 1 - Intro - History (Compatibility Mode)Naishadh BhavsarNoch keine Bewertungen

- Fdc658ap 103298Dokument6 SeitenFdc658ap 103298Alan jorgeNoch keine Bewertungen

- Fairchild Ll4007 PDFDokument1 SeiteFairchild Ll4007 PDFKathyNoch keine Bewertungen

- Datasheet fgd4536Dokument8 SeitenDatasheet fgd4536BraulioCoroNoch keine Bewertungen

- They Would Be GodsDokument13 SeitenThey Would Be Godsanon-52108100% (1)

- RURG3020CC: 30 A, 200 V, Ultrafast Dual DiodeDokument5 SeitenRURG3020CC: 30 A, 200 V, Ultrafast Dual DiodeHadeedAhmedSher0% (1)

- Pengenalan Teknologi Rangkaian Terintegrasi: Eka Maulana, ST, MT, Meng. Adharul Muttaqin, S.T., M.TDokument35 SeitenPengenalan Teknologi Rangkaian Terintegrasi: Eka Maulana, ST, MT, Meng. Adharul Muttaqin, S.T., M.TMuhammad FauzanNoch keine Bewertungen

- DM74LS32 Quad 2-Input OR Gates: General DescriptionDokument6 SeitenDM74LS32 Quad 2-Input OR Gates: General DescriptionTIERRA LIBERTADNoch keine Bewertungen

- Mpsa42 PDFDokument5 SeitenMpsa42 PDFpeti5_1Noch keine Bewertungen

- Sses Computer 6 Melc 1 Week 1Dokument13 SeitenSses Computer 6 Melc 1 Week 1Ioan Khin LucioNoch keine Bewertungen