Beruflich Dokumente

Kultur Dokumente

PLL

Hochgeladen von

rohit_raj210 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

29 Ansichten25 SeitenOriginaltitel

Pll

Copyright

© Attribution Non-Commercial (BY-NC)

Verfügbare Formate

DOCX, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

29 Ansichten25 SeitenPLL

Hochgeladen von

rohit_raj21Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 25

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-1

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

LECTURE 090 PLL DESIGN EQUATIONS AND PLL

MEASUREMENTS

(Reference [2, Previous ECE6440 Notes])

Objective

The objective of this presentation is

1.) To provide a summary of relationships and equations that can be used to design

PLLs.

2.) Illustrate the design of a DPLL frequency synthesizer

3.) Show how to make measurements on PLLs

Outline

PLL design equations

PLL design example

PLL measurements

Summary

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-2

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

PLL DESIGN EQUATIONS

Introduction

The following design equations are to be used in designing PLLs and apply both to

LPPLs and DPLLs with the following definitions:

LPLLs: N = 1 and = 1

where N is the divider in the feedback loop and is the loop expansion factor

determined by the type of PFD.

Loop gain = K =

KdKoF(0)

N =

KvF(0)

N

Goal of these equations:

Permit the basic design of an LPLL or DPLL.

These notes are taken from PLL Design Equations Notes by R.K Feeney, July 1998

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-3

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Type I, First-Order Loop (F(0) = 1)

Crossover frequency (frequency at which the loop gain is 1 or 0dB):

(c = K (radians/sec.)

-3dB Bandwidth (frequency at which the closed-loop gain is equal to 3dB):

Closed loop transfer function =

K

s + K (-3dB = K (radians/sec.)

Noise Bandwidth:

Bn = !

0

|H(j2f)|2df =

! ] ]

0

K2

K2+(2f)2

df =

K

2

! ] ]

0

K

K2+(2f)2

d(2f) =

K

2

2

=

K4

(Hz)

Hold Range:

(H = NK

Lock (Capture) Range:

(L = (H = NK

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-4

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Type-I, First-Order Loop (F(0) = 1) - Continued

Steady-State Phase Error:

For a sinusoidal phase detector, ss = lim

t

\(t) = sin-1

. | | |

(osc

NK

For a nonsinusoidal (digital) phase detector, ss = lim

t

\(t) =

(osc

NK o

The steady-state error is never larger than . A larger error indicates a failure to

lock.

Frequency Acquisition Time:

Ta =

1K

(sec.)

For a Type-I loop,

Lock Range and Acquisition Time = Hold Range and Acquisition Time.

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-5

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Type-I, Second-Order Loop

This type of loop is generally implemented with a lag-lead filter as shown below.

Vf

R1

R2

C

+

-

Vd

+

-

|F(j()| dB

0dB

1

(1

1

(2

(1

(2

dB

Fig. 090-01 log10(()

-20 dB/decade

Filter Transfer Function:

F(s) =

1+(2s

1+(1s where (1 = (R1+R2)C and (2 = R2C

(Note: The definition for (1 = (R1+R2)C which is different from that in Lecture

050)

System Parameters:

(n =

K

(1 and | =

(n

2

. | |

(2 +

1K

=

1

2

1

K(1

(1+(2K)

Note that because (2 < (1, we see that

(n

2K < | <

K2+(n

2

2(nK

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-6

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Type-I, Second-Order Loop Continued

Crossover Frequency:

The general close-loop frequency response for high-gain loops is,

H(s) =

2s|(n + (n

2

s2 + 2|(ns + (n

2 =

1

1+

s2

2|(ns + (n

2

=

1

1+Loop Gain

The crossover frequency, (c, is the frequency when the loop gain is unity.

4

(c

4

(n

4+4|2(n

2(c

2 = 1 (c

4 (4|2(n

2)(c

2 - (n

4 = 0

Solving for (c gives,

(c = (n 2|2 + 4|4+1

3dB Bandwidth:

(-3dB = (n b + b2+1 where b = 2|2 + 1 -

(n

K

. | | |

4| -

(n

K

Noise Bandwidth:

Bn =

(n

2

. | |

| +

1

4| (Hz)

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-7

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Type-I, Second-Order Loop Continued

Hold Range:

(H = NK at the output (H = K at the input

Lock Range:

(L =

(2

(1 (H =

(2

(1 NK

Lock Time:

The lock time is set by the loop natural frequency, (n and is

TL =

2

(n

Pull-in Range:

(P = N 2 2|(nKF(0)-(n

2 at the output (P = 2 2|(nKF(0)-(n

2 at the input

This formula is only valid for moderate or high loop gains, i.e. KF(0) o 0.4(n.

Pull-in Time:

TP H

4

. | | |

fosc

N

2

Bn

3 H

2

16

(osc

2

|(n

3 Note that (H o (osc o (P

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-8

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Type-I, Second-Order Loop Continued

Frequency Acquisition Time:

Ta = TP + TL

If the frequency step is within the lock limit (one beat), then the pull-in time is

zero.

Steady-State Phase Error to a frequency step of (osc:

For a sinusoidal phase detector, ss = lim

t

\(t) = sin-1

. | | |

(osc

NK

For a nonsinusoidal (digital) phase detector, ss = lim

t

\(t) =

(osc

NK o

The steady-state error is o . A larger error indicates a failure to lock.

Maximum Sweep Rate of the Input Frequency:

Largest sweep rate of the input frequency for which the loop remains in lock.

d(()

dt = (n

2

. |radians/sec|

sec

Maximum Sweep Rate for Aided Acquisition:

This is the case when the VCO is externally swept to speed up acquisition.

d(()

dt =

(n

2

2

. ||

radians/sec

sec

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-9

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Type-2, Second-Order Loop

This type of PLL system generally uses the active PI filter as shown below.

R1

+

-

R2 C

Vf

+

-

Vd

+

-

|F(j()| dB

1

(2

R1

R2 dB

log10(()

Fig. 2.1-05

-20 dB/decade

(1

(2 =

Filter Transfer Function:

F(s) = -

1 + s(2

s(1

= -

. | | |

(2

(1

. | | |

s + 1/(2

s = -

. | | |

R2

R1

. | | |

s + 1/(2

s where (1 = R1C and (2 = R2C

System Parameters:

(n =

K

(1 and | =

1

2 K(2

R2

R1

=

1

2(2

K

(1 =

(2(n

2

3dB Bandwidth:

(-3dB = (n 2|2 + 1 + (2|2 + 1)2 +1

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-10

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Type-2, Second-Order Loop Continued

Noise Bandwidth:

Bn =

(n

2

. | |

| +

1

4| or Bn =

1

4

. | | |

K

R2

R1

+

1

(2

Hold Range:

Limited by the dynamic range of the loop components.

Lock (Capture) Range:

(H = N2|(n

Lock (Capture) Time:

TL =

2

(n

Pull-in Range:

The pull-in range is the frequency range beyond the lock (capture) range over

which

the loop will lock after losing lock (skipping cycles).

The pull-in range for a 2nd or higher order, type-2 loop is theoretically infinite

and

limited by the amplifier and phase detector offsets and by the dynamic range of the

loop.

A system with large offsets and a large frequency error may never lock.

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-11

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Type-2, Second-Order Loop Continued

Pull-in Time:

TP = (2

. | | |

(osc

N

K

R2

R1

- sin\

where \ is the initial phase difference between the reference and VCO signals.

Assume sin\o = -1 for the worst case.

Pull-out Range:

(PO H 1.8N(n(1 + |) at the output

(PO H 1.8(n(1 + |) at the input

Frequency Acquisition Time:

Ta = TP + TL

If the frequency step is within the lock limit (one beat), then the pull-in time is

zero.

Steady-state Phase Error:

The steady-state phase error of a type-2 system is zero for both a phase step and a

frequency step.

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-12

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Type-2, Second-Order Loop Continued

Steady-state Phase Error Continued:

The steady-state phase error due to a frequency ramp of (osc radians/sec./sec. is,

For a sinusoidal phase detector, ss = lim

t

\(t) = sin-1

( ( (

. | | |

R1

R2

(2

d(osc

dt

NK

For a nonsinusoidal (digital) phase detector, ss = lim

t

\(t) =

( ( (

. | | |

R1

R2

(2

d(osc

dt

NK o

The steady-state error is o . A larger error indicates a failure to lock.

Maximum Sweep Rate of Input Frequency:

Largest sweep rate of the input frequency for which the loop remains in lock.

d((in)

dt = (n

2

. |radians/sec|

sec

Maximum Sweep Rate for Aided Acquisition:

This is the case when the VCO is externally swept to speed up acquisition.

d((osc)

dt =

N

2(2

. | | |

4Bn -

1

(2

. ||

radians/sec

sec

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-13

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

DESIGN OF A 450-475 MHz DPLL FREQUENCY SYNTHESIZER

Specifications

Design a DPLL frequency synthesizer that meets the following specifications:

Frequency Range: 450 475 MHz

Channel Spacing: 25 kHz

Modulation: FM from 300 to 3000 Hz

Modulation Deviation: 5kHz

Loop Type: Type 2

Loop Order: Second order

VCO Gain: Ko = 1.25MHz/V = 7.854 Mradians/sec./V

Phase Detector Type: PFD ( = 2)

Phase Detector Gain: Kd = 0.796 V/radian

(This example will be continued later in more detail concerning phase noise and

spurs)

Note on channel spacing:

Carsons rule BW of an FM signal is H 2[fc + fm(max)] = 2(5kHz+3kHz) =

16kHz

If we assume a 9 kHz guard band, then

Channel Spacing = 9 kHz + 16 kHz = 25 kHz

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-14

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

PLL System

Block Diagram:

Kd F(s)

\1 \e

\2'

vfm

(2

Ko

1s

1N

\2

Phase Detector

PFD + Charge Pump+Filter

Fig. 090-02

vd

The pertinent transfer function for this problem is given as

(2(s)

Vfm(s) which is found as

(2(s) = Ko

( ( (

Vfm(s) + F(s)Kd

. | | |

\1 -

(2(s)

sN = Ko

( ( (

Vfm(s) + F(s)Kd\1 -

F(s)Kd

sN (2(s)

Setting \1 = 0 gives

(2(s)

Vfm(s) =

Ko

1+

F(s)KdKo

sN

PLL System - Continued

The charge-pump + filter combination has a transfer function given as

F(s) =

1+(2s

(1s

The final form of the closed-loop transfer is given as

(2(s)

Vfm(s) =

Ko

1+

(1+(2s)KdKo

s2N(1

=

s2Ko

s2 +

KdKo(2

N(1

s +

KdKo

N(1

=

s2Ko

s2 + 2|(n s + (n

2

where,

(n =

KdKo

N(1

and | =

(2

2

KdKo

N(1

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-16

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Finding the Loop Parameters

1.) Division Ratio

Nmin =

450 MHz

25 kHz = 18,000 and Nmax =

475 MHz

25 kHz = 19,000

2.) Loop Bandwidth

To pass the 300Hz lower frequency limit, we require that the maximum 3dB

frequency is 300Hz. Therefore, BL = 300Hz.

3.) Damping Constant

For reasons discussed previously, we select | = 0.707. Let us check to see if this is

consistent with the design.

We know that,

| =

(2

2

KdKo

N(1

| =

k

N

4 |max =

k

Nmin

and |min =

k

Nmax

|max = |min

Nmax

Nmin

= 1.0274|min

Also, | = |max |min = 0.707, which gives

|min

2(1.0274) = 0.5 |min = 0.6976 and |max = 1.02740.6976 = 0.7167

Finding the Loop Parameters Continued

4.) Natural frequency, (n

(-3dB = (n 2|2 + 1 + (2|2 + 1)2 +1 (n =

(-3dB

2|2 + 1 + (2|2 + 1)2 +1

The maximum (n will occur at the minimum value of N and the minimum damping

factor.

Therefore,

(n(max) =

(-3dB

2|min

2 + 1 + (2| min

2 + 1)2 +1

=

2 300

2(0.6976)2 + 1 + (2(0.6976)2 + 1)

= 980 radians/sec.

(n(min) =

(-3dB

2|max

2 + 1 + (2| max

2 + 1)2 +1

= 910 radians/sec.

4 (n = (n(max) (n(min) = 944

Loop Parameter Summary:

Frequency (MHz) N (n (rads./sec.) | Bandwidth (Hz)

450.00 18,000 910 0.7167 300

475.00 19,000 980 0.6976 300

Design of the Loop Filter

The loop filter selected is the active PI using the single-ended realization below.

+

-

R1

R2 C

Vd Vf

Fig. 090-03

The transfer function is,

F(s) =

sR2C + 1

sR1C =

s(2 + 1

s(1

(1 = R1C and (2 = R2C

1.) Time constants

We will use the date for N = 18,000 to design the filter.

(1 =

KdKo

N(n

2 =

0.796 7.854x106

18,000(910)2 = 0.419 ms

(2 =

2|

(n =

2 0.7167

910 = 1.575 ms

2.) Loop filter design

Select R1 = 2.4k. which gives

C =

(1

R1

=

0.419x10-3

2.4x103 = 0.175 F and R2 =

(2

C =

1.575x10-3

0.175x10-6 = 9.0 k.

Design of the Loop Filter Continued

3.) Simulated response of the filter.

-100

-80

-60

-40

-20

0

20

40

60

1 10 100 1000 10 4 10 5

dB or Degrees

Frequency (Hz) Fig. 090-04

4.) Differential version of the filter.

+

-

R1

R2 C

Vf

Fig. 090-05

Vd R1

+

-

R2

C

R1 = 2.4k.

R2 = 9.0k.

C = 0.175F

Loop Stability

1.) Loop Gain.

The loop gain for N = 18,000 is given by

LG(s) =

KdKoF(s)

Ns =

K(s(2 + 1)

s2N(1

=

7.854x106 0.796 (1+1.575x10-3s)

0.419x10-3 18,000 s2

=

828.83x103(1+1.575x10-3s)

s2

2.) Bode Plot

-60

-40

-20

0

20

40

60

80

100

1 10 100 1000 10 4 10 5

VDB(2)

Frequency (Hz)

Cutoff

Frequency

Phase

Margin

H 68

Closed Loop Gain

A plot of the closed-loop transfer function of

(2(j()

Vfm(j() is shown below.

0

50

100

150

200

1 10 100 1000 104 105

dB or Degrees

Magnitude

Phase

Frequency (Hz)

Bandwidth

Fig. 090-07

(We will continue this example later.)

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-22

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

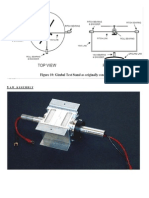

MEASUREMENT OF PLL PERFORMANCE

(The device under test in this section is the Exar XR-S200.)

Measurement of Center Frequency, fo

Cext

19 20

23

24

17

18

21

VCO

To oscilloscope

(Counter)

Ro = 10k.

2.2k.

VCO gain

+

-

vf VCO in

Fig. 2.4-01

Results:

vf =0

T/2

T/2 H 76s

or T = 152s

4 fo = 1/T = 6.54 kHz

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-23

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Measurement of the VCO Gain, Ko

Use the same measurement configuration as for fo. Vary vf and measure the output

frequency of the VCO.

Calculation of Ko.

Ko =

(

vf

=

2(6.54-5.88)

1-0 x103 = 4.13x103

1

V sec

T/2 H 85s

or T = 170s

4 fo = 1/T = 5.88 kHz

T/2

vf =0

vf =+1V

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-24

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Measurement of the Phase Detector Gain, Kd

Test circuit: Measurement Principle:

The above measurement assumes that \e = 90 so that vd = Kd sin90 = Kd

For a sinewave input, the dc output of the PD is 2/ of the peak sinusoidal voltage.

If a dc voltage is applied at the PD input of ( 2/1)x(2/) Vpeak H 0.9Vpeak, then Kd

is

simply 1/2 of the peak-to-peak output of the phase detector.

Cext

19

4

23

24

17 18

21

VCO

To oscilloscope

10k.

Ro =2.2k.

VCO

gain

VCO in

Fig. 2.4-02

Ground 6

20

0.1F

VCO out

7 3

5

10 11 8 9

Rx=0 Ry=0

X-gain Y-gain

PD in PD out

DC Level

+

-

t

PD in #1

(Pin 7)

t

t

PD in #2

(Pin 5)

PD out

(Between

Pins 3

and 4)

Kd

t

Sinewave Input- DC Input

DC level

t

t

+Kd

-Kd

Fig. 2.4-03

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-25

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Measurement of Kd Continued

v1 = 10, 20, 30 and 40 mV (rms)

More values indicate that the PD saturates at 0.4V (rms)

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-26

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Measurement of the Hold Range, (H, and the Pull In Range, (p

Measurement Circuit:

The measurement requires

a full functional PLL. The

loop filter must be added

which in this case consists of

both on-chip and external

components.

1.) To measure fH, start with a value of f1 where the loop is locked and slowly

vary f1 to

find the upper and lower values where the system unlocks.

2.) To measure fp, start with f1 at approximately the center frequency, then

increase f1

until the loop locks out. Decrease f1 until the loop pulls in. The difference between

this

value of f1 and fo is fp.

Cext=8.2nF

19

4

23

24 21

VCO

To oscilloscope

10k.

VCO in

Fig. 2.4-04

20

0.1F

VCO out

7 3

5

10 11 8 9

Rx=0 Ry=0

X-gain Y-gain

PD in R1=6k. PD out C=20nF

+

-

Loop filter

Signal

Generator

v1

v2

f1

Y1

Y2

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-27

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Measurement of (H and (p Continued

Loop out of lock Loop on the threshold of lock

Loop locked

v1

v2

v2

v1

v2

v1

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-28

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Measurement of (n, |, and the Lock Range (L

Test circuit:

Waveforms:

Parameter extraction:

With A1=1.9, A2=1.4, | =

ln(A1/A2)

2+[ ln(A1/A2)]2 and (n =

2

T 1-|2 | = 0.8 and fn = 4.1kHz

vd

v2'

Signal

Generator

FM

Input

Output

Square

Wave

Generator H 1kHz vf

v1

vz

PD Lowpass

Filter

VCO

v1

H 70kHz

To

Oscilloscope

Fig. 2.4-05

v1

vf

Modulating

square wave

T

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-29

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Measurement of (n, |, and the Lock Range (L Continued

Measurement of (L:

1.) The signal generator is adjusted to generate two frequencies, (high and (low such

that,

(high > (o + (p

2.) Set (low = (high (the amplitude of the square wave generator will be zero)

3.) Decrease (low.

4.) When (low H (o + (L, the PLL will lock.

4 (L H (low - (o

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-30

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Measurement of the Phase Transfer Function, H(j()

Since most signal generators are not phase modulated, use a frequency modulated

signal generator instead as follows.

Test circuit:

Signal

Generator

FM

Input

Output vf H H(j()

PD Lowpass

Filter

VCO

To oscilloscope or

spectrum analyzer

Fig. 2.4-06

Sinusoidal (m

Generator

FM signal

Principle:

(1 = (o + ( sin(mt \1(t) = !

0

t

(1dt = -

(

(m cos (mt |\1(j()| =

(

(m

H(j() =

\2(j()

\1(j() and VCO gain at (m \2(j() =

Ko

j(m

Vf(j(m)

4 | H(j()| =

KoVf(j(m)

(

What about (?

As long as ( is small enough, the PD operates in its linear region and vf(t) is an

undistorted sinewave (see next slide).

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-31

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Measurement of H(j() Continued

( small enough for linear operation. ( too large for linear operation.

Implementation:

1.) Can plot the frequency response point-by-point.

2.) Use a spectrum analyzer

Sweep generator rate << Spectrum analyzer

sweep rate

Watch out that resonance peaks in the

response dont cause nonlinear operation.

Typical results:

(-3dB

(

,H(j(),

H(0)

0.707H(0)

Fig. 2.4-07

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-32

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

Measurement of H(j() Continued

Timing relationship between the sweep generator and the spectrum analyzer:

t(secs.)

Frequency

10kHz

0 1 2 3 4 5 98 99 100

0

Spectrum

Anaylzer

t(secs.)

Frequency

10kHz

0 1 2 3 4 5 98 99 100

0

Sweep

Generator

Fig. 2.4-08

Basically, fm should approximate a constant during one sweep period of the

analyzer.

Problem due to resonance peaks that cause nonlinear operation:

Marker

0 dB

0 dB

Marker

Linear Nonlinear

Lecture 090 PLL Design Equations & PLL Measurements (5/22/03) Page 090-33

ECE 6440 - Frequency Synthesizers P.E. Allen - 2003

SUMMARY

PLL Design Equations

Basic design equations for

- Type-I, first-order loop

- Type-I, second-order loop

- Type-II, second-order loop

Design of a 450-475 MHz DPLL Frequency Synthesizer

PFD plus Charge Pump

Design of active PI filter

Stability

Measurements of PLL Performance

How to experimentally measure the various performance parameters of a PLL

Das könnte Ihnen auch gefallen

- Implementation of BPCS in StegnographyDokument12 SeitenImplementation of BPCS in Stegnographysanga_sravanthiNoch keine Bewertungen

- KecaDokument21 SeitenKecarohit_raj21Noch keine Bewertungen

- Sensordevices 2013 10 30 20140Dokument6 SeitenSensordevices 2013 10 30 20140rohit_raj21Noch keine Bewertungen

- Detailed RequirementsDokument4 SeitenDetailed Requirementsrohit_raj21Noch keine Bewertungen

- Base PaperszgdDokument7 SeitenBase Paperszgdrohit_raj21Noch keine Bewertungen

- Detailed RequirementsDokument4 SeitenDetailed Requirementsrohit_raj21Noch keine Bewertungen

- Sunmodule Solar Panel 250 Mono Ds PDFDokument2 SeitenSunmodule Solar Panel 250 Mono Ds PDFrohit_raj21Noch keine Bewertungen

- MethodDokument1 SeiteMethodrohit_raj21Noch keine Bewertungen

- Cover LetterDokument1 SeiteCover Letterrohit_raj21Noch keine Bewertungen

- PcaDokument33 SeitenPcarohit_raj21Noch keine Bewertungen

- AW SsemblyDokument10 SeitenAW Ssemblyrohit_raj21Noch keine Bewertungen

- Snap 2Dokument1 SeiteSnap 2rohit_raj21Noch keine Bewertungen

- ResumeDokument3 SeitenResumerohit_raj21Noch keine Bewertungen

- Mechanical ProjectsDokument6 SeitenMechanical Projectsrohit_raj21100% (1)

- Antivirus ReportDokument126 SeitenAntivirus Reportrohit_raj21Noch keine Bewertungen

- Network Log ManagmentDokument31 SeitenNetwork Log Managmentrohit_raj21Noch keine Bewertungen

- Data Security and Transmission Over Wireless Networks: Mr. Nidheesh NDokument35 SeitenData Security and Transmission Over Wireless Networks: Mr. Nidheesh Nrohit_raj21Noch keine Bewertungen

- Text 2 SpeechDokument18 SeitenText 2 SpeechSiddharth JaiswalNoch keine Bewertungen

- Project ListDokument2 SeitenProject Listrohit_raj21Noch keine Bewertungen

- RinkiDokument1 SeiteRinkirohit_raj21Noch keine Bewertungen

- Antivirus ReportDokument126 SeitenAntivirus Reportrohit_raj21Noch keine Bewertungen

- Remaining ProjectsDokument1 SeiteRemaining Projectsrohit_raj21Noch keine Bewertungen

- Text 2 SpeechDokument18 SeitenText 2 SpeechSiddharth JaiswalNoch keine Bewertungen

- Criteria Decision Analysis 7, 34-47, 1998Dokument1 SeiteCriteria Decision Analysis 7, 34-47, 1998rohit_raj21Noch keine Bewertungen

- For New Project in NetbeansDokument4 SeitenFor New Project in Netbeansrohit_raj21Noch keine Bewertungen

- Y Ignou: It's A Biggest University in World Its Very Beautiful UniversityDokument4 SeitenY Ignou: It's A Biggest University in World Its Very Beautiful Universityrohit_raj21Noch keine Bewertungen

- Text MiningDokument1 SeiteText Miningrohit_raj21Noch keine Bewertungen

- 50acfassignment Unit 2 3Dokument1 Seite50acfassignment Unit 2 3rohit_raj21Noch keine Bewertungen

- BTH 2013 AdapaDokument61 SeitenBTH 2013 Adaparohit_raj21Noch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Cellular and Mobile Communication-Lecture 1Dokument33 SeitenCellular and Mobile Communication-Lecture 1Jumanne AllyNoch keine Bewertungen

- Company Profile Perushaan TelekomunikasiDokument33 SeitenCompany Profile Perushaan TelekomunikasiDendy Baskhara PutraNoch keine Bewertungen

- Fortinet EMEA Channel 40mins Webinar FortiSASE Q42022Dokument27 SeitenFortinet EMEA Channel 40mins Webinar FortiSASE Q42022sadique010Noch keine Bewertungen

- Communication Protocols Devices Available in The MarketDokument199 SeitenCommunication Protocols Devices Available in The MarketSujit Kumar BaratNoch keine Bewertungen

- Exercice Sujet BTS 1Dokument2 SeitenExercice Sujet BTS 1ivan_segNoch keine Bewertungen

- 19 - Introduction To Cyber Security OR Information Security (Coll. & Dept.) PDFDokument5 Seiten19 - Introduction To Cyber Security OR Information Security (Coll. & Dept.) PDFBrijbhushan ChavanNoch keine Bewertungen

- CSC541 Fall2015 QuestionBankDokument12 SeitenCSC541 Fall2015 QuestionBankAmanuel TadeleNoch keine Bewertungen

- Akamai CaseStudy AudiDokument2 SeitenAkamai CaseStudy AuditrinityneoNoch keine Bewertungen

- Samsung 6G VisionDokument46 SeitenSamsung 6G Visionstart-up.roNoch keine Bewertungen

- White Paper c11 737899 PDFDokument23 SeitenWhite Paper c11 737899 PDFtrinnychackocrNoch keine Bewertungen

- Grundig Illion DectDokument47 SeitenGrundig Illion DectΓεωργία ΓιαννακοπούλουNoch keine Bewertungen

- Ati F/T DevicenetDokument29 SeitenAti F/T Devicenetelmacuarro5Noch keine Bewertungen

- KNX 100G - Setup Guide: E G H C D FDokument4 SeitenKNX 100G - Setup Guide: E G H C D FSkrapNoch keine Bewertungen

- HandoverDokument21 SeitenHandovernadiraraihanNoch keine Bewertungen

- PNP-64 Thermal PrinterDokument8 SeitenPNP-64 Thermal PrinterSougata DasNoch keine Bewertungen

- UMTS-900 MHZ PDFDokument20 SeitenUMTS-900 MHZ PDFNino BongoyNoch keine Bewertungen

- Home Products & Services Microwave Radio Pasolinkseries: Pasolink NeoDokument2 SeitenHome Products & Services Microwave Radio Pasolinkseries: Pasolink NeoDeny SetiadyNoch keine Bewertungen

- Computer Network Fundamentals - EngineeringDokument98 SeitenComputer Network Fundamentals - Engineeringc pardha krishnaNoch keine Bewertungen

- SONY HCD-G2BNiP, G2NiP PDFDokument84 SeitenSONY HCD-G2BNiP, G2NiP PDFboroda2410100% (4)

- Leslie Turner CH 14Dokument34 SeitenLeslie Turner CH 14AYI FADILLAHNoch keine Bewertungen

- Course Overview: Waleed EjazDokument44 SeitenCourse Overview: Waleed EjazMuskaan KalraNoch keine Bewertungen

- Customer Training Catalog Course Descriptions: HUAWEI Learning ServiceDokument45 SeitenCustomer Training Catalog Course Descriptions: HUAWEI Learning ServicegobinathNoch keine Bewertungen

- Global Area Network (GAN) ConceptDokument17 SeitenGlobal Area Network (GAN) ConceptAlejandro SalcidoNoch keine Bewertungen

- YUVDokument13 SeitenYUVs_paraisoNoch keine Bewertungen

- WiringAccessoriesLIST PDFDokument5 SeitenWiringAccessoriesLIST PDFReginald D. De GuzmanNoch keine Bewertungen

- Electronic Communication: Amplitude Modulation (AM)Dokument15 SeitenElectronic Communication: Amplitude Modulation (AM)prithuNoch keine Bewertungen

- Zxr10 2900 SeriesDokument262 SeitenZxr10 2900 SeriesShelton SizibaNoch keine Bewertungen

- User Manual: Smart Alarm System & AppDokument41 SeitenUser Manual: Smart Alarm System & AppEduardo Jose Fernandez PedrozaNoch keine Bewertungen

- Cisco Catalyst 1000 Series BrochureDokument5 SeitenCisco Catalyst 1000 Series Brochurearif dwi nurcahyoNoch keine Bewertungen

- OptiX RTN 980L IP Longhaul Hardware DescriptionDokument50 SeitenOptiX RTN 980L IP Longhaul Hardware DescriptionJcarlo Rodriguez67% (3)