Beruflich Dokumente

Kultur Dokumente

Computer Organization

Hochgeladen von

Swetha VanamOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Computer Organization

Hochgeladen von

Swetha VanamCopyright:

Verfügbare Formate

www.jntuworld.

com

www.jwjobs.net

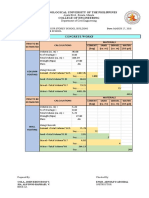

Code No: 09A61002

R09

(Common to EIE, ICE)

SET-1

Max. Marks: 75

B. Tech III Year II Semester Examinations, April/May - 2012 COMPUTER ORGANIZATION Time: 3 hours Answer any five questions All questions carry equal marks --1.a) b) Describe i) assembler ii) complier iii) interpreter Represent decimal number 4593 in i) Excess 3 code and ii) as a binary number What are memory reference instruments ? Explain with examples. Write short notes on stock organization.

[15]

2.a) b) 3.a) b) 4.a) b)

What are the functional parts of a micro instruction format? Draw the block diagram depicting address selection for control memory.

What are the different methods available for dividing numbers ? Explain. Prove that the multiplication of two n - digit numbers in base v gives a product no more than 2n digits in length. [15] Show by the means of a block diagram a 8Mx32 memory using 512k x 8 memory chips. Explain i) associative mapping ii) set associate mapping iii) direct mapping. [15] What are the different functions of an I/ o inter face? What is the basic advantage of using interrupt initiated data transfer over transfer under program control without an interrupt. [15] What is a structural hazard? Explain with an example. Give an example of a program that will cause data conflict in a three segment pipeline. [15] Explain i) mutual exclusion ii) critical section iii) hardware lock Differentiate between serial arbitration logic and parallel arbitration logic.

5.a) b)

6.a) b)

7.a) b)

T N

W U

********

R O

D L

[15]

[15]

8.a) b)

[15]

www.jntuworld.com

www.jntuworld.com

www.jwjobs.net

Code No: 09A61002

R09

(Common to EIE, ICE)

SET-2

Max. Marks: 75

B. Tech III Year II Semester Examinations, April/May - 2012 COMPUTER ORGANIZATION Time: 3 hours Answer any five questions All questions carry equal marks --1.a) b) 2.a) b) 3.a) b) 4.a) b) 5.a) b) 6.a) b) 7.a) b) 8.a) b) Compare the merits and demerits of assembly language and high level language. Convert the hexa decimal F3A7C2 to binary and octal.

[15]

What are the basic differences between a branch instruction, a call subroutine instruction and a program interrupt? Explain about the program status word. [15] What are the address sequencing capabilities required in a control memory? Explain with a block diagram the decoding of micro operation fields. [15] Write short notes on Decimal Arithmetic unit. Draw the flow chart for multiplication of floating - point numbers.

Write short notes on i) write buffer ii) prefetching . What are the different types of magnetic memory? Describe each briefly.

Explain with a timing diagram an input data transfer using hand shake scheme. Explain the working of a daisy chain priority interrupt. [15] Explain the basic concepts of instruction pipeline. What is an array processor? What are the different types of array processors? [15] What is cache coherence and why is it important in shared memory multiprocessor systems. Explain i) Cross bar networks ii) Multistage networks [15]

T N

W U

*********

R O

D L

[15]

[15]

www.jntuworld.com

www.jntuworld.com

www.jwjobs.net

Code No: 09A61002

R09

(Common to EIE, ICE)

SET-3

Max. Marks: 75

B. Tech III Year II Semester Examinations, April/May - 2012 COMPUTER ORGANIZATION Time: 3 hours Answer any five questions All questions carry equal marks --1.a) b) 2.a) b) 3.a) b) 4.a) b) 5.a) b) What are EBC DIC codes? How many characters can be represented by these codes? Discuss over flow and underflow phenomena which occurs in a digital computer. [15] What are the main types of interrupt that cause a break in the normal execution of a program? List the important differences between RISC and CISC architecture. [15] Explain the usage of a control address register. What are the various parameters which control a conditional branch decision? [15] Show the hardware implementation for Booths algorithm. Show that there can be no mantisa overflow after a multiplication operation. [15] Discuss the advantages and disadvantages of making the size of the cache blocks larger or smaller. What is memory inter leaving? How does it reduce the block transfer time? Explain. [15] What is a bus arbitration? Explain i) centralized arbitration ii) distributed arbitration. Explain IEEE 1394 standard for high speed serial data transfer.

6.a) b) 7.a) b) 8.a)

Write short notes on i) Precise exception ii) Imprecise exception. What kind of exception is provided in case of external interrupts? Explain Attached array processor. [15] Discuss the difference between tightly coupled multiprocessors and loosely coupled multiprocessor from the view point of hardware organization and programming techniques. How does a hypercube inter connection work? [15] ********

T N

W U

R O

D L

[15]

b)

www.jntuworld.com

www.jntuworld.com

www.jwjobs.net

Code No: 09A61002

R09

(Common to EIE, ICE)

SET-4

Max. Marks: 75

B. Tech III Year II Semester Examinations, April/May - 2012 COMPUTER ORGANIZATION Time: 3 hours Answer any five questions All questions carry equal marks --1.a) b) 2.a) b) 3.a) b) What is a multi processor system? What are the similarities between a multi processor and a multi computer? How is a negative number represented? Represent 7 in a binary format. [15] What is the difference between a software interrupt and a sub routine call. How is the state of the CPU determined at the end of the execute cycle?

What are the micro instructions needed for a fetch routine? What are steps that a control must undergo during the execution of a single instruction? [15] Implement a 2- circuit by 2 bit array multiplier using combinational circuit. Explain with a block diagram for a BCD adder. [15] What are replacement algorithms ? Explain any one in detail? What is a memory is it used? What are its functions?

4.a) b) 5.a) b) 6.a) b)

Write briefly about i) subroutine ii) interrupt service routine. Why does the DMA have priority over the CPU when both request a memory transfer? [15] What are the different ways in which branch instructions can be handled to reduce their negative impact on the rate of execution of instructions? Give an example of a program that will cause a branch penalty in a three segment pipeline. [15]

7.a) b)

T N

W U

********

R O

D L

[15]

[15]

8.a)

b)

What is the purpose of a system bus controller ? Explain how the systems can be designed to distinguish between references to local memory and references to common shared memory. What is cache coherence? Explain. [15]

www.jntuworld.com

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Empowerment Technology/ Prelim: 11-A, B, AND C Nadia G. Refil 09464199149Dokument44 SeitenEmpowerment Technology/ Prelim: 11-A, B, AND C Nadia G. Refil 09464199149John Carlo Cabiles MellizaNoch keine Bewertungen

- Advanced Product Quality Planning (APQP)Dokument15 SeitenAdvanced Product Quality Planning (APQP)José AlcocerNoch keine Bewertungen

- Researchpaper Design of ALU Using Reversible Logic Based Low Power Vedic MultiplierDokument5 SeitenResearchpaper Design of ALU Using Reversible Logic Based Low Power Vedic MultiplierSwetha VanamNoch keine Bewertungen

- Finalpublishedpaperoriginal PDFDokument10 SeitenFinalpublishedpaperoriginal PDFSwetha VanamNoch keine Bewertungen

- Full Swing Gate Diffusion Input Logic - Case Study of Low Power CLA Adder DesignDokument9 SeitenFull Swing Gate Diffusion Input Logic - Case Study of Low Power CLA Adder DesignSwetha VanamNoch keine Bewertungen

- 6193398 (1)Dokument111 Seiten6193398 (1)Swetha VanamNoch keine Bewertungen

- 1ea7 PDFDokument6 Seiten1ea7 PDFSwetha VanamNoch keine Bewertungen

- 6193398 (1)Dokument111 Seiten6193398 (1)Swetha VanamNoch keine Bewertungen

- Kishore 2017Dokument5 SeitenKishore 2017Swetha VanamNoch keine Bewertungen

- Optical Fibers Communication: Debanshu Ghosh Aeie Batch (F-Y) Roll No.: 40Dokument24 SeitenOptical Fibers Communication: Debanshu Ghosh Aeie Batch (F-Y) Roll No.: 40Swetha VanamNoch keine Bewertungen

- 52.design of Sequence Detector Using Mealey and Moore Finite State Machines.Dokument1 Seite52.design of Sequence Detector Using Mealey and Moore Finite State Machines.Swetha VanamNoch keine Bewertungen

- Optimize Design of Full Subtractor Using 45nm Technology: Swetha S, Reddy NSS and Hemalatha RDokument5 SeitenOptimize Design of Full Subtractor Using 45nm Technology: Swetha S, Reddy NSS and Hemalatha RSwetha VanamNoch keine Bewertungen

- Bee Lab ManualDokument62 SeitenBee Lab ManualSwetha VanamNoch keine Bewertungen

- Introduction To Programming TechnologiesDokument34 SeitenIntroduction To Programming TechnologiesSwetha VanamNoch keine Bewertungen

- Xilinx Design Reuse Methodology PDFDokument27 SeitenXilinx Design Reuse Methodology PDFvikas310Noch keine Bewertungen

- LexionAir Flyer UKDokument2 SeitenLexionAir Flyer UKficom123Noch keine Bewertungen

- 2 Concrete Works CompuDokument14 Seiten2 Concrete Works CompuALFONSO RAPHAEL SIANoch keine Bewertungen

- AICE Milestone04 03.04.2024Dokument15 SeitenAICE Milestone04 03.04.2024kevinkiprotichyegonNoch keine Bewertungen

- Coolmay: MX2N Series PLC Programming ManualDokument32 SeitenCoolmay: MX2N Series PLC Programming ManualAbel G AbelNoch keine Bewertungen

- Electronics Mechanic: Craft Instructor Training Scheme (CITS)Dokument35 SeitenElectronics Mechanic: Craft Instructor Training Scheme (CITS)Alibaba ShopNoch keine Bewertungen

- WinCNC Optiscout Operations-ManualDokument11 SeitenWinCNC Optiscout Operations-ManualRadoNoch keine Bewertungen

- Certificado Apc Iso 14001-2004 PDFDokument4 SeitenCertificado Apc Iso 14001-2004 PDFMao MartinNoch keine Bewertungen

- Event Specification GuideDokument2 SeitenEvent Specification GuideMarie Toni FondevillaNoch keine Bewertungen

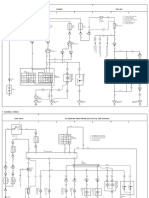

- Cpu - VTT Vcore: Gigabyte TechnologyDokument35 SeitenCpu - VTT Vcore: Gigabyte TechnologyDébo Orellano100% (1)

- 3D Construction Printing: Technical Specifications 2021Dokument3 Seiten3D Construction Printing: Technical Specifications 2021Camilo Sebastián Romero VivancoNoch keine Bewertungen

- Electric Kick Scooter SwagTron Metro SK3 Official User ManualDokument21 SeitenElectric Kick Scooter SwagTron Metro SK3 Official User ManualBruno CoutoNoch keine Bewertungen

- Installing Screen FontsDokument5 SeitenInstalling Screen Fontsg444Noch keine Bewertungen

- Exsite Ip Pant Tilt System Spec SheetDokument8 SeitenExsite Ip Pant Tilt System Spec SheetAnuj PalNoch keine Bewertungen

- Avanza Xenia Wiring DiagramDokument5 SeitenAvanza Xenia Wiring DiagramFazri Putugerah100% (2)

- Unit-2 Linear Data Structure-ArrayDokument27 SeitenUnit-2 Linear Data Structure-ArraySanskruti DhananiNoch keine Bewertungen

- 002 Gaming PC Office PC Server PC AI Data Mining Research PC SystemsDokument4 Seiten002 Gaming PC Office PC Server PC AI Data Mining Research PC SystemsBizgram AsiaNoch keine Bewertungen

- ResourcesDokument15 SeitenResourcesitsyourzsinghNoch keine Bewertungen

- ISO 14971 ChangedDokument1 SeiteISO 14971 ChangedSen MingNoch keine Bewertungen

- File HandlingDokument25 SeitenFile HandlingThe Invincible'sNoch keine Bewertungen

- DORNA EPS-B1 Servo User Manual V1.11 OcrDokument191 SeitenDORNA EPS-B1 Servo User Manual V1.11 Ocrnapo3tNoch keine Bewertungen

- I'm About To Reduce My Cost For Launching ProductsDokument1 SeiteI'm About To Reduce My Cost For Launching ProductsJose Luis FloresNoch keine Bewertungen

- 4.4.02-LineRunner-SDHDSL-LCM-DTM - E1 ExtenderDokument4 Seiten4.4.02-LineRunner-SDHDSL-LCM-DTM - E1 ExtenderIan JaredNoch keine Bewertungen

- ConveyersDokument10 SeitenConveyersSai Srinivas BodapatiNoch keine Bewertungen

- 1298Dokument136 Seiten1298Iker BasqueAdventureNoch keine Bewertungen

- How To Make Lite Versions of KONTAKT LibrariesDokument18 SeitenHow To Make Lite Versions of KONTAKT LibrariesBerlinband 237Noch keine Bewertungen

- Simple Mail Transfer ProtocolDokument29 SeitenSimple Mail Transfer ProtocolRahim AbbaNoch keine Bewertungen

- F A N T - Filtering and Noise Adding Tool: Author DateDokument4 SeitenF A N T - Filtering and Noise Adding Tool: Author DateAhmed Khalid KadhimNoch keine Bewertungen

- Sri Ramakrishna Institute of Technology, Coimbatore-10: Mechatronics QUIZ-1Dokument4 SeitenSri Ramakrishna Institute of Technology, Coimbatore-10: Mechatronics QUIZ-1Veerakumar SNoch keine Bewertungen