Beruflich Dokumente

Kultur Dokumente

Scan Synthesis Overview

Hochgeladen von

Nirmal SoniOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Scan Synthesis Overview

Hochgeladen von

Nirmal SoniCopyright:

Verfügbare Formate

Scan Synthesis

Scan Synthesis

1

Design-for-TestabiIity

Design Kit

array@cic.edu.tw

___)__ ___)__ ___)__ ___)__

Chip Implementation Center

Scan Synthesis

Scan Synthesis

2

OutIine - 01

!Introduction

!Scan Synthesis and ATPG FIow

!Scan Synthesis: Step by Step

!Case Study: Scan Synthesis

!FrequentIy Asked Commands (FACs)

!FiIe Output

!Course Review

Scan Synthesis

Scan Synthesis

3

OutIine - 02

!TetraMAX and DC XP

!TetraMAX Overview

!TetraMAX FIow

!STIL Procedure FiIe

!ATPG and FauIt Coverage

!FauIt Grading before ATPG

!Course Review

!Lab1: Scan Synthesis

!Lab2: ATPG

Scan Synthesis

Scan Synthesis

4

Introduction - 01

!Design Verification vs. Manufacturing Test

"Design Verification ensures "design" matches

intent

"Manufacturing Test ensures "parts" are

manufactured correctIy

!How is Manufacturing Test Performed?

"Automatic Test Equipment (ATE) appIies input

stimuIus to the Device Under Test (DUT) and

measure the output response.

"If the ATE observes a response different from

the expected response, the DUT faiIs that test

Scan Synthesis

Scan Synthesis

5

Introduction - 02

!Why is Manufacturing Testing Required?

"Reject the faiI parts before shipment

"Debug manufacturing process

"Improve yieId

! There are Defective Chips.

"They're not my fauIt.

"My chip was weII designed and functionaIIy

correct.

"It simuIated and synthesized just fine, but it

did not work.

Scan Synthesis

Scan Synthesis

6

Introduction - 03

!Types of Test

"Function Test: verify functionaIity

"StructuraI Test: verify manufacturabiIity

"Parametric Test: verify AC and DC parametrics

"At-Speed Test: verify performance

!Test Generation

"ManuaI: time consuming, not practicaI for

Iarge design, unpredictabIe quaIity

"ATPG: support Iarger design, predictabIe

quaIity, high test coverage

Scan Synthesis

Scan Synthesis

7

Introduction - 04

!Scan Synthesis: FuII Scan

"The most predictabIe DFT methodoIogy

"AII the fIip fIops in the design become

controIIabIe and observabIe

"Most wideIy adopted methodoIogy in industry

"EnabIe faster ATPG (combinationaI ATPG)

"Achieve the highest fauIt coverage (>95%)

# of detected faults

FauIt Coverage=

total # of faults

Scan Synthesis

Scan Synthesis

8

Introduction - 05

!Scan Synthesis: PartiaI Scan

"Not aII fIip fIops are converted to be scannabIe

"Not aII fIip fIops are controIIabIe and

observabIe

"PartiaI scan may be required for performance

and area-sensitive designs

"Requires expensive computations (sequentiaI

ATPG)

"FauIt coverage is not predictabIe

Scan Synthesis

Scan Synthesis

9

Introduction - 06

!FauIt ModeI

"Stuck-at fauIt: net is connected to Vdd or Vss

Verify the topology, not the timing, of the manufactured chip

Verify the connectivity and truth table description of each gate

"DeIay fauIt:simiIar to the stuck-at fauIt but

incIude timing effects

Named as gate delay or path delay

"Current-based fauIt:

Defects may cause high current leakage

Defects may not cause a boolean error

Named as pseudo-stuck-at fault (lDDq)

Verify the reliability problem

Scan Synthesis

Scan Synthesis

10

D

C

B

A

Z

Introduction - 07

!ExampIe: singIe stuck-at fauIt modeI

SA0

Scan Synthesis

Scan Synthesis

11

Introduction - 08

!FauIt activate

D

C

B

A

Z

SA0

1/0

Scan Synthesis

Scan Synthesis

12

Introduction - 09

!Back tracing (controIIabiIity)

D

C

B

A

Z

SA0

1/0

0

Scan Synthesis

Scan Synthesis

13

Introduction - 10

!FauIt propagation (observabiIity)

D

C

B

A

Z

SA0

1/0

0

1

1/0

Scan Synthesis

Scan Synthesis

14

Introduction - 11

!FauIt detection

"If Z(T)fauIty differs from Z(T)good

D

C

B

A

Z

SA0

1/0

0

1

1/0

1

1

X

0/1

Test Pattern T

Discrepancy

Scan Synthesis

Scan Synthesis

15

Introduction - 12

!Test SequentiaI Designs

AppIy test input at PI and set vaIue here to test SA0

SA0 occurs at here

Observe/Verify output at PO

1

0

1

0

Scan Synthesis

Scan Synthesis

16

Introduction - 13

!Test SequentiaI Designs

InitiaIize internaI nets by

shifting in pattern

SA0 occurs at here

Capture output here

1

0

1

0

SI

Z/SO

SE

Compare shifted out data here

Scan Synthesis

Scan Synthesis

17

Introduction - 14

!SimpIify sequentiaI test probIem

si

so

S

c

a

n

F

F

s

P

r

i

m

a

r

y

I

/

O

s

P

r

i

m

a

r

y

I

/

O

s

S

c

a

n

F

F

s

Scan Synthesis

Scan Synthesis

18

Introduction - 15

!Scan Test Sequence

PI

SI

PI

SE

C

B

A

D

PO

PO/SO

PO

Scan Shift Scan Shift

M

e

a

s

u

r

e

C

a

p

t

u

r

e

F

i

r

s

t

S

c

a

n

O

u

t

CLK

SE

Scan Synthesis

Scan Synthesis

19

Introduction - 16

!Scan styIes

D

Tl

TE

CP

Q

QN

MuItipIexed FIip-FIop

D

CLK

Sl

SC

Q/SO

QN

CIocked Scan FIip-FIop

D

LSSD

C

Scan_in

A

B

(test_clock)

(slave_clock)

Q/scan_out

dual-port

master

latch

dual-port

slave

latch

Scan Synthesis

Scan Synthesis

20

Scan Synthesis and ATPG FIow

HDL

Code

1-Pass Scan Synthesis

1

DFT Check

3

Scan Specification

4

Scan Preview

5

Scan Chain Synthesis

6

DFT Check

7

Top-LeveI

NetIist

Scan Chain Identification

8

ATPG Configuration

9

DFT Check

10

ATPG

11

Vector Formatting

12

2

Test Configuration

Scan Synthesis

Scan Synthesis

21

Scan Synthesis FIow

set_scan_configuration

-clock_mixing

-chain_count

-disable

-bidi_mode

set_scan_path

set_scan_signal

set_scan_element

set_scan_segment

preview_scan show all

insert_scan

Specify

Preview

Synthesize

set_scan_XXXX

preview_scan

insert_scan

Scan Synthesis

Scan Synthesis

22

Step - 01

!One-Pass Scan Synthesis

"Scan circuitry can be synthesized directIy from

HDL, top-down or bottom-up, moduIe by

moduIe

"Test-ready compiIe

compile -scan

HDL Synthesis,

Scan Synthesis

and Optimization

D

CP

D

CP

SI

SE

SI

SE

HDL

description

DC XP

Tech. Lib.

Scan Synthesis

Scan Synthesis

23

Step - 02

!Test Configuration

ATE CycIe VariabIes

test_default_period =100

test_default_delay =5

test_default_bidir_delay =55

test_default_strobe =95

test_default_strobe_width =0

DefauIt Test CIock

period test_default_period

1

st

edge 0.45*test_default_period

2

nd

edge 0.55*test_default_period

Scan Synthesis

Scan Synthesis

24

Step - 03

!Check gate-IeveI scan design ruIe before

scan chain synthesis

"Inform user about potentiaI testabiIity probIem

"Identify fIip-fIops with scan design ruIe

vioIations

!DFT Check

set_test_hold

read_init_protocol

read_test_protocol

check_test

Scan Synthesis

Scan Synthesis

25

Step - 04

!Scan Specification

set_scan_configuration methodology

[style, chain_count, clock_mixing,

bidi_mode, add_lockup, replace,

disable]

set_scan_path

set_scan_signal

set_scan_element

set_scan_segment

set_scan_transparent

Scan Synthesis

Scan Synthesis

26

Step - 05

!Scan Preview

"Check your scan specification for consistency

"CompIete your scan specification

"Report scan architecture

"Using "-script" to generate a script fiIe which

specifies scan architecture

preview_scan show [script, command]

Scan Synthesis

Scan Synthesis

27

Step - 06

!Scan Chain Synthesis

"Architect scan chains

"DisabIes three states

"Conditions bi-directionaI

"BuiId scan chains

"Minimizes constraint vioIations

"Perform scan repIacement (for not test-ready

compiIe)

insert_scan

Scan Synthesis

Scan Synthesis

28

Step - 07

!Check gate-IeveI scan design ruIe after

scan chain synthesis

"Confirm there are no new DFT probIems

"Verify the scan chains synthesized operates

properIy

"Create an ATPG-ready database

!DFT Check

check_test

report_test scan_path

Scan Synthesis

Scan Synthesis

29

Step - 08

!Scan Chain Identification (When?)

"Import an existing scan design in non-db

netIist format (e.g., EDIF, VHDL, VeriIog)

"Using reset_design after scan chain

synthesis (it wiII remove the test attributes

from the design)

set_scan_configuration existing_scan true

set_signal_type

!DFT Check Again?!

"Check if you have the same testabiIity at the

top IeveI design

"Verify scan chains

Scan Synthesis

Scan Synthesis

30

Step - 09

!Examine check_test Report

"Error: serious test probIem must be resoIved

"Warning: testabiIity probIem Iower FC

"Information: more detaiIs

"Test design ruIe vioIation summary

"SequentiaI ceII summary

"Check aII vioIations

check_test -verbose

!Obtain Estimated FC

create_test_patterns -dft

Scan Synthesis

Scan Synthesis

31

Step - 10

!Test Design RuIe VioIation Summary

TotaI VioIations: 12

TopoIogy VioIation

1 combinational feedback loop violation (TEST-117)

Scan In VioIations

2 cells constant during scan violations (TEST-142)

Capture VioIations

1 clock used a data violation (TEST-131)

4 illegal path to data pin violations (TEST-478)

4 cell does not capture violations (TEST-310)

Scan Synthesis

Scan Synthesis

32

Step - 11

!SequentiaI CeII Summary

11 out of 45 sequentiaI ceIIs have vioIations

SequentiaI ceIIs with vioIations

4 Cells have parallel capture violations

2 Cells have constant values

2 Cells have scan shift violations

3 Cells are black box

SequentiaI ceIIs without vioIations

30 cells are valid scan cells

4 cells are transparent latches

Scan Synthesis

Scan Synthesis

33

Step - 12

!How to Fix DFT VioIations

"Specify proper test configuration

Constant values to be held at primary inputs

lnitialization sequences to enter a test mode

"Workaround the probIem

lnsert DFT logic to bypass the problem

"Redesign the moduIe

Avoid uncontrollable clocking

Avoid uncontrollable asyn. set/reset

Avoid uncontrollable three-state/bidir enables

"Ignore the probIem

Only if the reduction in FC is allowable

Scan Synthesis

Scan Synthesis

34

Script ExampIe - 01

!Test Synthesis Script

current_design TOP

compiIe -scan /* test-ready compiIe */

set_test_hoId 1 find (port, TM) /* set TM=1 */

check_test /* pre-scan check */

set_scan_configuration -chain_count 2 /* 2 scan chains */

set_scan_configuration -bidi_mode input /* bidir_mode=input */

set_scan_configuration -cIock_mixing mix_cIocks /* muIti-cIocks/chain */

set_scan_signaI test_scan_in -port {si1, si2} /* assign scan in port*/

set_scan_signaI test_scan_enabIe -port SE /* assign scan enabIe*/

set_scan_signaI test_scan_out -port {so1, so2} /* assign scan out */

preview_scan /* scan preview */

insert_scan /* scan synthesis */

check_test /* post-scan check */

report_test -scan_path /* scan chain report */

Scan Synthesis

Scan Synthesis

35

Bottom-Up Synthesis

!Benefits of Bottom-Up Test Synthesis

"CompIete moduIes to satisfy design

constraints

"Reduce scan synthesis runtime for Iarge

designs

"prevent DC XP from renaming the sub-designs

of the CORE

!Tips of Bottom-Up Test Synthesis

"Do NOT specify scan signaIs, mix cIock

domains

"Switch OFF the insertion of disabIe Iogic for

muItipIy-driven nets

Scan Synthesis

Scan Synthesis

36

Script ExampIe - 02

!Bottom-Up Synthesis Script

current_design A

compiIe -scan

check_test

set_scan_configuration -disabIe faIse

set_scan_configuration -cIock_mixing no_mix

preview_scan

insert_scan

check_test

.

current_design TOP

check_test

set_scan_configuration -disabIe true

preview_scan

insert_scan

Scan Synthesis

Scan Synthesis

37

Case Study - 00

!ParaIIeI CIock Buffers

!Gated CIocks

!CIock Generators

!Asynchronous Set/Reset

!Shift Registers

!Bi-directionaI Port

!CombinationaI Loops

!Latches

!BIack Box (RAMs, Unknown CeIIs)

Scan Synthesis

Scan Synthesis

38

Case Study - 01

!ParaIIeI CIock Buffers

"ParaIIeI cIock buffers is a speciaI case of a

reconvergent cIock.

"DC XP does not support reconvergent cIocks.

It can not guarantee that a cIock puIse at the

input does generate a singIe cIock puIse at the

fIip-fIop.

"To make DC XP accept paraIIeI cIock buffers

test_allow_clock_convergence = true

cIock

cIock buffer

Scan Synthesis

Scan Synthesis

39

Case Study - 02

!Gated CIocks

"Since DC XP traces back from FF cIock pins to

find the cIock port, the gate must be enabIed

using set_test_hold 1 TM

"If t is not a PI of the design, you have to induce

enabIe Iogic (OR gate) and a test mode port.

"The set_test_hold command does onIy

appIy to top IeveI input ports.

clk

TM

F1

Scan Synthesis

Scan Synthesis

40

Case Study - 03

!CIock Generators

"ATE onIy controIs the waveform for the

primary input CLK

F3

F2

F1

CLOCK_GEN

F4

CLK

UnpredictabIe

whiIe scan shifting

Scan Synthesis

Scan Synthesis

41

Case Study - 03

!CIock Generator: SoIution 1

F3

F2

F1

CLOCK_GEN

F4

CLK

TCLK

TM

Extra gate

Extra Pins

Scan Synthesis

Scan Synthesis

42

Case Study - 03

!CIock Generator: SoIution 2

F3

F2

F1

CLOCK_GEN

F4

CLK

TM

Extra gate

Extra Pin

Scan Synthesis

Scan Synthesis

43

Case Study - 04

!Asynchronous Set/Reset

"Asynchronous Set/Reset is controIIed by a

combinationaI circuit bIock

No DFT problem

DC XP determine how to control input ports to ensure all FFs

will not be Set/Reset

"Asynchronous Set/Reset is controIIed by a

sequentiaI circuit bIock

Add control logic to prevent FFs from Set/Reset in test mode

"Asynchronous Set/Reset is controIIed by a

shift register

Provide an initial test protocol to prevent FFs from Set/Reset in

test mode

Scan Synthesis

Scan Synthesis

44

Case Study - 04

!Asynchronous Set/Reset: exampIe 1

!Asynchronous Set/Reset: exampIe 2

F1

F2

res

F1

F2

res

F3

R

R

Scan Synthesis

Scan Synthesis

45

Case Study - 04

!ExampIe 1

"Add a test pin and controI Iogic such that

signaI R wiII be 1 aII the time (in test mode)

!ExampIe 2

"Set pin res as 1 and appIy two cIock puIse,

then signaI R wiII be 1 aII the time (in test mode)

set_test_hold 1 res

check_test

write_test_protocol format tpf out dut.tpf

<EDIT dut.tpf>

read_init_protocol dut.tpf

check_test -verbose

Scan Synthesis

Scan Synthesis

46

Case Study - 04

!Edit test protocoI fiIe dut.tpf

foreach_program () {

vector () {

set(all_ports, X, 0, );

}

vector (2) {

set(all_ports, 1, 0, );

set(clk, C);

}

foreach_pattern () {

}

Scan Synthesis

Scan Synthesis

47

Case Study - 05

!Shift Registers

"They are no need to be repIaced by Mux-FFs

"Designate them as scan segments

"DC XP recognizes scan segments if

You declare such structures in your design

DC XP infers scan chains it has introduced itself (in a sub-

design) to be scan segments

set_scan_segment SR access {test_scan_in \

dff1/d, test_scan_out, dff3/q} \

-contains {dff*}

preview_scan show segments

Scan Synthesis

Scan Synthesis

48

Case Study - 06

!Bi-directionaI Port

"ControI the direction of bi-directionaI ports

during test

ln this case, the direction of the ports can not change during

parallel measure and capture

set_scan_configuration bid_mode input

"Avoid contention and fIoat on bi-directionaI

ports

DC XP synthesizes disabling logic

Switch off the synthesis of disable logic if you have already

provided in your HDL design

set_scan_configuration disable false

Scan Synthesis

Scan Synthesis

49

Case Study - 07

!CombinationaI Loops

"If the Ioop is IogicaIIy broken by Iogic vaIues,

DC XP wiII not break this Ioop again

set_test_hold

lnitialization sequences

"You can override the pin seIected by

set_test_isolate user_selected_pin_name

OUT1

MUX

AND

BUF

IN1

SEL

IN2

0

1

Scan Synthesis

Scan Synthesis

50

Case Study - 08

!Latches in FIip-FIop Based Design

"No scan ceII for Iatches

"Can not be observed

"Can not be controI

"Latch ceIIs wiII not be repIaced

L1

Can't

Observe

Can't

ControI

Scan Synthesis

Scan Synthesis

51

Case Study - 08

!SeIect a Latch ModeI

SequentiaI Latch ModeI

(SequentiaI ATPG onIy)

TestabIe

UntestabIe

CombinationaI Latch ModeI

(need set_scan_transparent)

Scan Synthesis

Scan Synthesis

52

Case Study - 08

!Use CombinationaI Latch ModeI

"For fuII scan designs, using combinationaI

Iatch modeI is recommended

set_scan_transparent true <object> -existing

"No design modification is required

"The Iatch enabIe pin and its fan-in cone wiII not

be testabIe, but data input and output pins and

their fan-in and fan-out cones wiII be fuIIy

testabIe

"This modeI is vaIid onIy if the Iatch enabIe is

not connected to a test cIock

Scan Synthesis

Scan Synthesis

53

Case Study - 09

!BIack Box

"Provide functionaI test vectors to test this

bIack box

"Add a muItipIexer structure to bypass this

bIack box, but the number of input pins and

output pins usuaIIy do not match

"Add scan register around this bIack box to

isoIate it from its environment

lnput: add scan FFs

Output: add scan FFs/MUXs

Scan Synthesis

Scan Synthesis

54

Case Study - 09

!BIack Box

U

n

-

o

b

s

e

r

v

a

b

I

e

BIack Box

U

n

-

c

o

n

t

r

o

I

I

a

b

I

e

S

c

a

n

R

e

g

i

s

t

e

r

s

S

c

a

n

R

e

g

i

s

t

e

r

s

Add wrapper to improve observabiIity/controIIabiIity

scan_in

scan_out

O

b

s

e

r

v

a

b

I

e

C

o

n

t

r

o

I

I

a

b

I

e

Scan Synthesis

Scan Synthesis

55

FACs - 01

!Key of Scan Insertion

"Architect Scan Chains: chain counts, scan

ports, cIock domains, .

"Minimize constraint vioIations Ieft after scan

insertion

Disable 3 states so that exactly one driver is active during scan

shift

Set bi-directional ports to be either input or output mode during

scan shift

Create proper test clock

"BaIance scan chains

"Predict scan resuIt by preview_scan

Scan Synthesis

Scan Synthesis

56

FACs - 02

!Checking for the Existence of Scan CeIIs

"Search the Iibrary .db fiIe.

Every scan cell must have a scan input pin and a scan output

pin

test_scan_in and test_scan_out are two signal type attribute

read class.db

filter find (pin, class/*/*) \

@signal_type==test_scan_in

"Check the design ruIes

You must have a current_design defined before running the

check_test command

Warning: Target library for design contains no

scan-cell models. (TEST-224)

Scan Synthesis

Scan Synthesis

57

FACs - 03

!Checking for Scan EquivaIents

"To verify that the technoIogy Iibrary contains

scan equivaIents for the sequentiaI ceIIs in

your design.

"If not

Warning: No scan equivalent exists for cell

instance (reference). (TEST-120)

"ExampIe (check_test verbose)

Warning: No scan equivalent exists for cell

q_reg (FD1P). (TEST-120)

Scan equivalent mappings for target library are:

FJK3 -> FJK3S

Scan Synthesis

Scan Synthesis

58

FACs - 04

!Type of Scan CIock

set_scan_configuration clock_mixing no_mix

" DefauIt. DC XP wiII generates one scan chain per cIock

domain.

" A cIock domain contains aII FFs cIocked by the same

edge of a cIock.

set_scan_configuration clock_mixing mix_edges

" AIIow mixing of cIock edges within a scan chain

" DefauIt chain count equaIs the no. of cIocks

set_scan_configuration clock_mixing mix_clocks

" AIIow any arbitrary mixing of cIocks within a scan chain

" Generate equaI Iength scan chains

Scan Synthesis

Scan Synthesis

59

FACs - 05

!No. of Scan Chains

set_scan_configuration chain_count N

" DC XP wiII spiIt Iongest chains into smaIIer chains

" The scan chains probabIy wiII not have equaI Iength

!Lockup Latch

set_scan_configuration add_lockup false

" DC XP orders the FFs within a chain by cIock domain

" DC XP inserts Iockup Iatch between adjacent scan FFs if

they are triggered by different cIocks and the test cIock

waveforms are the same

Scan Synthesis

Scan Synthesis

60

FACs - 06

!Add Lockup Latch (Why?)

d

scan_in

scan_en

cIk

q

qn

d

scan_in

scan_en

cIk

q

qn

cIk1 cIk2

A

B

cIk1

cIk2

cIk1

cIk2

OK!

Big ProbIem

If not rearrange cIock domain or add Iockup Iatch

d

q

qn

en

Scan Synthesis

Scan Synthesis

61

FACs - 07

!Specify Scan Chain SignaIs

"For scan insertion: designate scan ports

set_scan_signal signal_type port port_list

"For design ruIe checking: read in ASCII netIist

set_signal_type attribute port_name

.

test_scan_cIock

test_scan_enabIe

test_scan_out

test_scan_in

SignaI_type/Attribute

Scan Synthesis

Scan Synthesis

62

FACs - 08

!Suppress RepIacement of SequentiaI CeIIs

"insert_scan repIaces aII non-vioIated

sequentiaI ceIIs for fuII-scan designs

"To prevent such repIacement for certain ceIIs

set_scan_element false cell_design_ref_list

"Identify existing Iogic as a scan segment

set_scan_segment scan_segment_name access

signal_type_pin_list contains member_list

"Scan segments impIement scan in a particuIar

scan styIe

Scan Synthesis

Scan Synthesis

63

FACs - 09

!Scan Chain Order

"The routing order is aIphanumeric by

hierarchicaI instance names, except

Explicit specification of a certain routing order

There is a direct functional connection from a FF to an output

port: it will be moved to the end of the scan chain.

Depending on your test clock definitions: FF clocked by a late

clock edge must be placed in front of FFs clocked by earlier

edge.

set_scan_path scan_chain {last FFs}

Scan Synthesis

Scan Synthesis

64

FACs - 10

!ExpIicit Scan Chain Specification

"Specify the scan chain order directIy

"Modify from existing chain

preview_scan script > scan.scr

<edit scan.scr>

include scan.scr

preview_scan show all

Scan Synthesis

Scan Synthesis

65

FACs - 11

!Routing ExampIe

set_scan_path scan1 {instA/dff*} -complete true

set_scan_path scan2 {instB, instC/dff1}

Top

ModuIe A

dff1

dff2

dff4

dff1

dff3

dff2

ModuIe C

dff1

dff

2

ModuIe B

Scan Synthesis

Scan Synthesis

66

FACs - 12

!Scan Chain Ports Requirements

"Each scan chain requires a separate scan in

and scan out port

"Scan enabIe signaI can be shared among aII

scan chains

"You can use existing functionaI pins for scan

in and scan out ports

"AIways use a dedicated pin for scan enabIe

Scan Synthesis

Scan Synthesis

67

FACs - 13

!DefauIt Scan Chain Ports

"DC XP wiII automaticaIIy generate aII ports

needed to impIement the scan chains if you

don't specify them

"DC XP wiII find a FF directIy driving an output

port, and move it to the end of the scan chain

"DefauIt scan chain port name are controIIed by

variabIe in .synopsys_dc.setup

test_scan_in_port_name_style = test_si%s%s

test_scan_out_port_name_style = test_so%s%s

test_scan_enable_port_name_style = test_se%s%s

Scan Synthesis

Scan Synthesis

68

FACs - 14

!GuideIines for Scan Ports

"IncIude the scan enabIe (and aIso test mode)

port in your top-IeveI design

This eliminates having to adjust your top-level testbench to

match the design port list after scan chain synthesis

"Set design ruIe constraints on the scan enabIe

port

This ensures that the scan enable net is being buffered during

scan synthesis

"Don't specify moduIe functionaI ports for scan

signaIs if you use bottom-up methodoIogy

Scan Synthesis

Scan Synthesis

69

FACs - 15

!GuideIines for Bottom-Up MethodoIogy

"DO NOT insert 3-states disabIe Iogic in each

moduIe, DO it at top IeveI

set_scan_configuration disable false

"Describe the correct disabIe Iogic in your HDL

code and aIways Iet disabIe set to faIse

"Specify cIock no_mix for each moduIe

Scan Synthesis

Scan Synthesis

70

FACs - 16

!DRC ReIated Commands

"Define a test mode

set_test_hold value port_list

"Define an initiaI Iogic vaIue

set_test_initial value pin_list

"Assign an unknown vaIue to a pin/ceII

set_test_isolate object_list

U1

U2

U3

U1

U2

U3

U1

U2

U3

X

X

originaI

set_test_isoIate U1/Z

set_test_isoIate U2/A

Scan Synthesis

Scan Synthesis

71

FACs - 17

!Remove Scan Specification

"Remove scan specifications made using

set_scan_configuration, set_scan_path,

set_scan_segment, and set_scan_signal

commands

remove_scan_specification [-all] [-chain

chain_name] [-configuration] [-segment

segment_name] [-signal port_name]

!Caution!

"reset_design command removes aII

constraints and attributes from a design, not

just test reIated constrains and attributes

Scan Synthesis

Scan Synthesis

72

FiIe Output

!Create Synthesized Design FiIe

wirte hierarchy format verilog output \

core_syn.v

!Create STIL ProtocoI FiIe (SPF)

test_no_three_state_contention_after_capture=true

test_default_delay=0

test_default_bidir_delay=test_default_delay

test_default_strobe=40

test_default_period=100

test_stil_netlist_format = verilog | vhdl

wirte_test_protocol format stil out core.spf

Scan Synthesis

Scan Synthesis

73

Stuff You ShouId Know

!What is scan chain?

!How the scan chain works?

!How to architect scan chain?

!How to synthesis scan chain?

!How to check a design for scan testabiIity:

identify and resoIve scan design ruIe

vioIations?

!How to estimate fauIt coverage?

TetraMAX

TetraMAX and DC XP

!Test DeveIopment Environment

VeriIog (or TG)

Library

FuII FuII- -Scan ATPG Scan ATPG

FauIt SimuIation FauIt SimuIation

TetraMAX ATPG

SimuIation

Sign-Off

SimuIation

Sign-Off

PIace & Route

PIace & Route

Test

Vectors

Scanned

NetIist

1 1- -Pass Test Pass Test

FuII FuII- -Scan DFT Scan DFT

DC Expert Plus

IDDQ, Diagnostics IDDQ, Diagnostics

Setup & Init.

FiIe (STIL)

TetraMAX Overview - 01

!Feature

"Uses existing ASIC vendor functionaI

simuIation Iibraries (VeriIog or VHDL)

"Integrated fauIt simuIator for grading

functionaI patterns

"Support RAM and ROM

"Support IDDQ pattern generation

"Provide interactive graphicaI anaIysis and

debug of DFT ruIes

"Hypertext Iinking between transcript messages

and on-Iine manuaI

TetraMAX Overview - 02

!More Feature

"Support VeriIog, EDIF, and VHDL netIist input

"Support VeriIog, WGL, and VHDL pattern input

"Support VeriIog, WGL, and VHDL pattern output

"Support STIL (input and output)

"Provide static and dynamic pattern compression

techniques

"Provide buiIt-in GZIP compression function for

reading and writing (designs, Iibraries, protocoIs,

patterns, and fauIt Iists)

TetraMAX Overview - 03

!Input Support for Designs

"Designs may be described using forms of:

VeriIog structuraI netIists

Edif structuraI netIists

VHDL structuraI netIists

Mixtures of the above

"NetIists may be either fIat or hierarchicaI

"NetIists may exist as a singIe fiIe or muItipIe

fiIes

TetraMAX Overview - 04

!Input Libraries and ATPG ModeIs

"ATPG modeIs are created directIy from the

functionaI portion of simuIation modeIs

suppIied in VHDL or VeriIog (incIuding UDP's)

"VeriIog Ianguage attributes are understood

such as: `define, `ifdef, `incIude, `ceIIdefine,

`suppress_fauIts, `enabIe_portfauIts, etc.

"BehavioraI modeIs are not understood and

generaIIy Iead to bIack boxes

"Library reader for .LIB format is not pIanned

TetraMAX's GUI

GSV TooI Bar

TetraMAX Overview - 06

!Command Input

"Command input may be specified in a number

of ways:

menus, GUI buttons, or diaIog boxes

typed at the command input Iine

read from command fiIes:

BUILD> run_command filename

startup command fiIes in the current working

directory

.tmaxrc

" Command fiIes may be nested

10

TetraMAX Overview - 07

!Command Underscores

"Commands may use underscores "_" instead of

space

BUILD> read netIist fiIe1.v

BUILD> read_netIist fiIe1.v

BUILD> rea_net fiIe1.v

"Some command arguments contain underscores,

therefore, mixing of underscores and

abbreviations may Iead to confusion

set pindata [TEst_setup|.]

set_pindata_te // IegaI

set_pindata_te_set // THIS IS ILLEGAL

11

TetraMAX Overview - 08

!Some SheII Commands

"A Iimited set of sheII commands are supported

which can be performed directIy from the

command Iine

cd, pwd, ls, cat, cp, mv,

rm, mkdir, clear

"These commands are impIemented internaIIy

so they do not match exactIy their UNIX

equivaIent commands

12

TetraMAX Overview - 09

!Log FiIes and Messages ControI

"Write Iog message to fiIe

set message log logfile_name [-replace | -append]

"Turn off dispIaying Iog message to transcript

set message [nodisplay | display]

"Stop the comments appearing in the transcript

set message [-transcript_comments | -

notranscript_comments]

"SeIect message IeveI

set message [-level expert | standard ]

13

TetraMAX Overview - 10

!HeIp command exampIes:

BUILD> help add

Add Atpg Constraints Add Atpg Gates

Add CEll Constraints Add CLocks

Add Equivalent Nofaults Add Faults

Add Net Connections Add Nofaults

Add PI Constraints Add PI Equivalences

Add PO Masks

BUILD> help read netlist

REAd NEtlist <file_name> [-Format <Edif |

VErilog | VHdl>][-Sensitive | -INSensitive] [-

Delete] [-Noabort] [-Verbose]

14

TetraMAX Overview - 11

!MAN for command reference

"Entering "man" and a command name, or a

message ID, or a DFT ruIe ID or vioIation ID wiII

open up the on-Iine heIp to the reference page

for that topic.

"ExampIes:

BUILD> man getting_started // a topic

BUILD> man add clock // a command

TEST> man report faults // a command

TEST> man z4-6 // a violation

TEST> man m69 // a message ID

15

TetraMAX Overview - 12

!Hypertext Links to On-Line HeIp

" Messages in the transcript are hypertext linked to the on-line

help manual and generally appear in an alternate color.

" Using CTRL-RMB (CTRL and Right Mouse Button) or CTRL-

H will open on-line help to the page explaining the message.

16

Command History

!Lists aII commands entered through a diaIog, or

menu, or typed at the command input

17

Stop Process

!"Submit" button changes to "Stop" whiIe

performing operation. You can abort this

operation by this "Stop" button.

!CTRL-C and CTRL-Break do the same job.

18

Dynamic ScroIIing

!You can disabIe scroII function to see

earIier text in the transcript whiIe ATPG

tooI is stiII running.

19

TetraMAX FIow - 00

TetraMAX

ATPG

TetraMAX

ATPG

DC XP

DC XP

Test

ProtocoI

Design

NetIist

STIL

Text Editor

Text Editor

EDIF

VeriIog

VHDL

VeriIog

Design

Memories

Vendor

Library

CeIIs

STIL

VeriIog

VHDL

Test

Patterns

20

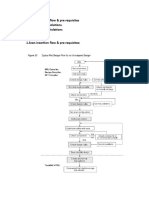

TetraMAX FIow - 01

Prep Netlist

Run ATPG

Read Design

Read Library

Build Model

Run DRC

Review

Results

Compress

Patterns

Save Patterns

Netlist

Library

DRC

DONE

Procedures

BEGIN

21

TetraMAX FIow - 02

!Read Design and Library

"Use NETLIST button or read netIist command

BUILD > read netIist mydesign.v

"NetIist type (veriIog, or VHDL, or EDIF) is auto-

detected

"NetIist compression (none, or proprietary, or

GZIP) is auto-detected

"WiIdcards '*' and '?' are support

BUILD > read netIist design/*/??design*.v

"DupIication of moduIe whiIe reading netIist, it

wiII keep the Iast moduIe encountered

22

TetraMAX FIow - 03

!BuiId the ATPG Design ModeI

"BuiId the top-IeveI moduIe in memory for

ATPG aIgorithm

top core

core

DEE

XOR

NOR2

core

nand2

DEE

XOR

NOR2

read netIist *.v

run buiId_modeI core

in memory

23

TetraMAX FIow - 04

!Perform DFT RuIes Check

run drc SPF_file

"Check Iists

The scan chains are checked for working order

during shift mode

CIocks and asyn. Set/Reset ports are checked to see

that they are controIIed onIy by PIs

CIocks/Sets/Resets are checked for off state whiIe

switching from normaI to scan shift and back again

MuIti-driver nets are checked for contention

24

TetraMAX FIow - 05

!AnaIyze RuIe VioIations

" Use ANALYZE button, seIect a vioIation, and the GSV window

wiII open to dispIay the probIem as a schematic segment

" Tracking back you see this X state comes from the TEST pin

" Was TEST pin defined as a constrained pin? Was it initiaIized

in Ioad_unIoad?

" Edit SPF and run DRC again

25

TetraMAX FIow - 06

!Generate ATPG Patterns

"After compIeting DFT ruIes checking

successfuIIy

TEST > add_faults all

TEST > run_atpg

"The transcript wiII indicate the progress of

pattern counts, fauIts detected and remaining,

and fauIt coverage

"Get a summary of resuIts

TEST > report_summaries

26

TetraMAX FIow - 07

!FauIt Grading

"Set externaI pattern

TEST > set patterns external filename

"Remove fauIt Iist then add aII fauIts

TEST > remove faults all; add faults -all

"Report summary

TEST > report summaries

"Run fauIt simuIation then report summary

again

TEST > run fault_sim sequential; rep sum

27

TetraMAX FIow - 08

!ATPG FoIIows FunctionaI Patterns

"Save remaining fauIt Iist

TEST > write faults filename all uncollapsed

replace

"Remove aII fauIts then read the remaining fauIt

Iist after fauIt grading

TEST > rem faults all

TEST > read faults filename

TEST > read faults filename retain

TEST > rep sum

"Set internaI pattern then run ATPG

TEST > set pat internal

TEST > run atpg -auto

28

TetraMAX FIow - 09

!Write Test Patterns

write patterns filename internal format <format>

"Write patterns using VeriIog/VHDL format

<format> = veriIog_singIe_fiIe|VHDL

"Write patterns using STIL format

<format> = stiI

"Write patterns using WGL format

<format> = wgI

29

SPF - 01

!STIL Procedure FiIe (SPF) and TetraMAX

"SPF fiIe provides the foIIowing info:

names of scan inputs and outputs

which pins act as "cIocks"

timing definitions for pins, cIocks, and measures

constrained ports and equivaIence reIationships

test setup sequence, the 'test_setup' macro

scan enabIe sequence, the 'Ioad_unIoad' procedure

scan shift sequence, the 'shift' procedure

other design dependent procedures: master_observe,

shadow_observe

"SPF may aIso contain pattern data

30

SPF - 02

!Create SPF

"A tempIate SPF can be created with

write drc fiIename.spf [-repIace]

"SPF reIated information can be increased by

add cIock <off_state> <port_name>

add pi constraint <held_value> <port_name>

add pi equivaIence <port_name> [-invert] <port_name>

"TerminoIogy

cIock: any signaI that affects the stored state of a

sequentiaI device

constraint: a restriction to be honored whiIe ATPG

31

SPF - 03

STIL;

ScanStructures {}

Procedures {

load_unload {

V {}

Shift {}

}

}

MacroDefs {

test_setup {}

}

!SPF consists of

" STIL header

" ScanStructures bIock

" Procedures bIock

Ioad_unIoad procedure

Shift statement

" test_setup macro is optionaI,

but may be needed to initiaIize

a particuIar design for test

mode

32

SPF - 04

!Define Chains

"Scan chains are defined in the ScanStructures

bIock of the SPF

"STIL is strongIy typed and the keywords must

be suppIied exactIy as specified with exact

uppercase/Iowercase usage

ScanStructures {

ScanChain c1 {ScanIn SI1; ScanOut SO1;}

ScanChain c2 {ScanIn SI2; ScanOut SO2;}

}

33

SPF - 05

!Check the Shift Statement

"The Shift statement defines how to shift the

scan chains by one bit position

"The "#" is a speciaI pIacehoIder which takes

on a vaIue from the scan input or scan output

data vector

"Predefined IabeIs "_si" for scan inputs and

"_so" for scan outputs

Shift {

V { _si=##; _so=##; CLOCK=P;} // pulse shift clock

}

34

SPF - 06

!Repeat String of STIL

"Use the repeat syntax for Iong strings

\r<count> string_to_repeat<space>

"ExampIe:

Shift {

V { _si=########;

_so=########; CLOCK=P;} //pulse shift clock

}

OR

Shift {

V { _si=\r8 # ; _so=\r8 # ; CLOCK=P;}

}

35

SPF - 07

!ControI Test Mode

"PIace the design into test mode usuaIIy

invoIves hoIding a specific top IeveI port to a

constant vaIue

"Define a PI constraint on the port

InitiaIize the port to its constrained vaIue in "Ioad_unIoad"

and other procedures

Add "test_setup" macro procedure

MacroDefs {

test_setup {

V { TEST_MODE=1; RESETB=0;}

V { RESETB=1;}

}

}

36

ATPG - 01

!Transcript

TEST> run_atpg

ATPG performed for 71765 faults using internal pattern source.

----------------------------------------------------------

#patterns #faults #ATPG faults test process

stored detect/active red/au/abort coverage CPU time

--------- ------------- ------------ -------- --------

Begin deterministic ATPG: abort_limit = 10...

32 50655 21110 0/0/2 71.60% 18.19

64 6954 14156 0/0/5 79.54% 28.54

96 3089 11067 0/0/7 83.08% 36.29

128 1851 9216 0/0/10 85.20% 44.29

160 1603 7613 0/0/13 87.03% 50.74

192 1538 6075 0/0/19 88.79% 58.79

224 843 5232 0/0/21 89.76% 65.13

: : : : : :

704 90 280 0/0/134 95.43% 152.32

736 72 208 0/0/134 95.51% 156.13

750 18 190 0/0/134 95.53% 157.83

37

ATPG - 02

!Summary Report

TEST > report_summaries

Uncollapsed Fault Summary Report

-----------------------------------------------

fault class code #faults

------------------------------ ---- ---------

Detected DT 83391

Possibly detected PT 54

Undetectable UD 1085

ATPG untestable AU 3742

Not detected ND 136

-----------------------------------------------

total faults 88408

test coverage 95.53%

-----------------------------------------------

Pattern Summary Report

-----------------------------------------------

#internal patterns 750

-----------------------------------------------

38

ATPG - 03

!Save ATPG Patterns

" STIL, VeriIog, WGL, VHDL,

or proprietary binary

outputs

" None or GZIP

compression

" SeriaI or ParaIIeI Form

" Compaction or not

" AII or part of patterns

" ATPG, chain test, setup,

or combo's patterns

39

ATPG - 04

!Adjust ATPG Effort

" Abort Iimit

" Capture cycIes

" Learn depth

" CPU seconds/fauIt

" CPU seconds totaI

" Pattern Iimit

" Coverage Iimit

" CIock choices

" Merge effort

" FauIt modeI

40

ATPG - 05

!ATPG Effort: Abort Limit

"Command: set atpg abort N

"DefauIt N is 10, reasonabIe range 5-1000

"During the ATPG aIgorithm certain

assumptions are made and paths sensitized in

an attempt to controI and observe fauIt

Iocations. If these assumptions are proved

faIse or Iead to bIocks then the aIgorithm

backtracks and remakes the decision untiI it

hits the "abort" Iimit

41

ATPG - 06

!ATPG Effort: Capture CycIes

"Command: set atpg capture_cycles <n>

"Suggest initiaI settings is 4. Range: 0-10

"This controIs the sequentiaI ATPG aIgorithm's

depth and defauIts to zero (off)

"This indicates the max. number of

capture_XXX procedures to be appIied

between the scan chain Ioad and unIoad

42

ATPG - 07

!ATPG Effort: Learn Depth

"Command: set atpg learn N

"DefauIt is 0, range: 0-5

"This controIs dynamic Iearning that can occur

during ATPG

"Use of this option may resuIt in excessive CPU

time for high vaIues of Iearn

43

ATPG - 08

!ATPG Effort: CPU Limit

" Command: set atpg time max_sec_per_fault

[max_sec_per_run]

" Use 0 to turn off this Iimit. DefauIt 0 0

" Use this option to Iimit the number of

CPU seconds spent on a particuIar fauIt

CPU seconds spent on the current "run atpg" command

!ATPG Effort: Pattern Limit

" Command: set atpg patterns N

" Use 0 to disabIe this Iimit. DefauIt 0

" This option enabIes the ATPG process wiII stop when

the specified number of patterns is achieved or fauIt

detection is compIeted

44

ATPG - 9

!ATPG Effort: Coverage Limit

"Command: set atpg coverage NN.N

"DefauIt is 100, usabIe range 1.0-100.0

"This controI indicates a stopping point when a

certain test coverage is exceeded

"The Iimit is checked on 32 pattern generation

boundaries so the actuaI test coverage is

usuaIIy sIightIy higher than requested

45

HeIpfuI Usage - 01

!Obtain a Quick Test Coverage

" Command: set atpg abort 5 clock any cover

100 learn 0 merge off patterns 0 time 0

0 nostore decision random

" The number of patterns is generaIIy 3X-4X greater than

the best number you might obtain for this design

" The test coverage achieved is generaIIy within 0.5% of the

best test coverage you wiII attain for this design using the

same restrictions

" Depend on the number of ND fauIts remaining, increase

the -abort_Iimit and run atpg again

46

HeIpfuI Usage - 02

!Obtain OptimaI Pattern

Count & Test Coverage

vs. Time

" Add fauIts if none are

present

" Perform "auto" run

add fault all

run atpg auto

Run one pass of static

compression

Report fauIt, test coverage,

and pattern resuIts

Report CPU time

47

Test Coverage - 01

!TetraMAX cIassifies fauIts into 11 fauIt

cIasses grouped in 5 fauIt categories

"DT: Detected

"PT: PossibIy Detected

"UD: Undetected

"AU: ATPG UntestabIe

"ND: Not Detected

48

Test Coverage - 02

!11 FauIt CIasses

" DT: detected

DS: detected by simuIation

DI: detected by impIication

" PT: possibIy detected

AP: ATPG untestabIe,

possibIy detected

NP: not anaIyzed, possibIy

detected

" UD: undetectabIe

UU: undetectabIe unused

UT: undetectabIe tied

UB: undetectabIe bIocked

UR: undetectabIe redundant

" AU: ATPG untestabIe

AN: ATPG untestabIe,

not detected

" ND: not detected

NC: not controIIed

NO: not observed

49

Test Coverage - 03

!Test Coverage is defined as

DT + (PT *posdet_credit)

Test Coverage = --------------------------------------------------

aII fauIts - (UD+(AN*au_credit))

posdet_credit = 50% (defauIt)

au_credit = 0% (defauIt)

50

SampIe Script

/* read design and library netlists */

read netlist *.v d

/* set build option and run build ATPG model */

set build black_box module

run build topmodule

run drc filename.spf

/* set fault lists, ATPG options then run ATPG */

add fault all

run atpg auto

/* write out test patterns */

write patterns file.v internal format

verilog_single_file

write patterns file.wgl internal format wgl

51

FauIt Grading before ATPG - 01

!Read in design netIist and Iibrary

read netlist *.v -d

!BuiId design modeI

run build topmodule

!Remove PI constraints

remove PI constrain -all

!Remove PI equivaIent

remove PI equiv -all

52

FauIt Grading before ATPG - 02

!Set DRC nofile

set drc -nofile

!Run DRC

run drc

!If DRC vioIation has occurred and keeps

us in DRC mode, change the severity of

DRC ruIe down to warning.

set rule xxx warn

53

FauIt Grading before ATPG - 03

!Run DRC again (You shouId enter into

TEST this time)

run drc

!Set externaI pattern source

set pattern external file.v

!Perform and observe fauIt free simuIation

run sim -seq

!Add fauIt Iist

remove faults all; add faults -all

54

FauIt Grading before ATPG - 04

!Perform fauIt simuIation

run fault_sim -seq

!Get a summary report

rep sum

!Save the fauIt Iist that exists at the end of

fauIt grade of the functionaI patterns

write faults fault.dat all uncollapsed replace

!Return to ATPG fIow

drc force

run drc file.spf

55

FauIt Grading before ATPG - 05

!Read in the fauIt Iist that existed at the

end of the functionaI pattern fauIt grade

rem faults all

read faults fault.dat

read faults fault.dat retain

!Set internaI pattern source

set pattern internal

!Run ATPG

run atpg -auto

56

FauIt Grading before ATPG - 06

!FauIt List FiIe Format

sa0 DS /U29/A1

sa0 -- /U39/A2

sa1 DI /U21/Z

sa1 -- /U29/Z

sa0 DS d2 ;comments

sa0 DS d3

sa0 -- /U01/A1

sa1 -- /U03/ZN

sa1 -- /U13/A2

sa1 -- /U14/A3

sa0 AP din

..........

!Description

" CoIumn 1: fauIt site,

may be {sa0, sa1, 0, 1}

" CoIumn 2: cIass of fauIt,

"-" indicates the fauIt

is equivaIent to the Iast

Iine before it

" CoIumn 3: pin path

name to the fauIt site

" Other test: treated as

comments

57

FunctionaI Pattern - 01

!Restrictions on functionaI patterns

" The functionaI patterns are reguIar, with the timing

changes to inputs and Iocations of cIock puIses

constant from one cycIe to the next.

" The input stimuIi, cIocks, and expected response

outputs can be broken down into a sequence of

identicaI test cycIes.

" FunctionaI test patterns must be timing insensitive

within each test cycIe.

" The design can have no race conditions.

" Patterns must be in a format acceptabIe to the ATPG

tooI.

" Bottom Iine: TetraMAX is Iimited to read the formats and

styIes that it writes.

58

Function Pattern - 02

!Function Pattern Generation

"The best way is to generate a few patterns for

the design without any defined scan chains,

then write out these patterns.

"This generates a tempIate of the format which

can be read in.

"Fit function pattern into the tempIate pattern

fiIe.

59

Design to SuccessfuI ATPG - 01

!Present some design guideIines to

faciIitate successfuI ATPG

!Suggest sources of extra ports for test I/O

60

Design to SuccessfuI ATPG - 02

!GuideIine 1: Generated PuIse SignaIs

"In test mode, ensure that cIocks or asyn. set

and reset signaIs come from a PI.

Do not use cIock dividers in ATPG test mode

Do not use gated cIocks in ATPG test mode

Do not use PLLs as cIock sources in ATPG test

mode

Do not use puIse generators in ATPG test mode

61

Design to SuccessfuI ATPG - 03

!GuideIine 2: CIock ControI

"In test mode, provide controI of cIock paths to

scan chain FFs.

CIock aIso refers to asyn. set and reset signaIs

If a cIock passes through a MUX, constrain the seIect

Iine of the MUX to a constant vaIue.

If a cIock passes through a combinationaI gate,

constrain the seIect Iine of the gate to a constant

vaIue.

Do not use bidirectionaI cIocks or asyn. set or reset

ports.

62

Design to SuccessfuI ATPG - 04

!GuideIine 3: PuIse SignaIs to Seq. Devices

"In test mode, do not aIIow a path from a puIsed

input signaI to the data input / cIock / asyn. set

/ asyn. reset of a sequentiaI device.

!GuideIine 4: MuItidriver Nets

"For muItidriver nets, ensure that one and onIy

one driver is enabIed during the shifting of

scan chains in test mode.

"PIan this guideIine into your design.

63

Design to SuccessfuI ATPG - 05

!GuideIine 5: BidirectionaI Port ControIs

"Force aII bidirectionaI ports to input mode

whiIe shifting scan chains in test mode, using

a top-IeveI port as controI.

"Force aII bidirectionaI or three-state ports to

output modeI whiIe shifting scan chains in test

mode, using a top-IeveI port as controI.

64

Design to SuccessfuI ATPG - 06

!GuideIine 6: CIock Sources, CIock Trees

and CIock Edges

"Use a singIe cIock tree to cIock aII FFs in the

same scan chain.

If the scan chain contains muItipIe cIock domains, insert

resynchronization Iatches (Iockup Iatch).

"Treat each cIock tree as a separate cIock

source.

"If possibIe, use the same cIock edge for aII FFs

in the same scan chain.

"Do not mix XNOR cIock inversion techniques

and cIock trees.

65

Design to SuccessfuI ATPG - 07

!GuideIine 7: Protection of RAMs

"DisabIe RAM write cIock or write enabIe Iine

whiIe shifting scan chain in test mode.

!GuideIine 8: RAM and ROM ControIIabiIity

"Connect RAM and ROM read and write controI

pins directIy to a top-IeveI input whiIe in test

mode.

!GuideIine 9: PuIsed SignaI to RAMs and

ROMs

"Do not aIIow an open path from a puIsed signaI

to a ROM or RAM's data, address, or controI

inputs (except read/write controI)

66

Design to SuccessfuI ATPG - 08

!GuideIine 10: Bus Keepers

"Do not aIIow a combinationaI gate path from

any puIsed port to drive the enabIe controIs of

three-state drivers that contribute to the

muItidriver net in test mode.

"WhiIe using bus keepers, ensure a no-Z state

on a muItidriver net by the end of the

Ioad_unoIad procedure.

"WhiIe using bus keepers, do not aIIow the non-

cIocked events that occur before the system

capture cIock to disturb the muItidriver net.

67

Design to SuccessfuI ATPG - 09

!Ports for TEST I/O: Suggestions

"At a minimum, onIy one extra port is required.

"The best port to redefine as scan input/output

is one that aIready feeds/comes directIy (or

nearIy) into/from a FF (in a scan chain).

"A three-state (standard) output can be

redefined as a bidirectionaI port and used in

input mode whiIe TEST asserting.

"An input port that has a minimaI amount of

fanout before entering a FF with undetected

fauIts is minimaI.

68

Stuff You ShouId Know

!Acquaint TetraMAX ATPG FIow and

TetraMAX commands

!Modify STIL Procedure FiIe for TetraMAX

!Generate scan pattern with reasonabIe

fauIt coverage

!Improve quaIity of scan pattern generated

by TetraMAX

69

References:

Scan Synthesis User Guide (Synopsys)

TetraMAX User Guide (Synopsys)

Training MateriaI of Test Synthesis and DFT with

DC XP Workshop (Synopsys)

Training MateriaI of ATPG with TetraMAX

Workshop (Synopsys)

DFT Lab

Lab. 1

!Circuit Description

"Asynchronous reset is controIIed by a

sequentiaI Iogic bIock

Add a test mode pin

"Exist a 3-bit shift register

Prevent it from scan ceII repIacement

"You can browse

www.cic.edu.tw/~array/dftIab.htmI

to downIoad pre-compiIed circuit database.

"This Iab works onIy if 0.35um ceII Iibrary

provide by CIC is adopted.

Lab. 1 - 01

!Scan Synthesis for circuit with

asynchronous reset and shift register

"CompiIe circuits as scan-ready netIist.

"Check testabiIity. Something wrong?

"Set CUT into test mode.

"Check testabiIity again. Is the probIem resoIved?

"Set scan configuration.

"Preview scan routing.

"ImpIement scan chain routing.

"Does shift register have repIaced the scan ceII as

non-scan ceII?

Lab. 1 - 02

"If not, go back to scan chain configuration.

"Use set_scan_element false ... and

set_scan_segment ... to prevent shift register

from scan ceII repIacement.

"Preview scan chain routing. Any different?

"ImpIement scan chain routing.

"Does shift register have repIaced the scan ceII

as non-scan ceII? If yes, go ahead.

"Check testabiIity again. Something wrong?

Lab. 1 - 03

"If not, estimate fauIt coverage and pattern

number. Do they meet your criteria?

"Write out STIL procedure fiIe (SPF) and

synthesized netIist.

"Now Scan Synthesis is finished, you can go

through ATPG fIow and get scan pattern.

Lab. 2 - 01

!Find scan pattern for circuit with

asynchronous reset and shift register

"Read in CUT (synthesized netIist generated in

Lab1) and Iibrary netIist. Are there any error or

warning messages?

"BuiId the fauIt simuIation modeI. Are there any

error or warning messages?

"Does TetraMAX enter into DRC mode? If yes,

you can go through the foIIowing procedures.

"Run design ruIe checking using STIL

procedure fiIe generated in Lab1. Are there any

error or warning messages?

Lab. 2 - 02

"Does TetraMAX enter into TEST mode? If yes,

you can go ahead and run ATPG procedure.

"Add fauIt Iist.

"Run ATPG. You wiII obtain fauIt coverage and

pattern number. Do you want to compact them?

"How many patterns? What is the fauIt

coverage? What is the count of the totaI fauIt?

"Do you satisfy the current resuIt? If yes, you

can write the test patterns out now; if not, try

to improve it.

Das könnte Ihnen auch gefallen

- Vasu DFTDokument28 SeitenVasu DFTsenthilkumarNoch keine Bewertungen

- Lock Up Latch in VLSIDokument8 SeitenLock Up Latch in VLSIsandy_711100% (1)

- What Is DFT in VLSIDokument22 SeitenWhat Is DFT in VLSINaga Nithesh100% (4)

- DFT Interview Questions1Dokument34 SeitenDFT Interview Questions1rajkumar gunjaNoch keine Bewertungen

- Scan Insertion - Week2&3Dokument48 SeitenScan Insertion - Week2&3VENKATRAMAN100% (1)

- DFT VisionDokument18 SeitenDFT VisionNaganithesh Ghattamaneni0% (1)

- 10 Commandments Scan Design High Coverage TestingDokument42 Seiten10 Commandments Scan Design High Coverage TestingSivaramakrishna Anumolu67% (3)

- Design For Testability and Design For Testability and Built Built - in Self in Self - Test TestDokument74 SeitenDesign For Testability and Design For Testability and Built Built - in Self in Self - Test TestSyed Waqas Arif Shah100% (1)

- Post-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Dokument10 SeitenPost-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Amena FarhatNoch keine Bewertungen

- DFT QuestionsDokument8 SeitenDFT QuestionsNaga NitheshNoch keine Bewertungen

- Scan and ATPG Process GuideDokument422 SeitenScan and ATPG Process Guideonlyexperiment100% (3)

- Synopsys DFT UGDokument375 SeitenSynopsys DFT UGDarshan Harish100% (8)

- DFT Rules - PPT 0Dokument18 SeitenDFT Rules - PPT 0prakashthamankar50% (4)

- DFT Test Point InsertionDokument21 SeitenDFT Test Point Insertionnoor_dcetNoch keine Bewertungen

- Memory BIST Training Workbook: Software Version 8.2004 - 1 February 2004Dokument268 SeitenMemory BIST Training Workbook: Software Version 8.2004 - 1 February 2004PradeepRoyal100% (3)

- Tetra MaxDokument75 SeitenTetra MaxVinay KothaNoch keine Bewertungen

- MBIST BasicsDokument91 SeitenMBIST BasicsKrish GokulNoch keine Bewertungen

- Gate Level SimulationsDokument6 SeitenGate Level SimulationsJyothi ShrinivasNoch keine Bewertungen

- DFT - CLK - Mux and DFT - CLK - Chain Data SheetDokument12 SeitenDFT - CLK - Mux and DFT - CLK - Chain Data SheetRohit PatelNoch keine Bewertungen

- DFT Advantages Goals Types Cons Assignment 1Dokument12 SeitenDFT Advantages Goals Types Cons Assignment 1senthilkumarNoch keine Bewertungen

- ATPGDokument54 SeitenATPGsrikanth100% (1)

- Debug Broken Scan ChainDokument31 SeitenDebug Broken Scan ChainNitish KumarNoch keine Bewertungen

- DFTDokument28 SeitenDFTHareshPatel100% (2)

- DFT For Advanced UserDokument151 SeitenDFT For Advanced UserAnonymous UeI6DVNoch keine Bewertungen

- How scan chains work for stuck-at and delay testingDokument15 SeitenHow scan chains work for stuck-at and delay testingprakashthamankarNoch keine Bewertungen

- DFT ProtocolDokument33 SeitenDFT Protocolnoor_dcetNoch keine Bewertungen

- Mahitha Scan Insertion Observation PDFDokument30 SeitenMahitha Scan Insertion Observation PDFPrafulani Gajbhiye100% (1)

- RC DFT GuideDokument58 SeitenRC DFT GuideSivanantham Sadhasivam0% (1)

- Interview Questions For DFTDokument3 SeitenInterview Questions For DFTsumitzz4737100% (1)

- DFT Interview Questions and Answers: 1. Re: Handling Reset During Transition Fault Pattern GenerationDokument10 SeitenDFT Interview Questions and Answers: 1. Re: Handling Reset During Transition Fault Pattern GenerationShankhadeep DasNoch keine Bewertungen

- Q-A's On Atpg & ScanDokument33 SeitenQ-A's On Atpg & ScanShankhadeep Das100% (2)

- DFTDokument14 SeitenDFTRahulNoch keine Bewertungen

- Lab2 Block Level SSN Insertion On Processor CoreDokument33 SeitenLab2 Block Level SSN Insertion On Processor Corezys WdNoch keine Bewertungen

- DftdocumentDokument66 SeitenDftdocumentSumanth Nayak100% (1)

- Compression NotesDokument10 SeitenCompression NotesSurendra Lovely Surendra50% (2)

- Scan Insertion Labs GuidelinesDokument12 SeitenScan Insertion Labs GuidelinessenthilkumarNoch keine Bewertungen

- Synthesis Guide Very GoodDokument332 SeitenSynthesis Guide Very GoodAtif Ammed SyedNoch keine Bewertungen

- Timing SimulationDokument3 SeitenTiming SimulationKarthik Sharma100% (1)

- EDTDokument47 SeitenEDTRaghavendra MatturNoch keine Bewertungen

- DFT Strategy For IPsDokument11 SeitenDFT Strategy For IPsumeshNoch keine Bewertungen

- Scan Insertion Lab Observation (K.S.K.S.sarma)Dokument33 SeitenScan Insertion Lab Observation (K.S.K.S.sarma)Kittu Krishna100% (2)

- Training On EDT (1) - Copy (1) (3) 1Dokument52 SeitenTraining On EDT (1) - Copy (1) (3) 1veena100% (1)

- Synopsys PrimeTime - Introduction To Static Timing Analysis WorkshopDokument21 SeitenSynopsys PrimeTime - Introduction To Static Timing Analysis WorkshopApoorva Bhatt100% (2)

- DFT Interview QuestionsDokument2 SeitenDFT Interview Questionsrupesh kumar100% (1)

- PrimeTime SlidesDokument47 SeitenPrimeTime SlidesRamakrishnaRao SoogooriNoch keine Bewertungen

- Atpg Lab Notes PDFDokument11 SeitenAtpg Lab Notes PDFrajkumar gunja100% (1)

- Atpg Coverage LossDokument4 SeitenAtpg Coverage LossUmesh ParasharNoch keine Bewertungen

- DFT Interview QuestionsDokument5 SeitenDFT Interview QuestionsHardik TrivediNoch keine Bewertungen

- Atpg Answer Name: Meet ZankatDokument5 SeitenAtpg Answer Name: Meet ZankatMeet ZankatNoch keine Bewertungen

- DFT Interview Questions - Welcome To World of VLSIDokument5 SeitenDFT Interview Questions - Welcome To World of VLSINaganithesh GhattamaneniNoch keine Bewertungen

- Atpg Overview: Ashokraj YellamrajuDokument37 SeitenAtpg Overview: Ashokraj Yellamrajuashokraj108100% (2)

- What is Static Timing Analysis (STADokument173 SeitenWhat is Static Timing Analysis (STAAtul100% (3)

- Scan Insertion FlowDokument9 SeitenScan Insertion Flowsharath ANoch keine Bewertungen

- DFT Interview QsDokument4 SeitenDFT Interview QsHARISH DAMARLANoch keine Bewertungen

- VLSI Test Principles and Architectures: Design for TestabilityVon EverandVLSI Test Principles and Architectures: Design for TestabilityBewertung: 4.5 von 5 Sternen4.5/5 (4)

- System-on-Chip Test Architectures: Nanometer Design for TestabilityVon EverandSystem-on-Chip Test Architectures: Nanometer Design for TestabilityNoch keine Bewertungen

- Formal Verification: An Essential Toolkit for Modern VLSI DesignVon EverandFormal Verification: An Essential Toolkit for Modern VLSI DesignBewertung: 4 von 5 Sternen4/5 (4)

- Fault Tolerance and TestabilityDokument16 SeitenFault Tolerance and TestabilitySukhada DeshpandeNoch keine Bewertungen

- Lab5 Synopsys Tetramax DFTDokument20 SeitenLab5 Synopsys Tetramax DFTJay PadaliyaNoch keine Bewertungen

- Scan Test Design Methodology and Practical ResultsDokument6 SeitenScan Test Design Methodology and Practical Resultsece gate2021Noch keine Bewertungen

- DFT DataDokument1 SeiteDFT DataNirmal SoniNoch keine Bewertungen

- Readme LLDokument1 SeiteReadme LLNirmal SoniNoch keine Bewertungen

- Jtag Best and BestDokument1 SeiteJtag Best and BestNirmal SoniNoch keine Bewertungen

- FileinfoDokument1 SeiteFileinfoDhanish KumarNoch keine Bewertungen

- FlipDokument2 SeitenFlipNirmal SoniNoch keine Bewertungen

- Reference Guide: TMS320F2802x/TMS320F2802xx Piccolo System Control and InterruptsDokument139 SeitenReference Guide: TMS320F2802x/TMS320F2802xx Piccolo System Control and InterruptsBertony QuemasdaNoch keine Bewertungen

- Bus and Memory TransfersDokument14 SeitenBus and Memory TransfersDaniel RizviNoch keine Bewertungen

- VEC Question Bank for Digital Principles and System DesignDokument12 SeitenVEC Question Bank for Digital Principles and System DesignvidhyalakshmikumaranNoch keine Bewertungen

- Experiment No. 2 Introduction To Combinational Circuits: Group Name: Group 7 Group Leader: JOSE DOROSAN Group MemberDokument11 SeitenExperiment No. 2 Introduction To Combinational Circuits: Group Name: Group 7 Group Leader: JOSE DOROSAN Group MemberJoy PeconcilloNoch keine Bewertungen

- Low Complexity QCA Universal Shift Register Design Using Multiplexer and D Flip Flop Based On Electronic CorrelationsDokument15 SeitenLow Complexity QCA Universal Shift Register Design Using Multiplexer and D Flip Flop Based On Electronic CorrelationsMORIS CUBE TECH AND MORE mmmNoch keine Bewertungen

- ADC0831/ADC0832/ADC0834/ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsDokument41 SeitenADC0831/ADC0832/ADC0834/ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsSathiya KumarNoch keine Bewertungen

- LOGIC - CIRCUITS Final Exam Q2 2010 - 2011 Problems and Answer KeyDokument2 SeitenLOGIC - CIRCUITS Final Exam Q2 2010 - 2011 Problems and Answer KeySimon Gregory Mabanta100% (1)

- PCF8553 PDFDokument55 SeitenPCF8553 PDFheokbwNoch keine Bewertungen

- Ec2207 - Digital Electronics Lab ManualDokument83 SeitenEc2207 - Digital Electronics Lab ManualasrafalisNoch keine Bewertungen

- Practical DTDokument19 SeitenPractical DTKundan BhartiNoch keine Bewertungen

- Docslide - Us - Microcontrollers and Embedded Systems PDFDokument282 SeitenDocslide - Us - Microcontrollers and Embedded Systems PDFRavikumar ImadabathuniNoch keine Bewertungen

- CS8351-Digital Principles and System Design PDFDokument16 SeitenCS8351-Digital Principles and System Design PDFJabeen BanuNoch keine Bewertungen

- Low Power and Area-Efficient Carry Select Adder: K.SaranyaDokument4 SeitenLow Power and Area-Efficient Carry Select Adder: K.Saranyapraba821Noch keine Bewertungen

- TFT 17MB20 SMDokument52 SeitenTFT 17MB20 SMecureuil67100% (1)

- CST202 Module 4 Control Logic DesignDokument22 SeitenCST202 Module 4 Control Logic DesignAkhil KrishnaNoch keine Bewertungen

- Esp32-C6 Technical Reference Manual enDokument1.277 SeitenEsp32-C6 Technical Reference Manual enpetrusz1Noch keine Bewertungen

- Chapter 4 - Structural ModelingDokument56 SeitenChapter 4 - Structural ModelingPhạm Gia LongNoch keine Bewertungen

- User Guide ESI V3!02!01Dokument49 SeitenUser Guide ESI V3!02!01emreka82Noch keine Bewertungen

- Embeded PU ComputerDokument188 SeitenEmbeded PU ComputerLoknath RegmiNoch keine Bewertungen

- Array Structured MemoriesDokument74 SeitenArray Structured MemoriesnagendraNoch keine Bewertungen

- Using The Set - Clock - Sense - Stop - Propagation Command Properly With PrimeTime SIDokument3 SeitenUsing The Set - Clock - Sense - Stop - Propagation Command Properly With PrimeTime SISumanth VarmaNoch keine Bewertungen

- CWDM BrochureDokument6 SeitenCWDM BrochureW@2nNoch keine Bewertungen

- Implementation of Boolean Function Using 8:1 Multiplexer: Title of Project ReportDokument15 SeitenImplementation of Boolean Function Using 8:1 Multiplexer: Title of Project ReportRahil MukeshNoch keine Bewertungen

- DM74LS153 Dual 1-Of-4 Line Data Selectors/Multiplexers: General Description FeaturesDokument5 SeitenDM74LS153 Dual 1-Of-4 Line Data Selectors/Multiplexers: General Description FeaturesBenito GarridoNoch keine Bewertungen

- Digital Logic Formula Notes Final 1 PDFDokument12 SeitenDigital Logic Formula Notes Final 1 PDFHima SekharNoch keine Bewertungen

- CS302 Midterm Paper - 01Dokument5 SeitenCS302 Midterm Paper - 01Manish RauniyarNoch keine Bewertungen

- Chapter 3Dokument49 SeitenChapter 3Getsi JebamalarNoch keine Bewertungen

- Question Bank Ids EteDokument6 SeitenQuestion Bank Ids EteErric FanshionNoch keine Bewertungen

- Ads 7824Dokument21 SeitenAds 7824Andres Alberto Meza BrocheroNoch keine Bewertungen

- Monitoring Fermentation With An Aber Yeast MonitorDokument30 SeitenMonitoring Fermentation With An Aber Yeast MonitorBahiru Bt0% (1)