Beruflich Dokumente

Kultur Dokumente

Efficient Implementation of Hummingbird Cryptographic Algorithm On A Reconfigurable Platform

Hochgeladen von

naveednad2003556Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Efficient Implementation of Hummingbird Cryptographic Algorithm On A Reconfigurable Platform

Hochgeladen von

naveednad2003556Copyright:

Verfügbare Formate

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol.

2 Issue 7, July - 2013

Efficient Implementation of Hummingbird Cryptographic Algorithm on a Reconfigurable Platform

Kutuboddin Jinabade Dept. of Electronics & Communication KLE DR.MSSCET Belgaum, Karnataka Krupa Rasane Dept. of Electronics & Communication KLE DR.MSSCET Belgaum, Karnataka

Abstract

For the resource constrained devices such as Radio Frequency Identification (RFID) tags, smart cards and wireless sensor networks, novel ultra lightweight Hummingbird cryptographic algorithm is presented. In this paper an attempt has been made to improve the architectural area as compared to previous hardware implementation on low cost Field Programmable Gate Array (FPGA) devices. Hummingbird provides design security with small block size and it is resistant to the most common attacks. Our results are compared with FPGA implementations of the various cryptographic algorithms. The results show that the work presented in this report gives optimization with respect to area utilization and hence cost effective in comparison to the referred papers.

This paper is the reimplementation of the concept described in[1] with optimized programming in VHDL. Index Terms RFID, Cryptography, Hummingbird, Encryption, Decryption.

1. Introduction

FID tags, smart cards, and wireless sensor nodes and various such smart devices, with their wide range of applications, have gained significant importance in home automation and health care. Many applications involve complicated processing of sensitive personal information and biological data. Moreover it is necessary to maintain confidentiality as much as its necessary to process it. Thus there is an ever increasing demand for integrating cryptographic functions into embedded applications and improvising them. But the important issue that is to be considered is that the smart devices have extremely constrained resources with respect to memory, power supply etc.,

IJERTV2IS70735

IJE RT

Core

thus it is impractical to use classical cryptographic algorithms. Moreover, the tight cost constraints also bring forward impending requirements for designing new cryptographic primitives that can perform strong authentication and encryption, and provide other security functionality for ultra-low-power applications in the era of pervasive computing. This emerging research area is usually referred to as lightweight cryptography. Hummingbird is the recently proposed lightweight cryptographic algorithm. For detail description of the Hummingbird cryptographic algorithm refer[1]. The design and implementation is described in Section 2, Section 3 gives the round-based architecture of 16-bit block cipher, The results and discussion is presented in Section 4. Finally, the paper is concluded in Section 5.

2. DESIGN AND IMPLEMENTATION

In this section an encryption only core and an encryption/decryption core have been implemented on the low-cost Xilinx FPGA series Spartan-3. 2.1 Speed Optimized Hummingbird Encryption

The top-level description of an speed optimized Hummingbird encryption core is as in[1]. In our work the traditional modulus operator is replaced by XOR operation. The working of the speed optimized Hummingbird encryption core is: The initialization process begins when the chip enable signal CE changes from 0 to 1 and within four clock cycles the four rotors RSi (i = 1, 2, 3, 4) are first initialized by four 16-bit random

www.ijert.org

1879

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol. 2 Issue 7, July - 2013

2.2 Speed Optimized Hummingbird Encryption/Decryption Core

The top-level description of an speed optimized Hummingbird encryption/decryption core is as in[1]. In our work the traditional modulus operator is replaced by XOR operation. The four operation modes supported by Hummingbird encryption/decryption core are: i) Encryption only; ii) Decryption only; iii) Encryption followed by decryption; and iv) Decryption followed by encryption. The same initialization procedure is shared by both encryption and decryption routines that first takes 4 clock cycles to load four random nonce into rotors through multiplexers M5 and M11 followed by 16 clock cycles for four iterations. The architecture of the encryption/decryption core is similar to that of the encryption only core apart from the following several aspects. Firstly, while encrypting two successive plaintext blocks in the encryption-only core the rotor RS2 completes the update, But in the encryption/decryption core, every rotor is fully updated each time a plaintext block is encrypted or decrypted to support the four operation modes. Hence, in order to fully update the rotor RS2 after each encryption/ decryption, two multiplexers M10 and M11 are introduced. Secondly, we include an XOR, which facilitates the execution of the corresponding arithmetic

IJERTV2IS70735

IJE RT

NONCE through the interface RSi(15:0). From the fifth clock cycle, the core starts encryption RS1 XOR RS3 for four times and each iteration requires four clock cycles to finish encryptions by four 16-bit block ciphers as well as the internal state updating. The correct computation results to update four rotors depending on the value of a round counter are chosen by the multiplexer M5 and other multiplexers select appropriate inputs to feed the 16-bit block cipher. The full update of the rotor RS2 involves successive encryptions of two plaintext blocks to save chip area for the encryption-only core. More accurately, the rotor RS2 is updated by V12t and RS4t+1 when encrypting two successive plaintext blocks, respectively. After 20 clock cycles the initialization process completes and the READY signal changes from 0 to 1 then the first 16 bit plaintext block is read from an external register for encryption. The required cipher text is obtained from the encryption core after another four cycles and the valid output signal VO becomes high level. Consequently, after an initialization process of 20 clock cycles, the proposed speed optimized Hummingbird encryption core can encrypt one 16-bit plaintext block per 4 clock cycles.

as per the operation modes of the core. Thirdly, the correct values to the encryption and decryption routines of the 16-bit block cipher is fed using two multiplexers M7 and M8, respectively. Finally, the appropriate inputs are selected by all the other multiplexers based on the value of a round counter as well as the operation modes. This indicates that the working of the encryption/decryption core matches that of encryptiononly core. Accordingly one 16-bit plaintext or cipher text block can be encrypted or decrypted by the speed optimized Hummingbird encryption/decryption core, after an initialization process of 20 clock cycles.

3. Round-based Architecture of 16-bit Block Cipher

The round-based architecture is as in[10], is used to further reduce the chip area and power consumption. This architecture repeatedly uses only one round function block as shown in Figure 1 and also consists of four regular rounds which shares the common hardware resources of one substitution and permutation layer and the final round is composed of another substitution layer and four XORs. Therefore, there are totally 5 XORs, 8 S-boxes, and one permutation layer for the datapath. Furthermore, three 16-bit multiplexers are introduced for different purposes: i) A 4-to-1 multiplexer M1 is utilized to switch among the required round keys; ii) A 2-to-1 multiplexer M2 is employed to choose between the input and the computation result of each round; and iii) A 2-to-1 multiplexer M3 is used to export either the computation result of each round or the final ciphertext that is then stored into a 16-bit register. The whole encryption can be performed in four clock cycles for the round-based architecture.

Fig 1. Round-based Architecture of 16-bit Block Cipher

www.ijert.org

1880

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol. 2 Issue 7, July - 2013

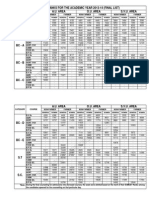

The round-based architecture of the 16-bit block cipher is implemented on the Spartan-3 XC3S200 FPGA. The area requirement of the round-based architecture is tested by four S-boxes and two implementation options, respectively. Table 1 summarizes our experimental results. Table 1: Area Requirement for the Round-based Architecture of 16-bit Block Cipher on the Spartan-3 XC3S200 FPGA in our work.

3.1 Area Optimized Hummingbird Encryption

Core

The depiction in Figure 2 shows the top-level description of an area optimized Hummingbird encryption core[10]. Working of the area optimized Hummingbird encryption core is as follows: The initialization process starts when the chip is enabled (i.e., CE = 1) and four rotors RSi (i = 1, 2, 3, 4) are first initialized by four 16-bit random nonce through the interface RSi(15:0). The message RS1 RS3 is encrypted when the core executes four iterations. To complete encryptions, four 16-bit block ciphers are executed with the 64-bit key and also updating the internal state. The 64-bit sub keys ki (i = 1, 2, 3, 4) are read from an external register based on the value of a round counter through the interfaces KEY1 (15:0) to KEY4 (15:0) and under the control of the signal KEYSEL (1:0). In addition, the corresponding inputs are also chosen from multiplexers M1, M2 and M3 and temporary registers RH, RA and RE under the control of the round counter. While the updating of four rotors is taken care by the multiplexer M1 where the appropriate operands to form the correct input of the 16-bit block cipher are selected by M2 and M3. The system initialization completes and the READY signal becomes high level. The first 16-bit plaintext block is then read from an external register for encryption. , the corresponding cipher text is obtained from the encryption core and the valid output(Vo) signal changes from 0 to 1.

IJERTV2IS70735

IJE RT

Fig 2: The Datapath of Area Optimized Hummingbird Encryption Core Using the Round-based Architecture of 16-bit Block Cipher

4. RESULTS AND DISCUSSION

A summary of our implementation results is presented in Table 2, where the area requirements (in slices) and the time period are given. All experimental results were extracted using ISE Design Suite from Xilinx on a XC3S200-5ft256 Spartan-3 platform with speed grade 5. Table 2: Implementation results of Hummingbird algorithm in our work

For the Hummingbird encryption-only core, Table 2 shows that the time period of the speed optimized implementation is 69.07 % faster than that of the area optimized implementation at the cost of additional 39 slices on the similar target platform. The speed optimized core is 91.28 % faster than traditional core

www.ijert.org

1881

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol. 2 Issue 7, July - 2013

and the area optimized core is 71.80% faster than the traditional core. The performance comparison of our Speed optimized Hummingbird implementation with the existing FPGA implementations of [1], [8], [9] and [2] are summarized in Table 3. Table 3: Performance comparison of Implementation of Cryptographic Algorithms FPGA

frequency. Thus the project presents a performance enhanced Hummingbird cryptographic algorithm with both speed and area optimization. Discussion : From the above results it can be concluded that the speed and area optimized encryption cores have better performance in terms of time period and number cryptographic algorithm with both speed and area optimization.

5. Conclusion

The Hummingbird encryption algorithm has been implemented with area optimization. The hardware implementation has been done on FPGA. The synthesis and simulation results have been compared and improvement has been observed. Compared to other lightweight FPGA implementations of block ciphers PRESENT, XTEA and AES, Hummingbird can be implemented with smaller area requirement. Consequently, Hummingbird can be considered as an ideal cryptographic primitive for resource-constrained environments. As the future research, we intend to conduct Encryption/Decryption core of Hummingbird cipher as well as propose low power ASIC implementations for low-cost RFID tags. ACKNOWLEDGMENT The performance comparison of our Area optimized Hummingbird implementation with the existing FPGA implementations of [1], [8], [9] and [2] are summarized in Table 4. Table 4: Performance Comparison of FPGA Simulation results of Cryptographic Algorithms REFERENCES

[1] X. Fan, G. Gong, K. Lauffenburger, and T. Hicks, FPGA Implementations of the Hummingbird Cryptographic Algorithm, IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), 2010 [2] P. Bulens, F.-X. Standaert, J.-J. Quisquater, and P. Pellegrin, Implementation of the AES-128 on Virtex-5 FPGAs, Progress in Cryptology - AFRICACRYPT 2008, LNCS 5023, pp. 16-26, 2008 [3] P. Chodowiec and K. Gaj, Very Compact FPGA Implementation of the AES Algorithm, The 5th International Workshop on Cryptographic Hardware and Embedded Systems - CHES 2003, LNCS 2779, pp. 319333, 2003.

The frequency increase in our work is 10.57 times more than the work[1], 6.77 times than [9] on Spartan-3 XC3S50-5, 1.27 times than [9] on Virtex-5 XC5VLX85-3, 2.16 times more than the work[2] on Spartan-3 XC3S2000-5 and 2.82 times more than the work [2] on Spartan 3.

From the analysis and comparison of results, it can be concluded that the work presented here has better area optimization than the results previously obtained and also has a better speed with tremendous increase in

IJERTV2IS70735

IJE RT

We are grateful to KLE DR M S. Sheshagiri College of engineering and Department of Electronics and communication for providing the necessary facilities for carrying out the project. We are grateful to all those who are directly or indirectly part of this paper.

www.ijert.org

1882

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol. 2 Issue 7, July - 2013

[4] D. Engels, X. Fan, G. Gong, H. Hu, and E. M. Smith, Hummingbird: Ultra-Lightweight Cryptography for Resource- Constrained Devices, to appear in the proceedings of The 14th International Conference on Financial Cryptography and Data Security - FC 2010, 2010 [5] T. Good and M. Benaissa, AES on FPGA from the Fastest to the Smallest, The 7th International Workshop on Cryptographic Hardware and Embedded Systems CHES 2005, LNCS 3659, pp. 427-440, 2005. [6] X. Guo, Z. Chen, and P. Schaumont, Energy and Performance Evaluation of an FPGA-Based SoC Platform with AES and PRESENT Coprocessors, Embedded Computer Systems: Architectures, Modeling, and Simulation - SAMOS2008, LNCS 5114, pp. 106115, 2008. [7] F. Mace, F.-X. Standaert, and J.-J. Quisquater, FPGA Implemenation(s) of a Scalable Encryption Algorithm, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 16, no. 2, pp. 212-216, 2008. [8] G. Rouvroy, F.-X. Standaert, J.-J. Quisquater, and J.-D. Legat, Compact and Efficient Encryption/Decryption Module for FPGA Implementation of the AES Rijndael Very Well Suited for Small Embedded Applications, International Conference on Information Technology: Coding and Computing - ITCC 2004, pp. 583-587, 2004. F.-X. Standaert, G. Piret, G. Rouvroy, and J.-J. Quisquater, FPGA Implementations of the ICEBERG Block Cipher, Integration, the VLSI Journal, vol. 40, iss. 1, pp. 20-27, 2007. [9] Daniel Engels, Xinxin Fan, Guang Gong, Honggang Hu, and Eric M. Smith,Ultra-Lightweight Cryptography for Low-Cost RFID Tags: Hummingbird Algorithm and Protocol,Department of Electrical and Computer Engineering University of Waterloo Waterloo, Ontario, N2L 3G1, CANADA. [10] Xinxin Fan- Efficient Cryptographic Algorithms and Protocols for Mobile Ad Hoc Networks-A Ph.d A thesispresented to the University of Waterloo, Canada.

IJERTV2IS70735

IJE RT

www.ijert.org

1883

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Popular Password Cracking ToolsDokument10 SeitenPopular Password Cracking Toolspravesh2231100% (1)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- IAPP Certification Foundation Study Guide OverviewDokument13 SeitenIAPP Certification Foundation Study Guide OverviewRenato Leite Monteiro33% (3)

- Presentation CrowdStrike Falcon Identity ProtectionDokument50 SeitenPresentation CrowdStrike Falcon Identity ProtectionAlbert gonzalez fuentesNoch keine Bewertungen

- Troubleshoot and diagnose IPsec VPN issuesDokument8 SeitenTroubleshoot and diagnose IPsec VPN issuesmipingoNoch keine Bewertungen

- Python For Reverse Engineering and Malware AnalysisDokument3 SeitenPython For Reverse Engineering and Malware AnalysisRotem SalinasNoch keine Bewertungen

- Security Metrics: Sajendra Kumar Iimt, Iet, MeerutDokument33 SeitenSecurity Metrics: Sajendra Kumar Iimt, Iet, MeerutSajendra Chaudhary100% (1)

- Informe Del Departamento de Energía de Estados Unidos: "Soluciones de Energía Resiliente para La Red de Puerto Rico"Dokument59 SeitenInforme Del Departamento de Energía de Estados Unidos: "Soluciones de Energía Resiliente para La Red de Puerto Rico"El Nuevo DíaNoch keine Bewertungen

- Java J2EE Job Interview Companion - K.arulkumaranDokument237 SeitenJava J2EE Job Interview Companion - K.arulkumaranAnu SreekumarNoch keine Bewertungen

- Coin Change ProblemDokument3 SeitenCoin Change Problemnaveednad2003556Noch keine Bewertungen

- Naveed ResumeDokument4 SeitenNaveed Resumenaveednad2003556Noch keine Bewertungen

- Problems To Ace Coding InterviewsDokument24 SeitenProblems To Ace Coding Interviewsnaveednad2003556Noch keine Bewertungen

- Career PDF CWE Clerks IV AdvtDokument34 SeitenCareer PDF CWE Clerks IV Advtnaveednad2003556Noch keine Bewertungen

- Basic GPS concept explainedDokument3 SeitenBasic GPS concept explainednaveednad2003556100% (1)

- APPSC ASOs Computer Science Paper - II - 2012Dokument18 SeitenAPPSC ASOs Computer Science Paper - II - 2012naveednad2003556Noch keine Bewertungen

- Quite SleepDokument66 SeitenQuite Sleepnaveednad2003556Noch keine Bewertungen

- PHD MPhil BrochureDokument9 SeitenPHD MPhil Brochurenaveednad2003556Noch keine Bewertungen

- Postal MtsDokument8 SeitenPostal Mtsnaveednad2003556Noch keine Bewertungen

- Englishcolorad 22.07.2014Dokument1 SeiteEnglishcolorad 22.07.2014naveednad2003556Noch keine Bewertungen

- How To Become A Great FinisherDokument2 SeitenHow To Become A Great Finishernaveednad2003556Noch keine Bewertungen

- Employment News Men Jun 2014 FinalDokument2 SeitenEmployment News Men Jun 2014 Finalnaveednad2003556Noch keine Bewertungen

- ASIC Power Groid AnalysisDokument121 SeitenASIC Power Groid AnalysisNilesh IngaleNoch keine Bewertungen

- Agriculture Last Ranks 2013-14Dokument2 SeitenAgriculture Last Ranks 2013-14Vinay ReddyNoch keine Bewertungen

- Cryptanalysis of Hummingbird-1Dokument23 SeitenCryptanalysis of Hummingbird-1naveednad2003556100% (1)

- ECE Adhoc Advt. MAy 2014Dokument2 SeitenECE Adhoc Advt. MAy 2014naveednad2003556Noch keine Bewertungen

- Sbi Assistant Clerk Notification 2014Dokument5 SeitenSbi Assistant Clerk Notification 2014Telugu VaahiniNoch keine Bewertungen

- Staff Selection Commission P&P-II Section: Notice ForDokument1 SeiteStaff Selection Commission P&P-II Section: Notice Fornaveednad2003556Noch keine Bewertungen

- IBPS PO4 CLK 4 RRB 3 CalenderDokument2 SeitenIBPS PO4 CLK 4 RRB 3 CalenderSreejith Sundar PalavilaNoch keine Bewertungen

- App Faculty Recruitment14Dokument4 SeitenApp Faculty Recruitment14naveednad2003556Noch keine Bewertungen

- The Advantages and Disadvantages of FIFO MehtodDokument5 SeitenThe Advantages and Disadvantages of FIFO Mehtodnaveednad2003556100% (1)

- Implementing Hamming Code Using VLSIDokument5 SeitenImplementing Hamming Code Using VLSInaveednad2003556Noch keine Bewertungen

- BER and SNRDokument8 SeitenBER and SNRshervinshNoch keine Bewertungen

- The Hummingbird-2 Lightweight Authenticated Encryption AlgorithmDokument14 SeitenThe Hummingbird-2 Lightweight Authenticated Encryption Algorithmnaveednad2003556Noch keine Bewertungen

- Enhanced FPGA Implementation of The Hummingbird Cryptographic AlgorithmDokument11 SeitenEnhanced FPGA Implementation of The Hummingbird Cryptographic Algorithmnaveednad2003556Noch keine Bewertungen

- Dataflow Modeling and Design For Cognitive Radio NetworksDokument6 SeitenDataflow Modeling and Design For Cognitive Radio Networksnaveednad2003556Noch keine Bewertungen

- Approved Annual Programme 2014Dokument1 SeiteApproved Annual Programme 2014Kiran KumarNoch keine Bewertungen

- 2-Lecture Notes Lesson3 6Dokument4 Seiten2-Lecture Notes Lesson3 6kstu1112Noch keine Bewertungen

- EmtechDokument13 SeitenEmtechrichNoch keine Bewertungen

- Introduction To Ethical Hacking, Ethics, and LegalityDokument18 SeitenIntroduction To Ethical Hacking, Ethics, and LegalitySad JokerNoch keine Bewertungen

- DDK Whitepaper Core2.1Dokument50 SeitenDDK Whitepaper Core2.1Masria LarawikiNoch keine Bewertungen

- Cryptography and System Security - May 2019 MUDokument1 SeiteCryptography and System Security - May 2019 MUFaraazNoch keine Bewertungen

- M. BalajiDokument53 SeitenM. BalajiCSK Marana waiterNoch keine Bewertungen

- RSA Algorithm Key ConceptsDokument13 SeitenRSA Algorithm Key ConceptsSk SharmaNoch keine Bewertungen

- Fundamental Areas of Cyber Security On Latest TechnologyDokument3 SeitenFundamental Areas of Cyber Security On Latest TechnologyEditor IJTSRDNoch keine Bewertungen

- Upp-Int Cumulative Test Units 1-10 BDokument6 SeitenUpp-Int Cumulative Test Units 1-10 BТори ПавленкоNoch keine Bewertungen

- Decentralized and Scalable Privacy-Preserving Authentication Scheme in VanetsDokument9 SeitenDecentralized and Scalable Privacy-Preserving Authentication Scheme in VanetsJackson SunnyNoch keine Bewertungen

- CSOE Certification Steps 1 PDFDokument3 SeitenCSOE Certification Steps 1 PDFApoorva BadolaNoch keine Bewertungen

- Debian-Ubuntu Hardening GuideDokument87 SeitenDebian-Ubuntu Hardening GuideadhieimoetzNoch keine Bewertungen

- Lesson 2Dokument7 SeitenLesson 2VENGIE PAMANNoch keine Bewertungen

- Cracking Wifi WPA:WPA2 Passwords Using Pyrit Cowpatty in Kali Linux - Page 3 of 4 - BlackMORE OpsDokument3 SeitenCracking Wifi WPA:WPA2 Passwords Using Pyrit Cowpatty in Kali Linux - Page 3 of 4 - BlackMORE OpstjmrgebjNoch keine Bewertungen

- Applied Crypto HardeningDokument100 SeitenApplied Crypto HardeningkorovamilkNoch keine Bewertungen

- Cse 1010eDokument13 SeitenCse 1010eKritika RamchurnNoch keine Bewertungen

- Lab Cisco 11.2.2.6Dokument4 SeitenLab Cisco 11.2.2.6Estiven ValenciaNoch keine Bewertungen

- Security SlogansDokument2 SeitenSecurity SlogansMinu C MNoch keine Bewertungen

- MTech Cyber I and II Sem SyllabusDokument24 SeitenMTech Cyber I and II Sem SyllabusDarmoni LaishramNoch keine Bewertungen

- Paxson Spring 2011 CS 161 Computer Security Final Exam: (Last) (First)Dokument18 SeitenPaxson Spring 2011 CS 161 Computer Security Final Exam: (Last) (First)Bertin BidiasNoch keine Bewertungen

- Female and Male Hacker Conferences Attendees: Their Autism-Spectrum Quotient (AQ) Scores and Self-Reported Adulthood ExperiencesDokument25 SeitenFemale and Male Hacker Conferences Attendees: Their Autism-Spectrum Quotient (AQ) Scores and Self-Reported Adulthood Experiencesanon_9874302Noch keine Bewertungen

- Guerrero Saade Raiu VB2017Dokument15 SeitenGuerrero Saade Raiu VB2017LGmnNoch keine Bewertungen

- Cryptography Hash Functions: STD Code Full Name Class MarksDokument21 SeitenCryptography Hash Functions: STD Code Full Name Class MarksBrikhov XNoch keine Bewertungen

- Alexander Polyakov - Attacking SAP Users With Sapsploit ExtendedDokument62 SeitenAlexander Polyakov - Attacking SAP Users With Sapsploit Extendedbronec10Noch keine Bewertungen