Beruflich Dokumente

Kultur Dokumente

12, Twin, Statcom

Hochgeladen von

sirageldeenOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

12, Twin, Statcom

Hochgeladen von

sirageldeenCopyright:

Verfügbare Formate

DC Voltage Controller For High Power STATCOM

Abstract: A four level static compensator integrating two 2 level converters, supplying/absorbing

reactive power to/from the grid, is reported in our earlier paper. Reduced component count, simpler

layout for switches, and smaller DC link capacitor values are the attractive features of the proposed

topology over the diode clamped and cascaded multilevel converters. This paper suggests

asymmetric twin converter topology. Suitable selection of the DC link voltage values reduces

distortion in the current fed to the grid. In addition, circuit topology is modified to avoid the split-

capacitor DC links. This reduces the number of independent DC capacitor voltages to be controlled

and eliminates the flow of third harmonic current through the transformer. In order to improve the

performance, a phase shifted carrier-based pulse width modulation technique is used. A

mathematical model of the system is derived, based on which a controller for the scheme is designed.

The effectiveness of the scheme is verified through detailed simulation study. This paper implements

with the advanced concept is Fuzzy logic. In this method of rule based decision making used for

expert systems and process control that emulates the rule of thumb thought process used by human

beings. Fuzzy logic arose from the DC voltage control and reduces the total harmonic distortion.

Keywords: Carrier Based Pulse Width Modulation (CBPWM), Pulse Width Modulation (PWM),

Static Synchronous Compensator (STATCOM), Total Harmonic Distortion (THD).

NagaRaju Pechetti

PG Scholar, Sri Vasavi Engineering College, Tadepalligudem,

West Godavari Dist, AP

Ch. Narendra Kumar

Senior Assistant Professor, Sri Vasavi Engineering College,

Tadepalligudem, West Godavari Dist, AP

Ch. Rambabu

Professor & HOD, Sri Vasavi Engineering College,

Tadepalligudem, West Godavari Dist, AP

I SSN 2319-9725

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 428

1. Introduction:

To provide transmission line voltage support, a Static Synchronous Compensator

(STATCOM) offers the optimal solution in terms of price, reliability and dynamic

performance [2], [3]. Generally, multipulse converter based [4] and multilevel converter

based [5][8] solutions are used for high power applications. A multipulse converter uses

more than one voltage source converter (VSC), with common DC link, operating with nearly

fundamental switching frequency and the output of each module is connected in series

through the multipulse transformer. By adjusting the triggering pulses of different VSCs,

specified Total Harmonic Distortion (THD) of the injected current is achieved with reduced

switching losses as compared to that of single VSC based solution. The major drawback of

this scheme is the high cost and complex structure of the bulky multipulse transformer.The

second solution is multilevel converters [5][8], which provide more than two steps in the

voltages, thereby reducing THD without switching semiconductor devices at a high

frequency. The two most commonly used schemes are diode clamped and cascaded converter

topologies. The diode clamped multilevel topology is mostly restricted to a three level

configuration because of the complex layout of the diodes (which grows as the square of the

number of levels) and the need for capacitor voltage balancing [5].

The other commonly used multilevel topology, i.e. cascaded converter topology [9][13],

comprises several single phase H bridge/full bridg converters, with separate dc links. The

following are the two associated problems of this topology:

i. The size of the DC-link capacitor required is high because the instantaneous power

involved with each module varies at twice the fundamental frequency [14] and

ii. The regulating voltage across a large number of self-supported dc-link capacitors

makes the controller design complex [12], [15][23].

To address some of the aforementioned limitations in multilevel converters, a four level

asymmetric twin converter topology based multilevel converter, shown in Fig. 1, is proposed

in [28]. This topology uses a reduced number of components (12 controlled switches with

antiparallel diodes) as compared to the diode clamped topology (18 controlled switches with

antiparallel diodes plus 18 diodes) [5]. Moreover, in this case, semiconductor switches are

arranged as VSC, which enables easier structural layout and reduced driver circuit

complexity. Therefore, standard VSC power modules [include six Insulated Gate Bipolar

Transistors (IGBTs) and their driver circuits in one package] can be used instead of discrete

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 429

components. Moreover, this topology utilizes cascade connection of three phase VSCs, and

hence, the size of the DC link capacitor is less as compared to that in cascaded H-bridge

multilevel converter. The reduced number of DC links makes voltage regulation easier as

compared to that in an equivalent cascaded converter. Comparison of diode clamped

converter, cascaded converter, and open ended transformer topologies for various parameters

is given in [1].

STATCOM (Static Synchronous Compensator), which is consists of a two level Voltage

Source Converter (VSC), a DC energy storage device, a coupling transformer connected in

shunt to the distribution network through a coupling transformer. The VSC converts the DC

voltage across the storage device into a set of three phase AC output voltages. These voltages

are in phase and coupled with the AC system through the reactance of the coupling

transformer. Suitable adjustment of the phase and magnitude of the STATCOM output

voltages allows effective control of active and reactive power exchanges between the

STATCOM and the AC system. Such configuration allows the device to absorb or generate

controllable active and reactive power. But, there are several factors that must be considered

when designing the STATCOM and associated control circuits.

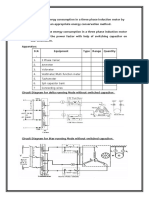

2. Proposed Methodology:

The asymmetric twin converter topology is proposed in this paper wherein only two DC links

are used without split capacitor arrangement, as shown in Fig. 1. Furthermore, the THD of

currents supplied to the grid is reduced by selecting a suitable ratio of DC link voltages of the

two VSCs. A ratio of 1:0.366 is selected based on the study of open ended induction motor

drive, which has similar power circuit configuration [25].

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 430

Figure 1: Asymmetric twin converter topology based STATCOM

In this paper, the principle of operation of the proposed scheme and a suitable pulse width

modulation (PWM) technique. Various switching states and corresponding phase voltages are

provided to justify the four level operation of the circuit. A mathematical model of the

proposed topology is describes the development of the controller. Operation of DC voltage

regulator and reactive power controller are also discussed.

A. Principle of Operation:

The proposed asymmetric-twin-converter-based multilevel topology, comprising two VSCs,

is shown in Fig. 1. Low voltage (LV) windings of the transformer are connected differentially

between two 2 level VSCs such that the voltage appearing on the LV side is the difference of

the output voltages of two VSCs. High-voltage (HV) windings, arranged in a star

configuration, are connected to the three-phase grid. Leakage inductances of the transformers

act as input filter inductances of the STATCOM. Both VSCs operate with separate DC links

to produce two level individual output. Voltages appearing on the LV windings of the

transformer are written in terms of output voltages of VSCs as

e

a

= e

a1g1

e

a2g2

+ e

g1g2

e

b

= e

b1g1

e

b2g2

+ e

g1g2

e

c

= e

c1g1

e

c2g2

+ e

g1g2

. (1)

where e

a

, e

a1g1

, e

a2g2

, and

e

g1g2

are the voltages across the LV winding of phase-a, the pole

voltage of VSC-1, the pole voltage of VSC-2, and the voltage difference between negative

DC link terminals of the two VSCs, respectively. Since both VSCs have separate DC links,

the sum of the LV winding phase currents should be zero

i

a

+ i

b

+ i

c

= 0 (2)

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 431

Furthermore, the sum of instantaneous values of grid voltages is equal to zero

V

a

+ V

b

+ V

c

= 0. (3)

The sum of the LV winding voltages is given by

LV a b c

a b c a b c a b c

HV

N d( i + i + i )

e + e + e = (v + v + v ) - r(i + i + i ) - L

N dt

(4)

where r and L are the resistance and leakage inductance as measured from the LV side,

respectively, and N

LV

/N

HV

is

the turns ratio. Substituting (2) and (3) into (4) gives

e

a

+ e

b

+ e

c

= 0. (5)

Substituting LV voltages from (1) in (5) results in

g1g2 a1g1 a2g2 b1g1 b2g2 c1g1 c2g2

1 1 1

e = - (e - e ) - (e - e ) - (e - e )

3 3 3

(6)

Substituting the value of e

g1g2

in (1) yields

a a1g1 a2g2

b b1g1 b2g2

c c1g1 c2g2

2 -1 -1

e e - e

1

e = -1 2 -1 e -e

3

e e - e

-1 -1 2

| |

| | | |

|

| |

|

| |

| | |

\ . \ .

\ .

(7)

The line voltages of the LV side e

ab

, e

bc

and e

ca

are expressed as pole voltages using (1)

ab a b a1g1 a2g2 b1g1 b2g2

bc b c b1g1 b2g2 c1g1 c2g2

ca c a c1g1 c2g2 a1g1 a2g2

e = e - e = e - e - e + e

e = e - e = e - e - e + e

e = e - e = e - e - e + e

(8)

For V

dc2

= 0.5V

dc1

, depending on the state of switches, voltage waveforms of e

ab

, e

bc

and e

ca

has seven different steps.

B. PWM Strategy:

Hence, the use of phase-shifted (PS) CB-PWM is suggested for the proposed topology This

PWM technique expects the controller to generate individual modulating waveforms for each

inverter output e

ag1

, e

b1g1

, e

c1g1

, e

a2g2

, e

b2g2

and e

c2g2.

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 432

Figure 2: Comparison of modulating and carrier waveforms for PS CB-PWM.

Each modulating waveform is compared with a carrier waveform to determine the switching

state of the corresponding inverter devices. This is similar to the PS CB-PWM technique used

in H-bridge cascaded converters [26], [27]. For two H-bridges per phase, the resultant

waveform of AC voltages is the sum of individual converter voltages. Therefore, carrier

waveforms are 180 PS from each other to cancel the carrier frequency harmonics. However,

in the case of asymmetric twin converter topology, the shift in carriers is not required because

the resultant waveform is the difference of two AC voltages. Comparison of modulating and

carrier signals for phase-a. Modulated converter voltages e

a1g1

, e

a2g2

and ea for the simulated

case of V

dc1

= 805 V, V

dc2

= 294 V, fundamental frequency f = 50 Hz, carrier frequency fc =

900 Hz, and modulation index m = 0.9 are shown in Fig. 2.

3. Development Of The Equivalent Circuit:

For the purpose of analysis, an equivalent circuit of the proposed STATCOM is derived and

is shown in Fig. 3. Transformer is represented by equivalent series combination of

inductances, resistances, and voltage sources. To model the losses in two VSCs, two

resistances r1 and r2 are placed in parallel to the two DC links.

Figure 3: Equivalent circuit diagram of the proposed STATCOM

The governing equations of the proposed system can be derived as

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 433

b

a a a a

b b

b b b b

c c c c

b

-r

0 0

L

i i -e +V

-r

S i = 0 0 i + -e +V (9)

L L

-e +V i i

-r

0 0

L

| |

|

| | | | | | |

| | | |

| | | |

| | | |

\ . \ . \ .

|

|

\ .

where L is defined as

b

l /z

base

. l,

b

and z

base

are the leakage inductance, base frequency and

base impedance of STATCOM. All the parameters and variables are expressed in per unit

(p.u.) system. Equation (9) is transformed into dq0 reference frame. The system variables in

the dq0 frame are expressed as follows

b

d1 d2 d d

b

q q q2 q2 b

-r

-

-e +e + V i i

L

S = + (10)

L i i -e +e -r

-

L

| |

|

| | | | | |

|

| | |

|

|

\ . \ . \ .

|

\ .

where id and iq are the d- and q-axis components of LV-side currents. e

d1

and e

q1

are the

voltage components of VSC-1, and e

d2

and e

q2

are the voltage components of VSC-2.

Equation(10) interrelates the AC parameters of the STATCOM with those of the grid. The

dependence between DC and AC parameters of STATCOM is derived using instantaneous

power balance equations. The following equation gives the power balance condition between

the AC and DC links of VSC-1

dc1 dc1 d1 d q1 q

3

V i = ( e i + e i ) (11)

2

The current flowing through the DC link capacitor c

1

is related to the DC link voltage V

dc1

as

follows

dc1

dc1 b 1 dc1

1

V

SV = C i - (12)

r

| |

|

\ .

where C

1

is defined as 1/(

b

c

1

z

base

). Substituting i

dc1

from equation (11)

dc1

dc1 b 1 d1 d q1 q

dc1 1

3 V

SV = C (e i + e i ) - (13)

2V r

| |

|

. \

Similarly, the governing equation for VSC-2 is expressed as

dc2

dc2 b 2 d2 d q2 q

dc2 2

-3 V

SV = C (e i + e i ) - (14)

2V r

| |

|

. \

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 434

Equations (10), (13), and (14) represent the behavior of the system.

4. Development of Controller:

The proposed asymmetric twin converter based STATCOM has two DC link voltages V

dc1

and V

dc2

. The controller should regulate these two DC link voltages and govern the total

reactive power flowing to/from the STATCOM. The total active power required to overcome

losses and regulate DC link voltages is drawn by STATCOM from the grid. This active

power needs to be redistributed among the two DC links. The distribution should ensure that

the two DC link voltages V

dc1

andV

dc2

are maintained equal to their corresponding reference

values.

Figure 4: Controller for STATCOM

5. Current Control:

The overall system is represented by two coupled differential equations, as depicted in (10).

To decouple them, two variables x1 and x2 are defined such that

d1 d2 1 q

b

L

-e + e = (x - i ) - V (15)

q1 q2 2 + d

b

L

-e + e = (x i ) (16)

By combining (10) with (15) and (16), the decoupled system equations are obtained as

follows:

b

d d 1 b

2 q q b

-r

0

i i x L

S = + (17)

x L i i -r

0

L

| |

|

| | | | | |

|

| | |

| \ . \ . \ .

|

\ .

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 435

Applying small signal analysis on the decoupled system of (17), the small signal plant

transfer function is derived as

( )

d q

b

1 2

i i 1

G S = = = (18)

r

x x

S+

L

Control variables x

1

and x

2

govern the system currents i

d

and i

q

, respectively, as per the

differential equation (17). Therefore, current control is achieved by controlling variables x

1

and x

2

using the errors between reference values and actual currents, as given by

1 p1 d_ref d i1 d_ref d ) X = k (i - i ) + k (i - i )dt (19

}

2 p2 q_ref q i2 q _ref q ) X = k (i -i ) + k (i - i )dt (20

}

Required LV voltages e

d1

e

d2

and e

q1

e

q2

are derived by using these values of x

1

and x

2

in

(15) and (16). To generate these voltages, modulation signals for the VSCs are derived as

follows

d1 q1 d2 q2

d1 q1 d2 q2

dc1 dc1 dc2 dc2

e e e e

m = ; m = ; m = ; m = ; (21)

V V V V

An inner current controller is implemented using (15), (16), and (19)(21), as shown in Fig.

4.

B. Reactive Power Control:

STATCOMs are commonly used either for transmission line voltage support or for reactive

power compensation of load. For voltage support of the transmission line, the reactive current

reference i

q_ref

is controlled by the deviation of the transmission line voltage from its nominal

value. On the other hand, for load compensation operation, the reactive current reference i

q_ref

is controlled by the deviation of source power factor from its required value. In both the

aforementioned cases, i

q_ref

will be supplied to the current controller by a higher level

controller.

C. DC Voltage Control:

i. Sum of DC Voltages: The sum of the dc voltages (V

dc1

+ V

dc2

) increases with the net

real power flow from grid to STATCOM and vice versa. In other words, the error in

the sum of DC link voltages (V

dc1

+ V

dc2

V

dc1ref

V

dc2ref

) indicates the amount of

real power to be absorbed from the grid. Hence, the d-axis reference current i

d_ref

is

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 436

controlled by the error existing between reference and actual DC link voltages of

VSCs, as shown in Fig. 4.

ii. Difference of DC Voltages: System equations (13) and (14) are coupled equations

describing the behavior of the DC link voltages. Considering C

1

= C

2

= C and

subtracting (14) from (13) give

dc1 dc2

dc1 dc2 3 b

1 2

V V

S(V - V ) = X - C( - ) (22)

r r

b d1 d2 q1 q2

3 d q

dc1 dc2 dc1 dc2

3 C e e e e

X = i ( + ) + i ( + ) (23)

2 V V V V

(

(

iii. Substituting modulation signals from (21) into (23) gives

b

3 d d1 d2 q q1 q2

3 C

X = i (m +m ) + i (m +m ) (24)

2

(

b

3

3 C

X = (m * i) (25)

2

where the modulation vector m = m

d1

+ m

d2

+ j(m

q1

+ m

q2

) and the current vector i = i

d

+ j i

q

.

Considering r

1

= r

2

= r and applying small signal analysis on (22) give the transfer function

dc1 dc2

b 3

V - V 1

H(S) = = (26)

C X

S+

r

Hence, the difference in power requirement between VSC-1 and VSC 2 is reflected in X

3

.

Using it, ( m* i ) is determined from (25). To achieve the required power flow between VSCs

with low DC link voltages, the modulation vector m is maintained in phase with i . Hence

3

b

2

m = X , m = i (27)

3 Ci

Z

The controller which ensures that the difference of DC voltages V

dc1

V

dc2

is maintained

equal to the reference V

dc1_ref

V

dc2_ref

is shown in Fig. 4.

D. Generation of Modulation Signals:

The current controller, shown in Fig. 4, generates the signals for primary voltages e

d1

e

d2

and

e

q1

e

q2

. These are transformed to modulation signals as follows:

d1 dc1 d2 dc2 d1 d2

q1 dc1 q2 dc2 q1 q2

m V - m V = e - e

m V - m V = e - e (28)

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 437

Furthermore, the Difference of DC Voltages controller generates m

d1

+ m

d2

and m

q1

+ m

q2

.

By arithmetic operation on the outputs of these two controllers, the individual modulation

signals for the two VSCs m

d1

, m

q1

, m

d2

, and m

q2

are generated by the block Modulation

Signals Generator, as shown in Fig. 4. These signals are then converted to stationary abc

frame of reference. The modulation waveforms for the two VSCs are then compared with the

carrier waveforms to generate gating signals for VSCs.

The simulation circuit for asymmetric twin converter STATCOM is shown in Fig. 5. The

distribution should ensure that the two DC link voltages V

dc1

and V

dc2

are maintained equal to

their corresponding reference values as show in fig. 5.

Figure 5: Simulation Circuit for Asymmetric Twin Converter Topology Based High Power

STATCOM

Figure 6: Simulation Circuit on Controller for STATCOM

Conn2

Conn4

Conn6

Conn1

Conn3

Conn5

transformer connected i n shunt wi th T-l i ne

Continuous

powergui In1

In2

In3

In4

In5

Out1

Out2

control l er

v

+-

Vol tage Measurement2

v

+

-

Vol tage Measurement1

v

+

-

Vol tage Measurement

Scope2 Scope1

Paral l el RLC Branch1

Paral l el RLC Branch

g

A

B

C

+

-

Inverter1

g

A

B

C

+

-

Inverter 2

293.6

Di spl ay1

804.3

Di spl ay

DC Vol tage Source1

DC Vol tage Source

i

+

-

Current Measurement3

i

+

-

Current Measurement2

i

+

-

Current Measurement1

x1

x2

del ta(kd)

del ta(kq)

kq2

kd2

kd1

kq1

note that subsystem1 and subsystem2 are identical,

but still its a "better" case

Idfre

2

Out2

1

Out1

1

|V|'

-K-

w3

1

w2

-K-

w

X

Y

x

y

uni t vector1

A

B

C

D

Q

0

abc to dq1

d

q

pwm

Subsystem2

d

q

pwm

Subsystem1

Scope3

Scope2

Product6

Product5

Product4

Product3

Product2

Product1

In1 Out1

PI5

In1 Out1

PI4

In1 Out1

PI3

In1 Out1

PI1

-K-

L'/wb1

-K-

L'/wb

Di vi de3

Di vi de2

Di vi de1

Di vi de

1.122

Di spl ay1

1

Constant3

-C-

Constant2

-C-

Constant1

1

6

1

3

1

2

-K-

1/230.0

-K-

1/230

-K-

1/125.5

-K-

1/125.2

-K-

1/125.1

1

1

5

In5

4

In4

3

In3

2

In2

1

In1

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 438

Figure 7: Simulation Circuit Based on Fuzzy Logic for STATCOM

Figure 8: Simulation Circuit Based on Fuzzy Logic Controller for STATCOM

6. Results:

The results of the simulation files of Asymmetric Twin Converter Based STATCOM and

Fuzzy Logic based STATCOM are shown below.

Conn2

Conn4

Conn6

Conn1

Conn3

Conn5

transformer connected i n shunt wi th T-l i ne

Continuous

powergui In1

In2

In3

In4

In5

Out1

Out2

control l er

v

+-

Vol tage Measurement2

v

+

-

Vol tage Measurement1

v

+

-

Vol tage Measurement

Scope4

Scope3

Scope2 Scope1

Paral l el RLC Branch1

Paral l el RLC Branch

g

A

B

C

+

-

Inverter1

g

A

B

C

+

-

Inverter 2

293.5

Di spl ay1

804.2

Di spl ay

Fo=72Hz

DC Vol tage Source1

DC Vol tage Source

i

+

-

Current Measurement4

i

+

-

Current Measurement3

i

+

-

Current Measurement1

x1

x2

del ta(kd)

del ta(kq)

kq2

kd2

kd1

kq1

note that subsystem1 and subsystem2 are identical,

but still its a "better" case

2

Out2

1

Out1

1

|V|'

-K-

w3

1

w2

-K-

w

X

Y

x

y

uni t vector1

A

B

C

D

Q

0

abc to dq1

In3 Out1

Subsystem5

In3Out1

Subsystem4

In3Out1

Subsystem3

d

q

pwm

Subsystem2

d

q

pwm

Subsystem1

In3Out1

Subsystem

Scope2

Product6

Product5

Product4

Product3

Product2

Product1

-K-

L'/wb1

-K-

L'/wb

Di vi de3

Di vi de2

Di vi de1

Di vi de

1.263

Di spl ay1

1

Constant3

-C-

Constant2

-C-

Constant1

1

6

1

3

1

2

-K-

1/230.0

-K-

1/230

-K-

1/125.5

-K-

1/125.2

-K-

1/125.1

1

1

5

In5

4

In4

3

In3

2

In2

1

In1

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 439

Figure 9: Simulated Transient Test Results. (i) LV-side voltage e

a

. (ii) LV-side phase-a

transformer current i

a

. (iii) p.u. reactive current i

q

. (iv) DC link voltages V

dc1

and V

dc2

.

Figure 10: Total Harmonic Distortion of LV Side Voltage (e

a

) For Asymmetric Twin

Converter Based STATCOM

Figure 11: Total Harmonic Distortion of LV-Side Voltage (e

a

) For Fuzzy Logic Based

STATCOM

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 440

Figure 12: Harmonic Spectrum Phase-a (Fuzzy Logic based)

7. Conclusion:

A high-power STATCOM based on two 2-level VSCs is reported in [1]. Reduced component

count, simpler layout of switches and reduced capacitance requirement are the attractive

features of the scheme over the diode clamped and cascaded multilevel converters. In the

proposed topology, only two DC voltages have to be controlled. Furthermore, the ratio of the

DC link voltages of the two VSCs is selected such that low distortion in current is achieved.

A DC link voltage controller has been proposed to regulate the DC link voltages of the two

converters by drawing requisite amount of real power from the utility and by differentially

distributing them between the two converters. A mathematical model of the system is

developed to facilitate the design of the controller. Simulation results carried in a simulation

study of proposed topology has been carried out using MATLAB/Simulink and the results are

presented.

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 441

References:

1. S. Anand, B. G. Fernandes, and K. Chatterjee, A new 4-level open-ended

transformer based STATCOM for high power applications, in Proc. 36

th

Annu. IEEE

IECON, Nov. 710, 2010, pp. 19571962.

2. C. Schauder and H. Mehta, Vector analysis and control of advanced static VAR

compensators, Proc. Inst. Elect. Eng. CGener., Transm. Distrib., vol. 140, no. 4,

pp. 299306, Jul. 1993.

3. E. M. John, A. Oskoui, and A. Petersson, Using a STATCOM to retire urban

generation, in Proc. IEEE Power Syst. Conf. Expo., Oct. 2004, vol. 2, pp. 693698.

4. D. Soto and T. C. Green, A comparison of high-power converter topologies for the

implementation of FACTS controllers, IEEE Trans. Ind. Electron., vol. 49, no. 5, pp.

10721080, Oct. 2002.

5. J. Rodriguez, J.-S. Lai, and F. Z. Peng, Multilevel inverters: A survey of topologies,

controls, and applications, IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724738,

Aug. 2002.

6. Y. Cheng, C. Qian, M. L. Crow, S. Pekarek, and S. Atcitty, A comparison of diode-

clamped and cascaded multilevel converters for a STATCOM with energy storage,

IEEE Trans. Ind. Electron., vol. 53, no. 5, pp. 1512 1521, Oct. 2006.

7. H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, Medium-voltage multilevel

convertersState of the art, challenges, and requirements in industrial applications,

IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 25812596, Aug. 2010.

8. S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B.Wu, J.

Rodriguez, M. A. Prez, and J. I. Leon, Recent advances and industrial applications

of multilevel converters, IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 25532580,

Aug. 2010.

9. F. Z. Peng, J. W. McKeever, and D. J. Adams, A power line conditioner using

cascade multilevel inverters for distribution systems, IEEE Trans. Ind. Appl., vol. 34,

no. 6, pp. 12931298, Nov./Dec. 1998.

10. K. V. Patil, R. M. Mathur, J. Jiang, and S. H. Hosseini, Distribution system

compensation using a new binary multilevel voltage source inverter, IEEE Trans.

Power Del., vol. 14, no. 2, pp. 459464, Apr. 1999.

11. C. K. Lee, S. Y. Ron Hui, and H. S. Chung, A 31-level cascade inverter for power

applications, IEEE Trans. Ind. Electron., vol. 49, no. 3, pp. 613617, Jun. 2002.

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 442

12. H. Akagi, S. Inoue, and T. Yoshii, Control and performance of a transformerless

cascade PWM STATCOM with star configuration, IEEE Trans. Ind. Appl., vol. 43,

no. 4, pp. 10411049, Jul./Aug. 2007.

13. M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, A survey on

cascaded multilevel inverters, IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197

2206, Jul. 2010.

14. Y. Fukuta and G. Venkataramanan, DC bus ripple minimization in cascaded H-

bridge multilevel converters under staircase modulation, in Proc. 37th IEEE IAS

Annu. Meeting, 2002, vol. 3, pp. 19881993.

15. S. Vazquez, J. I. Leon, J. M. Carrasco, L. G. Franquelo, E. Galvan, M. Reyes, J. A.

Sanchez, and E. Dominguez, Analysis of the power balance in the cells of a

multilevel cascaded H-bridge converter, IEEE Trans. Ind. Electron., vol. 57, no. 7,

pp. 22872296, Jul. 2010.

16. S. Lu, S.Mariethoz, and K. A. Corzine, Asymmetrical cascade multilevel converters

with noninteger or dynamically changing DC voltage ratios: Concepts andmodulation

techniques, IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 24112418, Jul. 2010.

17. S. Vazquez, J. I. Leon, L. G. Franquelo, J. J. Padilla, and J. M. Carrasco, DC-

voltage-ratio control strategy for multilevel cascaded converters fed with a single dc

source, IEEE Trans. Ind. Electron., vol. 56, no. 7, pp. 25132521, Jul. 2009.

18. J. A. Barrena, L. Marroyo, M. A. R. Vidal, and J. R. T. Apraiz, Individual voltage

balancing strategy for PWM cascaded H-bridge converterbased STATCOM, IEEE

Trans. Ind. Electron., vol. 55, no. 1, pp. 2129, Jan. 2008.

19. P. Cortes, A. Wilson, S. Kouro, J. Rodriguez, and H. Abu-Rub, Model predictive

control of multilevel cascaded H-bridge inverters, IEEE Trans. Ind. Electron., vol.

57, no. 8, pp. 26912699, Aug. 2010.

20. S. Rohner, S. Bernet, M. Hiller, and R. Sommer, Modulation, losses, and

semiconductor requirements of modular multilevel converters, IEEE Trans. Ind.

Electron., vol. 57, no. 8, pp. 26332642, Aug. 2010.

21. J. I. Leon, S. Kouro, S. Vazquez, R. Portillo, L. G. Franquelo, J. M. Carrasco, and J.

Rodriguez, Multidimensional modulation technique for cascaded multilevel

converters, IEEE Trans. Ind. Electron.,vol. 58, no. 2, pp. 412420, Feb. 2011.

22. Y. Liu, A. Q. Huang, S.Wenchao, S. Bhattacharya, and T. Guojun, Smallsignal

model-based control strategy for balancing individual dc capacitor voltages in cascade

January, 2014 www.ijirs.com Vol 3 Issue 1

International Journal of Innovative Research and Studies Page 443

multilevel inverter-based STATCOM, IEEE Trans. Ind. Electron., vol. 56, no. 6, pp.

22592269, Jun. 2009.

23. J. I. Leon, S. Vazquez, S. Kouro, L. G. Franquelo, J. M. Carrasco, and J. Rodriguez,

Unidimensional modulation technique for cascaded multilevel converters, IEEE

Trans. Ind. Electron., vol. 56, no. 8, pp. 29812986, Aug. 2009.

24. S. Ponnaluri, J. K. Steinke, P. Steimer, S. Reichert, and B. Buchmann, Design

comparison and control of medium voltage STATCOM with novel twin converter

topology, in Proc. 35th Annu. IEEE Power Electron. Spec. Conf., 2004, vol. 4, pp.

25462552.

25. K. K. Mohapatra, K. Gopakumar, V. T. Somasekhar, and L. Umanand, A harmonic

elimination and suppression scheme for an open-end winding induction motor drive,

IEEE Trans. Ind. Electron., vol. 50, no. 6, pp. 11871198, Dec. 2003.

26. D. G. Holmes and T. A. Lipo, Carrier-basedPWMofmultilevel inverter, in Pulse

Width Modulation for Power Converters: Principles and Practice, IEEE Series on

Power Engineering. Hoboken, NJ: Wiley, 2003, ch. 11, pp. 453530.

27. B. P. McGrath and D. G. Holmes, Multicarrier PWM strategies for multilevel

inverters, IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 858 867, Aug. 2002.

28. S. Anand, B. G.Fernandes, and K. Chatterjee, Asymmetric-Twin-Converter-

Topology-Based High-Power STATCOM IEEE Transactions on Industrial

Electronocs, vol. 60, no.1, pp. 11-19, January2013.

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Control Theory With MathScript ExamplesDokument90 SeitenControl Theory With MathScript ExamplessirageldeenNoch keine Bewertungen

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Tuning of A PID Controller Using Ziegler-Nichols MethodDokument7 SeitenTuning of A PID Controller Using Ziegler-Nichols MethodTomKish100% (1)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Electrical Machine Design Unit1-VKDokument8 SeitenElectrical Machine Design Unit1-VKSajidh M ShamsudeenNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- Electrical Machines Curriculum GuideDokument76 SeitenElectrical Machines Curriculum GuidesirageldeenNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Simulink Implementation and Analysis of PWMDokument102 SeitenSimulink Implementation and Analysis of PWMAla'a HusseinNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Applications of MATLAB in Science and EngineeringDokument522 SeitenApplications of MATLAB in Science and EngineeringNicoleta100% (1)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Minimal Harmonic Controller For A StatcomDokument10 SeitenA Minimal Harmonic Controller For A StatcomsirageldeenNoch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Basics For Practical Operation - Motor ProtectionDokument68 SeitenBasics For Practical Operation - Motor ProtectionSumit VermaNoch keine Bewertungen

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- InTech-Understanding Power Quality Based Facts Using Interactive Educational Gui Matlab PackageDokument25 SeitenInTech-Understanding Power Quality Based Facts Using Interactive Educational Gui Matlab PackagesirageldeenNoch keine Bewertungen

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- Nonlinear, Control, DstatcomDokument7 SeitenNonlinear, Control, DstatcomsirageldeenNoch keine Bewertungen

- 5-35 KV CablesDokument16 Seiten5-35 KV CablessirageldeenNoch keine Bewertungen

- 44 Statcom04Dokument14 Seiten44 Statcom04sirageldeenNoch keine Bewertungen

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Power Quality Improvement by Using DSTATCOMDokument12 SeitenPower Quality Improvement by Using DSTATCOMsirageldeenNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- 11 KV, Feeder, With, Statcom, ProjectDokument102 Seiten11 KV, Feeder, With, Statcom, ProjectsirageldeenNoch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- 11kv, Dstatcom, Control 1Dokument18 Seiten11kv, Dstatcom, Control 1sirageldeenNoch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Non Linear Control of StatcomDokument6 SeitenNon Linear Control of StatcomsirageldeenNoch keine Bewertungen

- Tuning of A PID Controller Using Ziegler-Nichols MethodDokument7 SeitenTuning of A PID Controller Using Ziegler-Nichols MethodTomKish100% (1)

- Dynamic Compensation StudyDokument61 SeitenDynamic Compensation StudysirageldeenNoch keine Bewertungen

- Power Flow AnalysisDokument11 SeitenPower Flow AnalysisChristina Tio TrisnasariNoch keine Bewertungen

- Guide to Earthing Systems in Electrical NetworksDokument113 SeitenGuide to Earthing Systems in Electrical NetworksRameez ZafarNoch keine Bewertungen

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Statcom, Cont, ModelDokument6 SeitenStatcom, Cont, ModelsirageldeenNoch keine Bewertungen

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- Statcom, Cont, ModelDokument6 SeitenStatcom, Cont, ModelsirageldeenNoch keine Bewertungen

- Power System Simulation Lab ManualDokument41 SeitenPower System Simulation Lab ManualArivumani86% (14)

- Jacobian, Lineariz, StatcomDokument66 SeitenJacobian, Lineariz, StatcomsirageldeenNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Save - Lamp AdvantagesDokument30 SeitenSave - Lamp AdvantagessirageldeenNoch keine Bewertungen

- Wind, DQ Decoupled Bees, DSTATCOM 2Dokument4 SeitenWind, DQ Decoupled Bees, DSTATCOM 2sirageldeenNoch keine Bewertungen

- DSTATCOM With Multilevel InveterDokument85 SeitenDSTATCOM With Multilevel InveterPoojitha ChouduryNoch keine Bewertungen

- pll.m in PLL.rar: Language/语言Dokument44 Seitenpll.m in PLL.rar: Language/语言sirageldeenNoch keine Bewertungen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- MK 231 ADokument4 SeitenMK 231 AAli AhmadNoch keine Bewertungen

- Lab 9: O A: Perational MplifiersDokument6 SeitenLab 9: O A: Perational MplifiersAhmed ChNoch keine Bewertungen

- 42-QR-1P26 B3 Element Hydro Quick StartDokument1 Seite42-QR-1P26 B3 Element Hydro Quick StartElputoAmo XDNoch keine Bewertungen

- Diverse BTS For Sale From Power Storm 4SN06200834Dokument4 SeitenDiverse BTS For Sale From Power Storm 4SN06200834Mohamed KsimaNoch keine Bewertungen

- GSA Chipset Report November 2018Dokument14 SeitenGSA Chipset Report November 2018Muhammad Jamil AwanNoch keine Bewertungen

- Iwh 090V08N0 1 - DS - 3 0 4Dokument1 SeiteIwh 090V08N0 1 - DS - 3 0 4KonstantinNoch keine Bewertungen

- LINEAR INTEGRATED CIRCUITS Unit3 Raghudathesh VTUDokument30 SeitenLINEAR INTEGRATED CIRCUITS Unit3 Raghudathesh VTUraghudatheshNoch keine Bewertungen

- 27 GHZ Silicon - Contacted Waveguide - Coupled GeSi Avalanche PhotodiodeDokument7 Seiten27 GHZ Silicon - Contacted Waveguide - Coupled GeSi Avalanche Photodiodeanushpamathi SundararajanNoch keine Bewertungen

- EMI Recording Console Handbook+Mk2Dokument71 SeitenEMI Recording Console Handbook+Mk2Zack Dagoba100% (2)

- HAVSO2S0022GSMDokument2 SeitenHAVSO2S0022GSMNISHANNoch keine Bewertungen

- DC aDCghskjskksks FjsDokument4 SeitenDC aDCghskjskksks FjsSaiteja GundapuNoch keine Bewertungen

- Me15n10 V1.4 - SpecDokument5 SeitenMe15n10 V1.4 - Specrov1976Noch keine Bewertungen

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- c600 Series Chipset Datasheet PDFDokument956 Seitenc600 Series Chipset Datasheet PDFSetya Montana100% (1)

- 2.1 Introduction BJTDokument3 Seiten2.1 Introduction BJTlizhi0007Noch keine Bewertungen

- PMU Lecture 6 - The Impedance Model and ZbusDokument17 SeitenPMU Lecture 6 - The Impedance Model and ZbusPoor AdamNoch keine Bewertungen

- Electrical Part List PDFDokument15 SeitenElectrical Part List PDFsafi alsafiNoch keine Bewertungen

- 100 - 200 Transistor Circuits by Colin Mitchell PDFDokument115 Seiten100 - 200 Transistor Circuits by Colin Mitchell PDFJoko NelongsoNoch keine Bewertungen

- Computer Book MaterialDokument69 SeitenComputer Book MaterialAqib Asad100% (1)

- Analog Electronics July 2017 (2015 Scheme)Dokument3 SeitenAnalog Electronics July 2017 (2015 Scheme)Movies and tv showsNoch keine Bewertungen

- Lecture 1 CDokument29 SeitenLecture 1 CLohith NNoch keine Bewertungen

- SW-TM4C-RLN-2 1 0 12573Dokument36 SeitenSW-TM4C-RLN-2 1 0 12573trungkiena6Noch keine Bewertungen

- Operation: USB Interface U1, U2, U3 and U4Dokument5 SeitenOperation: USB Interface U1, U2, U3 and U4Mohammed MostefaiNoch keine Bewertungen

- Multiple Choice Questions For Electronics Engineering Part 1Dokument4 SeitenMultiple Choice Questions For Electronics Engineering Part 1Anshad100% (1)

- Review On SIW TechnologyDokument6 SeitenReview On SIW TechnologyNitinNoch keine Bewertungen

- Improve 3-Phase Motor Efficiency with CapacitorsDokument5 SeitenImprove 3-Phase Motor Efficiency with CapacitorsBunny LuckyNoch keine Bewertungen

- LT Spice ExperimentsDokument15 SeitenLT Spice ExperimentsSachin George ThomasNoch keine Bewertungen

- Vek M4D / Vek M4Dc 4-Channel Loop Detectors For Traffic Light Systems and Car Park CountingDokument3 SeitenVek M4D / Vek M4Dc 4-Channel Loop Detectors For Traffic Light Systems and Car Park CountingFJGV7Noch keine Bewertungen

- ELECTRICAL Sample QuestionDokument17 SeitenELECTRICAL Sample QuestionSambit MohapatraNoch keine Bewertungen

- AD624Dokument17 SeitenAD624سعيد ابوسريعNoch keine Bewertungen

- ViewSonic VPW500 PlasmaDokument82 SeitenViewSonic VPW500 PlasmaMikhailNoch keine Bewertungen

- Introduction to Power System ProtectionVon EverandIntroduction to Power System ProtectionBewertung: 5 von 5 Sternen5/5 (1)

- Shorting the Grid: The Hidden Fragility of Our Electric GridVon EverandShorting the Grid: The Hidden Fragility of Our Electric GridBewertung: 4.5 von 5 Sternen4.5/5 (2)

- Nuclear Energy in the 21st Century: World Nuclear University PressVon EverandNuclear Energy in the 21st Century: World Nuclear University PressBewertung: 4.5 von 5 Sternen4.5/5 (3)

- Introduction to Power System ProtectionVon EverandIntroduction to Power System ProtectionNoch keine Bewertungen

- Power of Habit: The Ultimate Guide to Forming Positive Daily Habits, Learn How to Effectively Break Your Bad Habits For Good and Start Creating Good OnesVon EverandPower of Habit: The Ultimate Guide to Forming Positive Daily Habits, Learn How to Effectively Break Your Bad Habits For Good and Start Creating Good OnesBewertung: 4.5 von 5 Sternen4.5/5 (21)